Implementation of a Programmable Electronic Load for Equipment Testing

Abstract

:1. Introduction

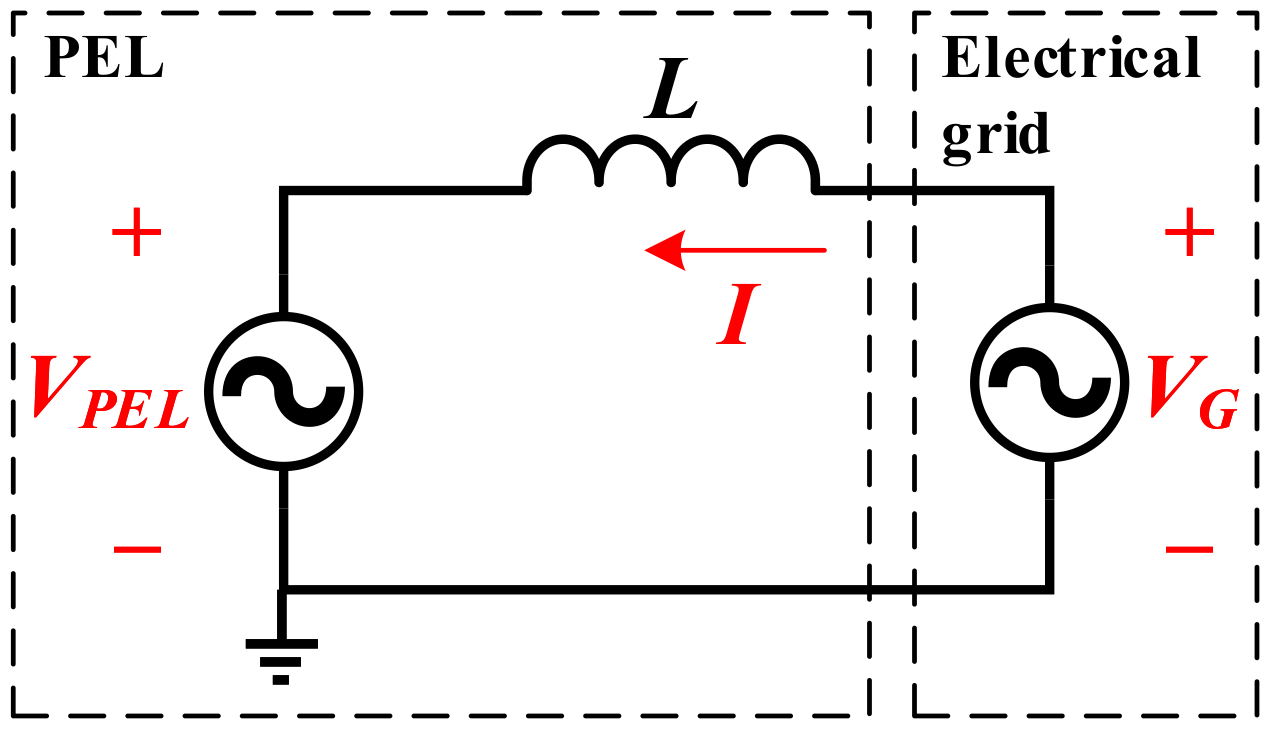

2. PEL Operation Modes and Limits

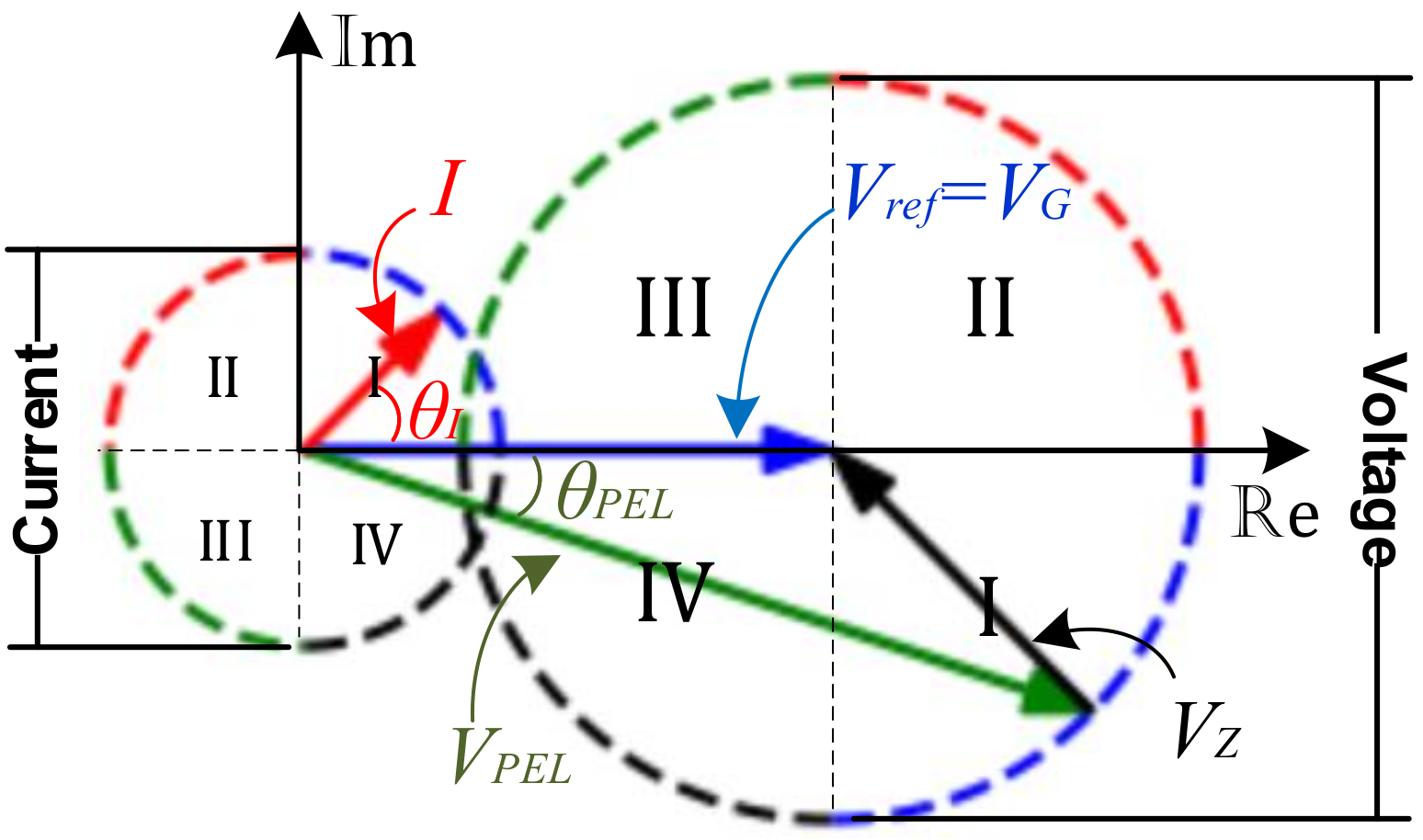

- Figure 3a,i, PEL as pure resistive load. PEL only consumes active power and its current has the same phase and direction as the electrical grid ().

- Figure 3b, PEL as load resistive–capacitive (). If desired, a current in the first quadrant (), then should move for the first quadrant of voltage circumference (both are shown with blue dotted lines).

- Figure 3c, PEL as capacitive load. PEL only consumes reactive power and the current is leading wih respect to the electrical grid.

- Figure 3d, PEL as leading source. If a current in the second quadrant is desired (), then should move for the second quadrant of voltage circumference (both are shown with red dotted lines).

- Figure 3e, PEL as pure active source. PEL only injects active power and its current has a phase and direction in opposition to the electrical grid ().

- Figure 3f, PEL as lagging source. If a current in the third quadrant is desired (), then should move for the third quadrant of voltage circumference (both are shown with green dotted lines).

- Figure 3g, PEL as pure lagging source. PEL only injects reactive power and the current is lagging with respect to the electrical grid.

- Figure 3h, PEL as resistive–inductive load (). If desired, a current in the fourth quadrant (), then should move for the four quadrant of voltage circumference (both are shown with black dotted lines).

- Yellow zone, in which is between and ; then, the PEL behaves as a resistive–capacitive load.

- Green zone, in which is between and ; then, the PEL behaves as a leading source.

- Blue zone, in which is between and ; then, the PEL behaves as a lagging source.

- Pink zone, in which is between and ; then, the PEL behaves as a resistive–inductive load.

- If the hardware does not have the capacity to support the maximum current, then the modulation index of the PEL control must be limited.

- If it is desired to emulate a particular load profile and the grid voltage is known, then it is possible to determine the current with Equation (1). Therefore, it is possible to determine the phasor diagram of the system (see Figure 2) and obtain the magnitude of the DC bus voltage required to emulate that profile.

- If the DC bus voltage is known and the maximum current is supported by the PEL hardware, then Figure 5 can be obtained, each region representing the power quadrant to be emulated as a function of the amplitude and angle emulated by the PEL. However, in case the PEL is unidirectional, it can only operate in two quadrants (yellow and pink), and Figure 5 can be used to constrain the control values based on the relationship of the regions and the axes representing the control variables.

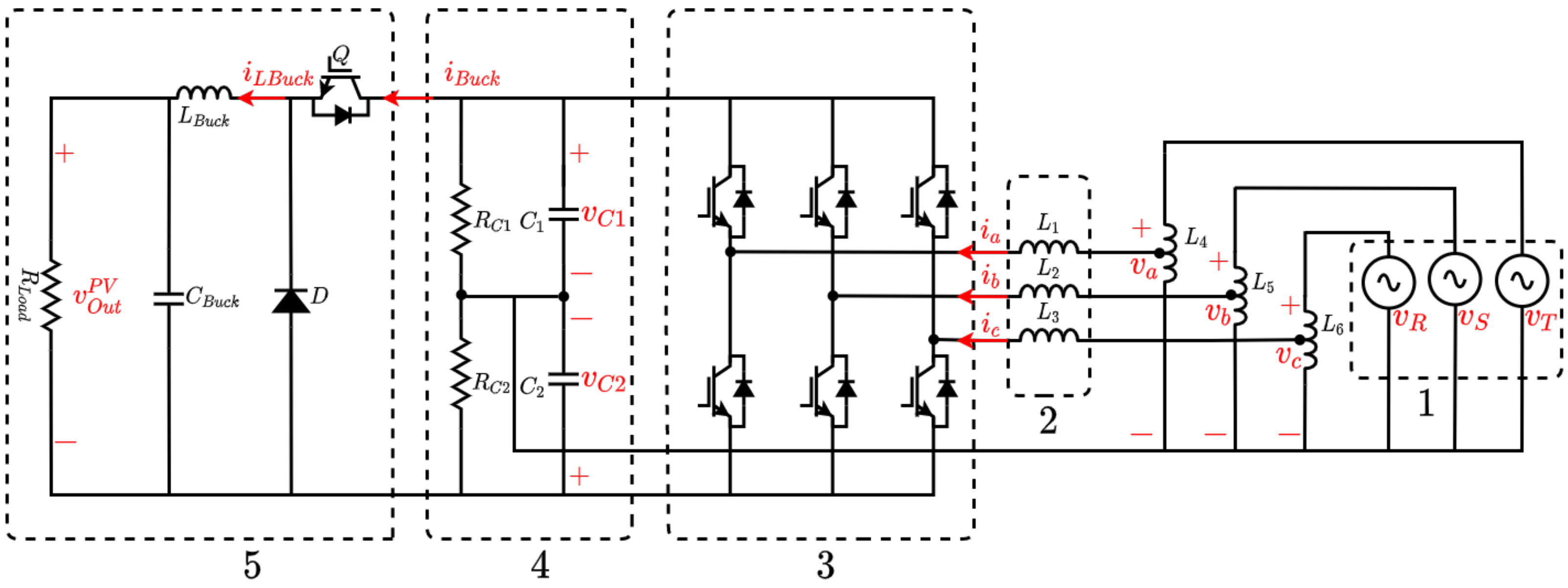

3. Programmable Electronic Load: Implemented Topology

3.1. VSI Mathematical Model

3.2. Mathematical Model of the DC/DC Buck Converter

3.3. Transfer Functions

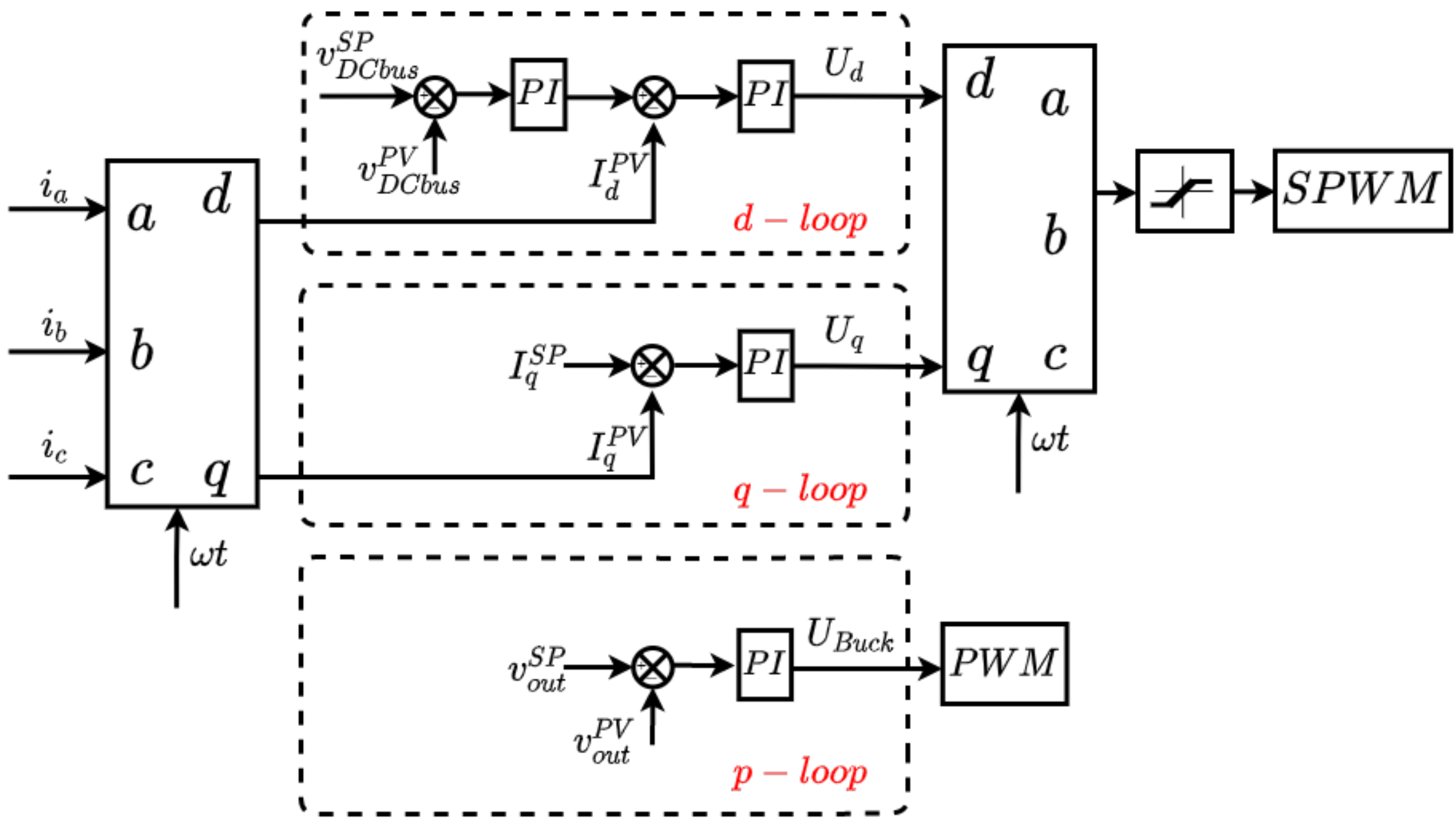

4. Programmable Electronic Load: Control System

- The d-loop is a cascade control. Its external loop regulates the voltage in the DC bus whereas its inner loop controls the current of the d-axis. is the set point of the DC bus voltage whereas the measured DC voltage is . The PI controller of the external loop gives reference to the inner loop, compared with the measured current in the d-axis . The control signal of this cascade system () is one of the two inputs of dq to abc transformation. The parameters for this control are presented in Table 1.

- The q-loop is a PI control loop where is the set point, and is the measured current in the q-axis. The control signal of this system () is the other input of the dq to abc transformation block. The output of the dq to abc transformation block passes by a limiter in order to avoid over-modulation in the SPWM block.

- The p-loop is in charge of determining the dissipated active power in , adjusting the output voltage with the Buck converter. The set point is and the measurement is . The control signal of this system () is the input of the PWM block. The control parameters for the Buck converter are given in Table 2.

5. Experimental Results

5.1. Experimental Setup

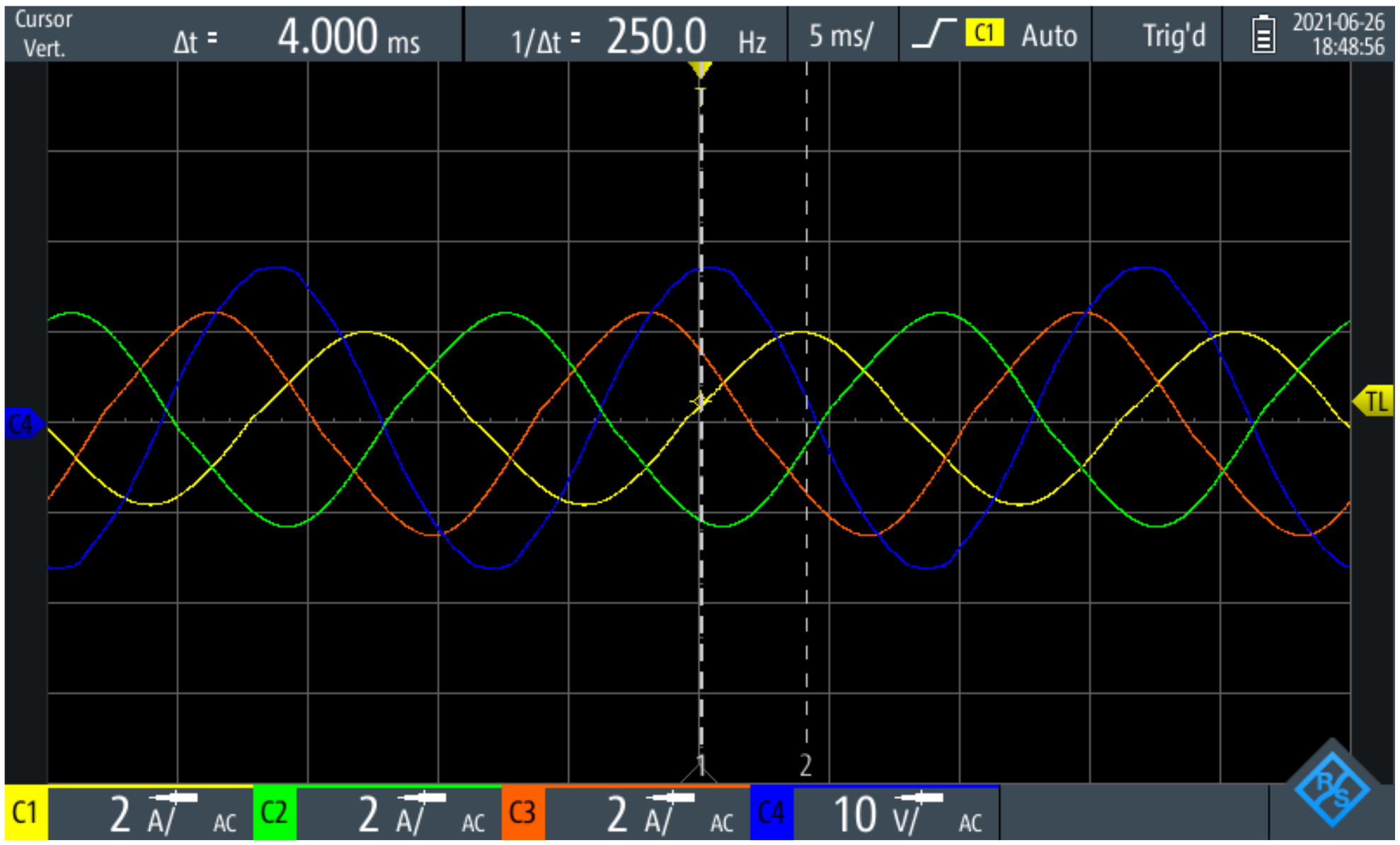

5.2. Emulation of Three-Phase Load Profiles

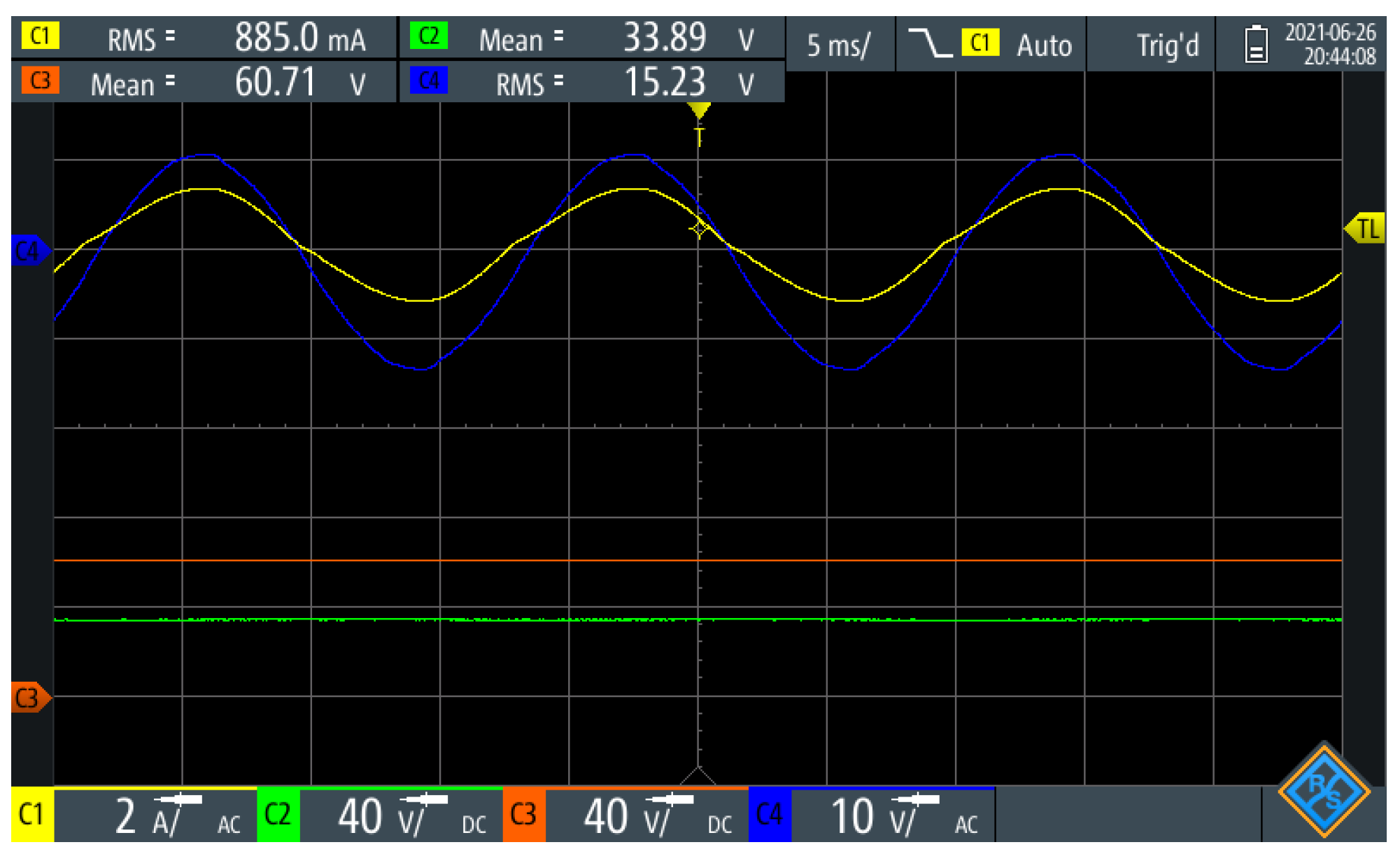

5.3. DC Bus Stability with Different Load Profiles

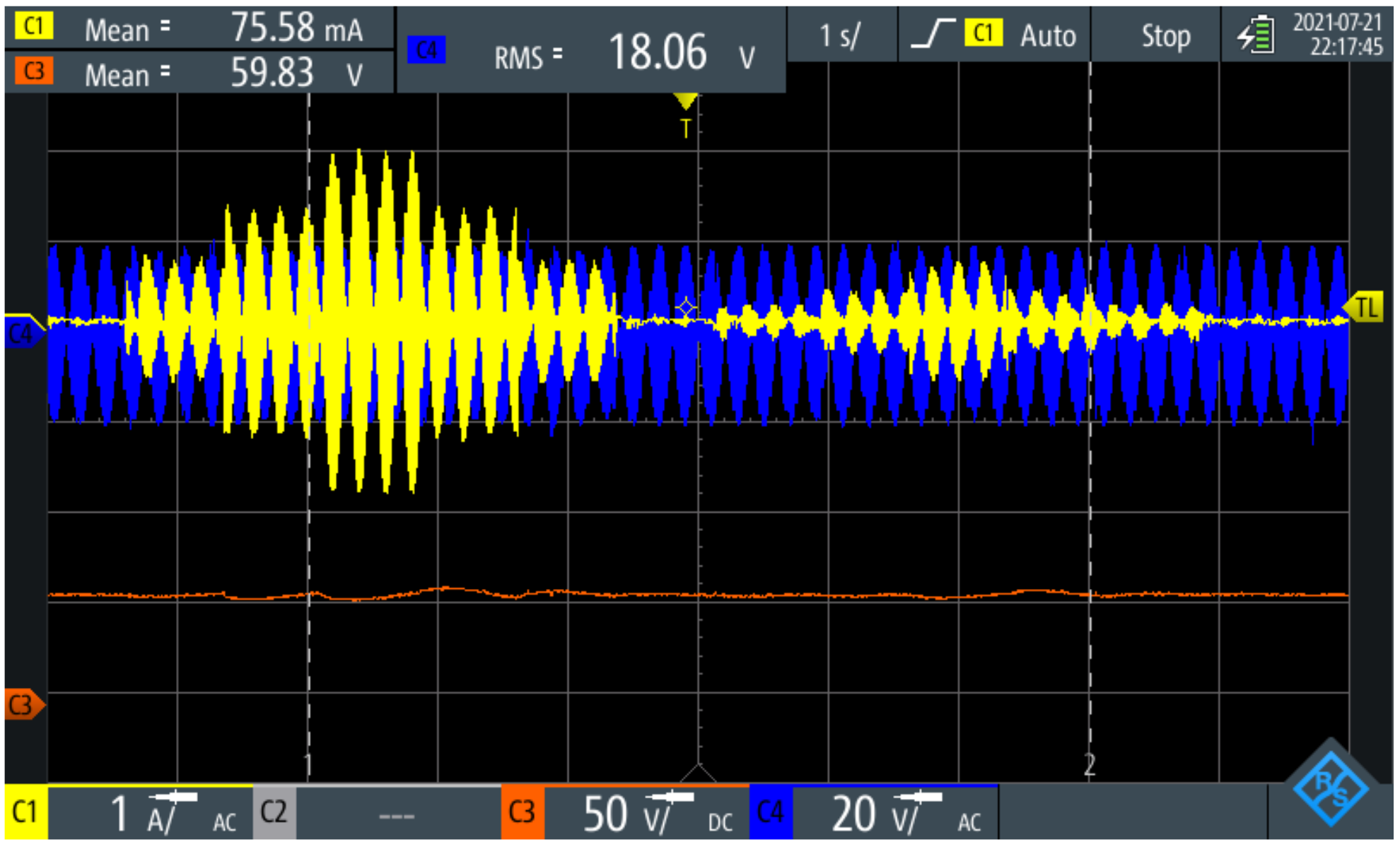

5.4. Transient Behavior of the PEL with Changes in Load Profile

6. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Telaretti, E.; Dusonchet, L. Battery storage systems for peak load shaving applications: Part 2: Economic feasibility and sensitivity analysis. In Proceedings of the 2016 IEEE 16th International Conference on Environment and Electrical Engineering (EEEIC), Florence, Italy, 7–10 June 2016; pp. 1–6. [Google Scholar] [CrossRef]

- Shen, J.; Jiang, C.; Li, B. Controllable Load Management Approaches in Smart Grids. Energies 2015, 8, 11187–11202. [Google Scholar] [CrossRef] [Green Version]

- Geng, Z.; Gu, D.; Hong, T.; Czarkowski, D. Programmable Electronic AC Load Based on a Hybrid Multilevel Voltage Source Inverter. IEEE Trans. Ind. Appl. 2018, 54, 5512–5522. [Google Scholar] [CrossRef]

- Pudur, R.; Srivastava, V.K. Performance Study of Electronic Load Controller for Integrated Renewable Sources. In Proceedings of the 2018 2nd International Conference on Electronics, Materials Engineering Nano-Technology (IEMENTech), Kolkata, India, 4–5 May 2018; pp. 1–6. [Google Scholar] [CrossRef]

- Serban, I.; Ion, C.; Marinescu, C.; Cirstea, M.N. Electronic Load Controller for Stand-Alone Generating Units with Renewable Energy Sources. In Proceedings of the IECON 2006 32nd Annual Conference on IEEE Industrial Electronics, Paris, France, 6–10 November 2006; pp. 4309–4312. [Google Scholar] [CrossRef]

- Kanadhiya, M.C.; Bohra, S.S. Simulation Analysis of Active Programmable Electronic AC Load. In Proceedings of the 2018 3rd International Conference for Convergence in Technology (I2CT), Pune, India, 6–8 April 2018; pp. 1–6. [Google Scholar] [CrossRef]

- Rosas-Caro, J.C.; Peng, F.Z.; Cha, H.; Rogers, C. Z-Source-Converter-Based Energy-Recycling Zero-Voltage Electronic Loads. IEEE Trans. Ind. Electron. 2009, 56, 4894–4902. [Google Scholar] [CrossRef]

- Shinde, U.K.; Kadwane, S.G.; Gawande, S.P.; Keshri, R. Solar PV emulator for realizing PV characteristics under rapidly varying environmental conditions. In Proceedings of the 2016 IEEE International Conference on Power Electronics, Drives and Energy Systems (PEDES), Trivandrum, India, 14–17 December 2016; pp. 1–5. [Google Scholar] [CrossRef]

- Zhou, Z.; Macaulay, J. An Emulated PV Source Based on an Unilluminated Solar Panel and DC Power Supply. Energies 2017, 10, 2075. [Google Scholar] [CrossRef] [Green Version]

- Averous, N.R.; Stieneker, M.; De Doncker, R.W. Grid emulator requirements for a multi-megawatt wind turbine test-bench. In Proceedings of the 2015 IEEE 11th International Conference on Power Electronics and Drive Systems, Sydney, Australia, 9–12 June 2015; pp. 419–426. [Google Scholar] [CrossRef]

- Biligiri, K.; Harpool, S.; von Jouanne, A.; Amon, E.; Brekken, T. Grid emulator for compliance testing of Wave Energy Converters. In Proceedings of the 2014 IEEE Conference on Technologies for Sustainability (SusTech), Portland, OR, USA, 24–26 July 2014; pp. 30–34. [Google Scholar] [CrossRef]

- Lohde, R.; Fuchs, F.W. Laboratory type PWM grid emulator for generating disturbed voltages for testing grid connected devices. In Proceedings of the 2009 13th European Conference on Power Electronics and Applications, Barcelona, Spain, 8–10 September 2009; pp. 1–9. [Google Scholar]

- Serna-Montoya, L.F.; Cano-Quintero, J.B.; Muñoz-Galeano, N.; López-Lezama, J.M. Programmable Electronic AC Loads: A Review on Hardware Topologies. In Proceedings of the 2019 IEEE Workshop on Power Electronics and Power Quality Applications (PEPQA), Manizales, Colombia, 30–31 May 2019; pp. 1–6. [Google Scholar] [CrossRef]

- Davis, P.N.; Wright, P.S. An Electronic Load to Verify Harmonic Emission Compliance. IEEE Trans. Instrum. Meas. 2017, 66, 1446–1453. [Google Scholar] [CrossRef]

- Wang Shaokun, H.Z.; Chuanbiao, P. A repetitive control strategy of AC electronic load with energy recycling. In Proceedings of the International Technology and Innovation Conference 2009 (ITIC 2009), Xi’an, China, 12–14 October 2009; p. 3. [Google Scholar]

- Nujithra, T.; Premarathne, U. Investigation of Efficient Heat Dissipation Mechanisms for Programmable DC Electronic Load Design. In Proceedings of the 2018 8th International Conference on Power and Energy Systems (ICPES), Colombo, Sri Lanka, 21–22 December 2018; pp. 201–206. [Google Scholar] [CrossRef]

- Peng, J.; Chen, Y.; Fang, Y.; Jia, S. Design of Programmable DC Electronic Load. In Proceedings of the 2016 International Conference on Industrial Informatics—Computing Technology, Intelligent Technology, Industrial Information Integration (ICIICII), Wuhan, China, 3–4 December 2016; pp. 351–355. [Google Scholar] [CrossRef]

- Tsang, K.M.; Chan, W.L. Fast Acting Regenerative DC Electronic Load Based on a SEPIC Converter. IEEE Trans. Power Electron. 2012, 27, 269–275. [Google Scholar] [CrossRef]

- Kazerani, M. A high-performance controllable AC load. In Proceedings of the 2008 34th Annual Conference of IEEE Industrial Electronics, Vigo, Spain, 4–7 June 2008; pp. 442–447. [Google Scholar] [CrossRef]

- Srinivasa Rao, Y.; Chandorkar, M.C. Real-Time Electrical Load Emulator Using Optimal Feedback Control Technique. IEEE Trans. Ind. Electron. 2010, 57, 1217–1225. [Google Scholar] [CrossRef]

- Zhang, W.; Zhang, X. A novel AC electronic load based on hysteresis current control scheme. In Proceedings of the 2011 International Conference on Electrical and Control Engineering, Yichang, China, 16–18 September 2011; pp. 1913–1916. [Google Scholar] [CrossRef]

- Aurilio, G.; Gallo, D.; Landi, C.; Luiso, M. AC electronic load for on-site calibration of energy meters. In Proceedings of the 2013 IEEE International Instrumentation and Measurement Technology Conference (I2MTC), Minneapolis, MN, USA, 6–9 May 2013; pp. 768–773. [Google Scholar] [CrossRef]

- Friedli, T.; Kolar, J.W.; Rodriguez, J.; Wheeler, P.W. Comparative Evaluation of Three-Phase AC–AC Matrix Converter and Voltage DC-Link Back-to-Back Converter Systems. IEEE Trans. Ind. Electron. 2012, 59, 4487–4510. [Google Scholar] [CrossRef]

- Li, F.; Zou, Y.P.; Wang, C.Z.; Chen, W.; Zhang, Y.C.; Zhang, J. Research on AC electronic load based on back to back single-phase PWM rectifiers. In Proceedings of the 2008 Twenty-Third Annual IEEE Applied Power Electronics Conference and Exposition, Austin, TX, USA, 24–28 February 2008; pp. 630–634. [Google Scholar] [CrossRef]

- Zheyu, Z.; Yunping, Z.; Zhenxing, W.; Jian, T. Design and research of three-phase power electronic load. In Proceedings of the 2009 IEEE 6th International Power Electronics and Motion Control Conference, Wuhan, China, 17–20 May 2009; pp. 1798–1802. [Google Scholar] [CrossRef]

- Jeong, I.W.; Slepchenkov, M.; Smedley, K.; Maddaleno, F. Regenerative AC Electronic Load with One-Cycle Control. In Proceedings of the 2010 Twenty-Fifth Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Palm Springs, CA, USA, 21–25 February 2010; pp. 1166–1171. [Google Scholar] [CrossRef]

- Li, F.; Zou, X.; Wang, C.Z.; Chen, W. Research on AC electronic load for testing ac power based on dual single-phase PWM converter. High Volt. Eng. 2008, 34, 930–934. [Google Scholar]

- Valdez, J.E.; Mayo, J.C.; Rosas, J.C.; Alejo, A.; Llamas, A. Energy Recycling Three-Phase Experimental Setup for Power Flow Control Devices. IEEE Lat. Am. Trans. 2018, 16, 1337–1342. [Google Scholar] [CrossRef]

- Kehler, L.B.; Corrêa, L.C.; Ribeiro, C.G.; Trapp, J.G.; Lenz, J.M.; Farret, F.A. Electronically adjustable load for testing three phase ac systems. In Proceedings of the 2013 Brazilian Power Electronics Conference, Gramado, Brazil, 27–31 October 2013; pp. 1082–1087. [Google Scholar]

- Novak, D.; Beraki, M.; Villa, G.; García, P. Low-cost programmable three phase load for microgrids labs. In Proceedings of the 2015 IEEE 15th International Conference on Environment and Electrical Engineering (EEEIC), Rome, Italy, 10–13 June 2015; pp. 599–604. [Google Scholar]

- Serna-Montoya, L.F.; Buitrago-Lopez, L.A.; Cano-Quintero, J.B.; Muñoz-Galeano, N.; López-Lezama, J.M. Modeling and Simulation of Buck Converters and their Applications in DC Microgrids. Iaeng Int. J. Comput. Sci. 2021, 48, 804–814. [Google Scholar]

- Urrea-Quintero, J.H.; Muñoz-Galeano, N.; López-Lezama, J.M. Robust Control of Shunt Active Power Filters: A Dynamical Model-Based Approach with Verified Controllability. Energies 2020, 13, 6253. [Google Scholar] [CrossRef]

| Parameters | Value | |

|---|---|---|

| External d-loop | 0.026 | |

| 0.015 | ||

| Inner d-loop | 0.1 | |

| 0.0008 | ||

| q-loop | 0.108069 | |

| 0.0008 |

| Parameters | Value |

|---|---|

| 0.074532 | |

| 0.32 |

| Parameters | Symbol | Value |

|---|---|---|

| Inductances | 23.7 mH | |

| 23.7 mH | ||

| 23.7 mH | ||

| 23.7 mH | ||

| Capacitances | 4400 uF | |

| 2700 uF | ||

| Resistances | 30 k | |

| 114 | ||

| PEL | 208 V | |

| PEL apparent power | 1.8 kVA | |

| DC bus voltage | 60 V | |

| Oscilloscope |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Serna-Motoya, L.F.; Ortiz-Castrillón, J.R.; Gil-Vargas, P.A.; Muñoz-Galeano, N.; Cano-Quintero, J.B.; López-Lezama, J.M. Implementation of a Programmable Electronic Load for Equipment Testing. Computers 2022, 11, 106. https://doi.org/10.3390/computers11070106

Serna-Motoya LF, Ortiz-Castrillón JR, Gil-Vargas PA, Muñoz-Galeano N, Cano-Quintero JB, López-Lezama JM. Implementation of a Programmable Electronic Load for Equipment Testing. Computers. 2022; 11(7):106. https://doi.org/10.3390/computers11070106

Chicago/Turabian StyleSerna-Motoya, León Felipe, José R. Ortiz-Castrillón, Paula Andrea Gil-Vargas, Nicolás Muñoz-Galeano, Juan Bernardo Cano-Quintero, and Jesús M. López-Lezama. 2022. "Implementation of a Programmable Electronic Load for Equipment Testing" Computers 11, no. 7: 106. https://doi.org/10.3390/computers11070106

APA StyleSerna-Motoya, L. F., Ortiz-Castrillón, J. R., Gil-Vargas, P. A., Muñoz-Galeano, N., Cano-Quintero, J. B., & López-Lezama, J. M. (2022). Implementation of a Programmable Electronic Load for Equipment Testing. Computers, 11(7), 106. https://doi.org/10.3390/computers11070106