Hardware Accelerators for Cardiovascular Signal Processing: A System-on-Chip Perspective

Abstract

1. Introduction

2. Context and Background

2.1. Cardiovascular Signals and Processing Challenges

2.2. Hardware Accelerators for Signal Processing: FPGAs and ASICs

2.3. Key Algorithms and Accelerator Functions

2.3.1. Denoising

2.3.2. Feature Extraction

2.3.3. Machine Learning for Decision Support

2.4. Benchmarking and Databases

- MIT–BIH Arrhythmia Database: 48 half-hour ECG recordings (360 Hz) for arrhythmia classification [33].

- PTB Diagnostic Database: 549 high-resolution ECG records (1000 Hz) for myocardial infarction detection [34].

- PPG-BP Database: 657 synchronised PPG and blood pressure traces for hypertension analysis [35].

3. Hardware Accelerators for Cardiovascular Signal Processing

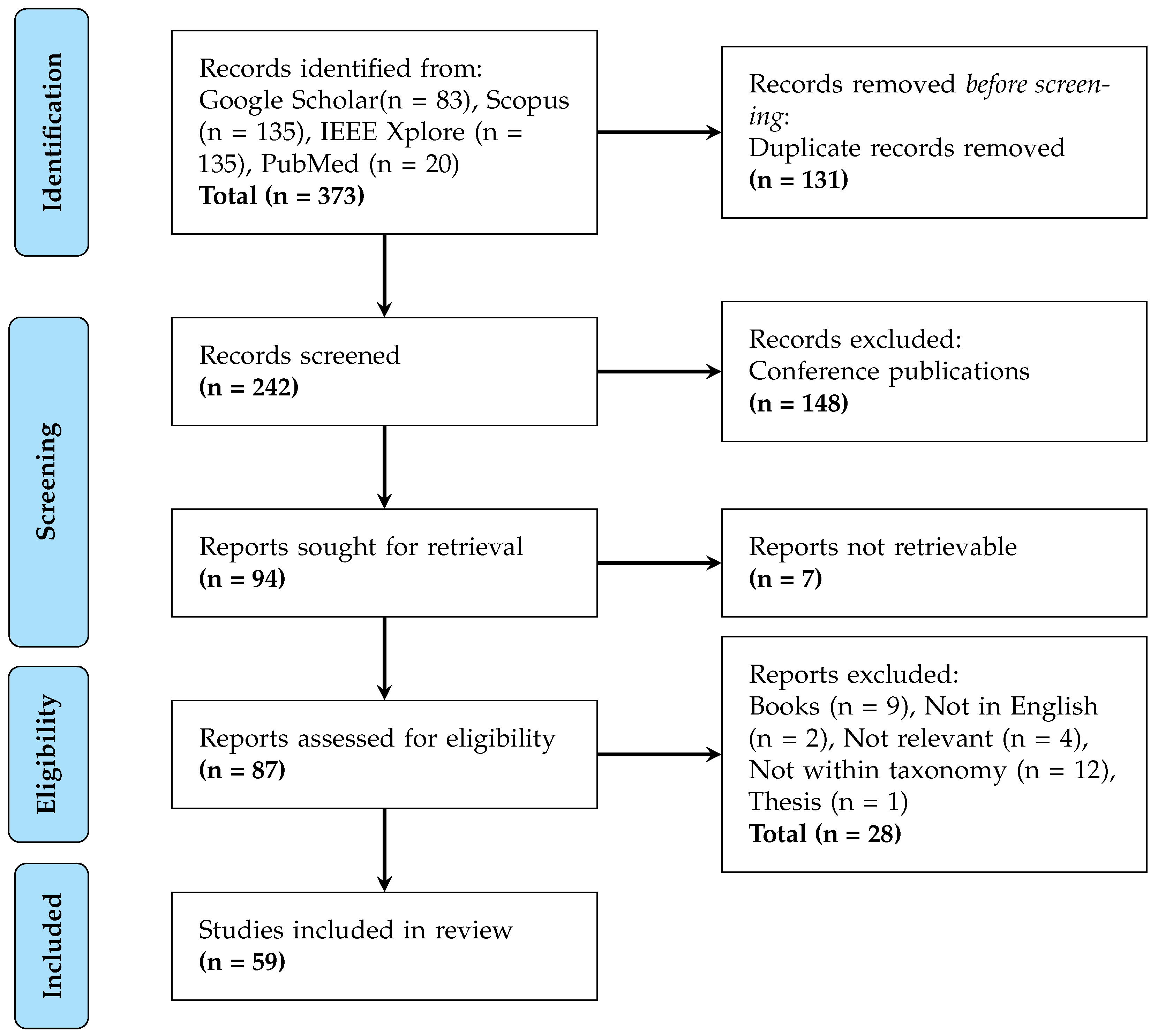

3.1. Systematic Literature Review Protocol

3.2. Taxonomic Classification and Comparative Framework

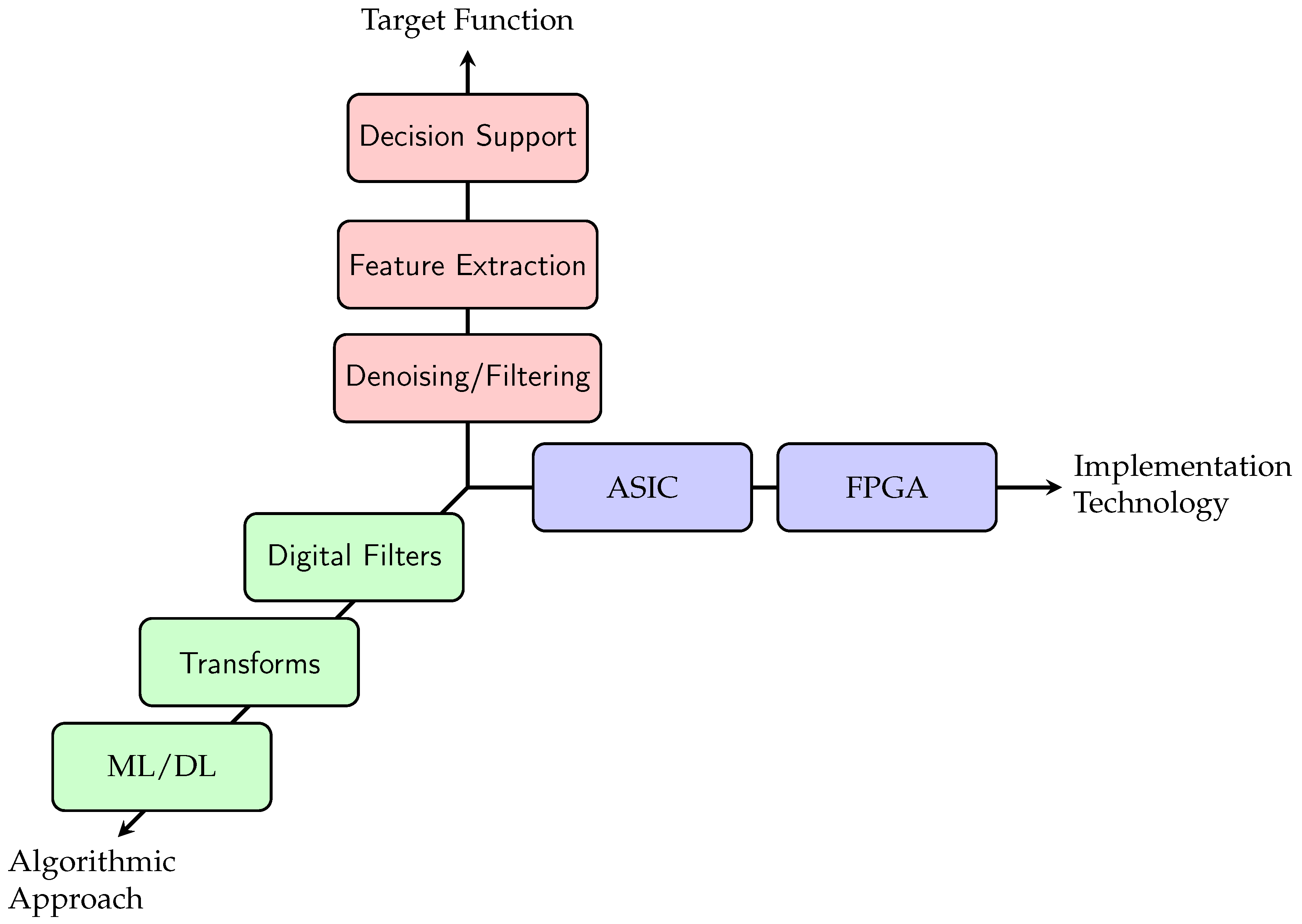

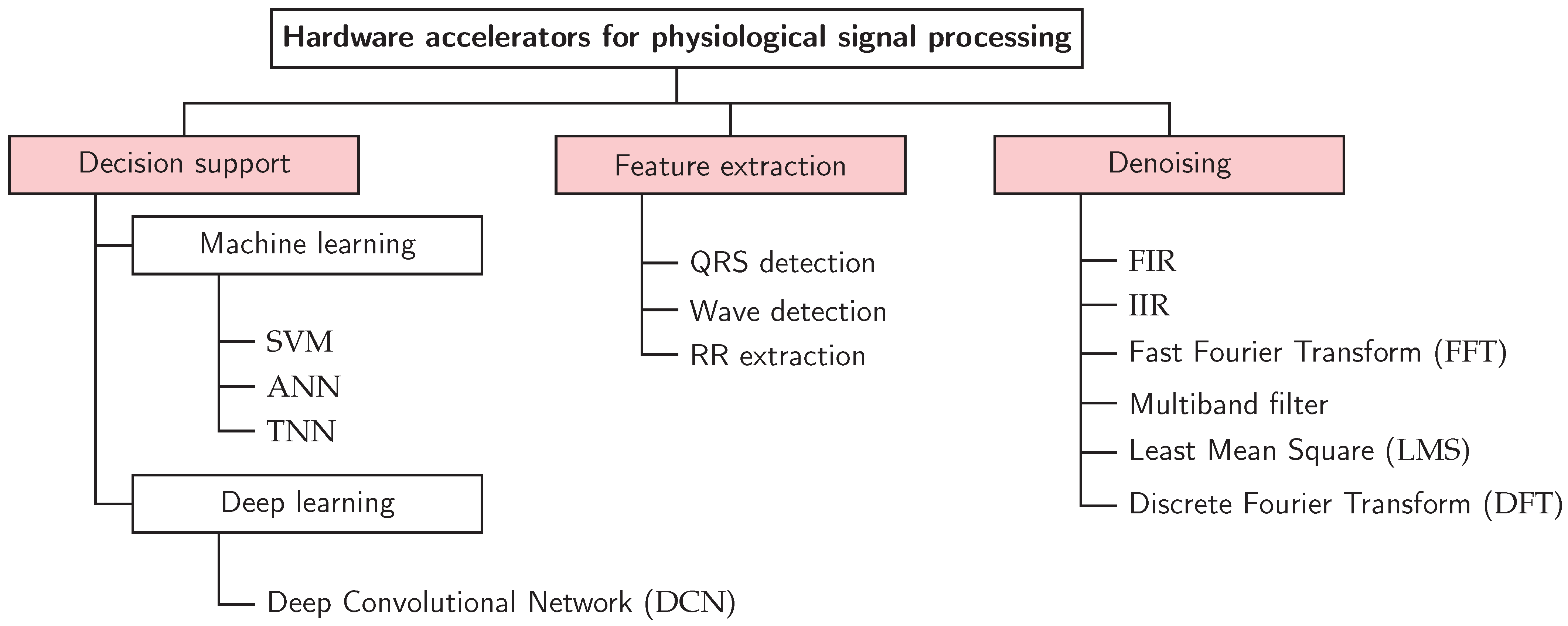

3.2.1. Taxonomic Axes

Target Function

- Denoising and Filtering: The initial signal conditioning stage, focused on removing noise and artifacts to improve signal quality.

- Feature Extraction: The process of identifying and isolating clinically relevant features from the cleaned signal.

- Decision Support: The highest-level function, involving the classification of signals or extracted features to support diagnostic decisions.

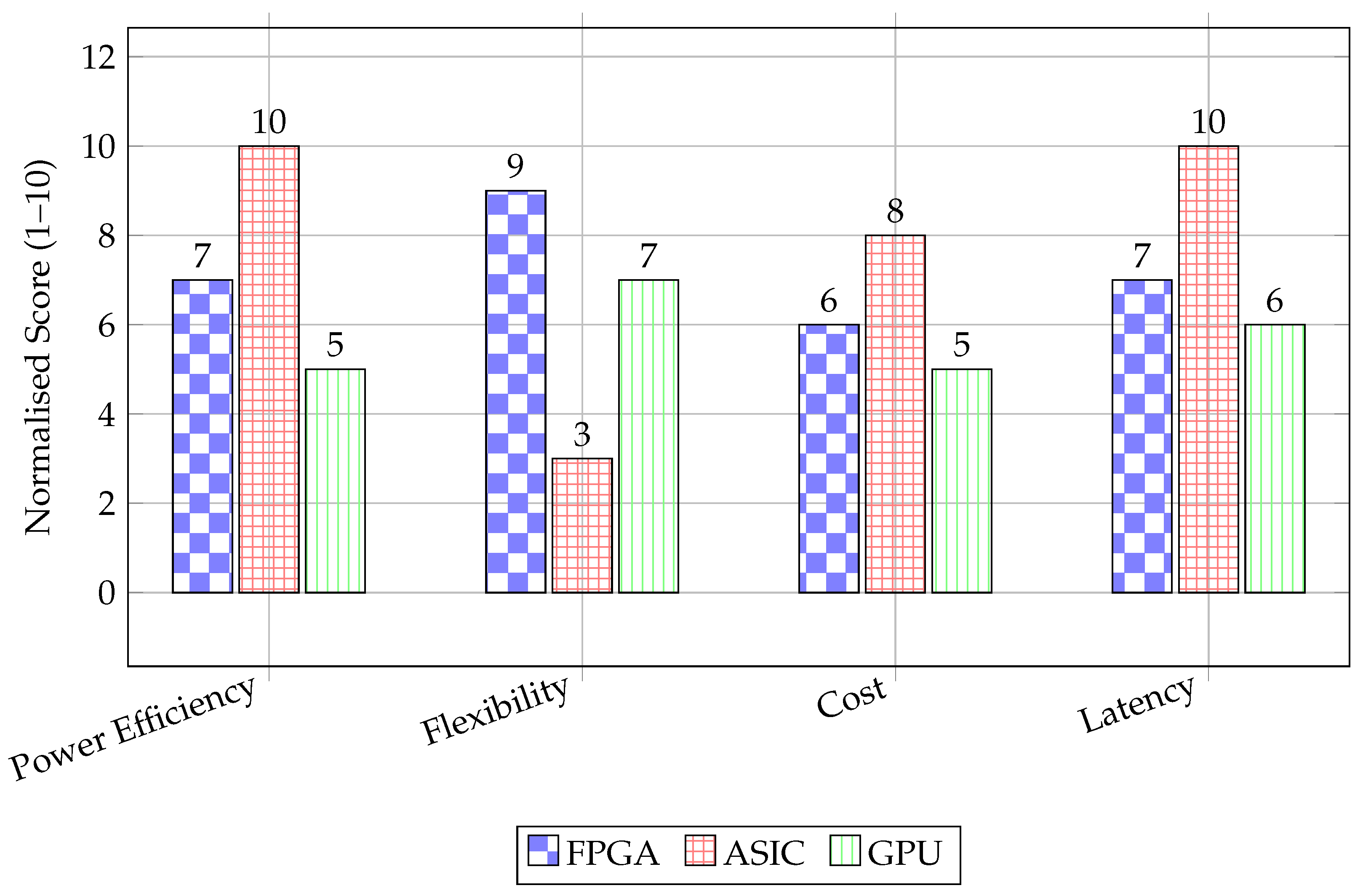

Implementation Technology

- FPGA: Field-Programmable Gate Arrays offer reconfigurability and high parallelism, making them ideal for prototyping and research.

- ASIC: Application-Specific Integrated Circuits provide the highest performance and lowest power consumption for a fixed function, making them suitable for mass-produced devices.

Algorithmic Approach

- Digital Filters: Includes finite/infinite impulse response (FIR/IIR) filters and adaptive filters (e.g., LMS).

- Transform-Based Methods: Includes methods like the DFT with its efficient form known as the FFT and Wavelet transforms.

- ML and DL: Encompasses models ranging from traditional classifiers like SVMs to deep learning architectures like CNNs and DCNs.

3.2.2. Comparative Analysis Framework

- Hardware-Centric Metrics: These metrics evaluate the physical efficiency and performance of the accelerator implementation.

- –

- Power Consumption (mW): Critical for wearable and implantable devices.

- –

- Area Efficiency (gate count or mm2): Measures the silicon footprint, which is directly related to cost.

- –

- Throughput (samples/s or inferences/s): Determines the capability for real-time processing.

- Algorithm-Centric Metrics: These metrics evaluate the clinical efficacy and quality of the processing output. The specific metric is tied to the Target Function of the accelerator.

- –

- Denoising: Noise suppression ratio (dB) and Percentage Root-mean-square Difference (Percentage Root mean square Difference (PRD)).

- –

- Feature Extraction/Decision Support: Clinical accuracy (F1-score, sensitivity and specificity), benchmarked against gold-standard databases (MIT–BIH, PTB and PPG-BP).

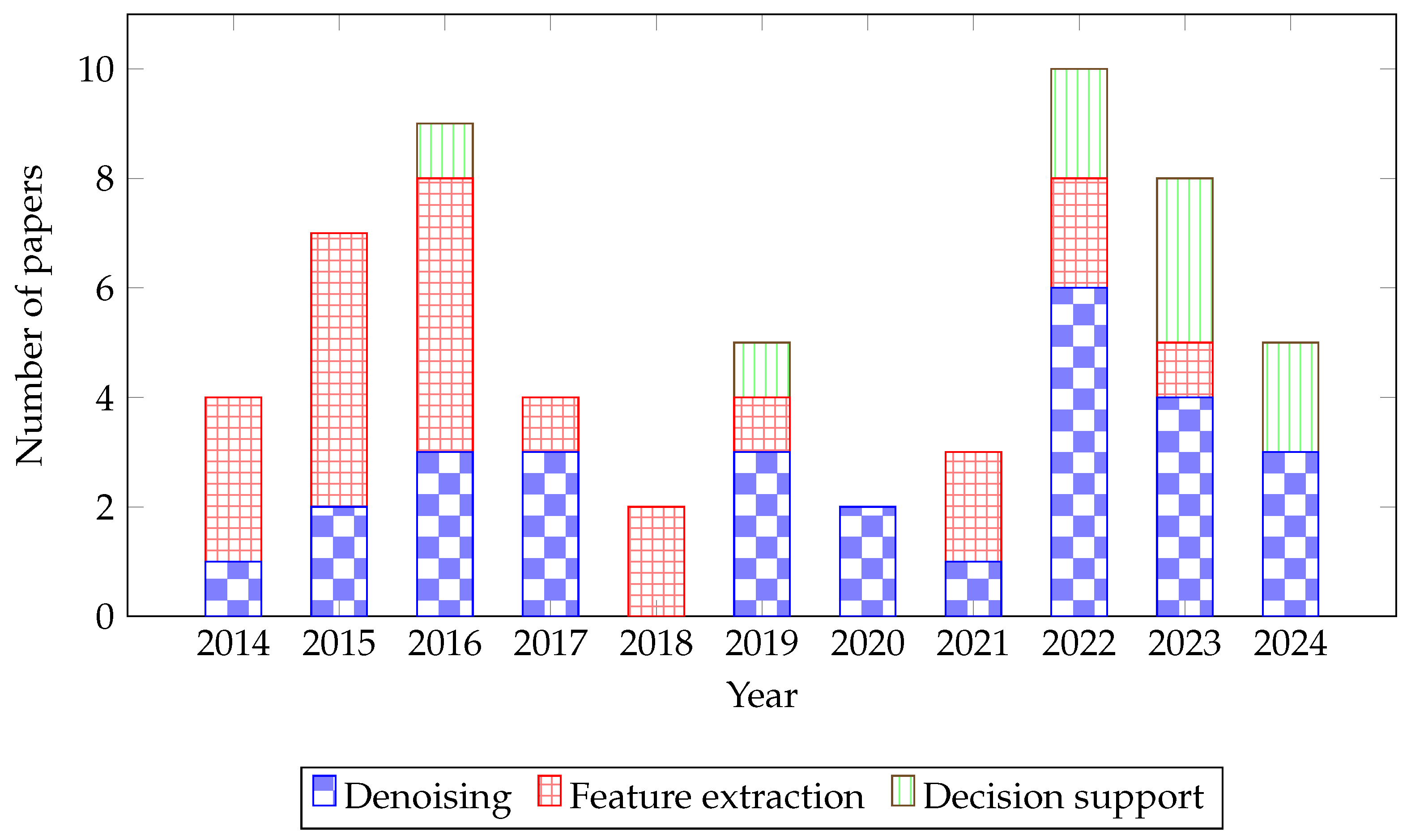

4. Results

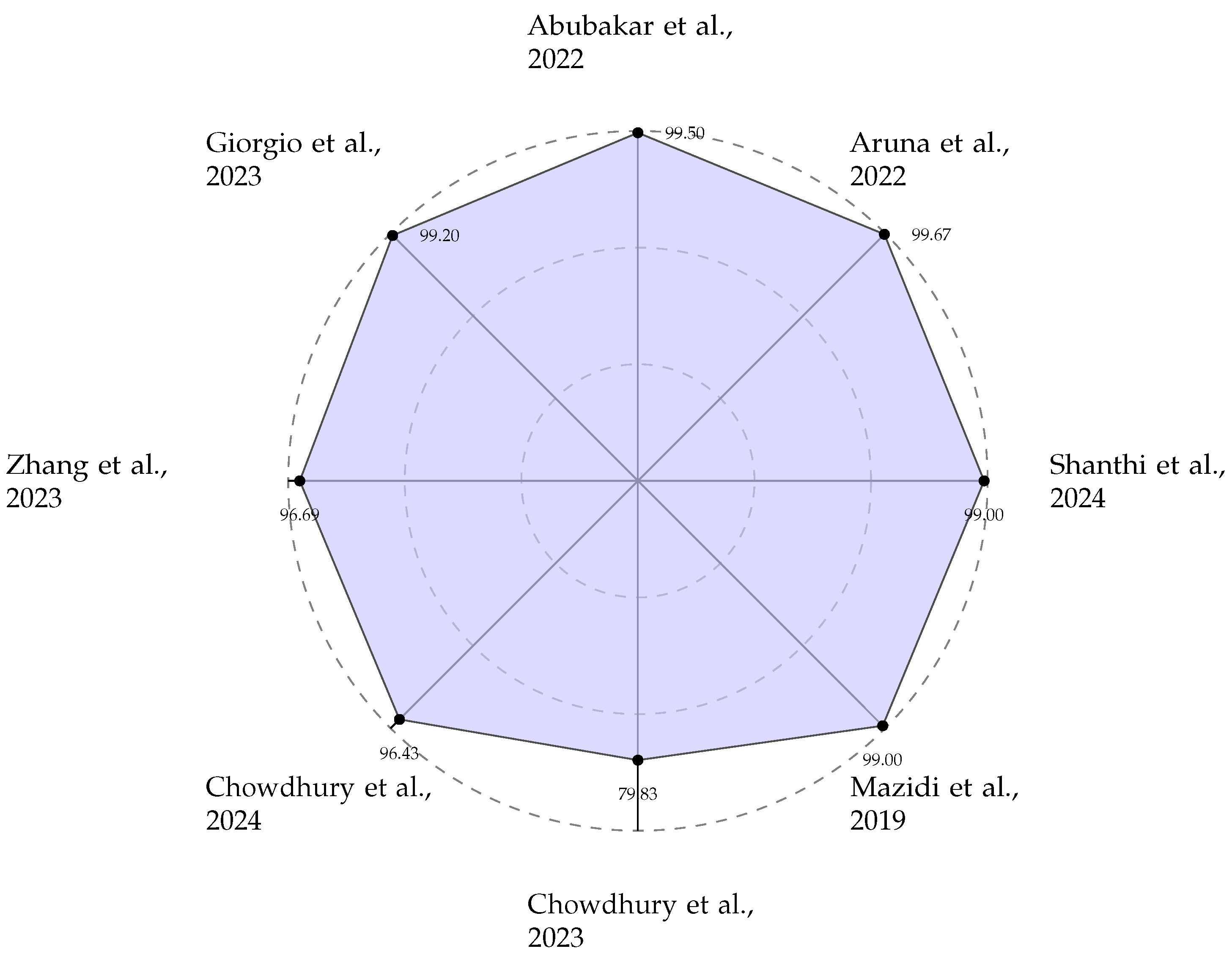

4.1. Decision Support Systems

4.2. Feature Extraction Accelerators

4.3. Denoising and Filtering Functionality

5. Discussion

5.1. Synthesis of Taxonomic Findings

5.2. The State of Deep Learning in Hardware Accelerators

5.3. Limitations and Challenges

5.4. Latency Considerations for Clinical Relevance

5.5. Future Directions

5.6. Integration into Commercial SoC Platforms

5.7. Bridging the DL-to-Hardware Gap: Model Optimisation Techniques

6. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

Abbreviations

| AF | Atrial Fibrillation |

| ANN | Artificial Neural Network |

| AI | Artificial Intelligence |

| ASIC | Application Specific Integrated Circuit |

| DL | Deep Learning |

| CLB | Configurable Logic Block |

| CNN | Convolutional Neural Network |

| CR | Compression Ratio |

| CVD | Cardiovascular Disease |

| DCN | Deep Convolutional Network |

| DFT | Discrete Fourier Transform |

| DSP | Digital Signal Processing |

| ECG | Electrocardiogram |

| FF | Flip Flop |

| FFT | Fast Fourier Transform |

| FIR | Finite Impulse Response |

| FPGA | Field Programmable Gate Array |

| GPU | Graphics Processing Unit |

| HRV | Heart Rate Variability |

| IoT | Internet of Things |

| IIR | Infinite Impulse Response |

| LMS | Least Mean Square |

| LUT | Lookup Table |

| ML | Machine Learning |

| MPU | Microprocessing Unit |

| PPG | Photoplethysmogram |

| PRISMA | Preferred Reporting Items for Systematic Reviews and Meta-Analyses |

| PRD | Percentage Root mean square Difference |

| RNN | Recurrent Neural Network |

| SNRimp | Single Noise Reservoir Improvement |

| SoC | System-on-Chip |

| SVM | Support Vector Machine |

| TNN | Ternary Neural Network |

| AUC | Area Under the Curve |

Appendix A. Benchmark Databases

| Database Name | Records Numbers | Duration | Sampling Rate | Meta Data |

|---|---|---|---|---|

| MIT–BIH Arrhythmia Database [33] | 48 ECG records. | 30 min per record. | 360 Hz. | The data consists of 47 human subjects: 25 men aged 32 to 89 years, and 22 women aged 23 to 89 years. |

| MIT–BIH Noise Stress Test Database [80] | 12 ECG records and 3 records of noise. | 30 min per record. | 360 Hz. | The data consists of 2 clean recordings (118 and 119) from the MIT–BIH Arrhythmia database. |

| MIT–BIH Normal Sinus Rhythm Database [81] | 18 long-term ECG records. | 10 min per record. | 128 Hz. | The data consists of 5 men aged 26 to 45, and 13 women aged 20 to 50 years. It is widely used in ECG signal analysis as well as in training various ML algorithms for heartbeat analysis. |

| PTB Diagnostic Database [34] | 549 ECG records. | 10 min per record. | 1000 Hz. | The data consists of 294 human subjects including healthy subjects and patients with a variety of heart diseases. The data consists of 209 men aged 17 to 87 years and 81 women with a mean age of 61.6 years. It is widely used in cardiac disease diagnosis and abnormality classification. |

| PPG-BP Database [35] | 657 records with PPG and blood pressure. | 2.1 s per record. | 125 Hz for PPG and 1000 Hz for blood pressure. | The data consists of 219 adults, 104 men and 115 women, aged 21 to 86 years. Widely used for hypertension detection and blood pressure prediction as well as cardiovascular disease analysis. |

| CSE ECG Database [82] | 1000 ECG records. | 8 to 10 s per record. | 500 Hz. | Widely used for arrhythmia detection and cardiovascular disease diagnosis. |

| AF Termination Challenge Database [83] | 60 ECG records. | 60 s per record. | 128 Hz. | Widely used for the analysis of AF termination during cardioversion. |

| QT Database [84] | 105 ECG records. | 15 min per record. | 250 Hz. | The data consists of ECG signals from the MIT–BIH Arrhythmia Database and several other ECG databases. Widely used in analysing QT intervals for arrhythmia prediction. |

| ECG-ID Database [85] | 310 ECG records. | 20 s per record. | 500 Hz. | The data consists of 90 volunteers, 44 men and 46 women aged from 13 to 75 years. Widely used for biometric human identification based on ECG. |

Appendix B. Search Terms

| Database | Search Strategy |

|---|---|

| Google Scholar through Publish or Perish. | ("Title words":FPGA AND ECG) OR ("Title words":Field Programmable Gate Array AND Electrocardiogram) OR ("Title words":FPGA AND Electrocardiogram) OR ("Title words":Field Programmable Gate Array AND ECG) OR ("Title words":FPGA AND PPG) OR ("Title words":Field Programmable Gate array AND Photoplethysmography) OR ("Title words":FPGA AND Photoplethysmography) OR ("Title words":Field Programmable Gate array AND PPG) OR ("Title words":ASIC AND ECG) OR ("Title words":Application Specific Integrated Circuit AND Electrocardiogram) OR ("Title words":ASIC AND Electrocardiogram) OR ("Title words":Application Specific Integrated Circuit AND ECG) OR ("Title words":ASIC AND PPG) OR ("Title words":Application Specific Integrated Circuit AND Photoplethysmography) OR ("Title words":ASIC AND Photoplethysmography) OR ("Title words":Application Specific Integrated Circuit AND PPG) |

| Scopus. | ("Article title":FPGA AND ECG) OR ("Article title":Field Programmable Gate Array AND Electrocardiogram) OR ("Article title":FPGA AND Electrocardiogram) OR ("Article title":Field Programmable Gate Array AND ECG) OR ("Article title":FPGA AND PPG) OR ("Article title":Field Programmable Gate array AND Photoplethysmography) OR ("Article title":FPGA AND Photoplethysmography) OR ("Article title":Field Programmable Gate array AND PPG) OR ("Article title":ASIC AND ECG) OR ("Article title":Application Specific Integrated Circuit AND Electrocardiogram) OR ("Article title":ASIC AND Electrocardiogram) OR ("Article title":Application Specific Integrated Circuit AND ECG) OR ("Article title":ASIC AND PPG) OR ("Article title":Application Specific Integrated Circuit AND Photoplethysmography) OR ("Article title":ASIC AND Photoplethysmography) OR ("Article title":Application Specific Integrated Circuit AND PPG) |

| PubMed. | (ti =FPGA AND ECG) OR (ti =Field Programmable Gate Array AND Electrocardiogram) OR (ti =FPGA AND Electrocardiogram) OR (ti =Field Programmable Gate Array AND ECG) OR (ti =FPGA AND PPG) OR (ti =Field Programmable Gate array AND Photoplethysmography) OR (ti =FPGA AND Photoplethysmography) OR (ti =Field Programmable Gate array AND PPG) OR (ti =ASIC AND ECG) OR (ti =Application Specific Integrated Circuit AND Electrocardiogram) OR (ti =ASIC AND Electrocardiogram) OR (ti =Application Specific Integrated Circuit AND ECG) OR (ti =ASIC AND PPG) OR (ti =Application Specific Integrated Circuit AND Photoplethysmography) OR (ti =ASIC AND Photoplethysmography) OR (ti =Application Specific Integrated Circuit AND PPG) |

| IEEE Xplore. | ("Document title":FPGA AND ECG) OR ("Document title":Field Programmable Gate Array AND Electrocardiogram) OR ("Document title":FPGA AND Electrocardiogram) OR ("Document title":Field Programmable Gate Array AND ECG) OR ("Document title":FPGA AND PPG) OR ("Document title":Field Programmable Gate array AND Photoplethysmography) OR ("Document title":FPGA AND Photoplethysmography) OR ("Document title":Field Programmable Gate array AND PPG) OR ("Document title":ASIC AND ECG OR ("Document title":Application Specific Integrated Circuit AND Electrocardiogram) OR ("Document title":ASIC AND Electrocardiogram) OR ("Document title":Application Specific Integrated Circuit AND ECG) OR ("Document title":ASIC AND PPG) OR ("Document title":Application Specific Integrated Circuit AND Photoplethysmography) OR ("Document title":ASIC AND Photoplethysmography) OR ("Document title":Application Specific Integrated Circuit AND PPG) |

References

- Paul, L.; Das, P.K.; Rahaman, A.T.; Nizamuddin, H.M.; Aushe, K.J. The silent Killer in your pantry-How sodium overload contributes to cardiovascular diseases. IOSR J. Dent. Med Sci. 2025, 24, 63–68. [Google Scholar] [CrossRef]

- Angell, S.Y.; McConnell, M.V.; Anderson, C.A.; Bibbins-Domingo, K.; Boyle, D.S.; Capewell, S.; Ezzati, M.; De Ferranti, S.; Gaskin, D.J.; Goetzel, R.Z.; et al. The American Heart Association 2030 impact goal: A presidential advisory from the American Heart Association. Circulation 2020, 141, e120–e138. [Google Scholar] [CrossRef]

- de Araújo, J.M.; Eufrosino de Alencar Rodrigues, R.; da Costa Pereira de Arruda Neta, A.; Leite Lima Ferreira, F.E.; Lira Formiga Cavalcanti de Lima, R.; Pinheiro de Toledo Vianna, R.; Vasconcelos Leitão Moreira, L.; Moreira da Silva Neto, J.; Moreira, P.V.L. The direct and indirect costs of cardiovascular diseases in Brazil. PLoS ONE 2022, 17, e0278891. [Google Scholar] [CrossRef]

- Rwebembera, J.; Marangou, J.; Mwita, J.C.; Mocumbi, A.O.; Mota, C.; Okello, E.; Nascimento, B.; Thorup, L.; Beaton, A.; Kado, J. 2023 World Heart Federation guidelines for the echocardiographic diagnosis of rheumatic heart disease. Nat. Rev. Cardiol. 2024, 21, 250–263. [Google Scholar] [CrossRef]

- Faust, O.; Hong, W.; Loh, H.W.; Xu, S.; Tan, R.S.; Chakraborty, S.; Barua, P.D.; Molinari, F.; Acharya, U.R. Heart rate variability for medical decision support systems: A review. Comput. Biol. Med. 2022, 145, 105407. [Google Scholar] [CrossRef] [PubMed]

- Fukumoto, Y. Lifestyle intervention for primary prevention of cardiovascular diseases. Eur. J. Prev. Cardiol. 2022, 29, 2250–2251. [Google Scholar] [CrossRef]

- Abo-Zahhad, M.; Zakaria, A.A.; Abozeid, A.M.; Abo-Zahhad, M.M. A Real-Time Health Monitoring System for Remote Cardiac Patients. In Proceedings of the 2023 11th International Japan-Africa Conference on Electronics, Communications, and Computations (JAC-ECC), Alexandria, Egypt, 18–19 December 2023; IEEE: New York, NY, USA, 2023; pp. 110–114. [Google Scholar]

- Mishra, B.; Arora, N.; Vora, Y. An ECG-PPG wearable device for real time detection of various arrhythmic cardiovascular diseases. In Proceedings of the 2019 9th International Symposium on Embedded Computing and System Design (ISED), Kollam, India, 13–14 December 2019; IEEE: New York, NY, USA, 2019; pp. 1–5. [Google Scholar]

- Giorgio, A.; Guaragnella, C.; Rizzi, M. FPGA-based decision support system for ECG analysis. J. Low Power Electron. Appl. 2023, 13, 6. [Google Scholar] [CrossRef]

- Tsoutsouras, V.; Koliogeorgi, K.; Xydis, S.; Soudris, D. HLS code transformation strategies and directives exploration for FPGA accelerated ECG analysis. In Proceedings of the Workshop in Reconfigurable Computing, Prague, Czech Republic, 21 February 2016; Springer: Berlin/Heidelberg, Germany, 2016. [Google Scholar]

- Uttraphan, C.; Ardani, M.I.A.; Heng, C.W.; Ahmad, N.; Ching, K.B.; Raj, A.A.E. Hardware Implementation of FIR Filter for ECG Signal Processing: Design, Optimization, and Performance Analysis on an FPGA. J. Adv. Res. Appl. Sci. Eng. Technol. 2024, 40, 50–61. [Google Scholar] [CrossRef]

- Wang, X.; Zhu, Y.; Ha, Y.; Qiu, M.; Huang, T. An FPGA-based cloud system for massive ECG data analysis. IEEE Trans. Circuits Syst. II Express Briefs 2016, 64, 309–313. [Google Scholar] [CrossRef]

- Lee, D.; Lee, S.; Oh, S.; Park, D. Energy-efficient FPGA accelerator with fidelity-controllable sliding-region signal processing unit for abnormal ECG diagnosis on IoT edge devices. IEEE Access 2021, 9, 122789–122800. [Google Scholar] [CrossRef]

- Goldberger, A.L.; Goldberger, Z.D.; Shvilkin, A. Goldberger’s Clinical Electrocardiography-E-Book: A Simplified Approach; Elsevier Health Sciences: Amsterdam, The Netherlands, 2023. [Google Scholar]

- Karataş, F.; Koyuncu, I.; Tuna, M.; Alçın, M.; Avcioglu, E.; Akgul, A. Design and implementation of arrhythmic ECG signals for biomedical engineering applications on FPGA. Eur. Phys. J. Spec. Top. 2022, 231, 869–884. [Google Scholar] [CrossRef]

- Luo, D.Y.; Zhang, Z.W.; Sibomana, O.; Izere, S. Comparison of diagnostic accuracy of electrocardiogram-based versus photoplethysmography-based smartwatches for atrial fibrillation detection: A Systematic Review and Meta-Analysis. Ann. Med. Surg. 2025, 87, 2307–2323. [Google Scholar] [CrossRef]

- Whelton, P.K.; Williams, B. The 2018 European society of cardiology/European society of hypertension and 2017 American college of cardiology/American heart association blood pressure guidelines: More similar than different. JAMA 2018, 320, 1749–1750. [Google Scholar] [CrossRef]

- Aruna, V.B.K.L.; Chitra, E.; Padmaja, M. Accelerating deep convolutional neural network on FPGA for ECG signal classification. Microprocess. Microsyst. 2023, 103, 104939. [Google Scholar] [CrossRef]

- Khan, M.I.; da Silva, B. Harnessing FPGA technology for energy-efficient wearable medical devices. Electronics 2024, 13, 4094. [Google Scholar] [CrossRef]

- Chandrasekaran, S.; Chandran, S.; Selvam, I.J. FPGA-Based Implementation of Real-Time Cardiologist-Level Arrhythmia Detection and Classification in Electrocardiograms Using Novel Deep Learning. Int. J. Circuit Theory Appl. 2025, 53, 3662–3683. [Google Scholar] [CrossRef]

- Jayashree, S.; Sakthivel, S.M. FPGA implementation of optimized FIR filter for ECG denoising using peresreversible logic gate. J. Theor. Appl. Inf. Technol. 2022, 100, 4582–4594. [Google Scholar]

- Abubakar, S.M.; Yin, Y.; Tan, S.; Jiang, H.; Wang, Z. A 746 nW ECG processor ASIC based on ternary neural network. IEEE Trans. Biomed. Circuits Syst. 2022, 16, 703–713. [Google Scholar] [CrossRef] [PubMed]

- Zhang, C.; Chang, J.; Guan, Y.; Li, Q.; Wang, X.; Zhang, X. A Low-Power ECG Processor ASIC Based on an Artificial Neural Network for Arrhythmia Detection. Appl. Sci. 2023, 13, 9591. [Google Scholar] [CrossRef]

- Monmasson, E.; Idkhajine, L.; Cirstea, M.N.; Bahri, I.; Tisan, A.; Naouar, M.W. FPGAs in industrial control applications. IEEE Trans. Ind. Inform. 2011, 7, 224–243. [Google Scholar] [CrossRef]

- Monmasson, E.; Hilairet, M.; Spagnuolo, G.; Cirstea, M.N. System-on-chip FPGA devices for complex electrical energy systems control. IEEE Ind. Electron. Mag. 2021, 16, 53–64. [Google Scholar] [CrossRef]

- Cirstea, M.; Benkrid, K.; Dinu, A.; Ghiriti, R.; Petreus, D. Digital electronic system-on-chip design: Methodologies, tools, evolution, and trends. Micromachines 2024, 15, 247. [Google Scholar] [CrossRef]

- Dinu, A.; Cirstea, M.N.; Cirstea, S.E. Direct neural-network hardware-implementation algorithm. IEEE Trans. Ind. Electron. 2009, 57, 1845–1848. [Google Scholar] [CrossRef]

- Alhelal, D.; Aboalayon, K.A.; Daneshzand, M.; Faezipour, M. FPGA-based denoising and beat detection of the ECG signal. In Proceedings of the 2015 Long Island Systems, Applications and Technology, Farmingdale, NY, USA, 1 May 2015; IEEE: New York, NY, USA, 2015; pp. 1–5. [Google Scholar]

- Saha, S.; Mandal, S.B. FPGA implementation of IIR elliptic filters for de-noising ECG signal. Biomed. Signal Process. Control 2024, 96, 106544. [Google Scholar] [CrossRef]

- hadi Mazidi, M.; Eshghib, M.; reza Raoufyc, M. FPGA implementation of wearable ECG system for detection premature ventricular contraction. Int. J. COMADEM 2019, 22, 51–59. [Google Scholar]

- Chowdhury, A.; Chowdhury, M.H.; Das, D.; Ghosh, S.; Cheung, R.C.C. FPGA Implementation of PPG-Based Cardiovascular Diseases and Diabetes Classification Algorithm. Arab. J. Sci. Eng. 2024, 49, 16697–16709. [Google Scholar] [CrossRef]

- Shanthi, K.G.; Kinol, A.; Joy, M.; Santhi, S.; Kannan, K. Real-time FPGA Integration for ECG Monitoring: Bidirectional Recurrent Chimp Search Model. IETE J. Res. 2024, 70, 6848–6863. [Google Scholar] [CrossRef]

- Moody, G.B.; Mark, R.G. The impact of the MIT–BIH arrhythmia database. IEEE Eng. Med. Biol. Mag. 2001, 20, 45–50. [Google Scholar] [CrossRef]

- Tsai, T.H.; Tsai, F.L. Efficient lossless compression scheme for multi-channel ECG signal processing. Biomed. Signal Process. Control 2020, 59, 101879. [Google Scholar] [CrossRef]

- Liang, Y.; Chen, Z.; Liu, G.; Elgendi, M. A new, short-recorded photoplethysmogram dataset for blood pressure monitoring in China. Sci. Data 2018, 5, 180020. [Google Scholar] [CrossRef]

- Chowdhury, A.; Das, D.; Hasan, K.; Cheung, R.C.C.; Chowdhury, M.H. An FPGA implementation of multiclass disease detection from PPG. IEEE Sens. Lett. 2023, 7, 6007604. [Google Scholar] [CrossRef]

- Pamula, V.R.; Valero-Sarmiento, J.M.; Yan, L.; Bozkurt, A.; Van Hoof, C.; Van Helleputte, N.; Yazicioglu, R.F.; Verhelst, M. A 172 μW/Compressively Sampled Photoplethysmographic (PPG) Readout ASIC with Heart Rate Estimation Directly From Compressively Sampled Data. IEEE Trans. Biomed. Circuits Syst. 2017, 11, 487–496. [Google Scholar] [CrossRef]

- Matsumoto, Y.; Tanaka, T.; Sonoda, K.; Kanda, K.; Fujita, T.; Maenaka, K. Low-Power ECG Processing ASIC. Electron. Commun. Jpn. 2016, 99, 13–20. [Google Scholar] [CrossRef]

- Habiboullah, A.; Terosiet, M.; Histace, A.; Romain, O. Improvement of a FPGA-based Detection of QRS Complexes in ECG Signal using an Adaptive Windowing Strategy. In Proceedings of the BIOSIGNALS, Rome, Italy, 21–23 February 2016; pp. 327–332. [Google Scholar]

- García Limón, J.A.; Martínez-Suárez, F.; Alvarado-Serrano, C. Implementation of wavelet-transform-based algorithms in an FPGA for heart rate and rt interval automatic measurements in real time: Application in a long-term ambulatory electrocardiogram monitor. Micromachines 2023, 14, 1748. [Google Scholar] [CrossRef]

- Roy Chowdhury, S. High-resolution detection of sustained ventricular and supraventricular tachycardia through FPGA-based fuzzy processing of ECG signal. Med Biol. Eng. Comput. 2015, 53, 1037–1047. [Google Scholar] [CrossRef] [PubMed]

- Aravind Kumar, M.; Manjunatha Chari, K. Efficient FPGA-based VLSI architecture for detecting R-peaks in electrocardiogram signal by combining Shannon energy with Hilbert transform. IET Signal Process. 2018, 12, 748–755. [Google Scholar] [CrossRef]

- Al-Shueli, A.I. Optimized implementation of ECG signal noise cancelation using FIR and IIR filter techniques based on FPGA. Eurasian J. Eng. Technol. 2022, 9, 43–54. [Google Scholar]

- Bodisco, T.; D’Netto, J.; Kelson, N.; Banks, J.; Hayward, R. Computation of ECG signal features using MCMC modelling in software and FPGA reconfigurable hardware. Procedia Comput. Sci. 2014, 29, 2442–2448. [Google Scholar] [CrossRef]

- Abdul-Kadir, N.A.; Safri, N.M.; Othman, M.A. ASIC design of natural frequency of ECG signal for atrial fibrillation detection module using high-level synthesis approach. J. Teknol. 2015, 74. [Google Scholar] [CrossRef]

- Jain, S.K.; Bhaumik, B. An Energy efficient application specific integrated circuit for electrocardiogram feature detection and its potential for ambulatory cardiovascular disease detection. Healthc. Technol. Lett. 2016, 3, 77–84. [Google Scholar] [CrossRef] [PubMed]

- Da He, D.; Sodini, C.G. A 58 nW ECG ASIC with motion-tolerant heartbeat timing extraction for wearable cardiovascular monitoring. IEEE Trans. Biomed. Circuits Syst. 2014, 9, 370–376. [Google Scholar]

- Abburi, R.; Rani, M.A. A Wavelet architecture for Abdominal ECG preprocessing and fetal QRS detection implemented in FPGA using 90nm technology. Int. J. Recent Technol. Eng. 2019, 8, 2762–2768. [Google Scholar] [CrossRef]

- Nagpal, N.; Chawla, M.; Phillips, D. A Simple FPGA Based ECG R Wave Peak Detection System For Heart Rate And Heart Rate Variability Calculation. Int. J. Eng. Res. Appl. 2014, 4, 33–36. [Google Scholar]

- Gu, X.; Zhu, Y.; Zhou, S.; Wang, C.; Qiu, M.; Wang, G. A real-time FPGA-based accelerator for ECG analysis and diagnosis using association-rule mining. ACM Trans. Embed. Comput. Syst. (TECS) 2016, 15, 1–23. [Google Scholar] [CrossRef]

- Desai, M.; Caffarena, G.; Jevtic, R.; Márquez, D.G.; Otero, A. A Low-Latency, Low-Power FPGA Implementation of ECG Signal Characterization Using Hermite Polynomials. Electronics 2021, 10, 2324. [Google Scholar] [CrossRef]

- Ganatra, M.M.; Vithalani, C.H. A novel morphological feature extraction approach for ECG signal analysis based on generalized synchrosqueezing transform, correntropy function and adaptive heuristic framework in FPGA. J. Circuits, Syst. Comput. 2022, 31, 2250312. [Google Scholar] [CrossRef]

- Alouneh, S.; Al-Shayeji, M.; Abed, S.; Samrajesh, M.D.; Sultan, S. FPGA enhanced implementation of ECG QRS complex detection algorithm. Int. J. Circuits Syst. Signal Process 2015, 9, 327–336. [Google Scholar]

- Chatterjee, H.; Mitra, M.; Gupta, R. Real–time detection of electrocardiogram wave features using template matching and implementation in FPGA. Int. J. Biomed. Eng. Technol. 2015, 17, 290–313. [Google Scholar] [CrossRef]

- Noor, S.M.; John, E.; Panday, M. Design and implementation of an ultralow-energy FFT ASIC for processing ECG in cardiac pacemakers. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2018, 27, 983–987. [Google Scholar] [CrossRef]

- Kalamani, C.; Kamatchi, S.; Sasikala, S.; Murali, L. The design and implementation of folded adaptive lattice filter structures in FPGA for ECG signals. Autom. časopis Za Autom. Mjer. Elektron. Računarstvo I Komun. 2023, 64, 772–782. [Google Scholar]

- Reddy, P.V.; Tallapragada, V.V.S. FPGA-enabled lossless ECG signal compression system using an integer adaptive compressor. Analog Integr. Circuits Signal Process. 2024, 119, 331–361. [Google Scholar] [CrossRef]

- Elbedwehy, A.N.; El-Mohandes, A.M.; Elnakib, A.; Abou-Elsoud, M.E. FPGA-based reservoir computing system for ECG denoising. Microprocess. Microsys. 2022, 91, 104549. [Google Scholar] [CrossRef]

- Egila, M.G.; El-Moursy, M.A.; El-Hennawy, A.E.; El-Simary, H.A.; Zaki, A. FPGA-based electrocardiography (ECG) signal analysis system using least-square linear phase finite impulse response (FIR) filter. J. Electr. Syst. Inf. Technol. 2016, 3, 513–526. [Google Scholar] [CrossRef]

- Venkatesan, C.; Karthigaikumar, P.; Varatharajan, R. FPGA implementation of modified error normalized LMS adaptive filter for ECG noise removal. Clust. Comput. 2019, 22, 12233–12241. [Google Scholar] [CrossRef]

- Sohal, H.; Jain, S. FPGA implementation of collateral and sequence pre-processing modules for low power ECG denoising module. Inform. Med. Unlocked 2022, 28, 100838. [Google Scholar]

- Janwadkar, S.; Dhavse, R. ASIC implementation of ECG denoising FIR filter by using hybrid Vedic–Wallace tree multiplier. Int. J. Circuit Theory Appl. 2024, 52, 1621–1646. [Google Scholar] [CrossRef]

- Patel, V.; Shah, A. Denoising of Electrocardiogram Signal using Multiband Filter and its Implementation on FPGA. SJEE 2022, 19, 115–128. [Google Scholar] [CrossRef]

- Aboutabikh, K.; Haidar, I.; Aboukerdah, N. Design and implementation of a digital FIR notch filter for the ECG signals using FPGA. Int. J. Adv. Res. Comput. Commun. Eng. 2016, 5, 452–456. [Google Scholar] [CrossRef]

- Priya, V.A.; Muralidhar, M. Design and Implementation of Digital Adaptive Filter on Spartan-6 FPGA for ECG Signal Processing. Int. J. VLSI Syst. Des. Commun. Syst. 2014, 2, 494–498. [Google Scholar]

- Çancıoğlu, E.; Cancioglu, E.; Çakıroğlu, G.; Cakiroglu, G.; Gökçen, A.; Gokcen, A.; Altanay, Y.S.; Altanay, Y.S. Design and Implementation of Digital Filters for ECG Data Based on Field Programmable Gate Array and MATLAB. Akıllı Sist. Ve Uygulamaları Derg. 2020, 3, 17–19. [Google Scholar]

- Patel, V.; Shah, A. Design and implementation of low power FPGA-based optimal multiband filter with Spline function for denoising ECG signals. Comput. Methods Biomech. Biomed. Eng. 2025, 28, 226–237. [Google Scholar] [CrossRef] [PubMed]

- Anusuya, S.; Samiappan, D.; Buvaneswari, P.R. Design and Implementation of Motion Artifact Reduction Asic for Wearable Ecg Recording. Am.-Eurasian J. Sci. Res. 2015, 10, 154–159. [Google Scholar]

- Gon, A.; Mukherjee, A. Design and FPGA Implementation of an Efficient Architecture for Noise Removal in ECG Signals Using Lifting-Based Wavelet Denoising. In Proceedings of the 2023 11th International Symposium on Electronic Systems Devices and Computing (ESDC), Guwahati, India, 23–24 March 2023; IEEE: New York, NY, USA, 2023; Volume 1, pp. 1–6. [Google Scholar]

- Sakthivel, S.M.; Reddy, O.S. Fault Tolerant FPGA Implementation on Redundancy Techniques and ECG Denoising. arXiv 2023, arXiv:2304.08165. [Google Scholar] [CrossRef]

- Shingne, H.B.; Dhanashri, H.G. FPGA based design and implementation of cascaded FIR filter for ECG signal processing. In Proceedings of the IDES Joint International Conferences on IPC and ARTEE, Bangalore, India, 15–17 December 2017; pp. 1673–1678. [Google Scholar]

- Ganatra, M.M.; Vithalani, C.H. FPGA design of a variable step-size variable tap length denlms filter with hybrid systolic-folding structure and compressor-based booth multiplier for noise reduction in ECG signal. Circuits Syst. Signal Process. 2022, 41, 3592–3622. [Google Scholar] [CrossRef]

- Sohal, H.; Jain, S. FPGA implementation of Power-Efficient ECG pre-processing block. In Lecture Notes in Networks and Systems; Springer: Berlin/Heidelberg, Germany, 2019; Volume 106. [Google Scholar]

- Padmavathi, C.; Veenadevi, S.V. An optimized FPGA based system design for the arrhythmia detection using ECG. Int. J. Innov. Technol. Explor. Eng. (IJITEE) 2019, 9, 2808–2818. [Google Scholar]

- Polat, Ö.; KAYHAN, S. FPGA implementation of LSD-OMP for real-time ECG signal reconstruction. Turk. J. Electr. Eng. Comput. Sci. 2021, 29, 1887–1907. [Google Scholar] [CrossRef]

- Alhelal, D.; Faezipour, M. Denoising and beat detection of ECG signal by Using FPGA. Int. J. High Speed Electron. Syst. 2017, 26, 1740016. [Google Scholar] [CrossRef]

- Sasikala, S.; Murugesan, G.; Gomathi, S. FPGA Implementation of Combination of Error Normalised Sign LMS and Zero Attractor-ENSLMS Algorithms for Denoising ECG Signals. Asian J. Res. Soc. Sci. Humanit. 2016, 6, 683–697. [Google Scholar] [CrossRef]

- Mohanraj, R.; Vimala, R. ECG Signal Denoising with Field-Programmable Gate Array Implementation of Fast Digital Finite Impulse Response and Infinite Impulse Response Filters. J. Med. Imaging Health Inform. 2020, 10, 81–85. [Google Scholar] [CrossRef]

- Faust, O.; Hagiwara, Y.; Hong, T.J.; Lih, O.S.; Acharya, U.R. Deep learning for healthcare applications based on physiological signals: A review. Comput. Methods Programs Biomed. 2018, 161, 1–13. [Google Scholar] [CrossRef]

- Moody, G.; Muldrow, W.; Mark, R. The MIT–BIH noise stress test database. Comput. Cardiol. 1984, 11, 381–384. [Google Scholar]

- Goldberger, A.L.; Amaral, L.A.; Glass, L.; Hausdorff, J.M.; Ivanov, P.C.; Mark, R.G.; Mietus, J.E.; Moody, G.B.; Peng, C.K.; Stanley, H.E. PhysioBank, PhysioToolkit, and PhysioNet: Components of a new research resource for complex physiologic signals. Circulation 2000, 101, e215–e220. [Google Scholar] [CrossRef] [PubMed]

- Smíšek, R.; Maršánová, L.; Němcová, A.; Vítek, M.; Kozumplík, J.; Nováková, M. CSE database: Extended annotations and new recommendations for ECG software testing. Med Biol. Eng. Comput. 2017, 55, 1473–1482. [Google Scholar] [CrossRef]

- Okada, M. A digital filter for the QRS complex detection. IEEE Trans. Biomed. Eng. 1979, BME-26, 700–703. [Google Scholar] [CrossRef] [PubMed]

- Laguna, P.; Mark, R.G.; Goldberg, A.; Moody, G.B. A database for evaluation of algorithms for measurement of QT and other waveform intervals in the ECG. In Proceedings of the Computers in Cardiology 1997, Lund, Sweden, 7–10 September 1997; IEEE: New York, NY, USA, 1997; pp. 673–676. [Google Scholar]

- Lugovaya, T.S. Biometric Human Identification Based on ECG. Master’s Thesis, Electrotechnical University, Saint-Petersburg, Russian, 2005. [Google Scholar]

| Author, Year | Tech. | Dataset | Materials (Performance) |

|---|---|---|---|

| Abubakar et al., 2022 [22] | ASIC | MIT–BIH database, Creighton University database and The PhysioNet/Computing in Cardiology Challenge 2015 dataset. | The system can detect 13 abnormal cardiac rhythms with 99.1% sensitivity and 99.5% specificity and measured a classification accuracy of 99.3% |

| Aruna et al., 2022 [18] | FPGA | MIT–BIH arrhythmia database and PTB diagnostic database. | The system achieved 98.6% accuracy on the MIT–BIH database and 99.67% accuracy on the PTB database. |

| Tsoutsouras et al., 2016 [10] | FPGA | MIT–BIH arrhythmia database | The system achieved a 94% execution latency gain compared to the original SVM code. |

| Giorgio et al., 2023 [9] | FPGA | PTB diagnostic database. | The system achieved 99.2% accuracy. |

| Zhang et al., 2023 [23] | ASIC | MIT–BIH arrhythmia database. | The system achieved 96.69% accuracy. |

| Chowdhury et al., 2024 [31] | FPGA | PPG-BP database. | The system achieved 93.48% accuracy for detecting cerebral infarction and 96.43% accuracy in detecting cerebrovascular disease. |

| Chowdhury et al., 2023 [36] | FPGA | PPG BP database. | The system achieved 79.83% accuracy in detecting multiclass diseases. |

| Mazidi et al., 2019 [30] | FPGA | MIT–BIH arrhythmia database. | The system achieved 99% accuracy in the detection of premature ventricular contraction using SVM. |

| Shanthi et al., 2024 [32] | FPGA | MIT–BIH arrhythmia database. | The system achieved a convincing performance with 99% accuracy and an error rate of 0.05. |

| Author, Year | Tech. | Dataset | Materials (Performance) |

|---|---|---|---|

| Matsumoto et al., 2016 [38] | ASIC | Not listed. | The ASIC system achieved an 85% power consumption reduction compared to operation with an Microprocessing Unit (MPU). |

| Habiboullah et al., 2016 [39] | FPGA | MIT–BIH arrhythmia database and QT database. | The system achieved 91.85% accuracy in QRS complex detection. |

| García Limón et al., 2023 [40] | FPGA | QT database | The system achieved 97.8% accuracy in QRS complex detection. |

| Chowdhury, 2015 [41] | FPGA | CSE ECG database. | The system achieved 99% accuracy in QRS complex detection. |

| Lee et al., 2021 [13] | FPGA | MIT–BIH arrhythmia database. | The system takes 5.7 s to diagnose ECG signals of five people containing 1987 beats with software and 0.572 s with hardware, which is 89.96% shorter than the software execution time. |

| Kumar and Chari, 2018 [42] | FPGA | MIT–BIH arrhythmia database | The system achieved 99.86% accuracy in R-peak detection. |

| Al-Shueli, 2015 [43] | FPGA | Not listed | The system improved the accuracy of the signal waveform and occupied only 30% of the available FPGA slices. |

| Karataş et al., 2022 [15] | FPGA | MIT–BIH arrhythmia database. | The system achieved a maximum operating speed of 651.827 MHz and it can be safely used in ECG simulators. |

| Bodisco et al., 2014 [44] | FPGA | Not listed. | The system produced computational optimisation of ECG signal features using the Markov-chain Monte Carlo method. |

| Abdul-Kadir et al., 2015 [45] | ASIC | Not listed. | Multiple designs were used and the best performing system was chosen. |

| Wang et al., 2016 [12] | FPGA | MIT–BIH arrhythmia database. | The system achieved up to 38 times improvement in performance and 142 times improvement in energy efficiency when compared to commercial servers. |

| Jain and Bhaumik, 2016 [46] | ASIC | MIT–BIH arrhythmia database and PTB diagnostic database. | The system achieved 99.86% sensitivity and 99.93% specificity for QRS complex peak detection. |

| Pamula et al., 2017 [37] | ASIC | Not listed. | The system achieved a reduction in power consumption by up to 30 times without significant loss of accurate heart rate estimation. |

| Da and Sodini, 2014 [47] | ASIC | MIT–BIH arrhythmia database. | The system is sufficiently low power and compact to be suitable for long-term, wearable cardiovascular monitoring applications. |

| Abburi and Rani, 2019 [48] | FPGA | Not listed. | The system produced a heart beat detector design for fetal ECG monitoring. |

| Nagpal et al., 2014 [49] | FPGA | MIT–BIH arrhythmia database and AF Termination Challenge database. | The system achieved 99% accuracy in hardware beat detection. |

| Gu et al., 2016 [50] | FPGA | MIT–BIH arrhythmia database. | The system took 0.731 ms to perform the analysis and produce diagnosis results for one minute of ECG signals. |

| Desai et al., 2021 [51] | FPGA | MIT–BIH arrhythmia database. | The system is capable of real-time and low-power processing. |

| Ganatra and Vithalani, 2022 [52] | FPGA | MIT–BIH arrhythmia database and QT database. | The system achieved 99.84% sensitivity, 99.85% accuracy and 99.86% positive prediction for QRS complex detection compared to those attained with state-of-the-art feature descriptors. |

| Alouneh et al., 2015 [53] | FPGA | MIT–BIH arrhythmia database. | The system achieved a 24% power reduction, 8.9% latency reduction and 10.5% area reduction compared to the original QRS algorithm. |

| Chatterjee et al., 2015 [54] | FPGA | Not listed. | The system achieved 97.58% detection sensitivity for the P-wave, 98.4% detection sensitivity for the R-wave, and 97.78% detection sensitivity for the T-wave. |

| Noor et al., 2018 [55] | ASIC | MIT–BIH arrhythmia database. | The system achieved a low-energy consumption of 27.72 nJ per FFT, which is 14.22% lower than a standard 128-point radix-2 FFT. |

| Author, Year | Tech. | Dataset | Materials (Performance) |

|---|---|---|---|

| Kalamani et al., 2023 [56] | FPGA | MIT–BIH arrhythmia database. | The system achieved a reduction in area size by 82.6% for folded adaptive lattice LMS filter of order K = 2 and 91.05% for folded adaptive lattice LMS filter of order K = 4. |

| A. I. Al-SAl-Shueli, 2022 [43] | FPGA | Not listed. | The system achieved effectiveness of filtering for ECG signals by eliminating high and low frequency noises. 50% AF probability within 40 weeks. Minimal-risk patients: 85% AF-free for 7 years. |

| Uttraphan et al., 2024 [11] | FPGA | Not listed. | The proposed system significantly outperformed the software implementation in MATLAB . In addition, it was shown that the system can be optimised for cost-performance trade-off. |

| Reddy and Tallapragada, 2024 [57] | FPGA | MIT–BIH arrhythmia database and PTB diagnostic database. | The proposed compressor system achieved 45.23% CR on the MIT–BIH database and 10.87% CR on the PTB diagnostic database. |

| Alhelal et al., 2015 [28] | FPGA | MIT–BIH arrhythmia database. | The system achieved 98% accuracy in hardware beat detection. |

| Elbedwehy et al., 2022 [58] | FPGA | MIT–BIH arrhythmia database. | The system achieved SNRimp of 15.8 and PRD of 24.6, for the electromyogram noise and SNRimp of 25.7 and PRD of 4.9, for power line interference noise. |

| Egila et al., 2016 [59] | FPGA | MIT–BIH arrhythmia database. | The system achieved 97.8% accuracy when compared to other designs, and achieved a reduction in utilising resources on FPGA implementation. |

| Venkatesan et al., 2019 [60] | FPGA | Not listed. | The system achieved a 20.4% increase in total area in delayed error normalised LMS filter, and a reduction in power consumption by 31.8%. |

| Saha and Mandal, 2024 [29] | FPGA | ECG-ID database, MIT–BIH arrhythmia database and MIT–BIH normal sinus rhythm database. | The system achieved 81.11% accuracy for ECG-ID recordings, 88.89% accuracy for MIT–BIH normal sinus rhythm and 85.41% accuracy for the MIT–BIH arrhythmia database. |

| Sohal et al., 2022 [61] | FPGA | MIT–BIH arrhythmia database. | The system of the Haar wavelet based pre-processor design consumed 136 mW of on-chip power, 0.76% of LUTs, 5.03% of slice registers and 6.7% of DSPs in comparison with other wavelet and window techniques using zedboard. |

| Jawadkar et al., 2024 [62] | FPGA | MIT–BIH arrhythmia database. | The system of the proposed FIR filter occupied 16.38% less area and consumed 79.58% less power than similar designs described in the literature. |

| Patel and Shah, 2022 [63] | FPGA | ECG-ID database. | The system of the proposed multiband filter achieved excellent performance in noise attenuation, and efficient hardware implementation, making it a valuable tool for ECG signal processing. |

| Aboutabikh et al., 2016 [64] | FPGA | Not listed. | The system of the proposed FIR notch filter has shown to be robust for eliminating power line interference. |

| Priya and Muralidhar, 2014 [65] | FPGA | MIT–BIH arrhythmia database. | The digital adaptive filter designed and implemented has demonstrated the potential for significant improvements in signal processing tasks, particularly in ECG analysis. |

| ÇancioĞlu et al., 2020 [66] | FPGA | Not listed. | The system demonstrated the effective performance of digital filters in ECG data processing, highlighting the advantages of using FPGA and MATLAB for this application. The approach ensures high-quality signal processing where the noisy ECG data has been successfully filtered out. |

| Patel and Shah, 2025 [67] | FPGA | ECG-ID database. | The filter design system utilised 1932 LUTs, 5299 FFs, 1 DSP block, and consumed 0.158 W of on-chip power. This indicates an efficient use of resources and low-power consumption, making it suitable for compact biomedical devices. |

| Anusuya et al., 2015 [68] | ASIC | Not listed. | The system provided a comprehensive approach to improve the performance of wearable ECG recording by focusing on reducing power consumption, optimising computational efficiency, and effectively managing motion artifacts. |

| Gon and Mukherjee, 2023 [69] | FPGA | MIT–BIH arrhythmia database and MIT–BIH noise stress database. | The system proposed used 85% fewer registers and 50% fewer LUTs compared to other denoising architectures, making it more resource-efficient. |

| Sakthivel and Reddy, 2023 [70] | FPGA | Not listed. | The system presented a comprehensive analysis of different fault-tolerant configurations and their impact on the performance of digital filters in ECG systems, highlighting the trade-offs between redundancy, noise reduction, and hardware complexity. |

| Shingne and Gawali, 2017 [71] | FPGA | MIT–BIH arrhythmia database and MIT–BIH noise stress database. | The system of the FPGA-based cascaded FIR filter demonstrated significant improvements in performance, power efficiency, and noise reduction capabilities, making it a robust solution for ECG signal processing. |

| Ganatra and Vithalani, 2022 [72] | FPGA | MIT–BIH arrhythmia database and MIT–BIH noise stress database. | The system consumed 153 LUTs and 186 slice FFs, which is a reduction compared to conventional designs. In addition, the system used less power. |

| Sohal et al., 2019 [73] | FPGA | MIT–BIH arrhythmia database. | The system produced an enhanced ECG processing performance ensuring effective noise reduction and resource efficiency. |

| Padmavathi and Veenadevi, 2019 [74] | FPGA | MIT–BIH arrhythmia database. | The system of the FPGA-based arrhythmia detection demonstrated significant improvements in resource utilisation and performance, with 77.57% reduction in the number of registers used compared to previous designs. |

| Jayashree et al., 2022 [21] | FPGA | Not listed. | The system consumed 30% less power, 20% reduction in area size, and more than 15% improvement in delay compared to other reported filter structure. |

| Polat and Kayhan, 2021 [75] | FPGA | MIT–BIH arrhythmia database. | The system of LSD-OMP implemented on FPGA demonstrated significant improvements in execution time, power consumption, and reconstruction efficiency. |

| Alhelal and Faezipour, 2017 [76] | FPGA | MIT–BIH arrhythmia database. | The system achieved 98% accuracy in beat detection when implemented in hardware while providing the detected beats and the classification of irregular heart-beat rates in real-time. |

| Sasikala et al., 2016 [77] | FPGA | Not listed. | The system achieved 5.1% reduction in LUT slices, and 3.22% reduction in the number of slice registers compared with the proposed combination. |

| Mohanraj and Vimala, 2020 [78] | FPGA | Not listed. | The system revealed that the high-speed IIR and FIR filters resulted in better performance than the conventional ones at the cost logic elements usage. |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license.

Share and Cite

Hariri, R.; Cirstea, M.; Oghaz, M.M.D.; Benkrid, K.; Faust, O. Hardware Accelerators for Cardiovascular Signal Processing: A System-on-Chip Perspective. Micromachines 2026, 17, 51. https://doi.org/10.3390/mi17010051

Hariri R, Cirstea M, Oghaz MMD, Benkrid K, Faust O. Hardware Accelerators for Cardiovascular Signal Processing: A System-on-Chip Perspective. Micromachines. 2026; 17(1):51. https://doi.org/10.3390/mi17010051

Chicago/Turabian StyleHariri, Rami, Marcian Cirstea, Mahdi Maktab Dar Oghaz, Khaled Benkrid, and Oliver Faust. 2026. "Hardware Accelerators for Cardiovascular Signal Processing: A System-on-Chip Perspective" Micromachines 17, no. 1: 51. https://doi.org/10.3390/mi17010051

APA StyleHariri, R., Cirstea, M., Oghaz, M. M. D., Benkrid, K., & Faust, O. (2026). Hardware Accelerators for Cardiovascular Signal Processing: A System-on-Chip Perspective. Micromachines, 17(1), 51. https://doi.org/10.3390/mi17010051