GaN HEMT Oscillators with Buffers

Abstract

1. Introduction

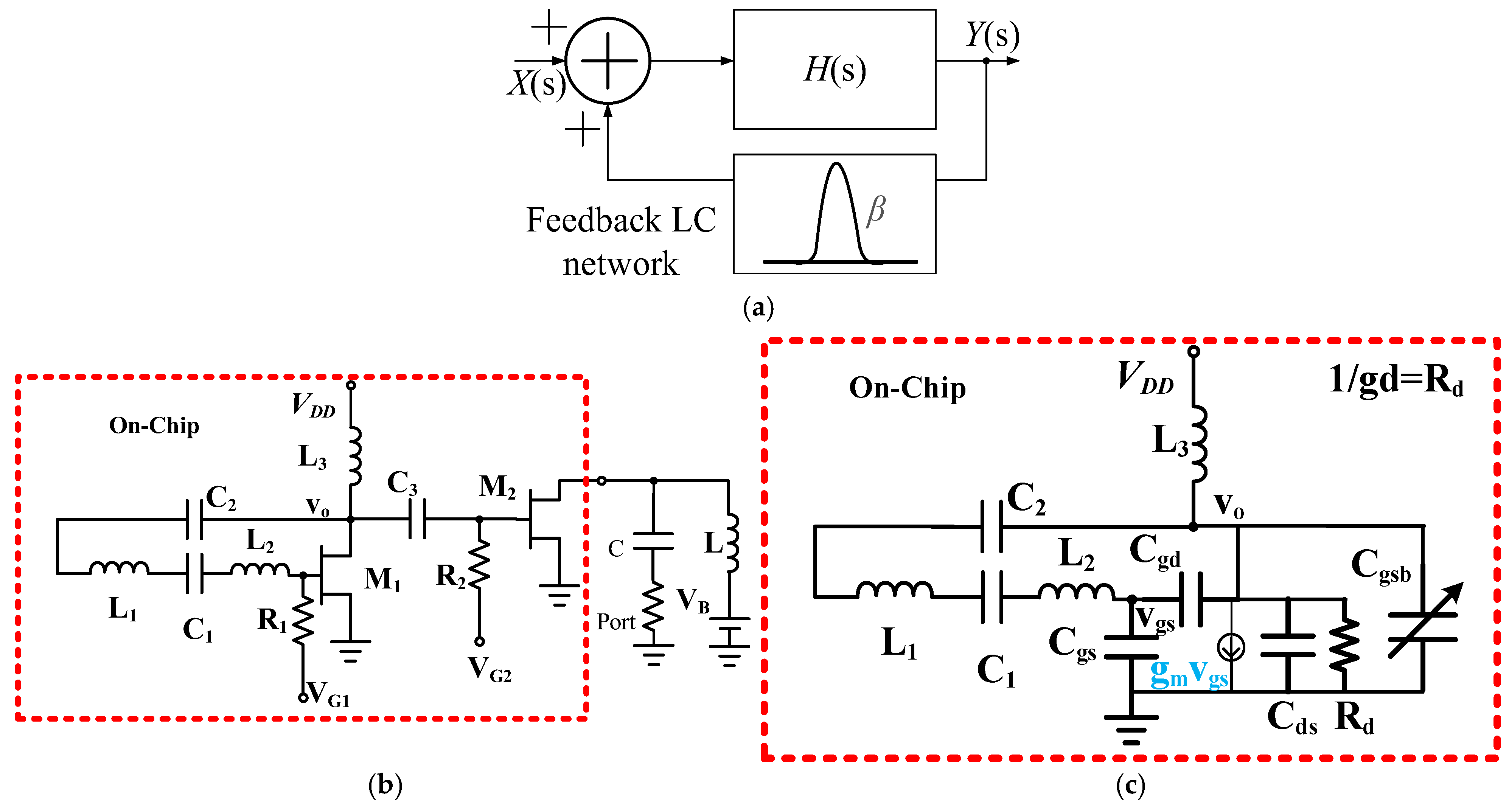

2. X-Band Feedback GaN HEMT Oscillator with Split Core and Buffer

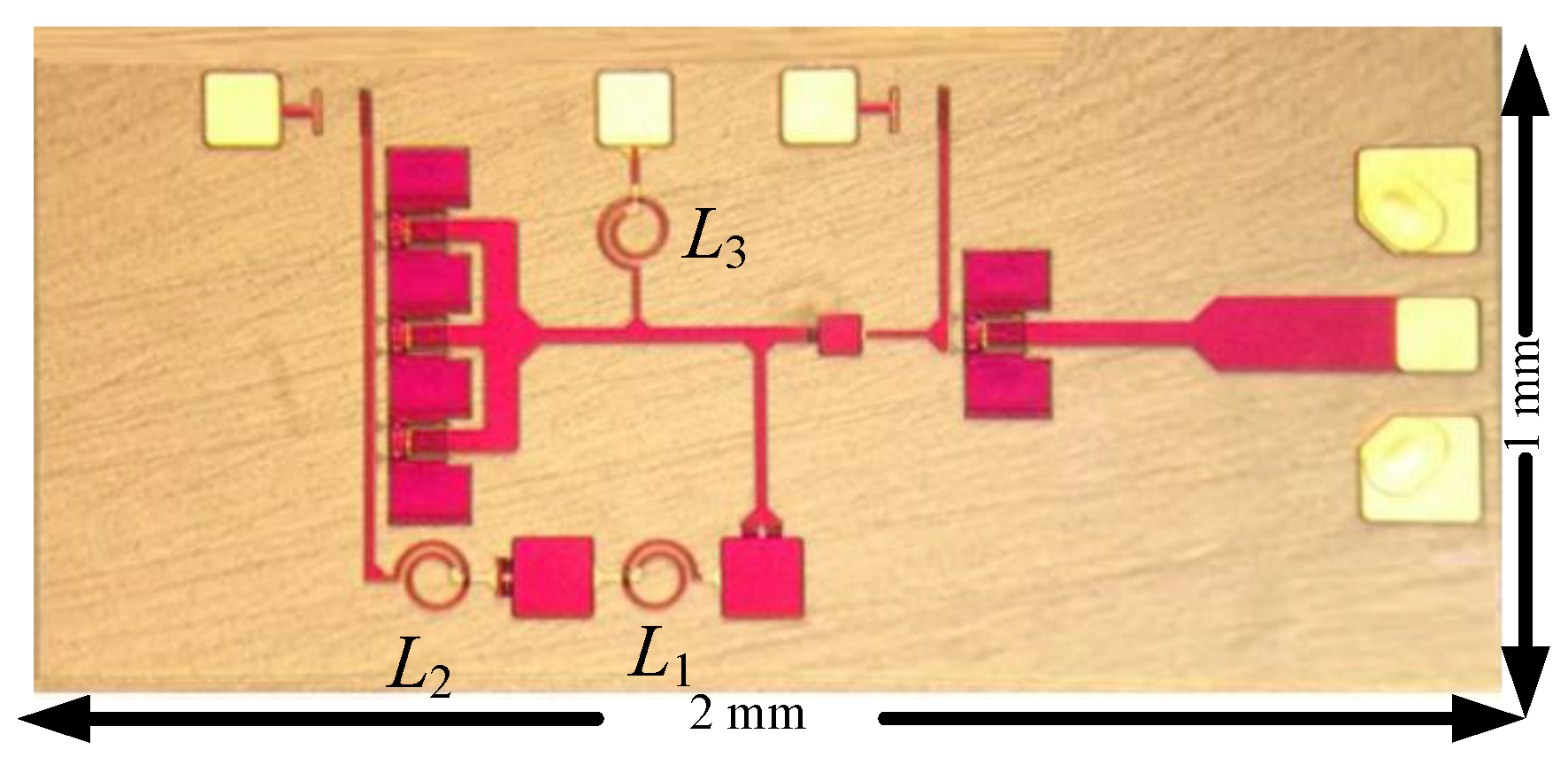

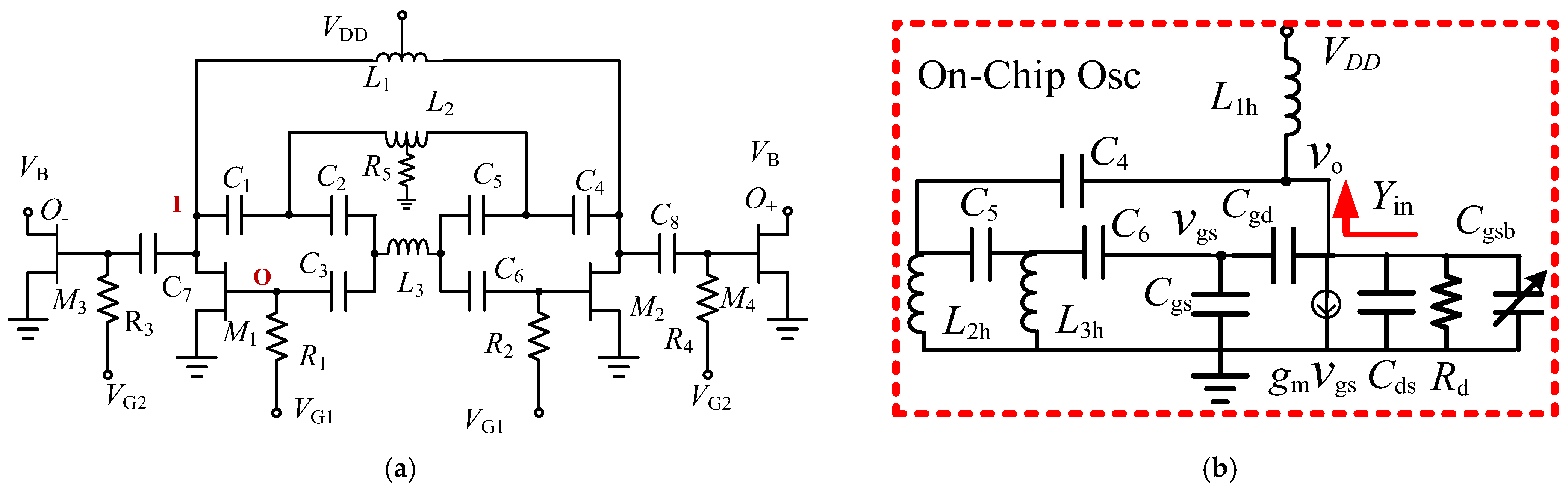

2.1. Circuit Design of the First Oscillator

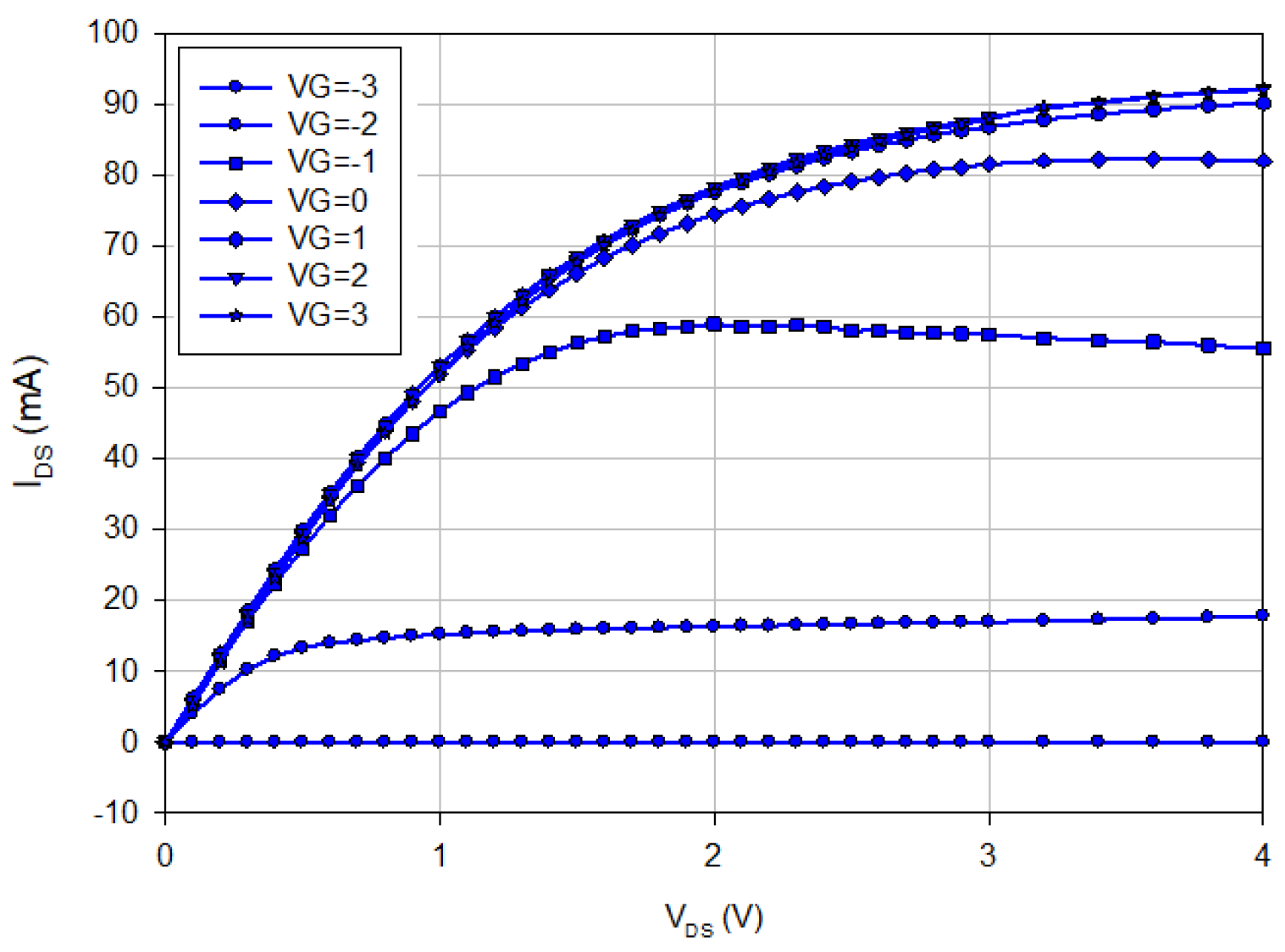

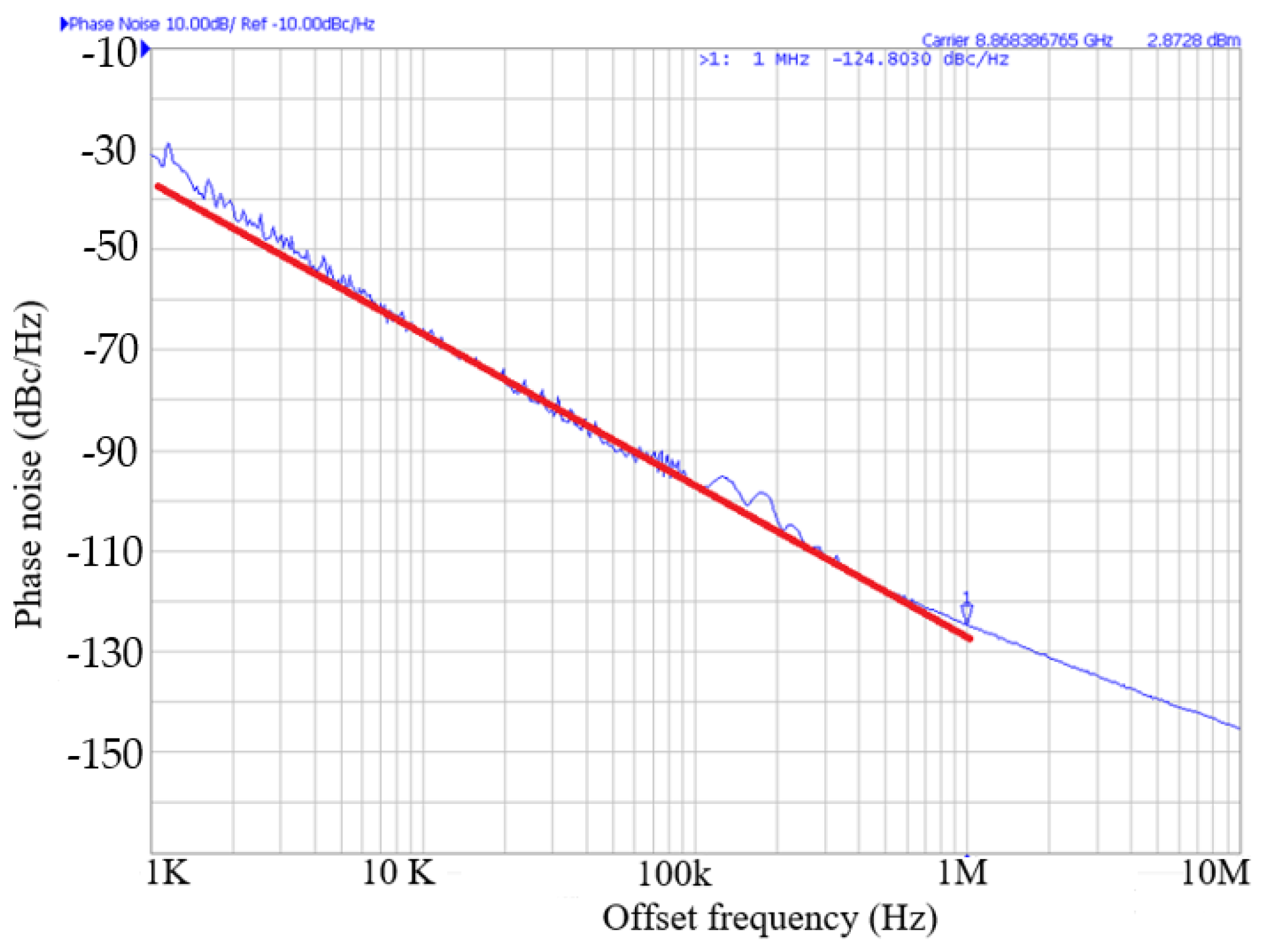

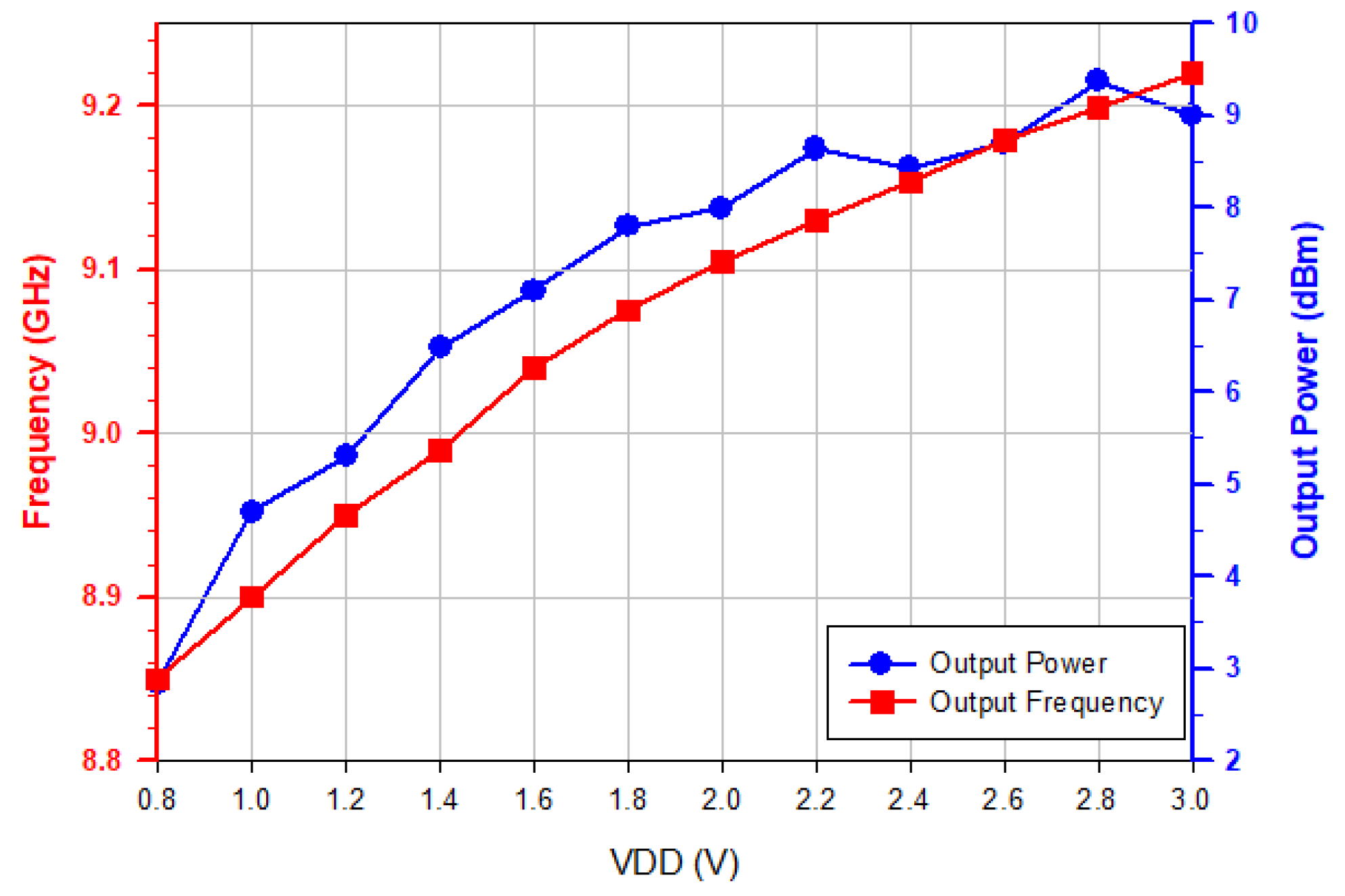

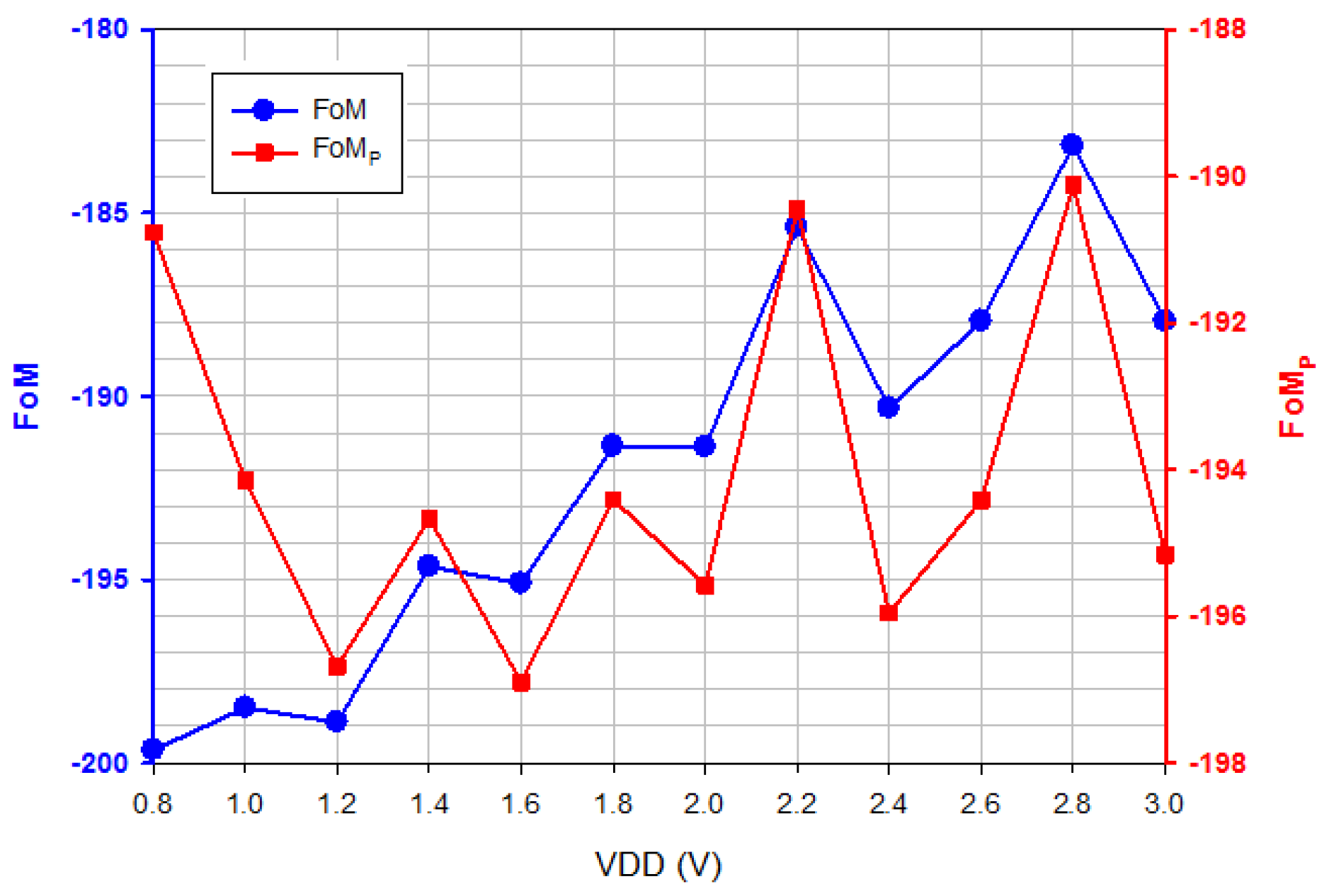

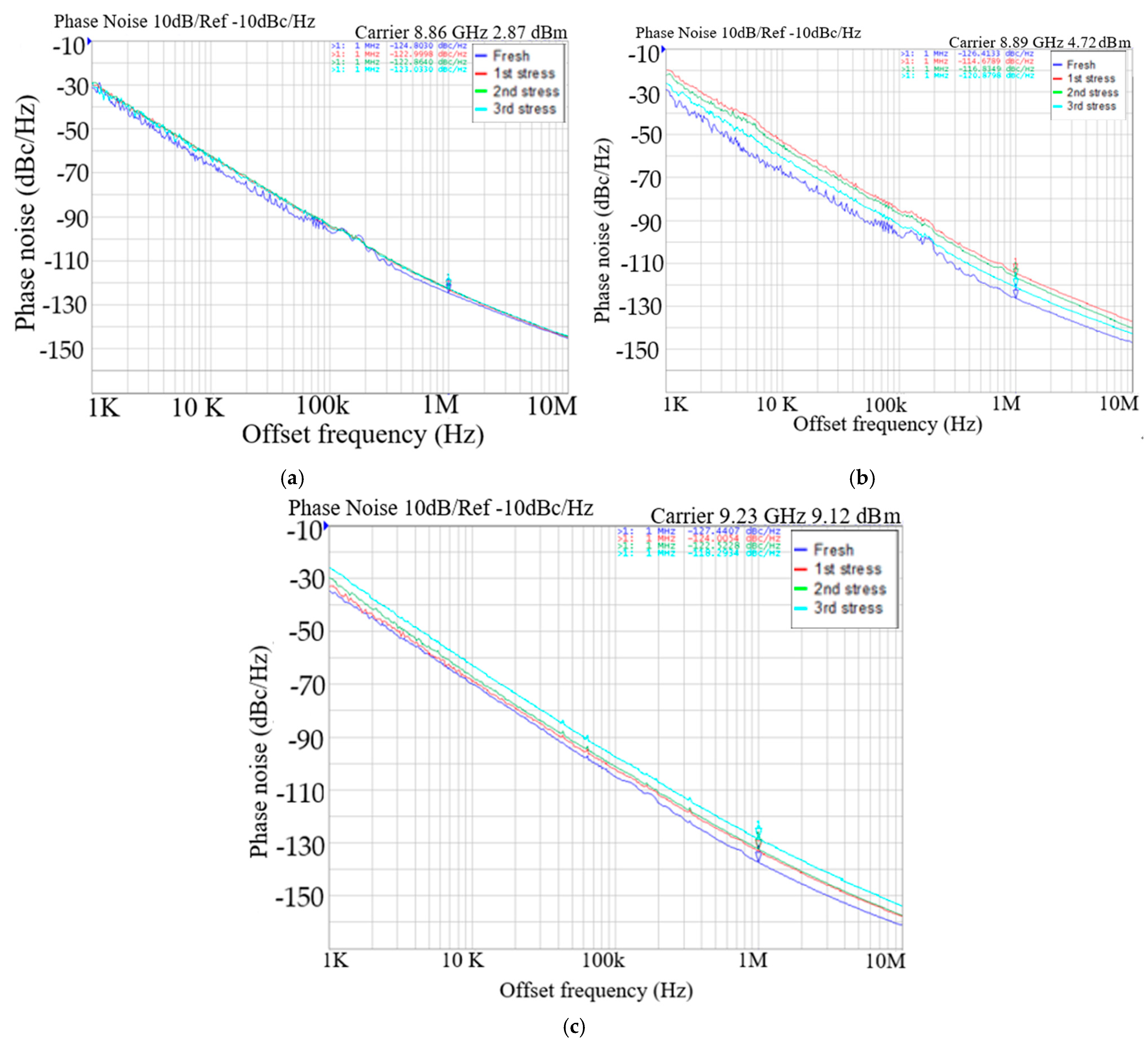

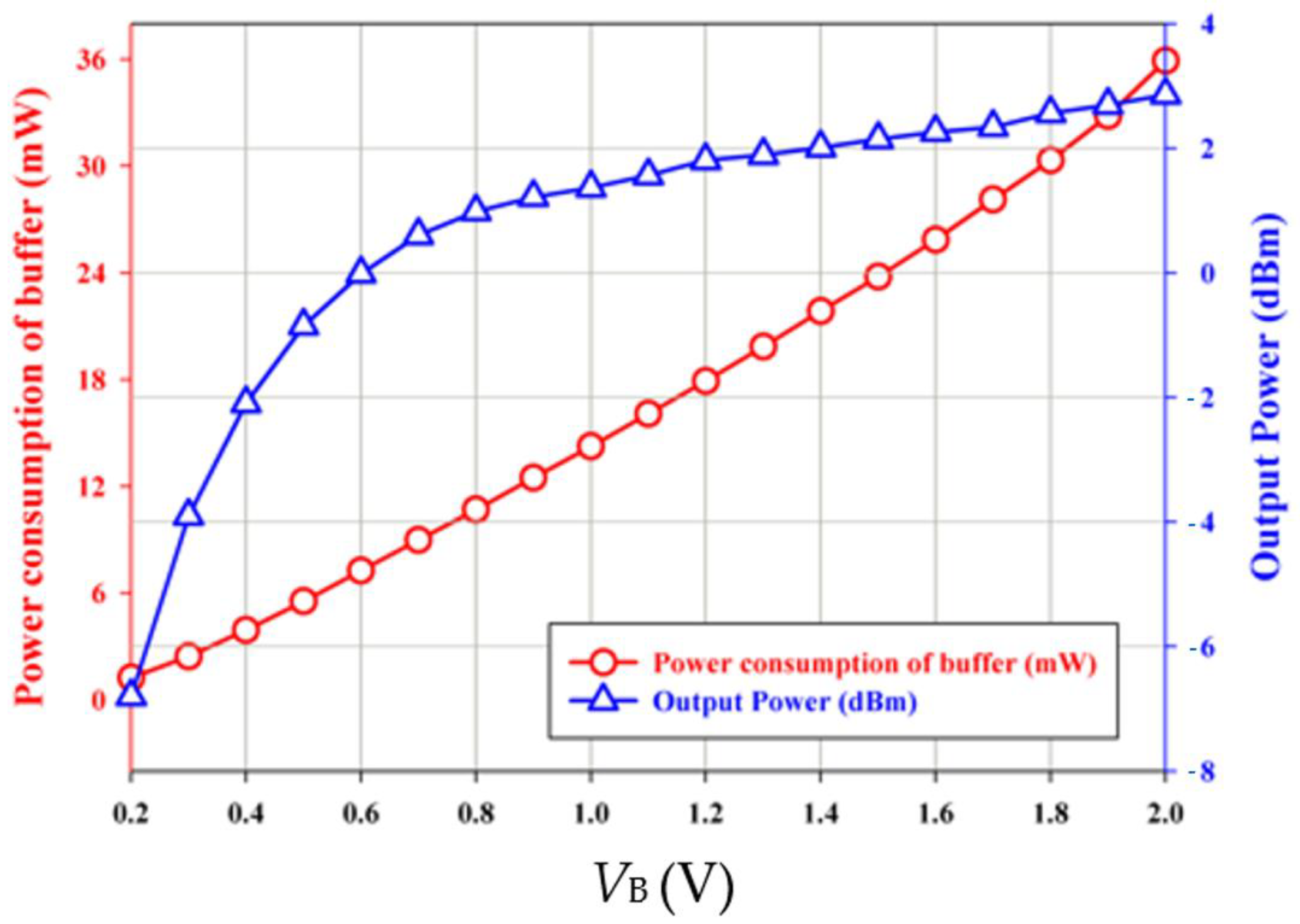

2.2. Measurement and Discussion

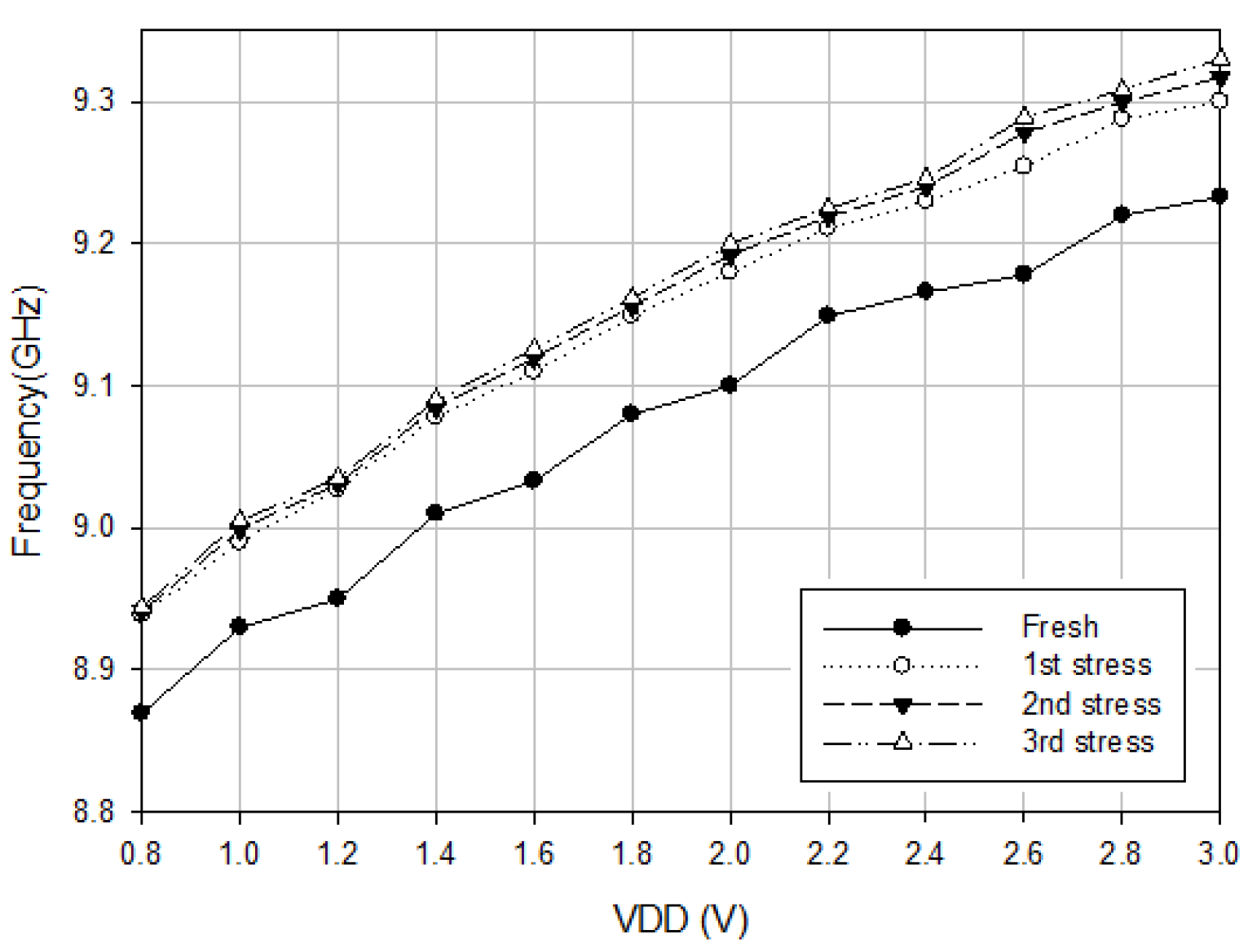

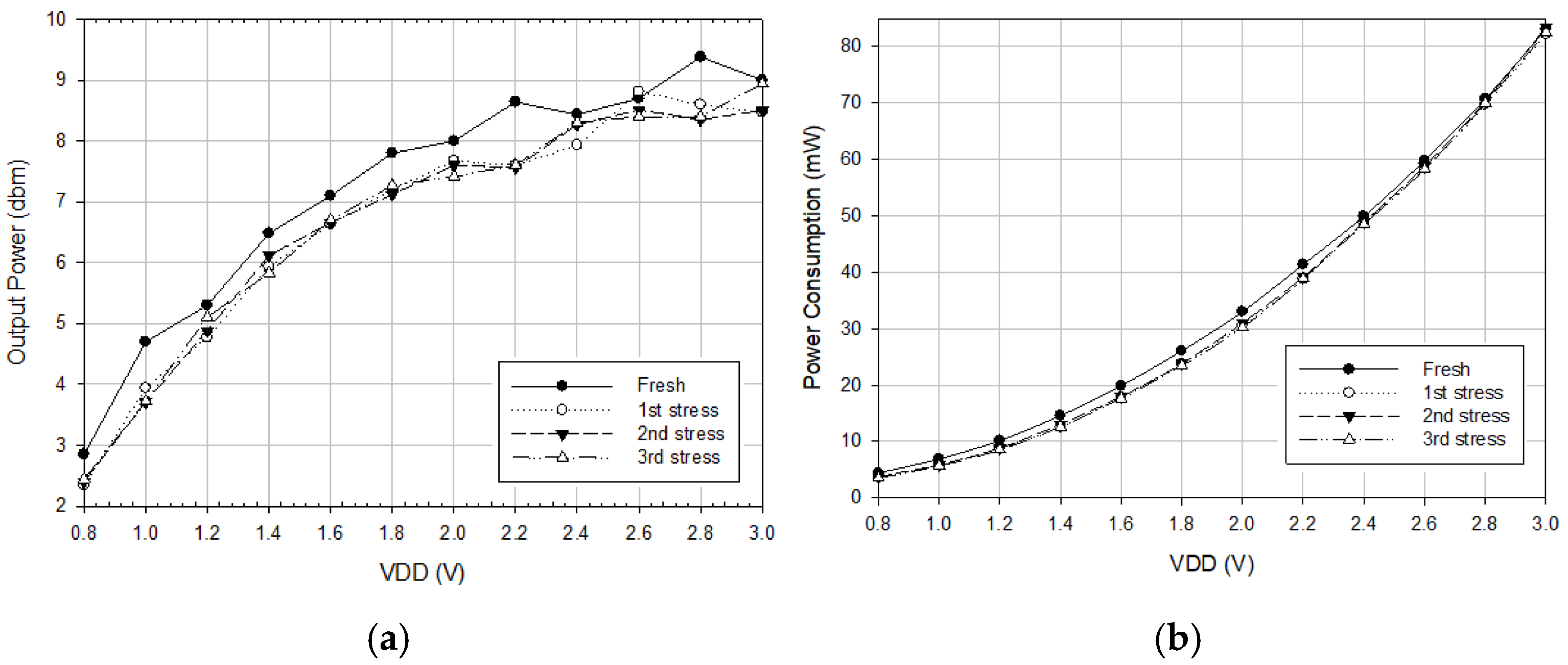

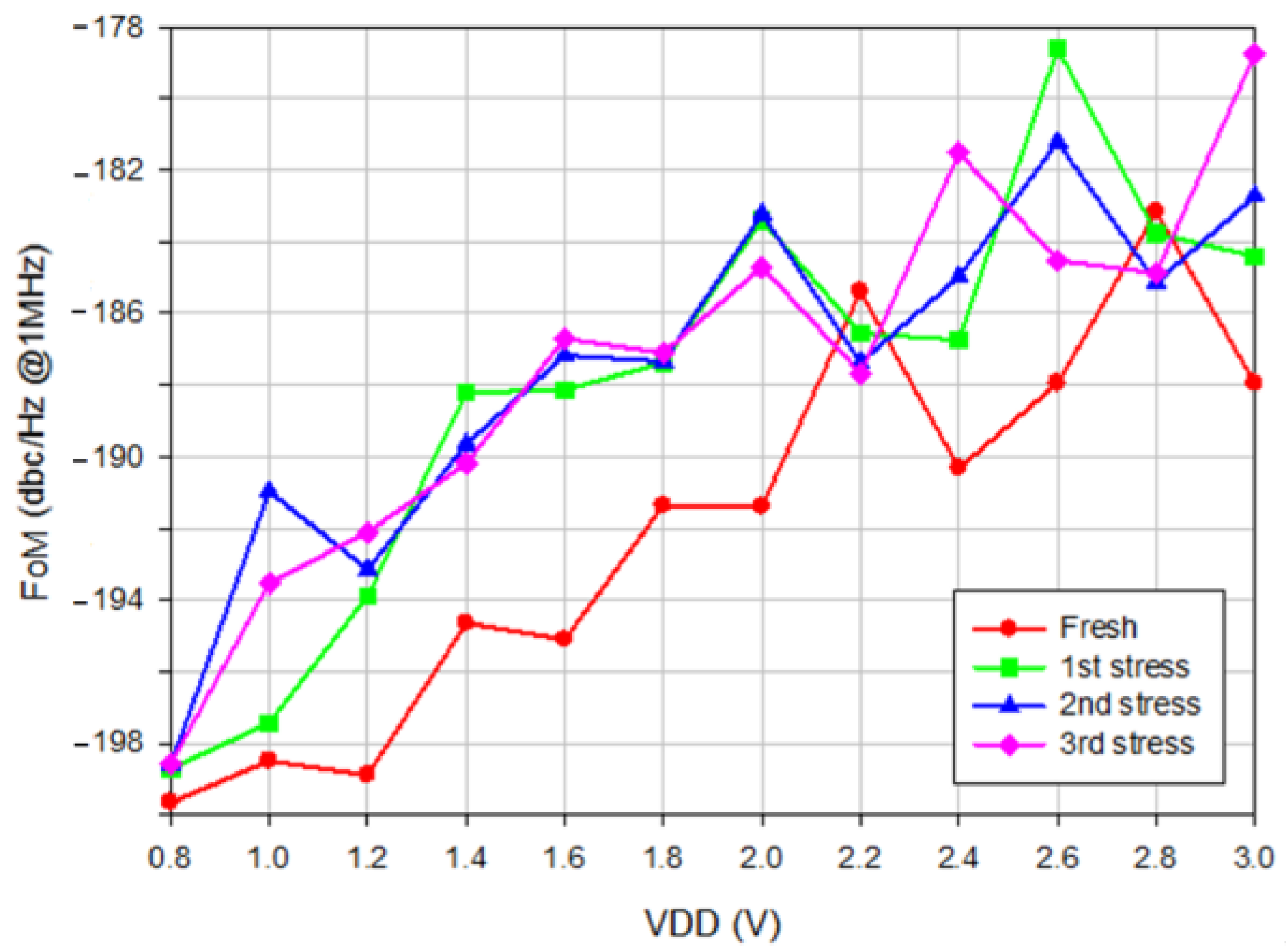

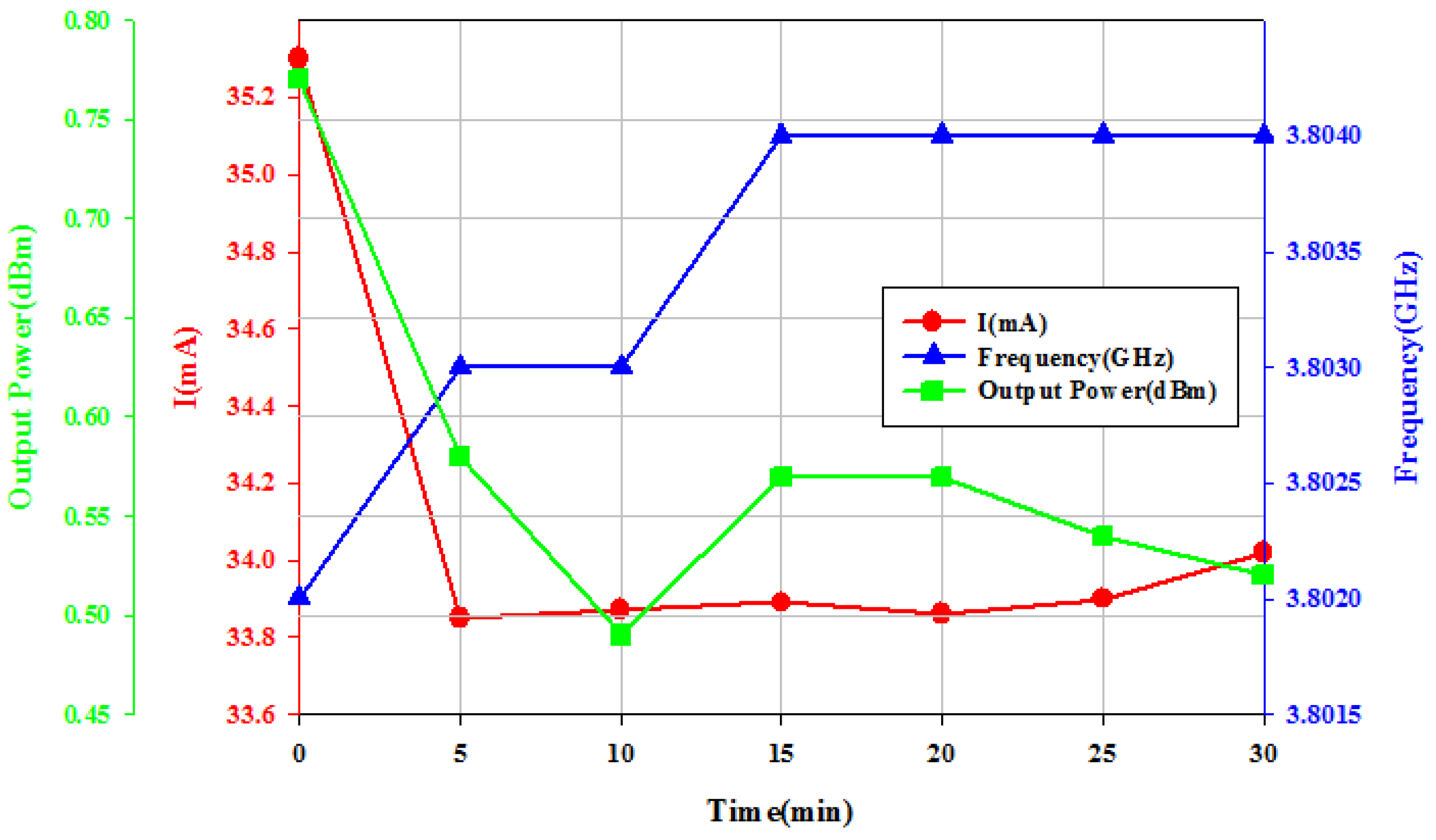

2.3. Drift of GaN HEMT Oscillator Performance with High Operating Bias

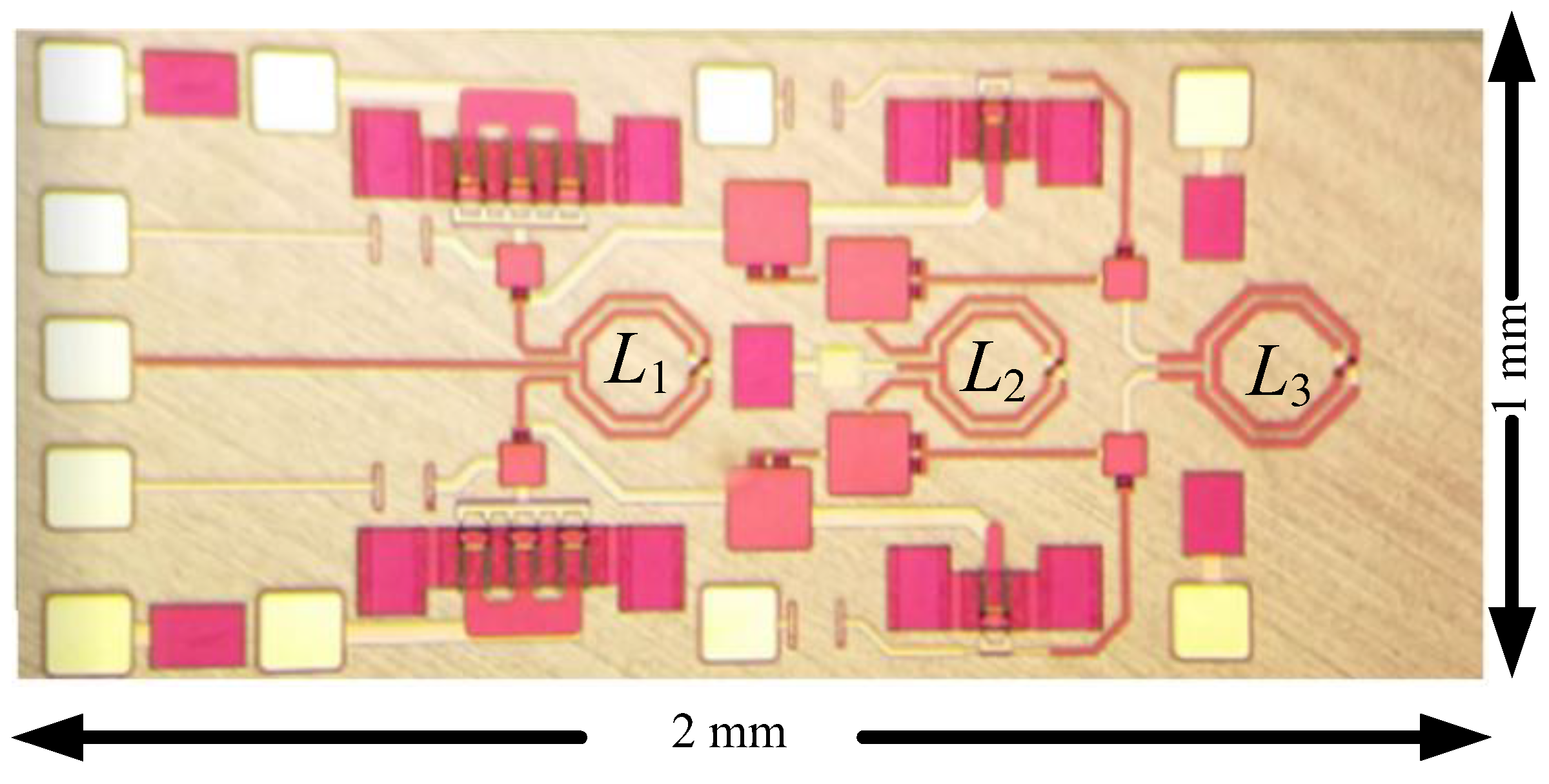

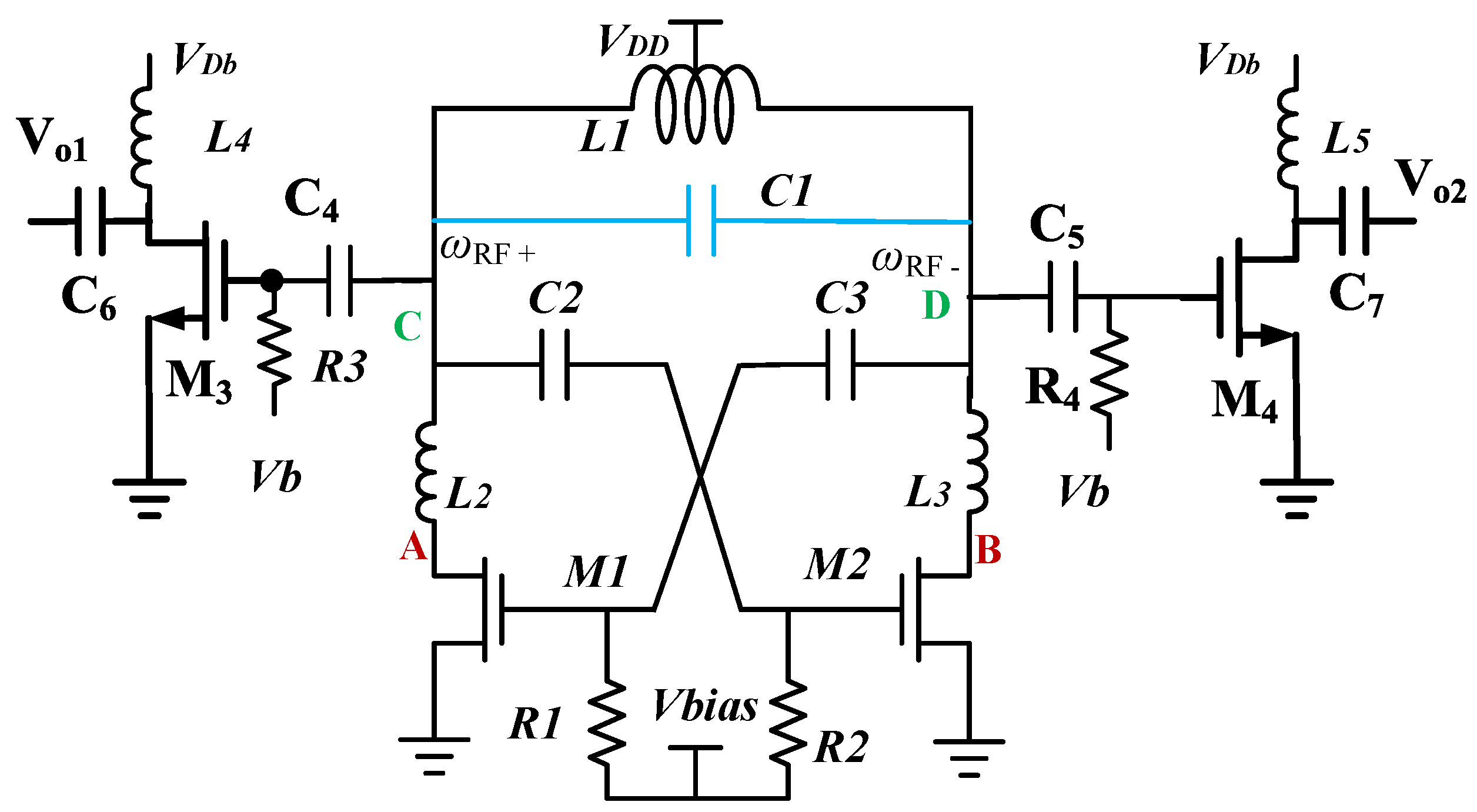

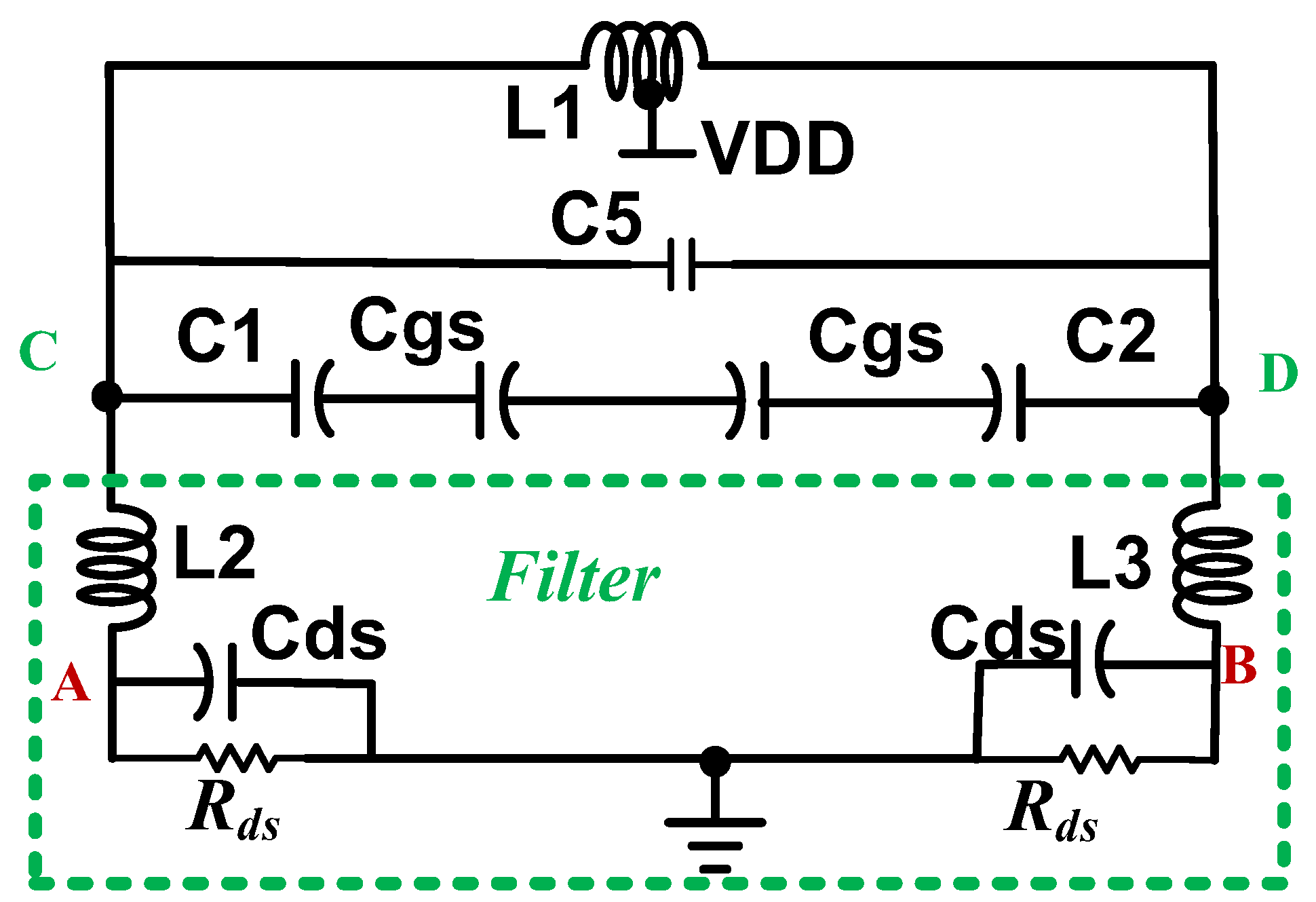

3. Balanced GaN HEMT Oscillator with Left-Handed Transmission Line Filter

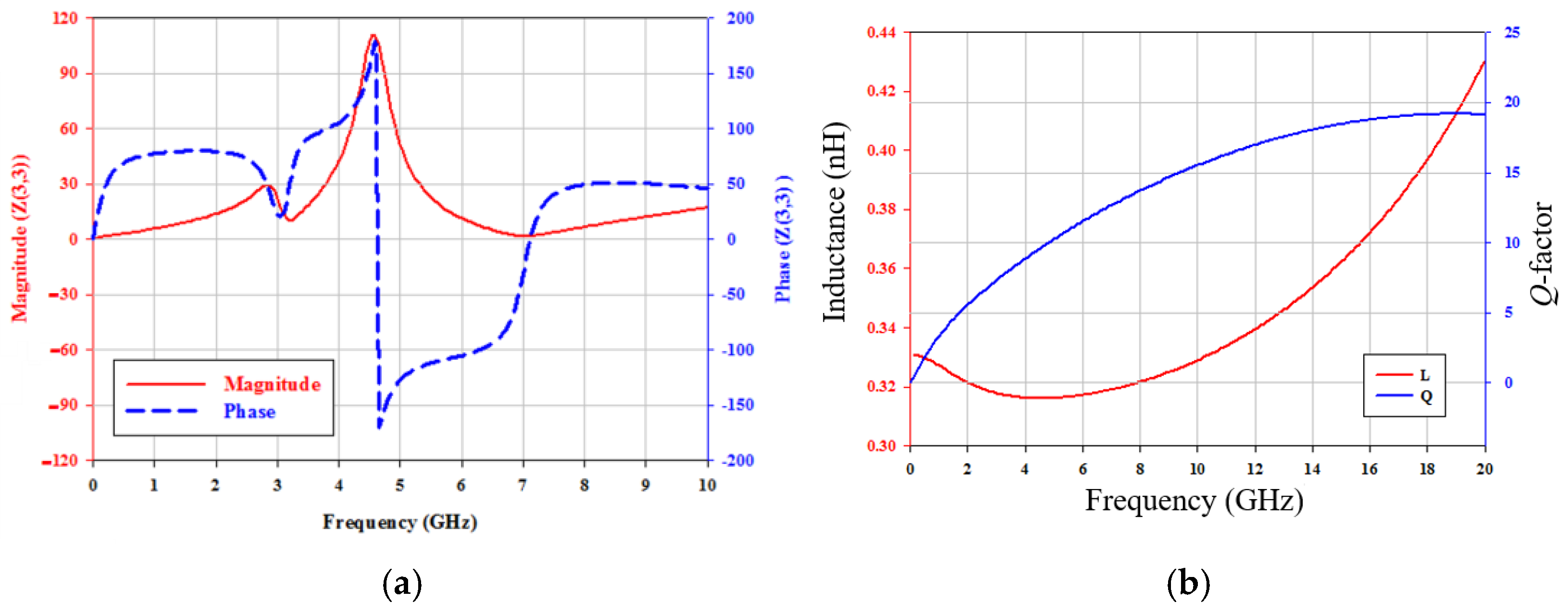

3.1. Circuit Design of the Balanced Oscillator

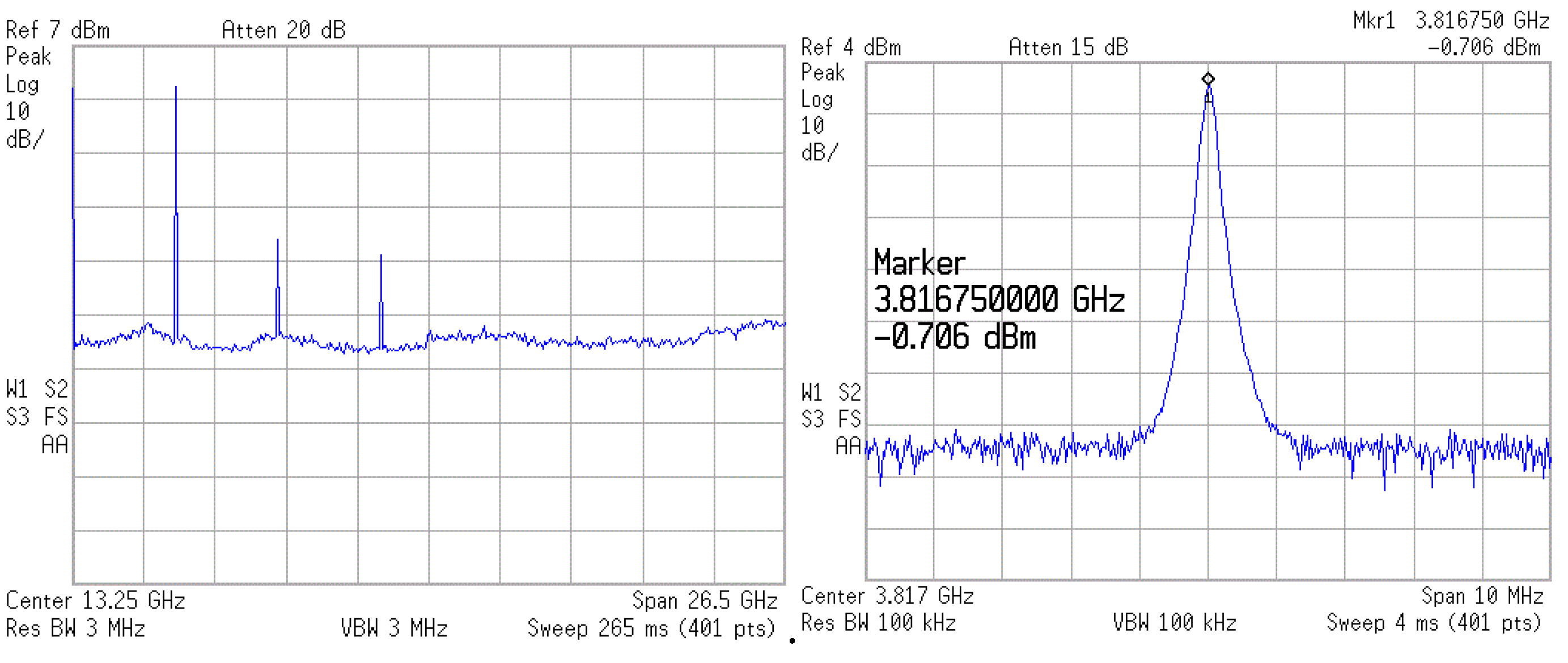

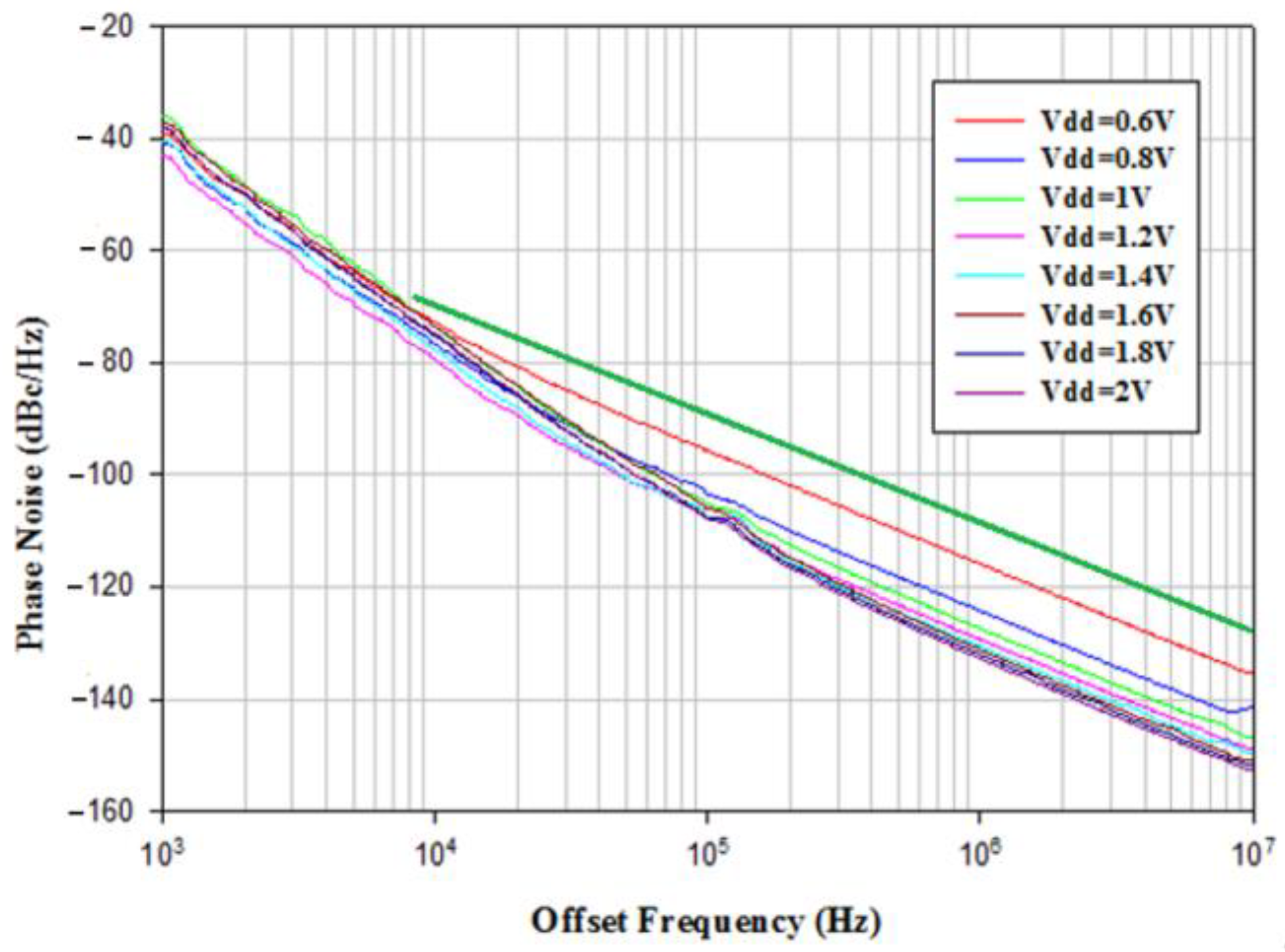

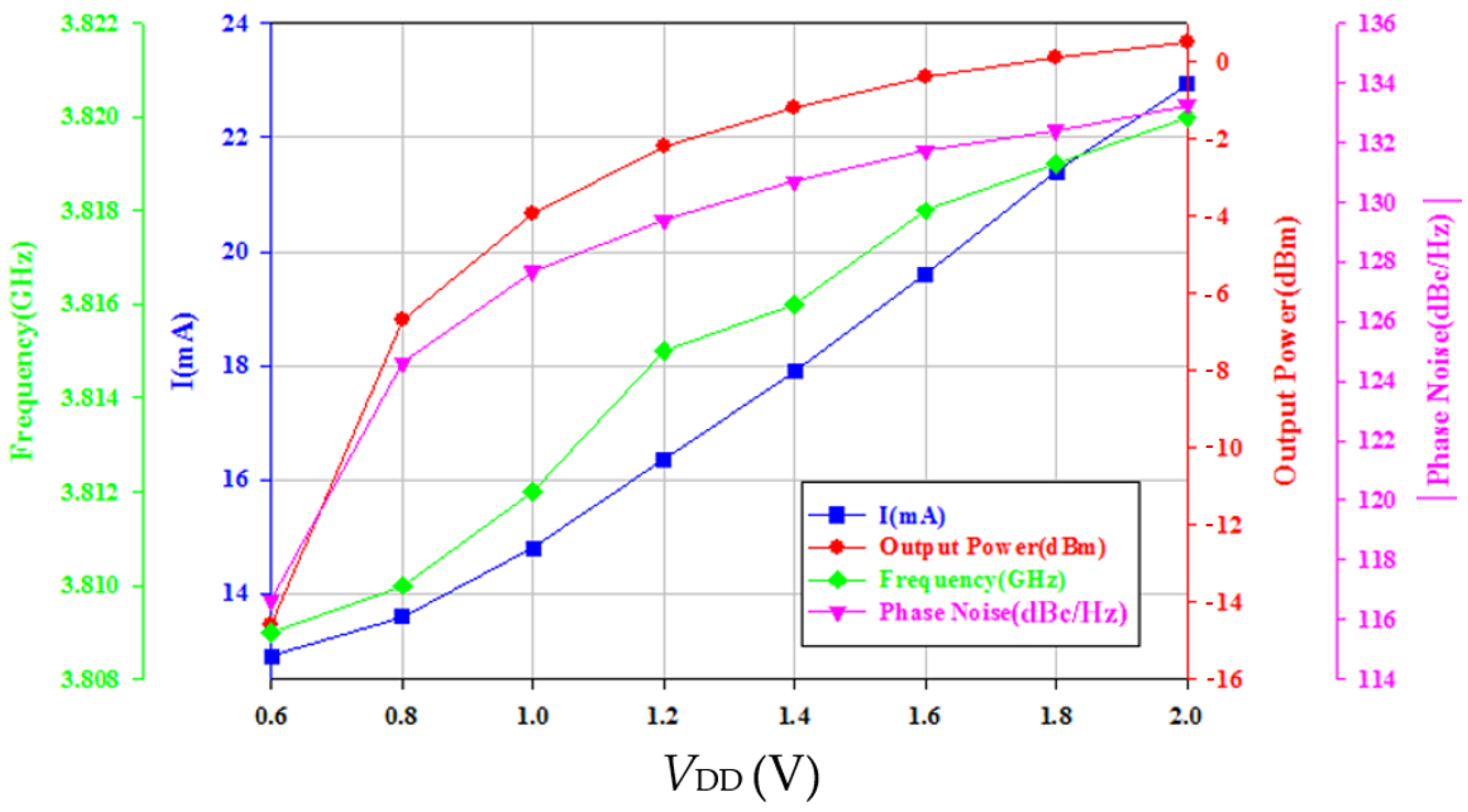

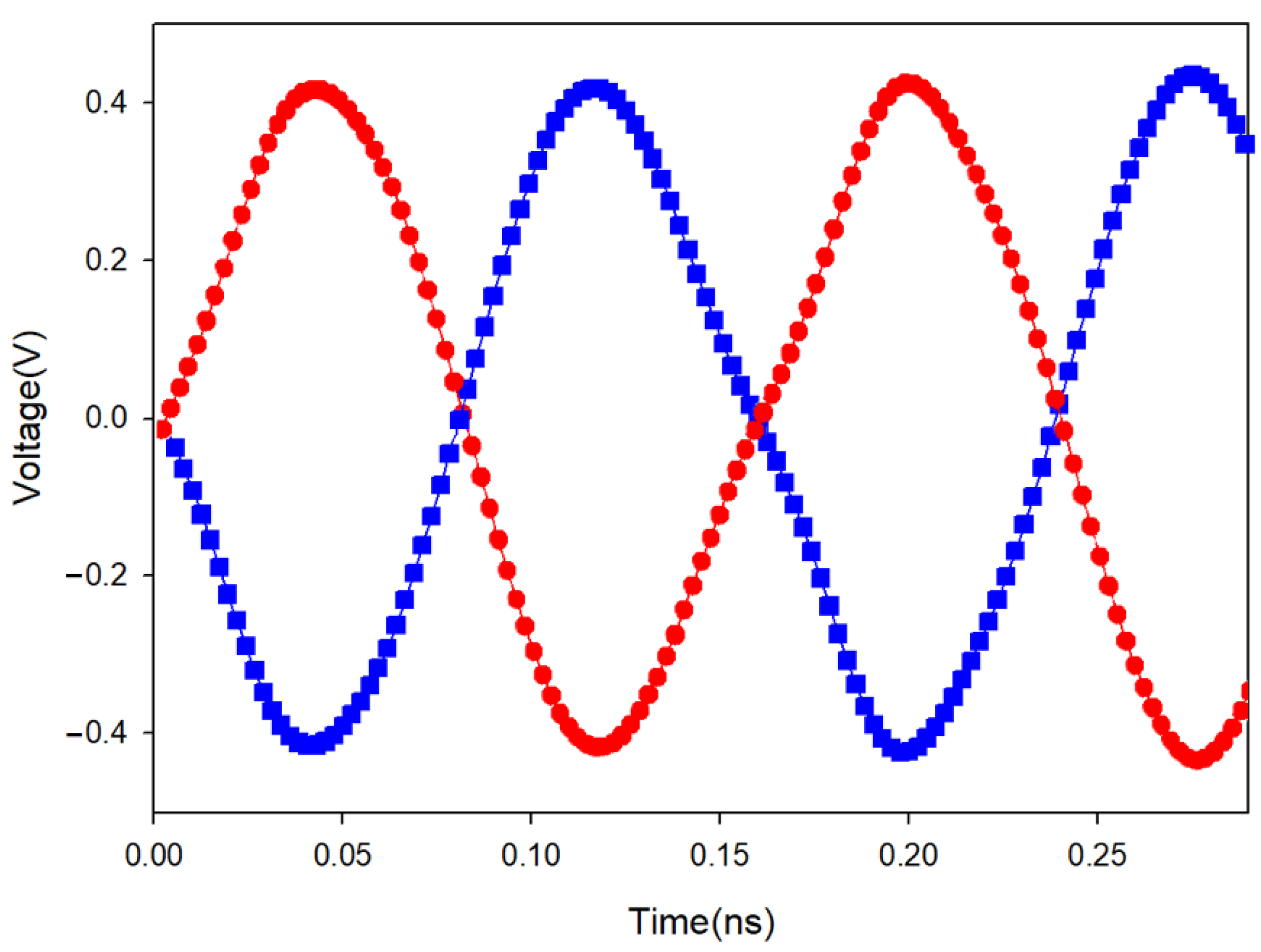

3.2. Measurement and Discussion

3.3. High-Supply Voltage Effect

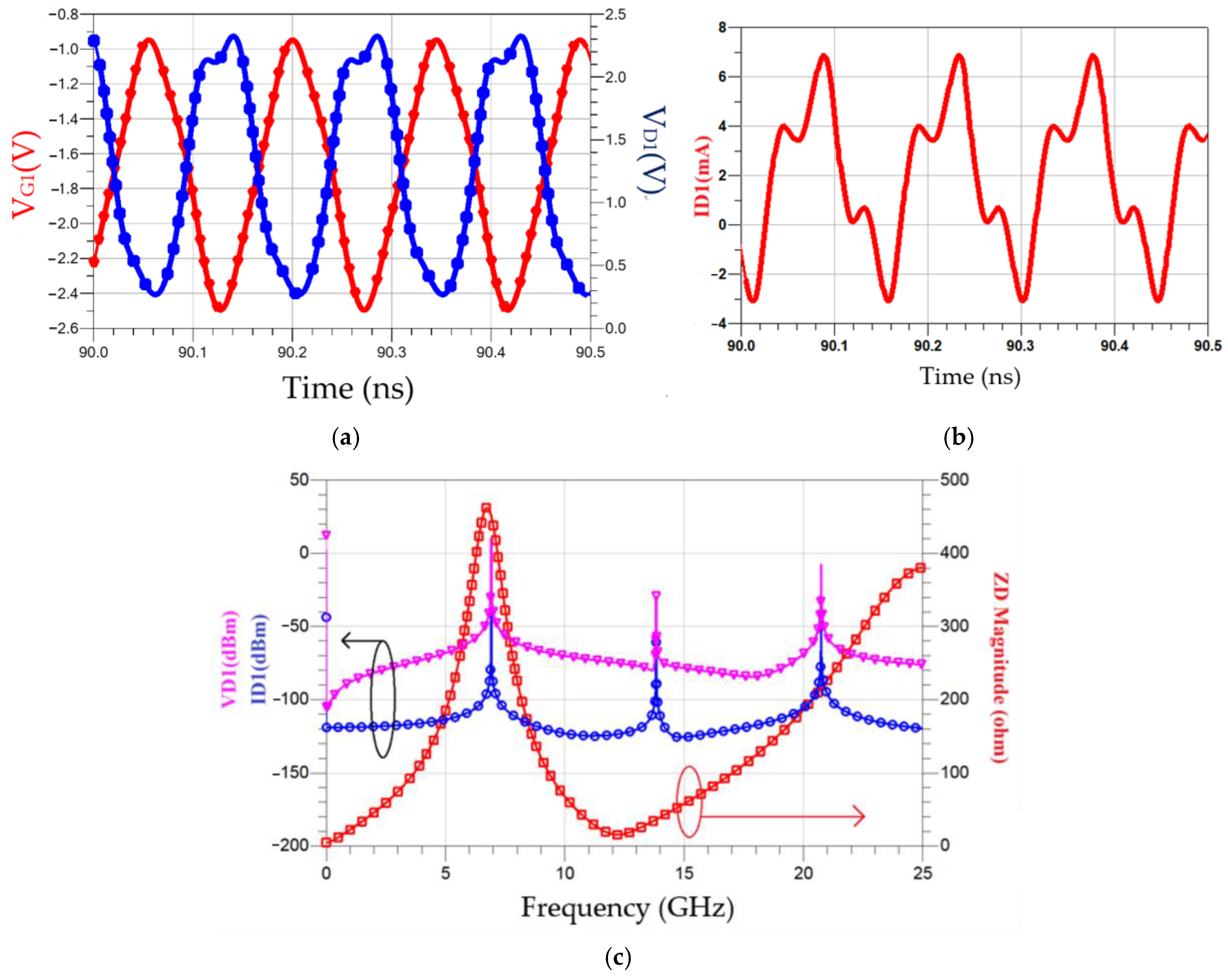

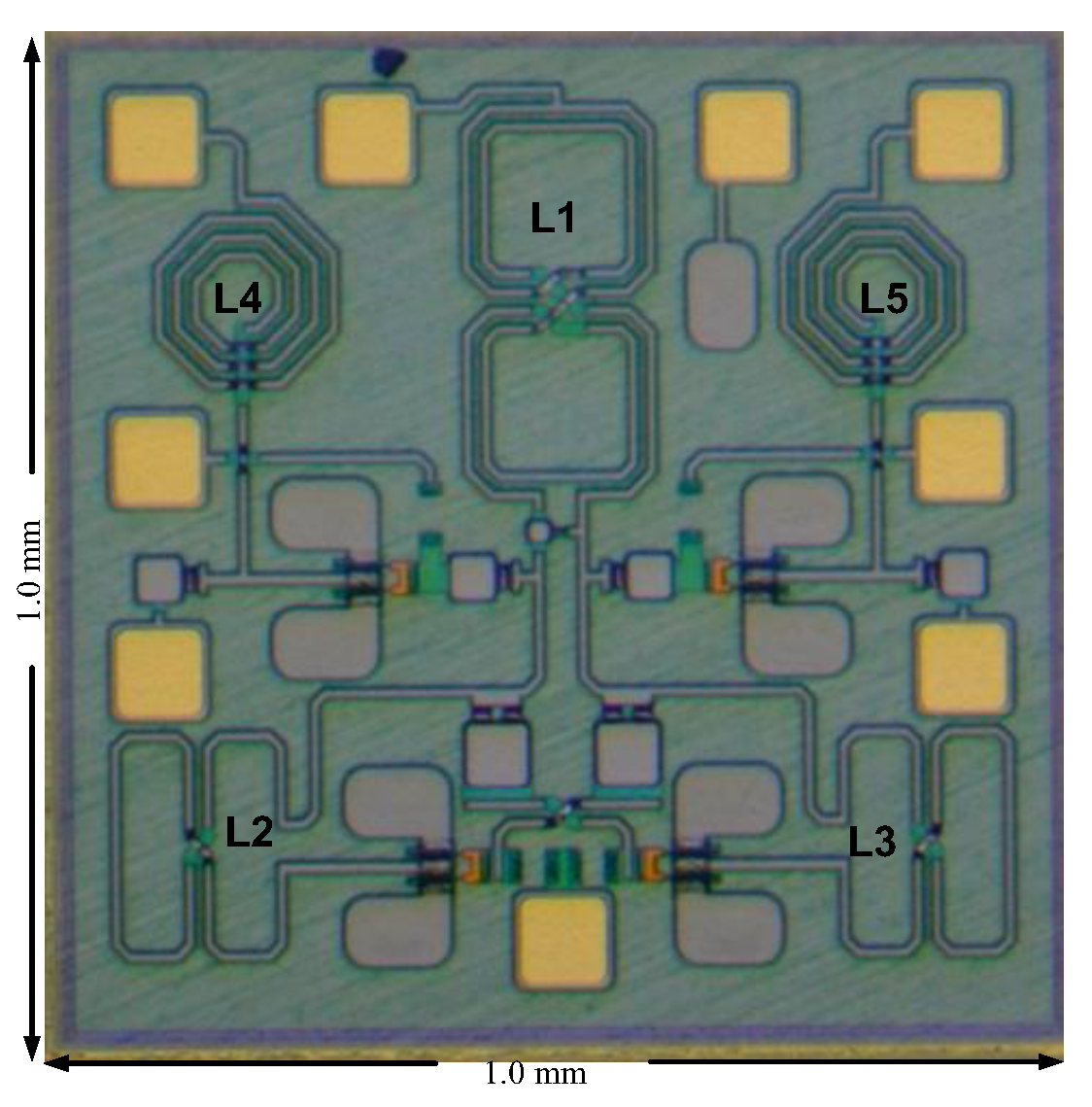

4. GaN HEMT Oscillator with Implicit-Resonator

4.1. Circuit Design

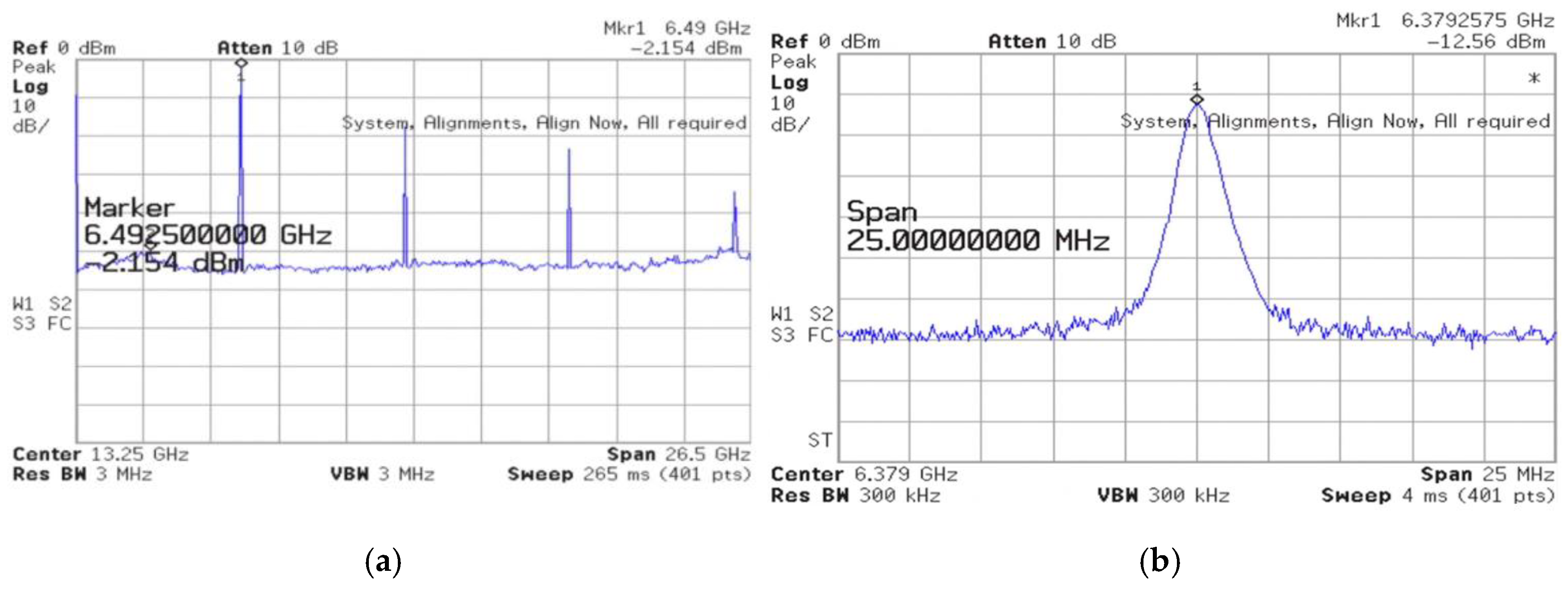

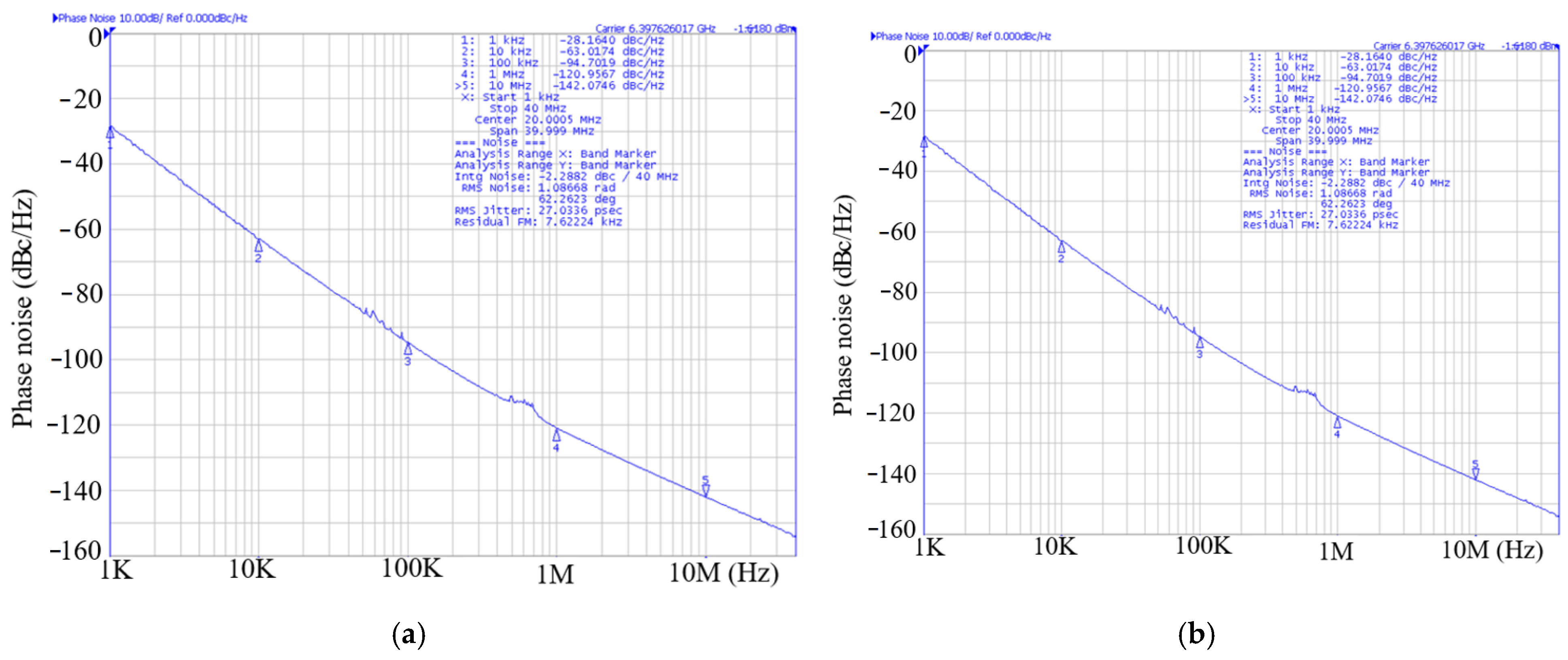

4.2. Measurement and Discussion

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Balandin, A.; Morozov, S.V.; Cai, S.; Li, R.; Wang, K.L.; Wijeratne, G.; Viswanathan, C.R. Low flicker-noise GaN/AlGaN heterostructure field-effect transistors for microwave communications. IEEE Trans. Microw. Theory Tech. 1999, 47, 1413–1417. [Google Scholar] [CrossRef]

- Hörberg, M.; Kuylenstierna, D. Low phase noise power-efficient MMIC GaN-HEMT oscillator at 15 GHz based on a quasi-lumped on-chip resonator. In Proceedings of the 2015 IEEE MTT-S International Microwave Symposium, Phoenix, AZ, USA, 17–22 May 2015; pp. 1–4. [Google Scholar] [CrossRef]

- Jang, S.-L.; Chang, Y.-H.; Lai, W.-C. A Feedback GaN HEMT Oscillator. In Proceedings of the 2018 International Conference on Microwave and Millimeter Wave Technology (ICMMT), Chengdu, China, 7–11 May 2018; pp. 1–3. [Google Scholar] [CrossRef]

- Jang, L.; Chang, Y.-H.; Chiou, J.-S.; Lai, W.-C. A single GaN HEMT oscillator with 4-path inductors. In Proceedings of the IEEE ISNE-2018, Taipei, Taiwan, 7–9 May 2018. [Google Scholar]

- Herbert, Z.; Lai, S.; Dan, K.; Jonathan, F.; Kristoffer, A.; Niklas, R. An X-band low phase noise AlGaN-GaN-HEMT MMIC push-push oscillator. In Proceedings of the 2011 IEEE Compound Semiconductor Integrated Circuit Symposium (CSICS), Waikoloa, HI, USA, 16–19 October 2011; pp. 1–4. [Google Scholar]

- Lai, S.; Kuylenstierna, D.; Ozen, M.; Horberg, M.; Rorsman, N.; Angelov, I.; Zirath, H. Low phase noise GaN HEMT oscillators with excellent figures of merit. IEEE Microw. Wirel. Compon. Lett. 2014, 24, 412–414. [Google Scholar] [CrossRef]

- Wohlmuth, W.; Weng, M.-H.; Lin, C.-K.; Du, J.-H.; Ho, S.-Y.; Chou, T.-Y.; Li, S.M.; Huang, C.; Wang, W.-C.; Wang, W.-K. AlGaN/GaN HEMT development targeted for X band applications. In Proceedings of the 2013 IEEE International Conference on Microwaves, Communications, Antennas and Electronic Systems (COMCAS 2013), Tel Aviv, Israel, 21–23 October 2013; pp. 1–4. [Google Scholar]

- Jang, L.; Su, Y.-J.; Lin, K.J.; Wang, B.-J. An 4.7 GHz low power cross-coupled GaN HEMT oscillator. Microw. Opt. Technol. Lett. 2018, 60, 2442–2447. [Google Scholar] [CrossRef]

- Jang, S.-L.; Lin, K.J.; Lai, W.C.; Juang, M.-H. A capacitive cross-coupled GaN HEMT injection-locked frequency divider. In Proceedings of the 2018 International Symposium on VLSI Design, Automation and Test (VLSI-DAT), Hsinchu, Taiwan, 16–19 April 2018; pp. 1–3. [Google Scholar] [CrossRef]

- Sanabria, C.; Xu, H.; Heikman, S.; Mishra, U.K.; York, R.A. A GaN differential oscillator with improved harmonic performance. IEEE Microw. Wirel. Compon. Lett. 2005, 15, 463–465. [Google Scholar] [CrossRef]

- Soubercaze-Pun, G.; Tartarin, J.G.; Bary, L.; Rayssac, J.; Morvan, E.; Grimbert, B.; Delage, S.L.; De Jaeger, J.-C.; Graffeuil, J. Design of a X-band GaN oscillator: From the low frequency noise device characterization and large signal modeling to circuit design. In Proceedings of the 2006 IEEE MTT-S International Microwave Symposium Digest, San Francisco, CA, USA, 11–16 June 2006; pp. 747–750. [Google Scholar]

- Kaper, V.S.; Tilak, V.; Kim, H.; Vertiatchikh, A.V.; Thompson, R.M.; Prunty, T.R.; Eastman, L.F.; Shealy, J.R. High-power monolithic AlGaN/GaN HEMT oscillator. IEEE J. Solid State Circuits 2003, 38, 1457–1461. [Google Scholar] [CrossRef]

- Jang, S.-L.; Hou, J.C.; Shih, B.-S.; Li, G.-Z. Low-phase noise 8.22 GHz GaN HEMT oscillator using a feedback multi-path transformer. Microw. Opt. Technol. Lett. 2019, 61, 605–609. [Google Scholar] [CrossRef]

- Jang, S.-L.; Lin, H.-H.; Hsue, C.-W. Mode-switching left-handed standing wave voltage-controlled oscillator. Microw. Opt. Technol. Lett. 2013, 55, 1977–2244. [Google Scholar] [CrossRef]

- Jang, S.-L.; Lee, W.-H.; Hsue, C.-W. Fully-integrated standing wave oscillator using composite right/left-handed LC network. Microw. Opt. Technol. Lett. 2013, 55, 985–988. [Google Scholar] [CrossRef]

- Jang, S.-L.; Liu, Y.-W.; Chang, C.-W.; Hsue, C.-W. Dual-band VCO with composite right-/left-handed resonator. Microw. Opt. Technol. Lett. 2013, 55, 468–471. [Google Scholar] [CrossRef]

- Liu, H.; Zhu, X.; Boon, C.C.; Yi, X.; Mao, M.; Yang, W. Design of ultra-low phase noise and high power integrated oscillator in 0.25 µm GaN-on-SiC HEMT technology. IEEE Microw. Wirel. Compon. Lett. 2014, 24, 120–122. [Google Scholar] [CrossRef]

- Lai, S.; Kuylenstierna, D.; Hörberg, M.; Rorsman, N.; Angelov, I.; Andersson, K.; Zirath, H. Accurate phase-noise prediction for a balanced Colpitts GaN HEMT MMIC oscillator. IEEE Trans. Microw. Theory Tech. 2013, 61, 3916–3926. [Google Scholar] [CrossRef]

- Wang, J.; Huang, Y.; Chang, Y.-C.; Liu, Y.; Chang, D.C.; Hsu, S.S.H. A K-band MMIC cross-coupled oscillator with high output power in 0.25-μm GaN HEMT. IEEE Microw. Wirel. Techn. Lett. 2023, 33, 1211–1214. [Google Scholar] [CrossRef]

- Lee, S.; Jeon, S.; Jeong, J. Harmonic-tuned high-efficiency RF oscillator using GaN HEMTs. IEEE Microw. Wirel. Compon. Lett. 2012, 22, 318–320. [Google Scholar] [CrossRef]

- Jang, S.-L.; Lee, Y.-C.; Lai, W.-C. Left-Hand Resonator VCO Using an Orthogonal Transformer. Electronics 2025, 14, 2765. [Google Scholar] [CrossRef]

- Jang, S.-L.; Lin, Z.-J.; Juang, M.-H. State-of-the-Art VCO with eight-shaped resonator-type transmission line. Electronics 2025, 14, 2322. [Google Scholar] [CrossRef]

- Shahmohammadi, M.; Babaie, M.; Staszewski, R.B. A 1/f noise upconversion reduction technique for voltage-biased RF CMOS oscillators. IEEE J. Solid State Circuits 2016, 51, 2610–2624. [Google Scholar] [CrossRef]

| Ref | Proc (um) | Topol | Vdd (V)/ Pdis (mW) | fo GHz | PN dBc/Hz | FOM dBc/Hz | 8-Shaped Inductor |

|---|---|---|---|---|---|---|---|

| [7] | 0.25 | Hartley | 28/1456 | 7.9 | −112 * | −178 | no |

| [10] | 0.25 | Balanced Colpitts | 6/180 | 9.92 | −136 | −193 | no |

| [14] | - | Push-push | 15/600 | 9.1 | −130 | −181 | no |

| [15] | 0.25 | Common source | 10/600 | 9.9 | −135 | −187 | no |

| [16] | 0.25 | Common gate | 30/10625 | 9.55 | −115.0 | −154.0 | no |

| [17] | 0.25 | Cross-coup | 0.4/2.669 | 4.746 | −121.77 | −191.03 | no |

| [18] | 0.25 | Bal Colpitts Osc | 15/600 | 8.6 | −102 | −172.9 | no |

| [19] | 0.25 | Cross-Coupled VCO | -/747 | 23.9–24.4 | −109.4 | −168.3 | no |

| [20] | - | Osc (on-board) | 28/4.9 | 2.44 | −123.1 | −164.03 | no |

| This 1 | 0.25 | feedback | 0.8/2.45 | 8.86 | −124.8 | −199.8 | no |

| This 2 | 0.25 | LH feedback | 1.6/31.36 | 3.818 | −131.73 | −188.4 | no |

| This 3 | 0.12 | Cross-Coupled Osc | 1.3/9.373 | 6.397 | −123.688 | −190.09 | yes |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Jang, S.-L.; Huang, C.-Y.; Yang, T.C.; Lu, C.-T. GaN HEMT Oscillators with Buffers. Micromachines 2025, 16, 869. https://doi.org/10.3390/mi16080869

Jang S-L, Huang C-Y, Yang TC, Lu C-T. GaN HEMT Oscillators with Buffers. Micromachines. 2025; 16(8):869. https://doi.org/10.3390/mi16080869

Chicago/Turabian StyleJang, Sheng-Lyang, Ching-Yen Huang, Tzu Chin Yang, and Chien-Tang Lu. 2025. "GaN HEMT Oscillators with Buffers" Micromachines 16, no. 8: 869. https://doi.org/10.3390/mi16080869

APA StyleJang, S.-L., Huang, C.-Y., Yang, T. C., & Lu, C.-T. (2025). GaN HEMT Oscillators with Buffers. Micromachines, 16(8), 869. https://doi.org/10.3390/mi16080869