Design and TCAD Simulation of GaN P-i-N Diode with Multi-Drift-Layer and Field-Plate Termination Structures

Abstract

1. Introduction

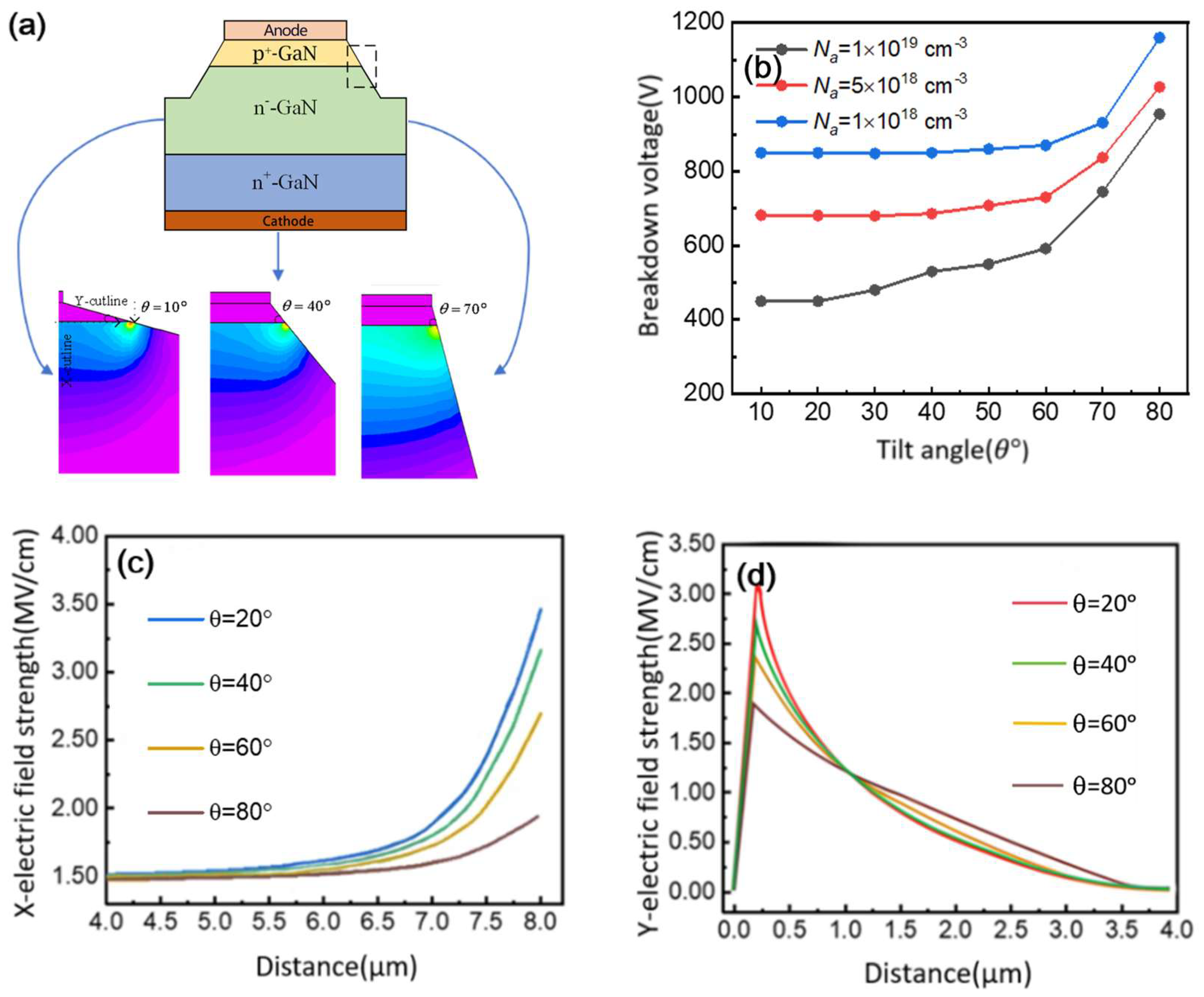

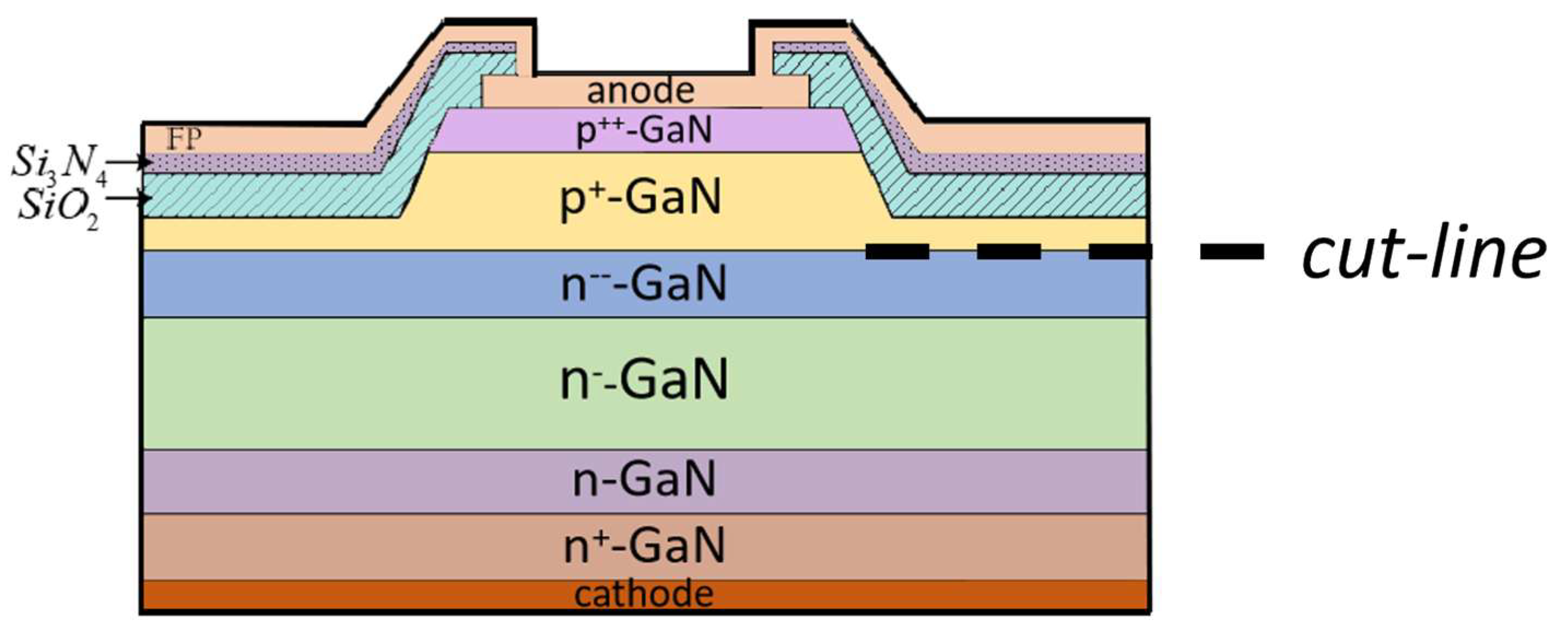

2. Structure Design of Different Mesa Terminals of GaN-Based P-i-N Diodes

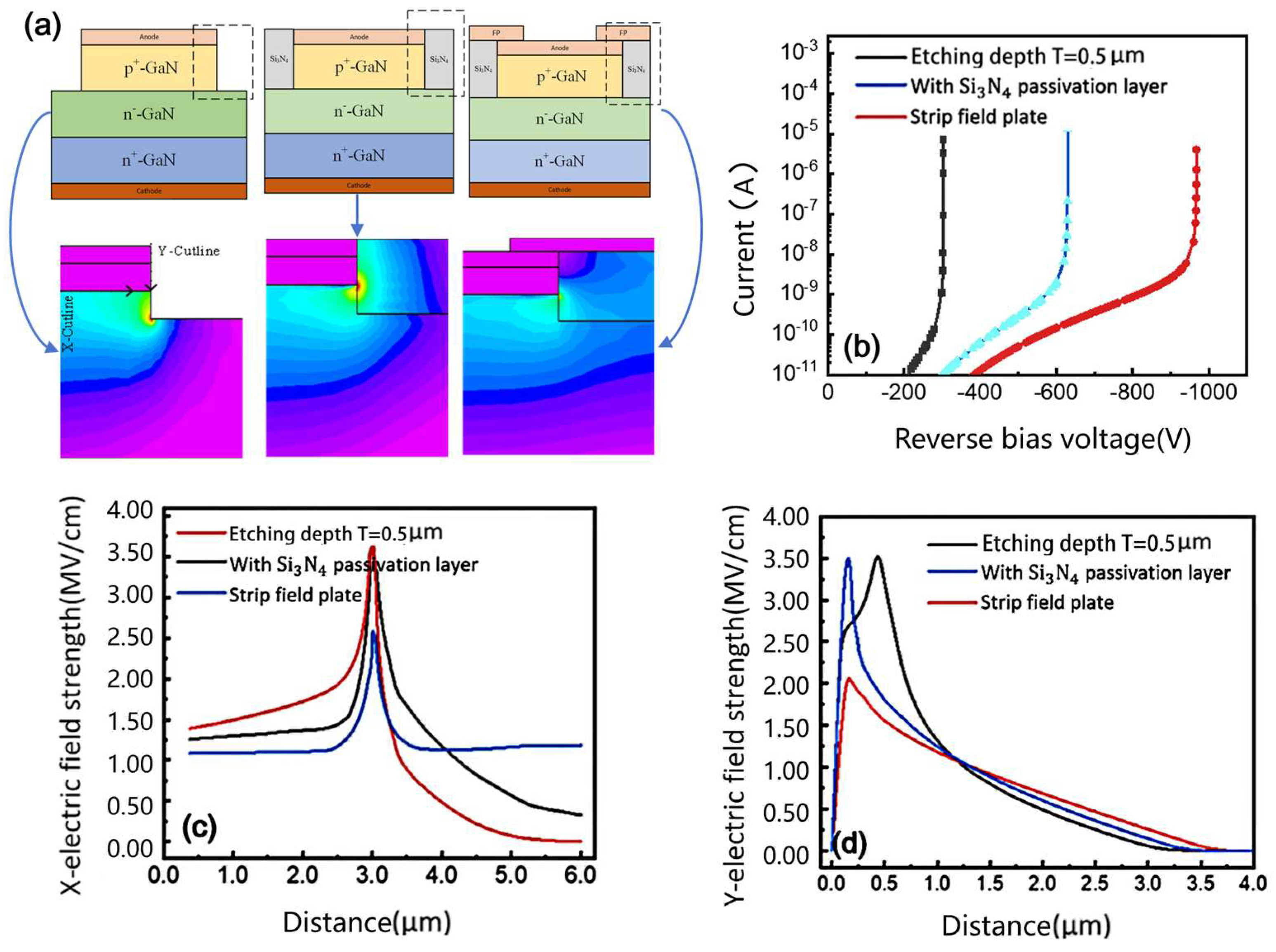

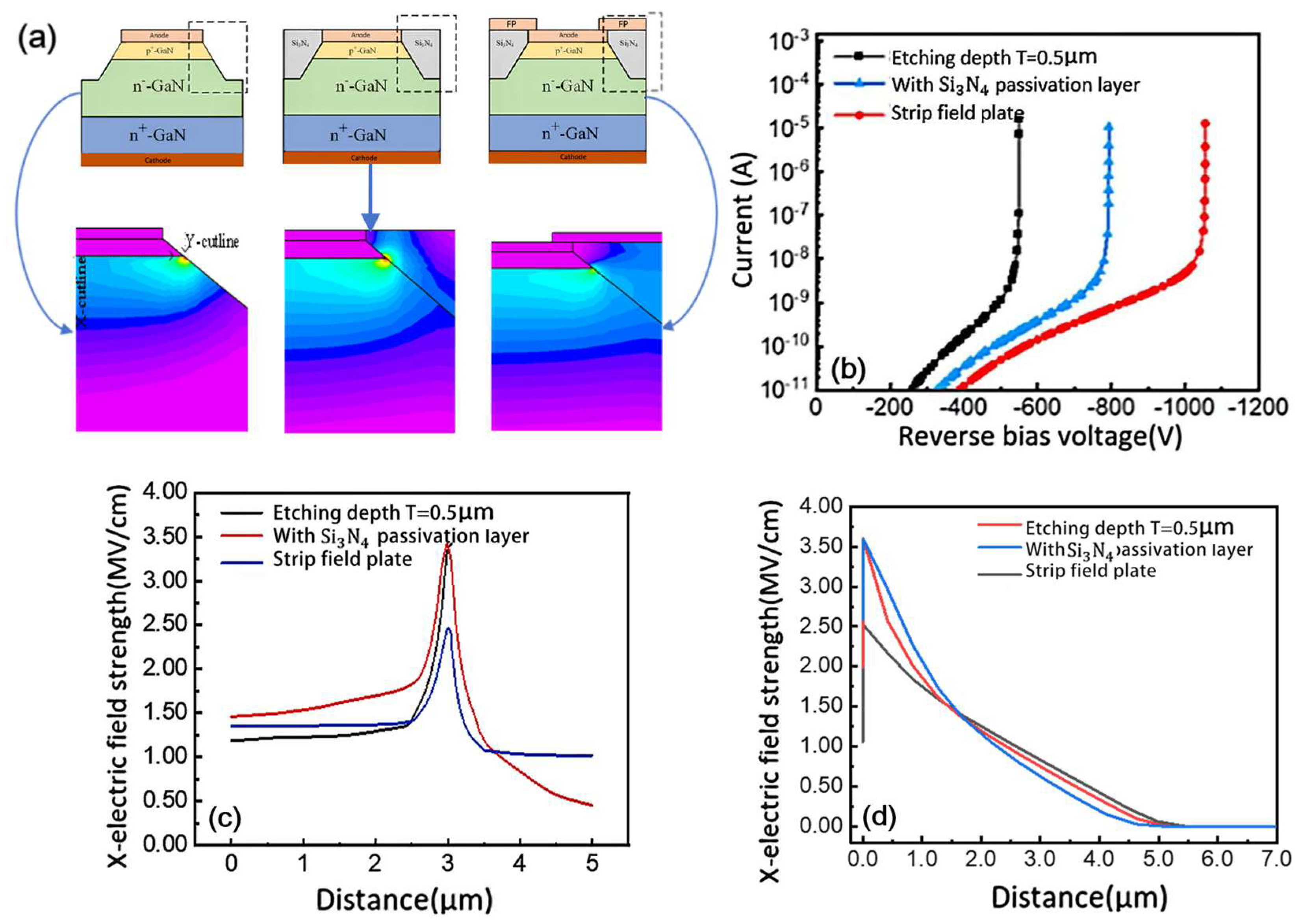

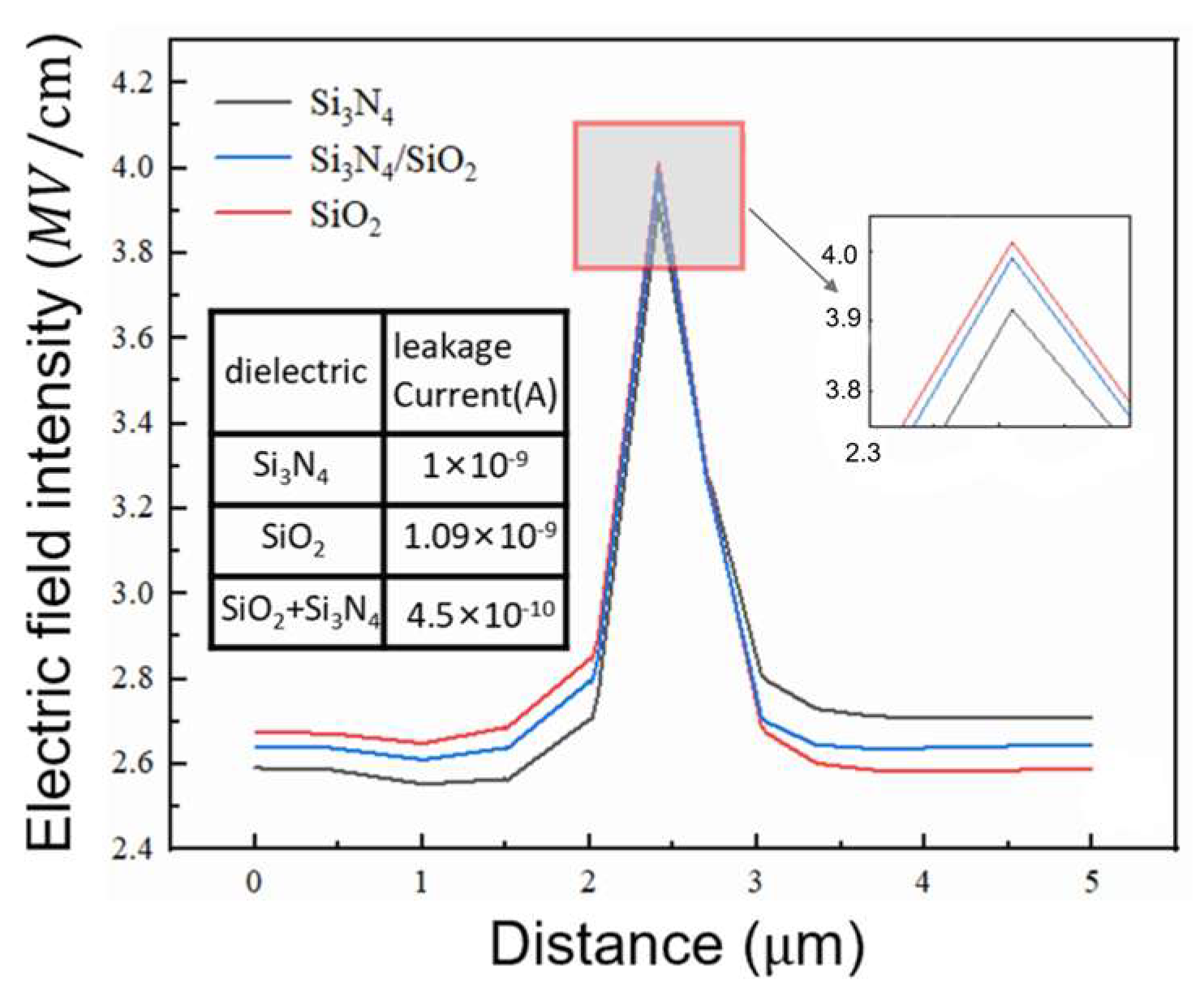

2.1. Simulation Analysis of Different Terminal Structures

2.2. Simulation Analysis of Field-Plate Mesa Termination Structure

3. Multi-Drift-Layer Structure Design of GaN-Based P-i-N Diode

3.1. Top P-GaN Region and Bottom N-GaN Region Design

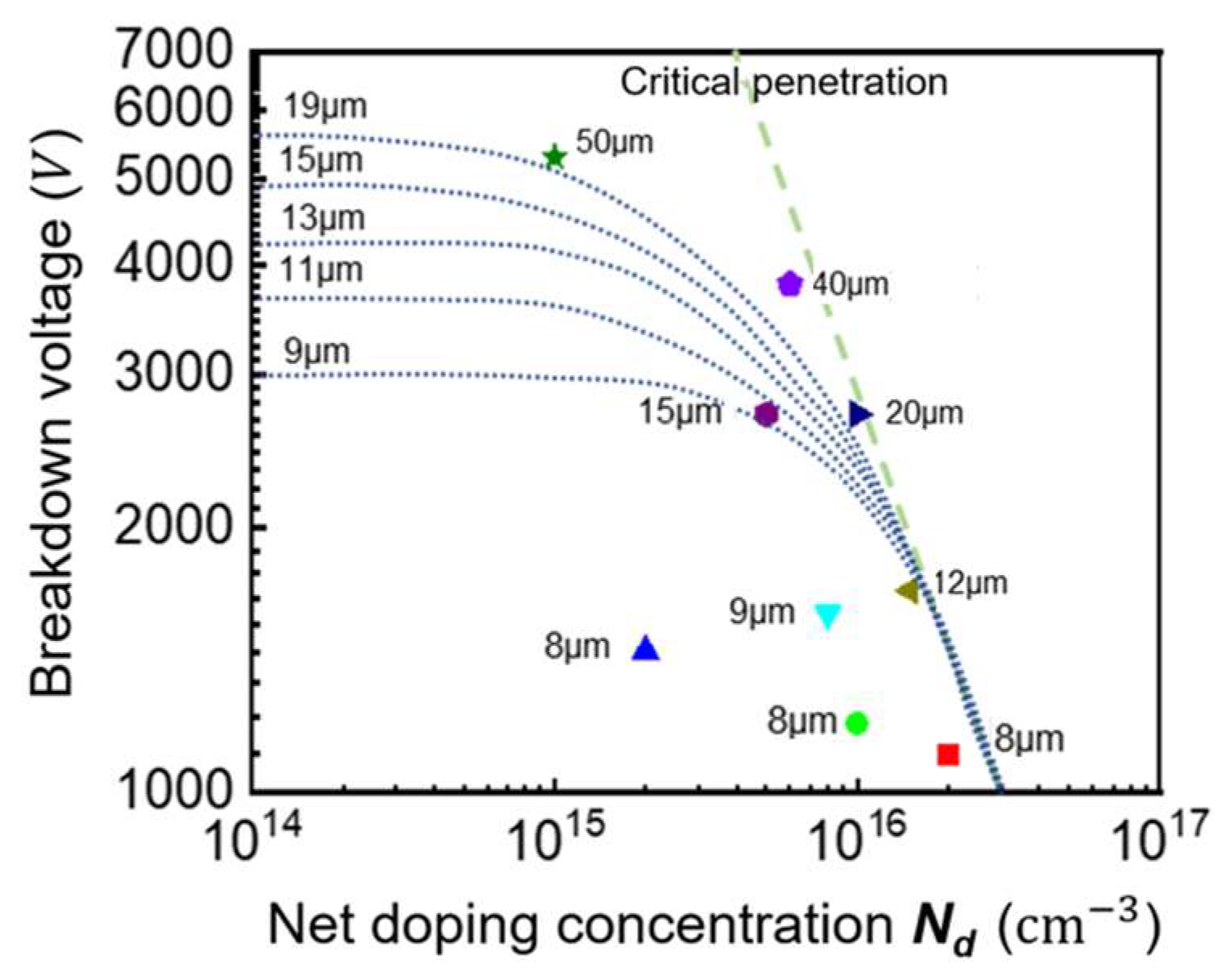

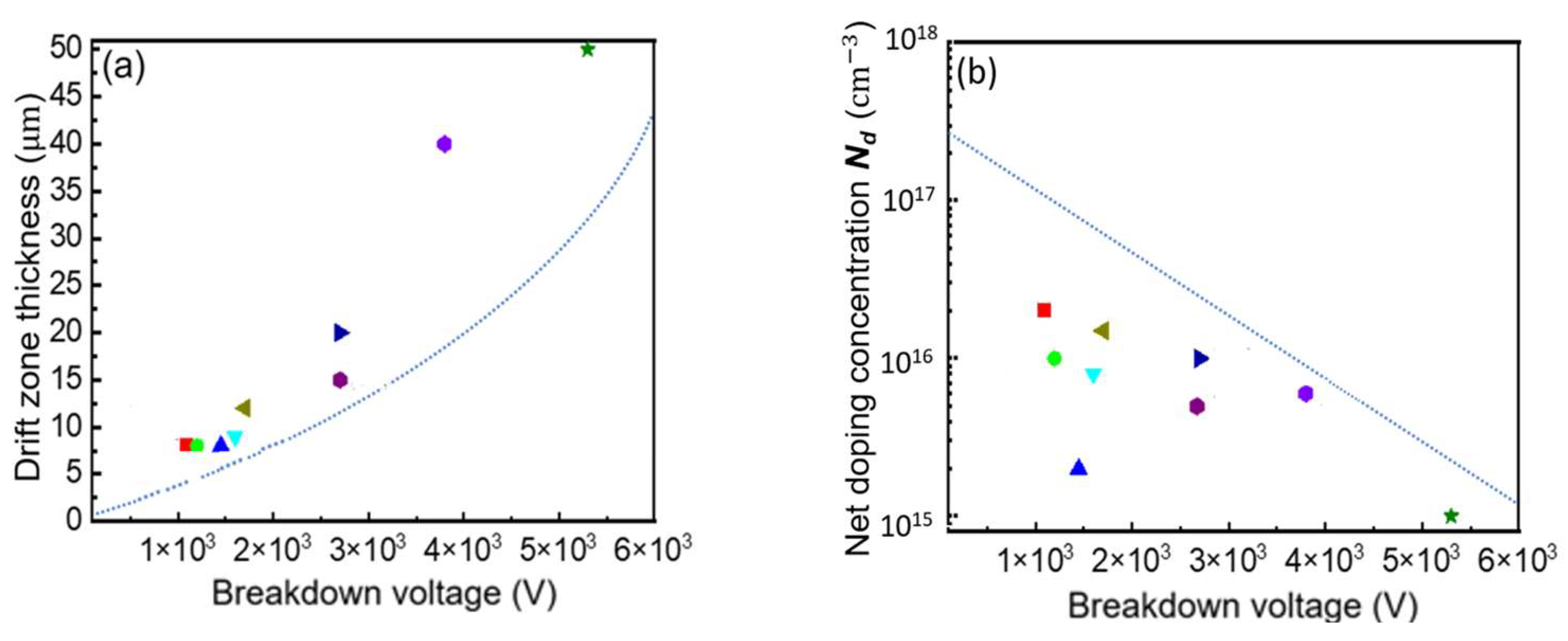

3.2. Drift Region Design

3.3. Device Structure

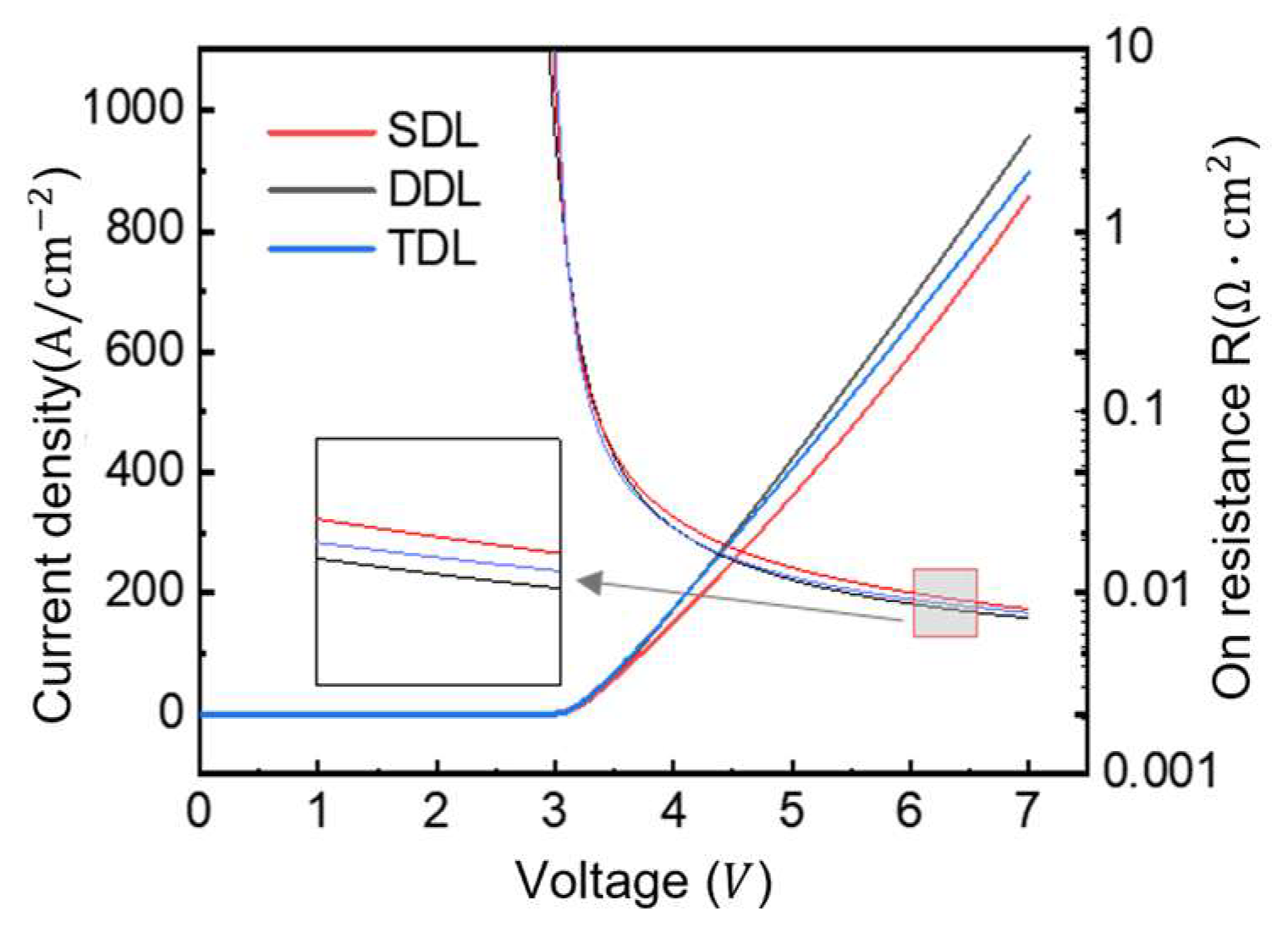

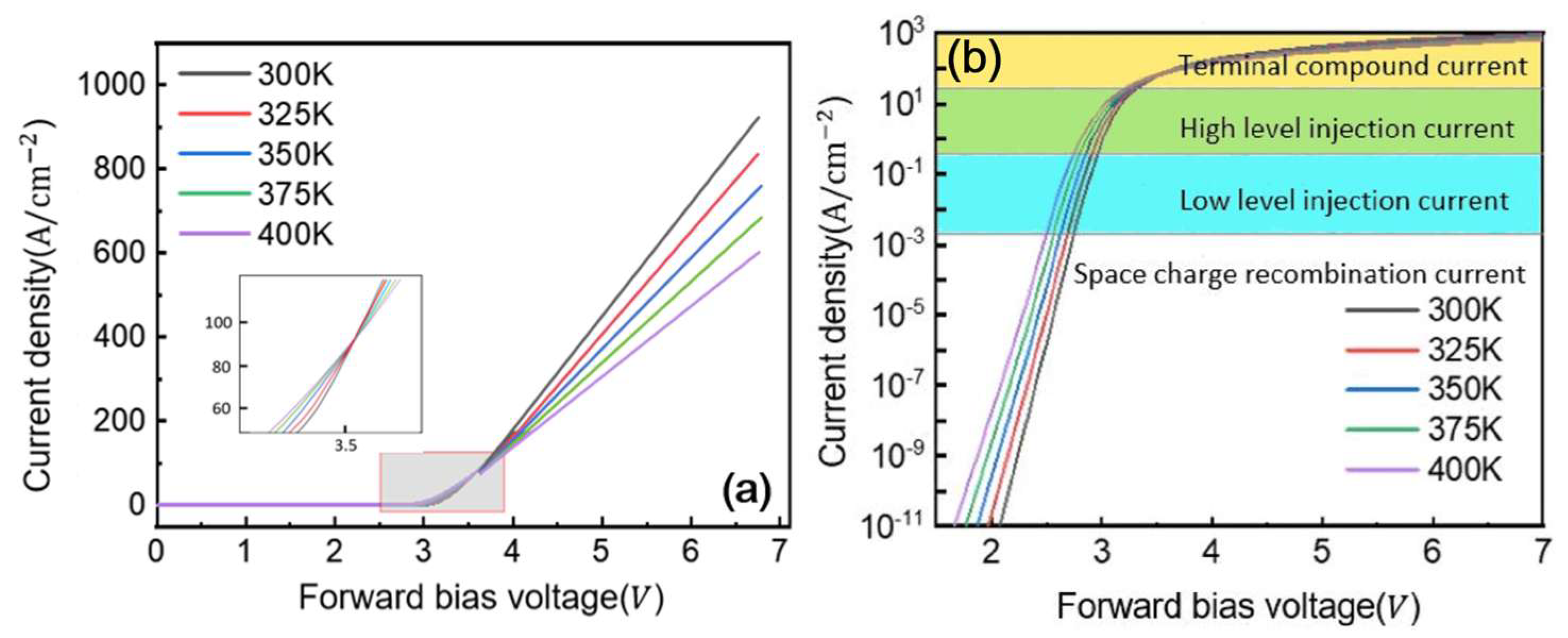

4. Forward Conduction and Conductance Modulation Characteristics of GaN P-i-N Diode

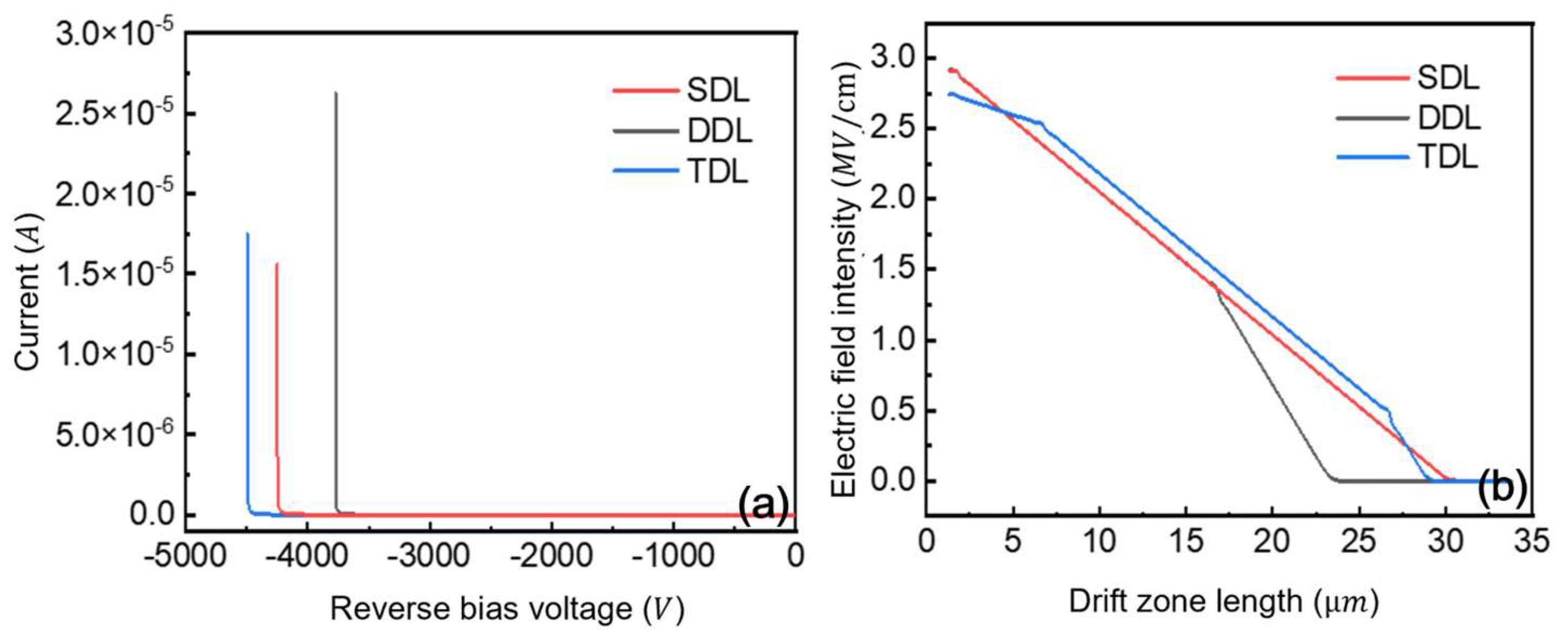

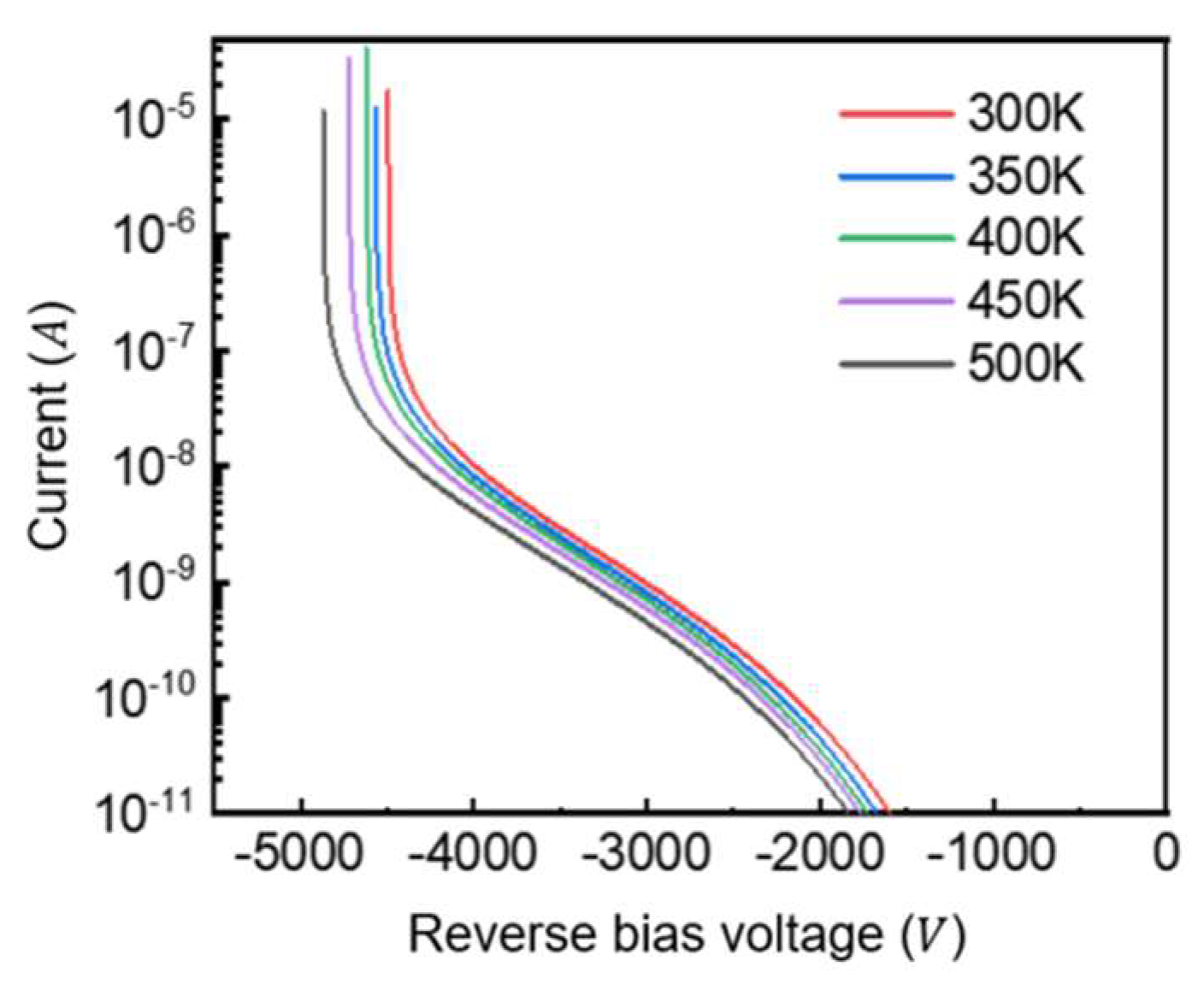

5. Reverse Breakdown Characteristics of GaN-Based P-i-N Diodes

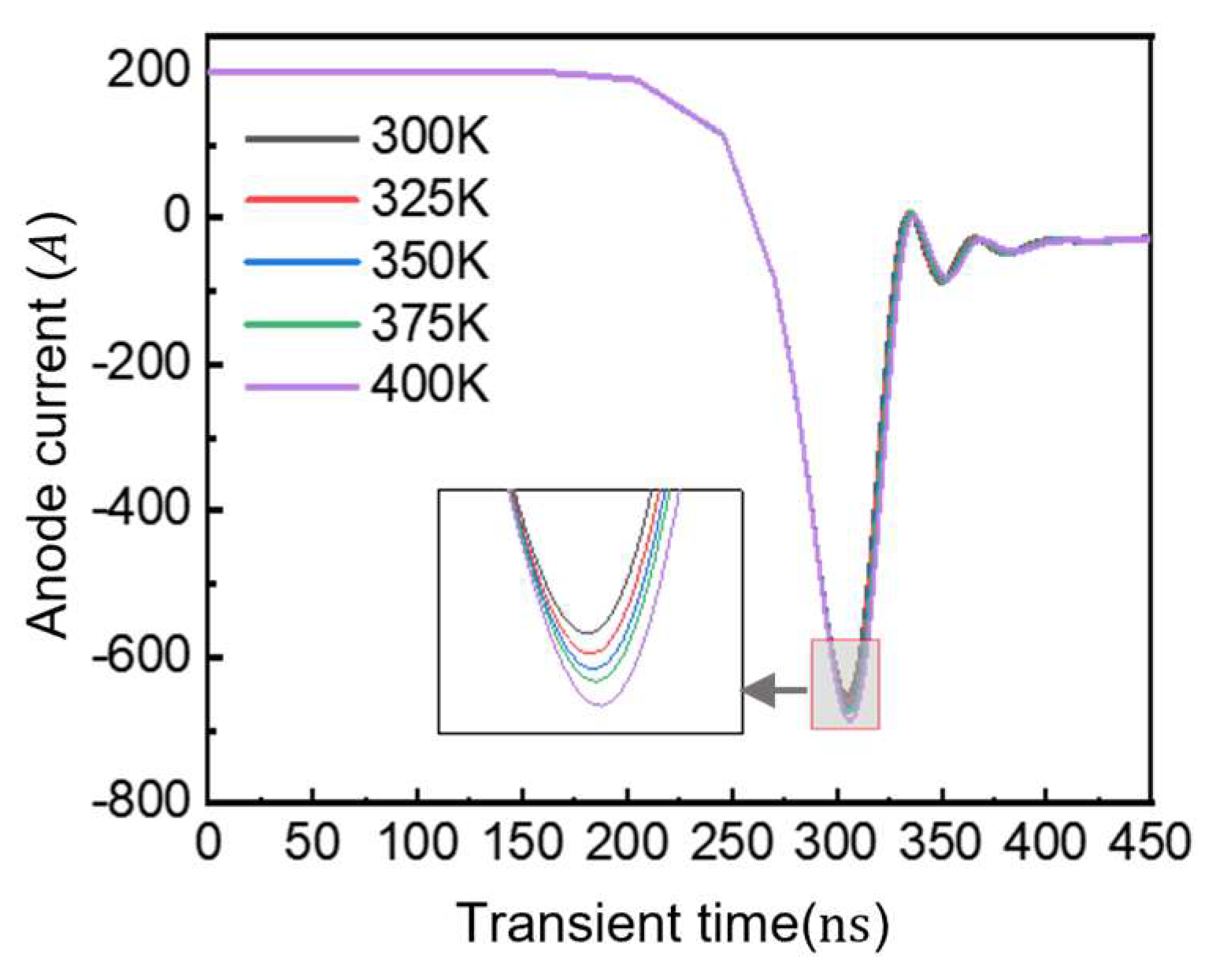

6. GaN-Based P-i-N Diode Switching Characteristics

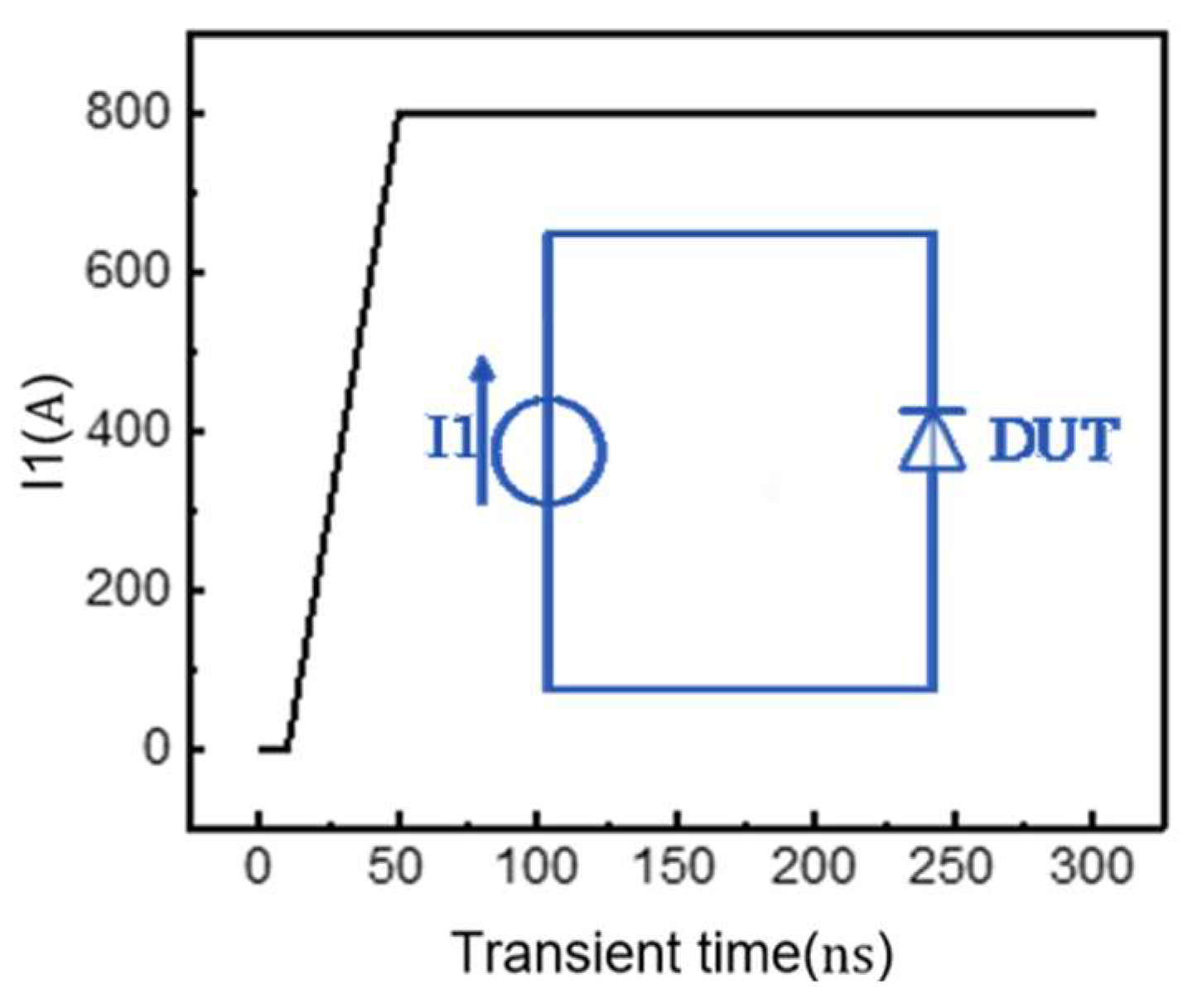

6.1. Forward Recovery Characteristics

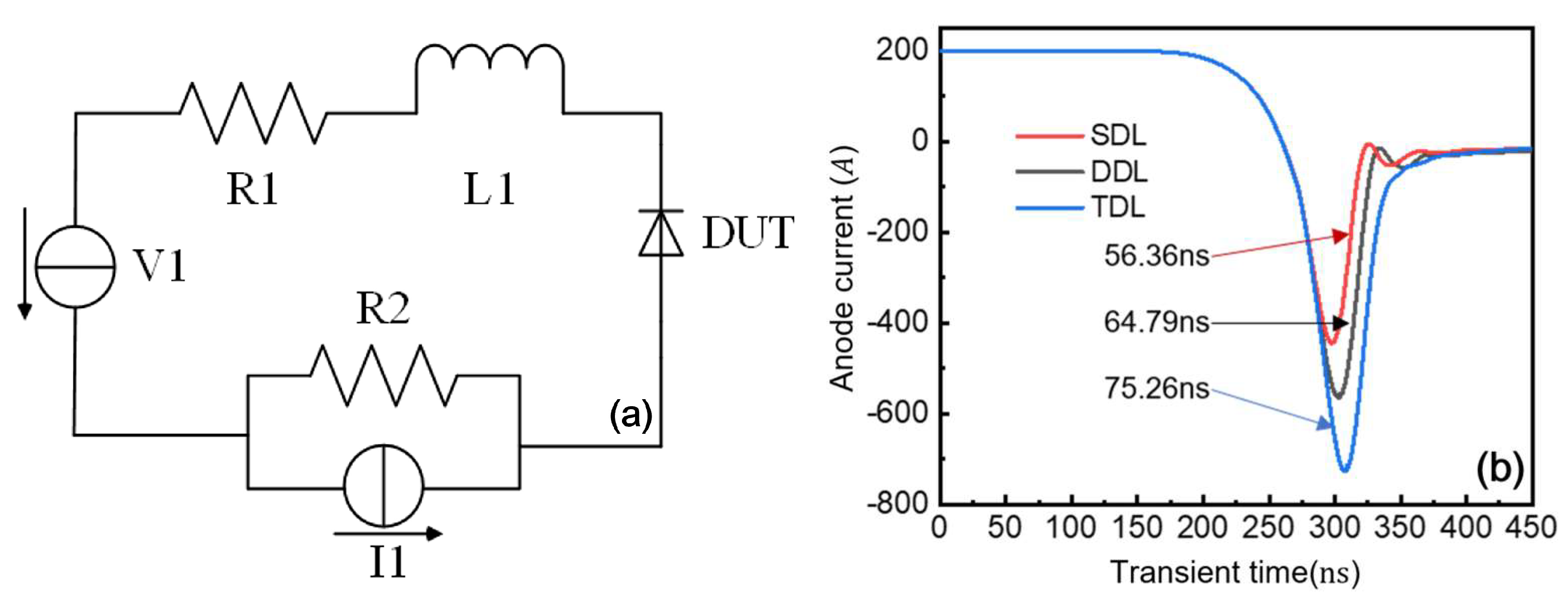

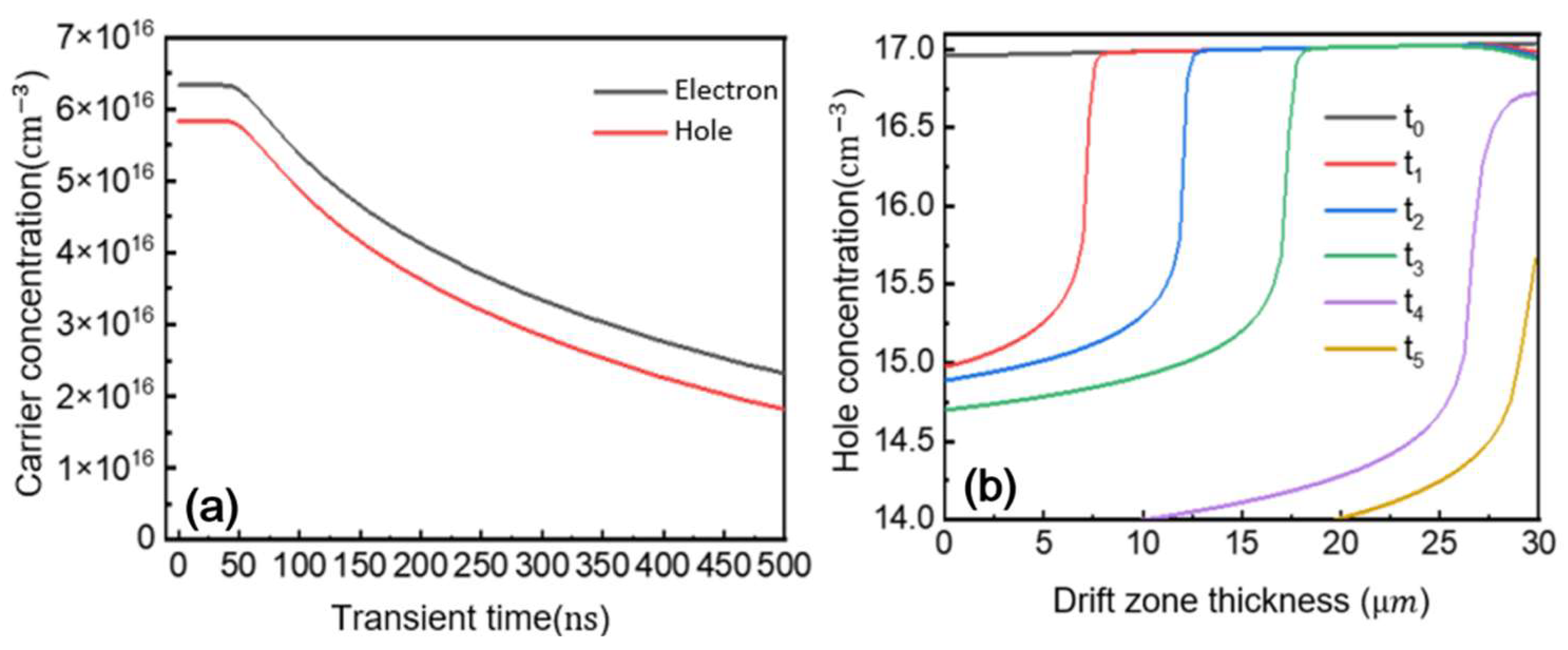

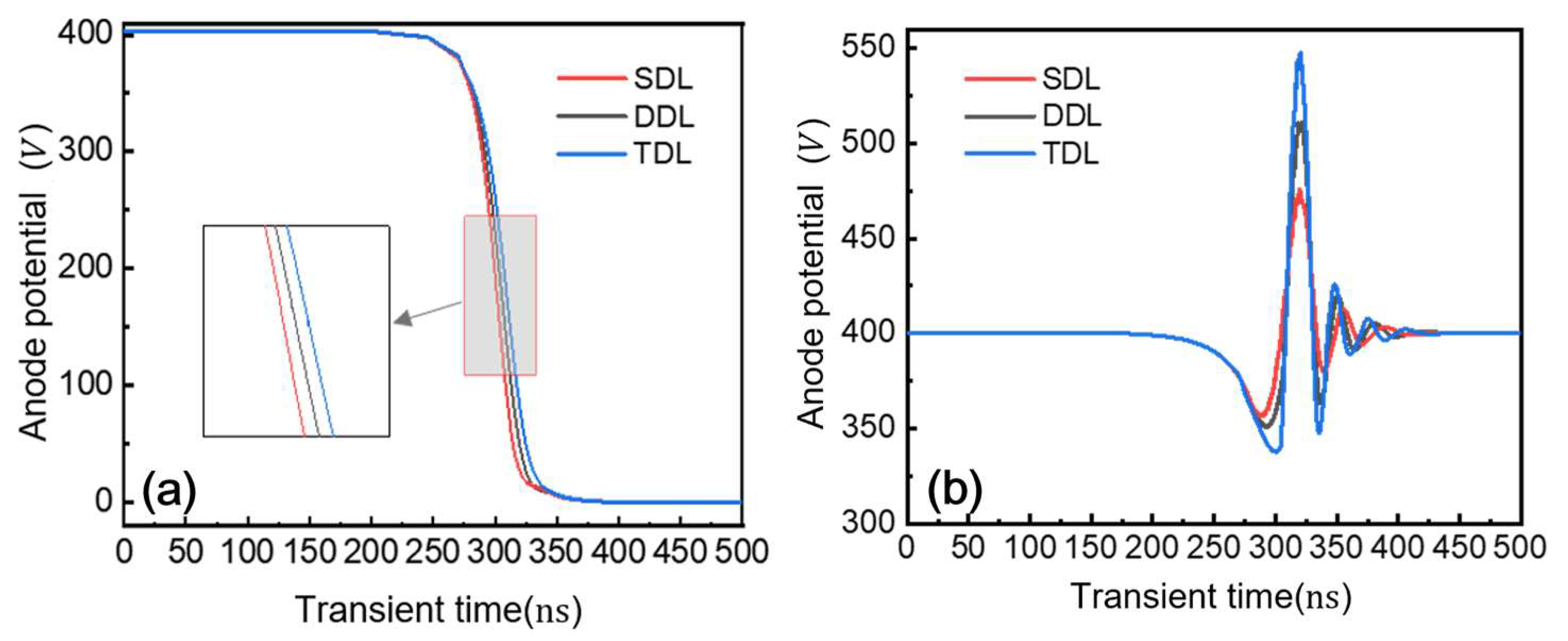

6.2. Reverse Recovery Characteristics

7. Comparison of Simulation Results

8. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Zhang, Y.; Dadgar, A.; Palacios, T. Gallium nitride vertical power devices on foreign substrates: A review and outlook. J. Phys. D Appl. Phys. 2018, 51, 273001. [Google Scholar] [CrossRef]

- Flack, T.J.; Pushpakaran, B.N.; Bayne, S.B. GaN technology for power electronic applications: A review. J. Electron. Mater. 2016, 45, 2673–2682. [Google Scholar] [CrossRef]

- Chowdhury, S.; Mishra, U.K. Lateral and vertical transistors using the AlGaN/GaN heterostructure. IEEE Trans. Electron Devices 2013, 60, 3060–3066. [Google Scholar] [CrossRef]

- Amano, H.; Baines, Y.; Beam, E.; Borga, M.; Bouchet, T.; Chalker, P.R.; Charles, M.; Chowdhury, N.; Chu, R.; De Santi, C.; et al. The 2018 GaN power electronics roadmap. J. Phys. D Appl. Phys. 2018, 51, 163001. [Google Scholar] [CrossRef]

- Chowdhury, S.; Swenson, B.L.; Wong, M.H.; Mishra, U.K. Current status and scope of gallium nitride-based vertical transistors for high-power electronics application. Semicond. Sci. Technol. 2013, 28, 074014. [Google Scholar] [CrossRef]

- Zhang, Y.; Sun, M.; Liu, Z.; Piedra, D.; Lee, H.-S.; Gao, F.; Fujishima, T.; Palacios, T. Electrothermal simulation and thermal performance study of GaN vertical and lateral power transistors. IEEE Trans. Electron Devices 2013, 60, 2224–2230. [Google Scholar] [CrossRef]

- Anderson, T.J.; Greenlee, J.D.; Feigelson, B.N.; Hite, J.K.; Kub, F.J.; Mishra, K.D.H. Improved vertical GaN Schottky diodes with ion implanted junction termination extension. ECS J. Solid State Sci. Technol. 2016, 5, Q176. [Google Scholar] [CrossRef]

- Nomoto, K.; Hatakeyama, Y.; Katayose, H.; Kaneda, N.; Mishima, T.; Nakamura, T. Over 1.0 kV GaN p-n junction diodes on free-standing GaN substrates. Phys. Status Solidi (A) 2011, 208, 1535–1537. [Google Scholar] [CrossRef]

- Hatakeyama, Y.; Nomoto, K.; Kaneda, N.; Kawano, T.; Mishima, T.; Nakamura, T. Over 3.0 GW/cm2 Figure-of-Merit GaN pn Junction Diodes on Free-Standing GaN Substrates. IEEE Electron Device Lett. 2011, 32, 1674–1676. [Google Scholar] [CrossRef]

- Ohta, H.; Hayashi, K.; Horikiri, F.; Yoshino, M.; Nakamura, T.; Mishima, T. 5.0 kV breakdown-voltage vertical GaN p–n junction diodes. Jpn. J. Appl. Phys. 2018, 57, 04FG09. [Google Scholar] [CrossRef]

- Sarker, P.; Kelly, F.P.; Landi, M.; Vesto, R.E.; Kim, K. High-Performance GaN Vertical p-i-n Diodes via Silicon Nitride Shadowed Selective-Area Growth and Optimized FGR- and JTE-Based Edge Termination. IEEE J. Electron Devices Soc. 2020, 9, 68–78. [Google Scholar] [CrossRef]

- Sheridan, D.C.; Niu, G.; Merrett, J.N.; Cressler, J.D.; Dufrene, J.B.; Casady, J.B.; Sankin, I. Comparison and Optimization of Edge Termination Techniques for SiC Power Devices. In Proceedings of the 2001 International Symposium on Power Semiconductor Devices & ICs, Osaka, Japan, 7 June 2001; pp. 191–194. [Google Scholar]

- Kim, S.; Seok, O. A Comprehensive Design of Edge Terminations for High—Voltage SiC Devices Utilizing P—Type Epitaxial Layer. J. Electr. Eng. Technol. 2025, 20, 1051–1057. [Google Scholar] [CrossRef]

- Lee, H.S.; Kalarickal, N.K.; Rahman, M.W.; Xia, Z.; Moore, W.; Wang, C. High-permittivity dielectric edge termination for vertical high voltage devices. J. Comput. Electron. 2020, 19, 1538–1545. [Google Scholar] [CrossRef]

- Fu, H.Q.; Fu, K.; Chowdhury, S.; Palacios, T.; Zhao, Y.J. Vertical GaN Power Devices: Device Principles and Fabrication Technologies—Part I. IEEE Trans. Electron Devices 2021, 68, 3200–3211. [Google Scholar] [CrossRef]

- Kizilyalli, I.C.; Edwards, A.P.; Aktas, O.; Prunty, T.; Bour, D. Vertical power pn diodes based on bulk GaN. IEEE Trans. Electron Devices 2014, 62, 414–422. [Google Scholar] [CrossRef]

- Laroche, J.R.; Ren, F.; Baik, K.W.; Pearton, S.J.; Shelton, B.S. Design of edge termination for GaN power Schottky diodes. J. Electron. Mater. 2005, 34, 370–374. [Google Scholar] [CrossRef]

- Hu, Z.; Nomoto, K.; Song, B.; Zhu, M.; Qi, M.; Pan, M.; Gao, X.; Protasenko, V.; Jena, D.; Xing, H.G. Near unity ideality factor and Shockley-Read-Hall lifetime in GaN-on-GaN pn diodes with avalanche breakdown. Appl. Phys. Lett. 2015, 107, 243501. [Google Scholar] [CrossRef]

- Dickerson, J.R.; Allerman, A.A.; Bryant, B.N.; Fischer, A.J.; King, M.P.; Moseley, M.W.; Armstrong, A.M.; Kaplar, R.J.; Kizilyalli, I.C.; Aktas, O.; et al. Vertical GaN power diodes with a bilayer edge termination. IEEE Trans. Electron Devices 2016, 3, 419–425. [Google Scholar] [CrossRef]

- Hu, Z.; Nomoto, K.; Qi, M.; Li, W.; Zhu, M.; Gao, X. 1.1-kV vertical GaN pn diodes with p-GaN regrown by molecular beam epitaxy. IEEE Electron Device Lett. 2017, 38, 1071–1074. [Google Scholar] [CrossRef]

- Wang, J.; Cao, L.; Xie, J.; Beam, E.; McCarthy, R.; Youtsey, C.; Fay, P. High voltage, high current GaN-on-GaN pn diodes with partially compensated edge termination. Appl. Phys. Lett. 2018, 113, 023502. [Google Scholar] [CrossRef]

- Wang, J.; Cao, L.; Xie, J.; Beam, E.; McCarthy, R.; Youtsey, C.; Fay, P. High voltage vertical pn diodes with ion-implanted edge termination and sputtered SiNx passivation on GaN substrates. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 9.6.1–9.6.4. [Google Scholar]

- Kizilyalli, I.C.; Edwards, A.P.; Nie, H.; Disney, D.; Bour, D. High voltage vertical GaN pn diodes with avalanche capability. IEEE Trans. Electron Devices 2013, 60, 3067–3070. [Google Scholar] [CrossRef]

- Yates, L.; Gunning, B.P.; Crawford, M.H.; Steinfeldt, J.; Smith, M.L.; Abate, V.M.; Dickerson, J.R.; Armstrong, A.M.; Binder, A.; Allerman, A.A.; et al. Demonstration of >6.0-kV breakdown voltage in large area vertical GaN pn diodes with step-etched junction termination extensions. IEEE Trans. Electron Devices 2022, 69, 1931–1937. [Google Scholar] [CrossRef]

- Nomoto, K.; Hu, Z.; Song, B.; Zhu, M.; Qi, M.; Yan, R.; Protasenko, V.; Imhoff, E.; Kuo, J.; Kaneda, N.; et al. GaN-on-GaN pn power diodes with 3.48 kV and 0.95 mΩ-cm2: A record high figure-of-merit of 12.8 GW/cm2. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015. [Google Scholar]

- Hatakeyama, Y.; Nomoto, K.; Terano, A.; Kaneda, N.; Tsuchiya, T.; Mishima, T.; Nakamura, T. High-Breakdown-Voltage and Low-Specific-on-Resistance GaN p–n Junction Diodes on Free-Standing GaN Substrates Fabricated Through Low-Damage Field-Plate Process. Jpn. J. Appl. Phys. 2013, 52, 028007. [Google Scholar] [CrossRef]

- Yoshino, M.; Horikiri, F.; Ohta, H.; Yamamoto, Y.; Mishima, T.; Nakamura, T. High-k Dielectric Passivation for GaN Diode with a Field Plate Termination. Electronics 2016, 5, 15. [Google Scholar] [CrossRef]

| Material/Model | Property | Value |

|---|---|---|

| GaN | Bandgap (eV) | 3.43 |

| Electron affinity (eV) | 4.1 | |

| Dielectric constant | 8.9 | |

| Effective Conduction Band Density of states (cm−3) | 2.24 × 1018 | |

| Effective Valence Band Density of states (cm−3) | 2.51 × 1019 | |

| Impact Ionization | an1/2 (cm−1) | 2.52 × 108 |

| bn1/2 (V/cm) | 3.41 × 107 | |

| ap1/2 (cm−1) | 5.37 × 106 | |

| bp1/2 (V/cm) | 1.96 × 107 | |

| Incomplete Ionization | Donor Activation Energy (ΔED) (meV) | 17 |

| αn (eV.cm) | 3.4 × 10−9 | |

| Acceptor Activation Energy (ΔEA) (meV) | 240 | |

| αp (eV.cm) | 1.15 × 10−9 | |

| SRH Recombination | Electron Lifetime (τn) | 1.2 × 10−8 |

| Hole Lifetime (τp) | 1.2 × 10−8 | |

| Auger Recombination | Electron Coefficient (cm6∙s) | 2.8 × 10−31 |

| Hole Coefficient (cm6∙s) | 9.9 × 10−32 |

| Structural | DCR | SDL | DDL | TDL |

|---|---|---|---|---|

| p++-GaN | >1 × 1019 cm−3 | 1 × 1020 cm−3/10 nm | 1 × 1020 cm−3/10 nm | 1 × 1020 cm−3/10 nm |

| P+-GaN | 1 × 1018~1 × 1019 cm−3 | 2 × 1018 cm−3/500 nm | 2 × 1018 cm−3/500 nm | 2 × 1018 cm−3/500 nm |

| n−−-GaN | <5 × 1015 cm−3 | — | — | 2 × 1015 cm−3/5 µm |

| n−-GaN | 5 × 1015~ 1 × 1016 cm−3 | 5 × 1015 cm−3/30 µm | 5 × 1015 cm−3/15 µm | 5 × 1015 cm−3/20 µm |

| n-GaN | 1 × 1016~ 1 × 1018 cm−3 | — | 1 × 1016 cm−3/15 µm | 1 × 1016 cm−3/5 µm |

| n+-GaN | 1 × 1018~1 × 1019 cm−3 | 2 × 1018 cm−3/2 µm | 2 × 1018 cm−3/2 µm | 2 × 1018 cm−3/2 µm |

| Structural and Performance Parameters | This Work | Ref. [22] | Ref. [24] | Ref. [25] |

|---|---|---|---|---|

| Terminal technology type | Field plate | Ion implantation | Junction terminal extension | Field plate |

| Drift region length (µm) | 5/20/5 | 8 | 50 | 6/11/15 |

| Doping concentration in drift region (cm−3) | 2 × 1015/5 × 1015 /1 × 1016 | 1 × 1016 | <1 × 1015 | 1 × 1015/3 × 1015 /1.2 × 1016 |

| Breakdown voltage VB (V) | 4494 | 1200 | 6400 | 3500 |

| On-resistance Ron (mΩ·cm2) | 7.81 | 0.11 | 10.2 | 0.95 |

| Substrate type | Bulk GaN | Bulk GaN | Bulk GaN | Bulk GaN |

| Fabrication technology | MOCVD | MOCVD | Solid-assisted separation | Hydride vapor phase epitaxy |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Yang, Z.; Wang, G.; Wang, Y.; Mao, P.; Ye, B. Design and TCAD Simulation of GaN P-i-N Diode with Multi-Drift-Layer and Field-Plate Termination Structures. Micromachines 2025, 16, 839. https://doi.org/10.3390/mi16080839

Yang Z, Wang G, Wang Y, Mao P, Ye B. Design and TCAD Simulation of GaN P-i-N Diode with Multi-Drift-Layer and Field-Plate Termination Structures. Micromachines. 2025; 16(8):839. https://doi.org/10.3390/mi16080839

Chicago/Turabian StyleYang, Zhibo, Guanyu Wang, Yifei Wang, Pandi Mao, and Bo Ye. 2025. "Design and TCAD Simulation of GaN P-i-N Diode with Multi-Drift-Layer and Field-Plate Termination Structures" Micromachines 16, no. 8: 839. https://doi.org/10.3390/mi16080839

APA StyleYang, Z., Wang, G., Wang, Y., Mao, P., & Ye, B. (2025). Design and TCAD Simulation of GaN P-i-N Diode with Multi-Drift-Layer and Field-Plate Termination Structures. Micromachines, 16(8), 839. https://doi.org/10.3390/mi16080839