A Multimodal CMOS Readout IC for SWIR Image Sensors with Dual-Mode BDI/DI Pixels and Column-Parallel Two-Step Single-Slope ADC

Abstract

1. Introduction

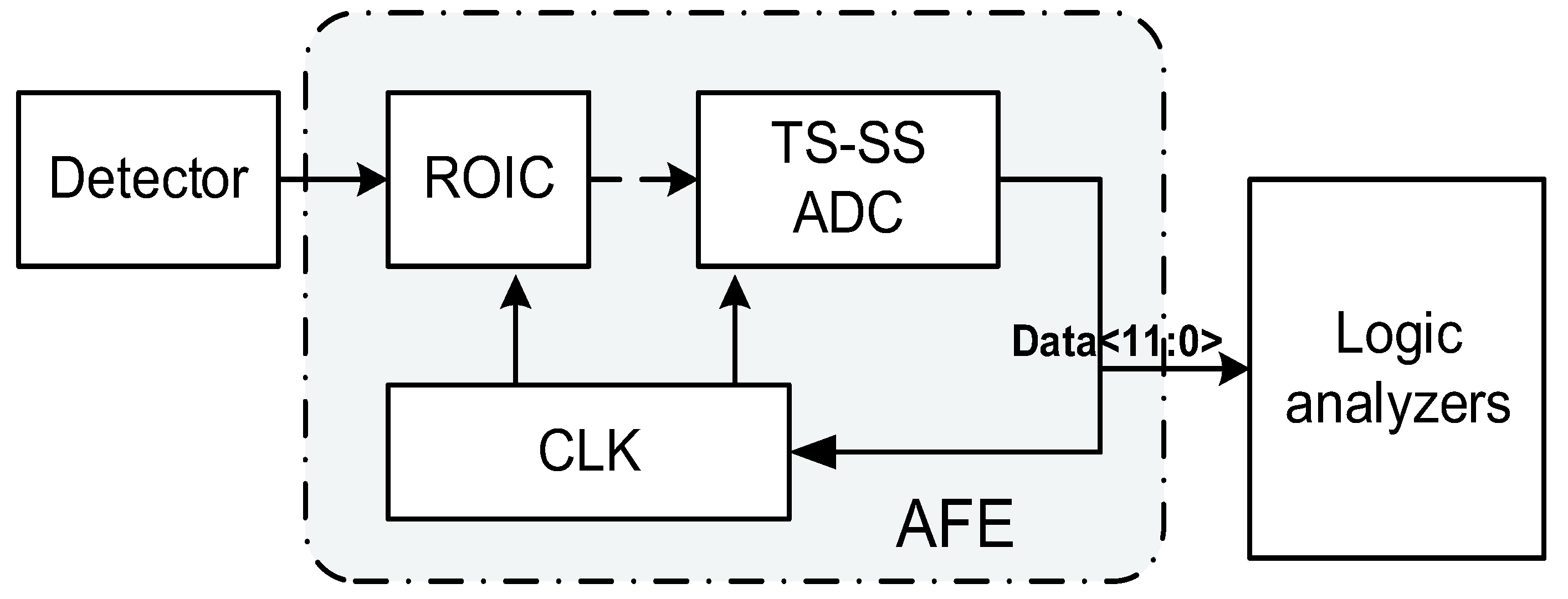

2. System Architecture

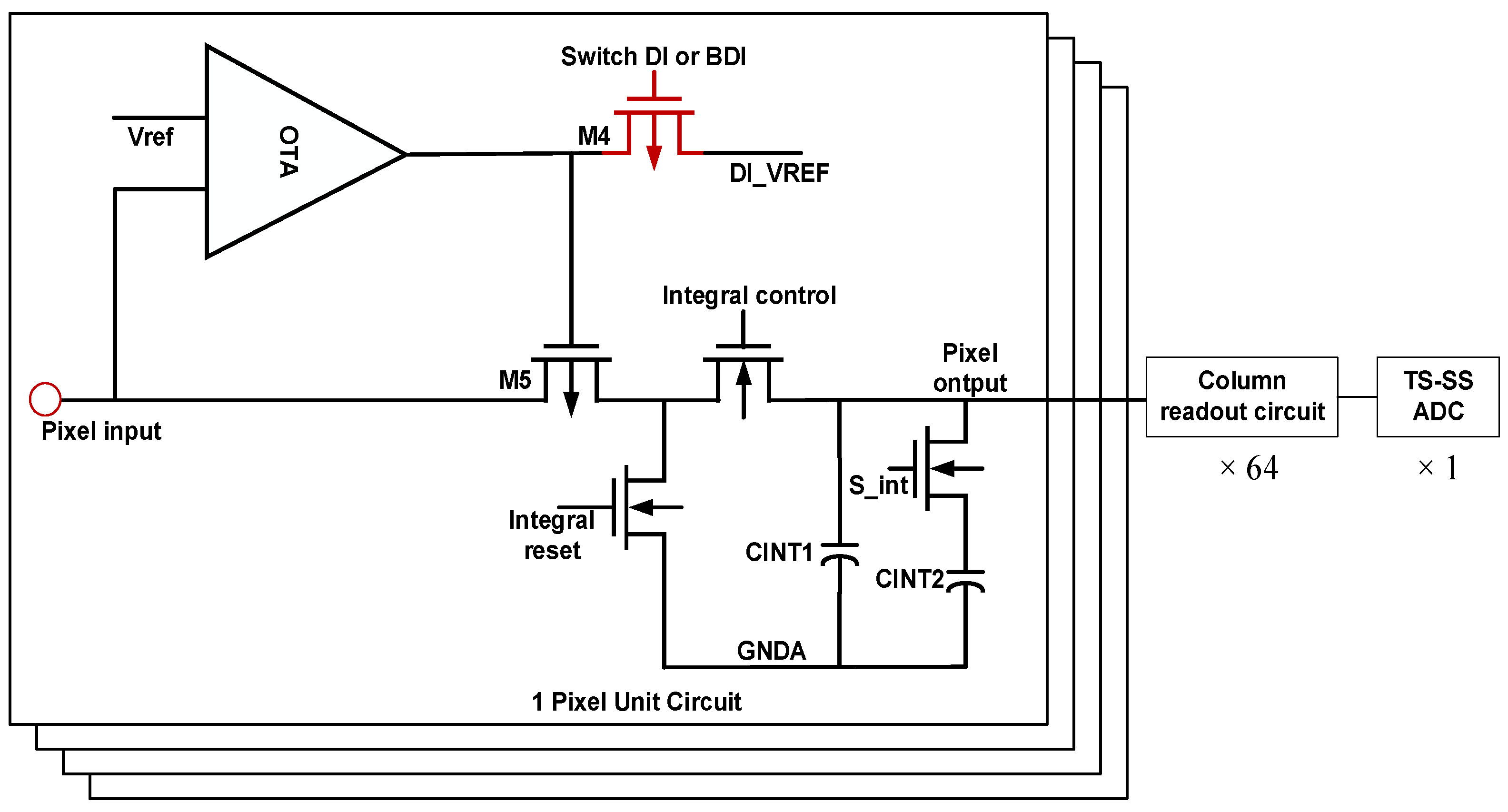

2.1. Analog Front-End with Dual-Mode

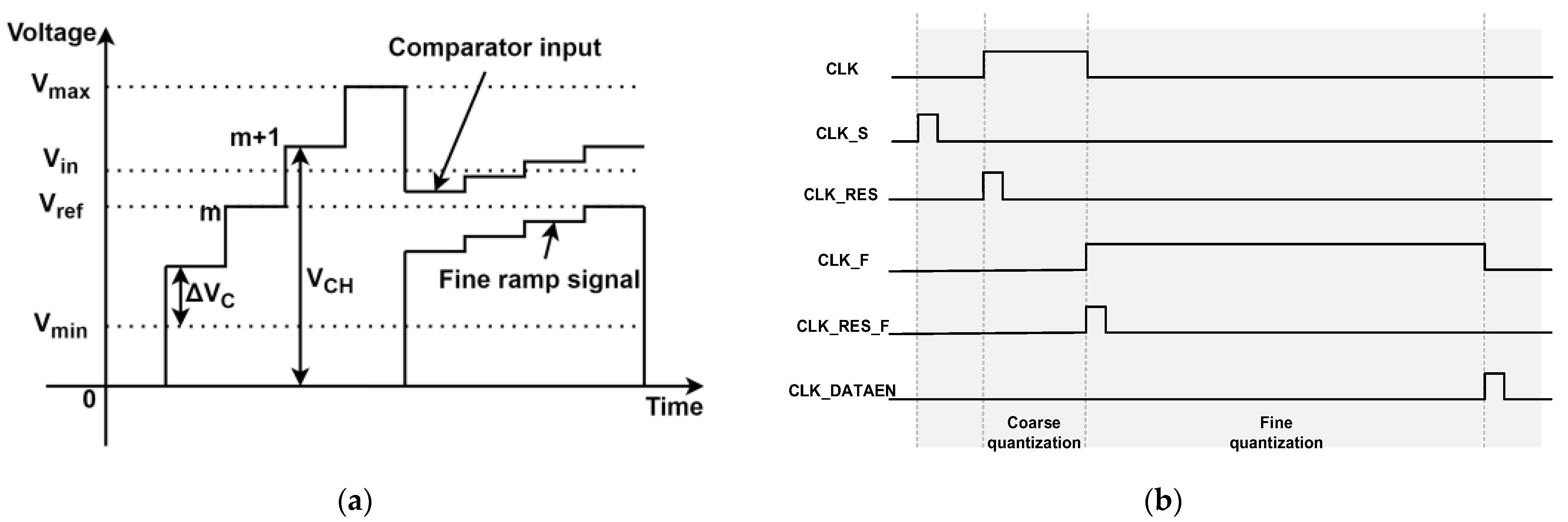

2.2. TS-SS ADC Design

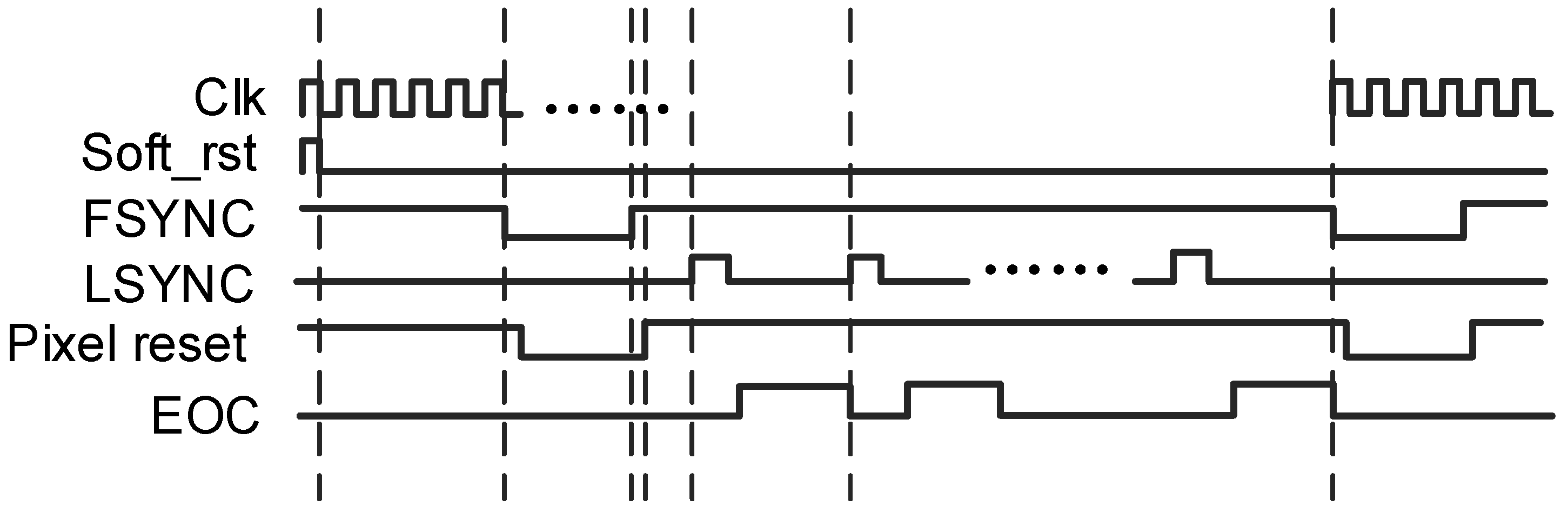

2.3. Digital Timing Control

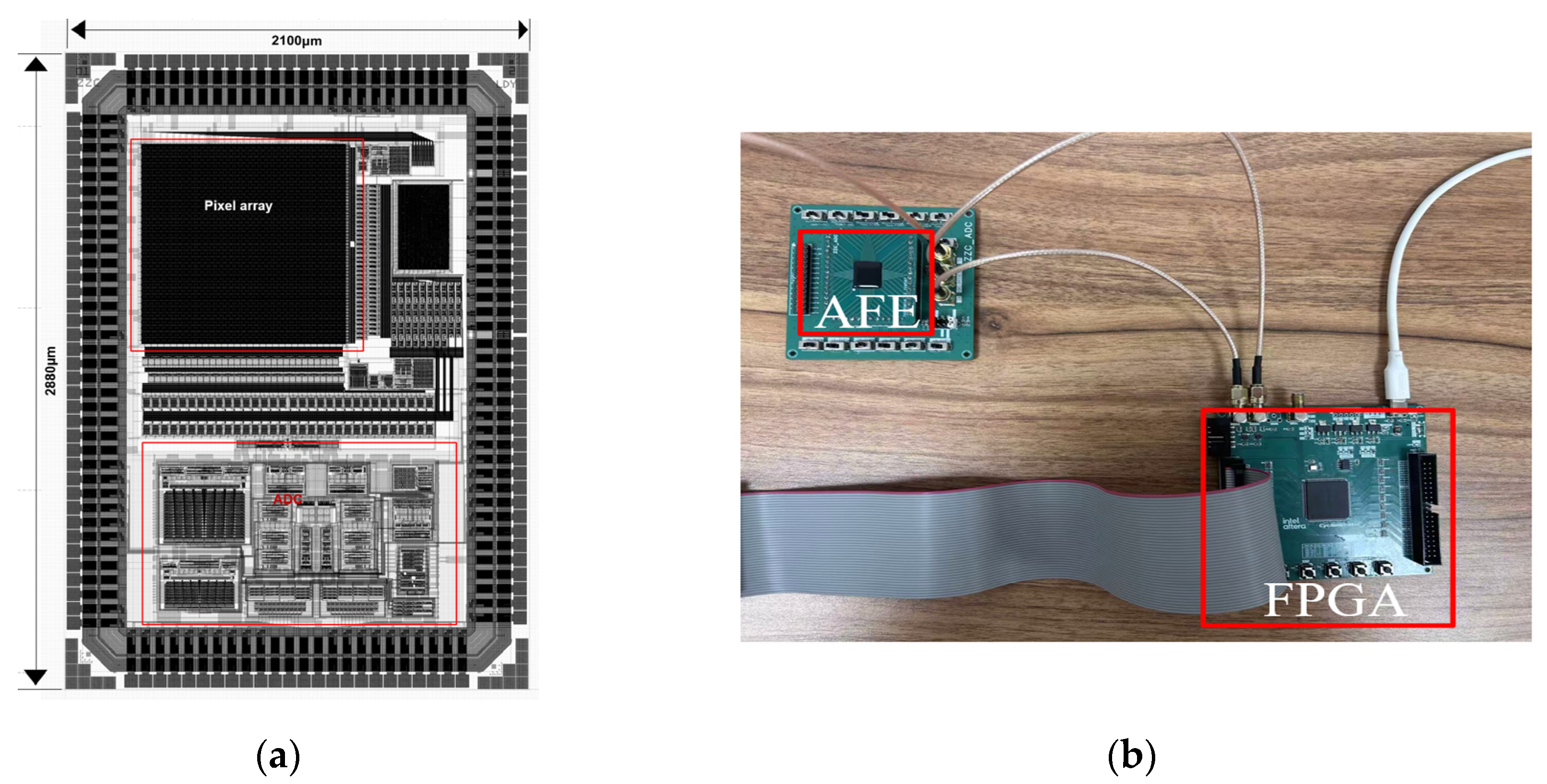

3. Silicon-Based ROIC Design

3.1. Dual-Mode Pixel Injection Structure

3.2. Transconductance and Injection Efficiency

- Injection Efficiency in BDI/DI Modes:

4. Silicon-Based ADC Design

4.1. Four-Terminal Comparator Architecture

- First Stage—Differential Difference Amplifier: Provides high open-loop gain and common-mode rejection, enabling accurate resolution of small voltage differences during both coarse and fine quantization. Figure 7b depicts a partial transistor-level schematic of the four-terminal dynamic comparator. The core employs a cross-coupled NMOS latch with PMOS active loads. Two auxiliary switches momentarily tie the storage capacitor CH to the latch tail during reset, canceling kick-back.

- Second Stage—Diode-Loaded Inverter: Offers high-speed signal regeneration with minimal propagation delay, ensuring rapid latching behavior at the threshold crossing.

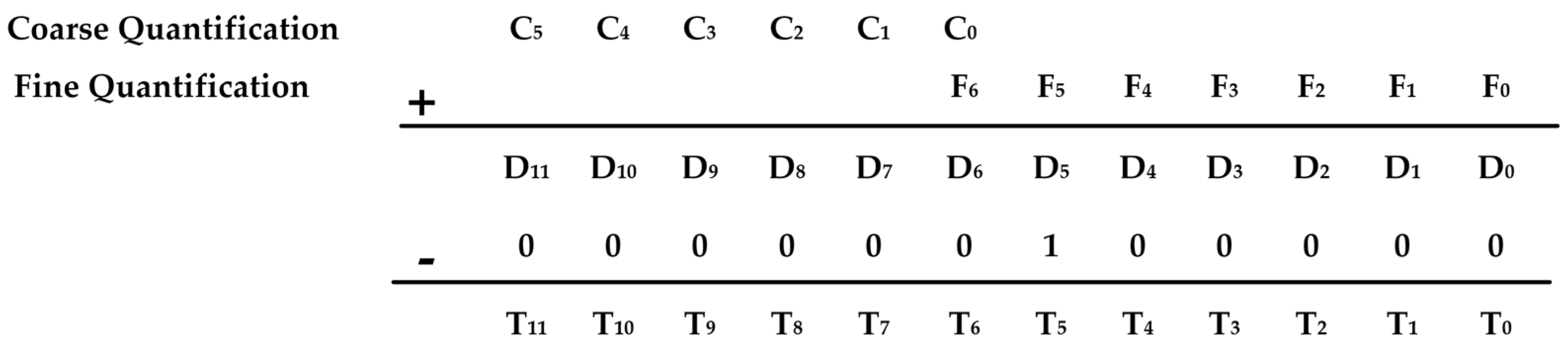

4.2. Quantization Scheme with Redundant Bit Allocation

- Coarse Phase: A 6-bit counter generates a globally distributed voltage ramp, enabling parallel acquisition of the most significant bits (MSBs) across all columns. This ramp resolves the voltage to a 64-level approximation.

- Fine Phase: A higher-resolution ramp is applied to the fine quantization stage, covering a dynamic range of 2ΔV to fully span the residue from the coarse stage. To account for transition errors, the fine ramp includes one extra redundant bit.

- Digital Correction: Post-processing logic combines the coarse and fine quantization results. As shown in Figure 9, an adder aligns the fine MSB with the coarse result, and a subtractor removes a fixed digital offset introduced by the redundancy, yielding a final 12-bit output with minimized DNL.

- Simulation and silicon measurements demonstrate that the proposed scheme suppresses non-monotonicity and reduces worst-case DNL to below 0.2 least significant bits (LSB), even in the presence of offset voltage mismatch and charge redistribution.

4.3. Switch Charge Injection Compensation

4.4. ADC Timing and Control Strategy

- Sampling Phase: The pixel output voltage is sampled and held (CLK_S high);

- Coarse Quantization Phase: The 6-bit counter generates VCoarse (CLK high), resolving MSBs within 64 cycles;

- Fine Quantization Phase: A 7-bit counter drives Vfine (CLK_F high), with redundancy and DAC compensation refining the least significant bits (LSBs);

- All transitions are synchronized to a 20 MHz master clock and governed by global synchronization signals (LSYNC, FSYNC), ensuring deterministic latency and pipeline compatibility. The entire column-parallel array can thus operate in parallel without temporal skew, enabling real-time readout of high-resolution frames. A foreground redundancy-based calibration removes coarse-stage transition errors, while the on-chip PLL offers background time-base calibration that trims the fine-ramp slope to <0.05% error.

4.5. Charge-Injection Compensation DAC

5. Experimental Results

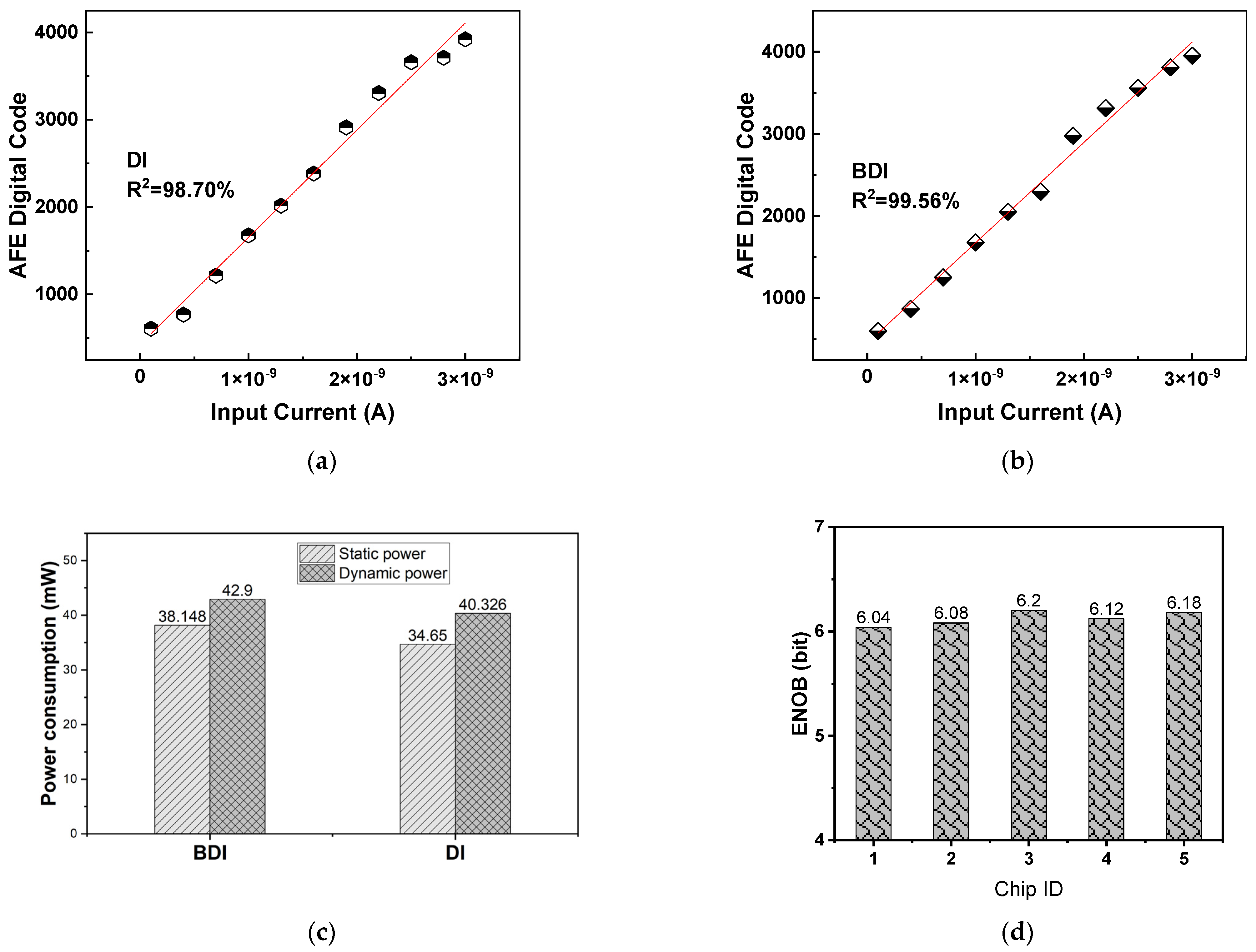

5.1. ROIC Performance

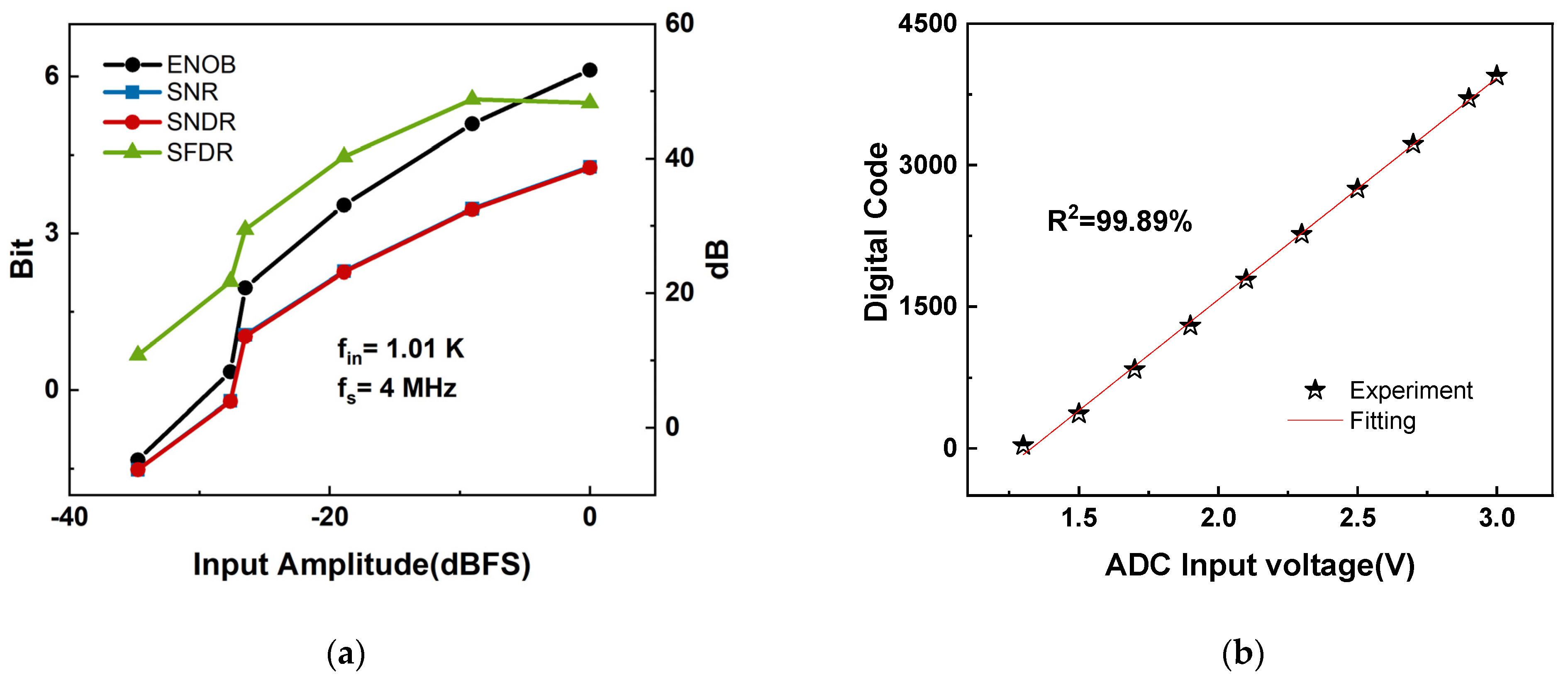

5.2. ADC Performance Evaluation

- Residual fine-ramp distortion due to second-order parasitic leakage around CH even after the four-terminal comparator decoupling, shortening the effective LSB range and degrading SNR.

- Clock-edge jitter of 18 ps rms propagates to 0.55 LSB timing uncertainty during the 7-bit fine ramp, removing ~0.4 bits.

- Board-level parasitics further reduce the measured ENOB: (i) supply noise contributes 0.6 bits per IEEE Std-1241 SNR scaling; (ii) ramp-line capacitance increases the effective LSB by 0.5 LSB. These losses are extrinsic and will be mitigated by a six-layer PCB with isolated analog grounds, on-board LDO filtering, differential ramp routing, and an aluminum enclosure. The output digital code of the ADC was tested with an incremental voltage step of 0.1 V. Each voltage generates 4096 digital codes, and the average value of the digital codes is taken to fit the line that coincides with the scatter plot. The four-terminal comparator eliminates charge leakage, achieving 99.89% linear ramp slope accuracy, as shown in Figure 12b. The architecture achieves 4220 fJ/conv-step (ADC-core) while offering dual-mode BDI/DI flexibility at the system level.

5.3. Pre- vs. Post-Layout Simulation Correlation

5.4. Comparative Analysis

- DI Mode: 74.98 mW (static + dynamic);

- BDI Mode: 81.04 mW (≈8% increase over DI).

- Pixel Size: Among dual-mode AFEs, this work achieves the smallest pixel pitch (15 μm), enhancing spatial resolution and integration density;

- Injection Range: The widest current sensing range (100 pA to 100 nA) is achieved, supporting both ultra-low signal and high-flux scenarios;

- Linearity: Linearity in BDI mode (99.56%) matches or exceeds that of high-end fixed-mode ROICs, validating the efficacy of buffer-assisted injection;

- Power Efficiency: Despite its dual-mode capability and integrated 12-bit ADC, the power remains within the same order as single-mode designs, emphasizing circuit efficiency. The 74.976 mW/81.048 mW figure refers to the full dual-mode front-end (BDI + DI) plus column ADC array and on-chip timing controller, whereas Ref. [26] reports a BDI/DI front-end. Isolating our ADC core yields 0.01 mW/pixel; however, Ref. [28] reaches 0.12 mW/pitch.

6. Conclusions

- Dual-Mode Pixel Architecture: The BDI/DI hybrid input stage enables dynamic switching between high injection efficiency (99.56% at 100 nA) and low power consumption (74.96 mW), achieving a 75.58 dB dynamic range in BDI mode and 8% power savings in DI mode. The feedback op-amp in BDI mode stabilizes detector bias voltage, reducing nonlinearity to <0.1% under varying photocurrent levels;

- Four-Terminal Comparator ADC: By grounding the storage capacitor’s bottom plate, charge leakage is eliminated, ensuring 99.95% linearity in the fine ramp signal;

- Dynamic reference-voltage compensation enables 48.3 dB SFDR and a measured 6.12-bit ENOB over a 100 pA–1 nA photocurrent range.

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Yin, X.; Zhang, C.; Guo, Y.; Yang, Y.; Xing, Y.; Que, W. PbS QD-Based Photodetectors: Future-Oriented Near-Infrared Detection Technology. J. Mater. Chem. C 2021, 9, 417–438. [Google Scholar] [CrossRef]

- Tao, Y.; Xiong, S.; Song, R.; Muller, J.P. Towards streamlined single-image superresolution: Demonstration with 10 msentinel-2 colour and 10–60 m multi-spectral VNIR and SWIR bands. Remote Sens. 2021, 13, 2614. [Google Scholar] [CrossRef]

- Zhang, W.; Linga, K.; Evans, M.J.; Liobe, J.C.; Chang, D.S.; Huang, W.; Enriquez, M.; Bereznycky, P.; Endicter, S.; Morales, M.; et al. Development of high-performance SWIR detectors for passive and active imaging applications[C]//Infrared Technology and Applications XLVII. Int. Soc. Opt. Photonics 2021, 11741, 1174109. [Google Scholar]

- Bluzer, N.; Stehlik, R. Buffered direct injection of photocurrents into charge coupled devices. IEEE J. Solid State Circuits 1978, 13, 86–92. [Google Scholar] [CrossRef]

- Goulding, F.S.; Landis, D.A. Signal processing for semiconductor detectors. IEEE Trans. Nucl. Sci. 1982, 29, 1125–1141. [Google Scholar] [CrossRef]

- Li, X.; Gong, H.-M.; Shao, X.-M.; Li, T.; Huang, S.-L.; Ma, Y.-J.; Yang, B.; Zhu, X.-L.; Gu, Y.; Fang, J.-X. Recent advances in short wavelength infrared InGaAs focal plane arrays. J. Infrared Millim. Waves 2022, 41, 129–138. [Google Scholar]

- Ma, W.; Shi, Y.; Zhang, Y.; Wu, Z. A high speed snap-shot mode readout circuit for QWIP IR FPAs. In Proceedings of the 2009 4th IEEE Conference on Industrial Electronics and Applications, Xi’an, China, 25–27 May 2009; pp. 1012–1015. [Google Scholar]

- Poonnen, T.; Esparza, K.; McCotter, S.; Ratledge, B.; Korth, W.; Dhawan, N.; Veeder, K. Low-Noise High-Sensitivity DROIC for 640 × 512 SWIR FPAs. In SPIE Conference Proceedings; SPIE: Bellingham, WA, USA, 2024; Volume 13046. [Google Scholar]

- Maestro, R.J.; Merken, P.; Tavernier, F. A > 70 dB Digital ROIC in 65 nm CMOS for 1 Mp SWIR. In Proceedings of the IEEE Sensors Conference, Kobe, Japan, 20–23 November 2024. [Google Scholar]

- Mu, Y.; Zhao, Z.; Chen, C.; Yuan, D.; Wang, J.; Gao, H.; Chi, Y. The Design of a Low-Noise, High-Speed Readout-Integrated Circuit for Infrared Focal Plane Arrays. Sensors 2023, 23, 8715. [Google Scholar] [CrossRef]

- Chatterjee, A.; Abhale, A.; Pendyala, N.; Rao, K.S.R.K. Group II–VI semiconductor quantum dot heterojunction photodiode for mid wave infrared detection. Optoelectron. Lett. 2020, 16, 290–292. [Google Scholar] [CrossRef]

- Zhou, T.; Liu, J.; Fu, B.; Cao, Y.; He, Y.; Jiang, B.; Su, Y. A high-precision and high-linearity readout integrated circuit for infrared focal plane array applications. Optik 2019, 185, 168–177. [Google Scholar] [CrossRef]

- Hsieh, C.-C.; Wu, C.-Y.; Jih, F.-W.; Sun, T.P. Focal-plane-arrays and CMOS readout techniques of infrared imaging systems. IEEE Trans. Circuits Syst. Video Technol. 1997, 7, 594–605. [Google Scholar] [CrossRef]

- Hsieh, C.-C.; Wu, C.-Y.; Sun, T.-P. A new cryogenic CMOS readout structure for infrared focal plane array. IEEE J. Solid State Circuits 1997, 32, 1192–1199. [Google Scholar] [CrossRef]

- El Gamal, A.; Eltoukhy, H. CMOS image sensors. Circuits Devices Mag. IEEE 2005, 21, 6–20. [Google Scholar] [CrossRef]

- Kim, J.B.; Hong, S.K.; Kwon, O.K. A Low-Power CMOS Image Sensor with Area-Efficient 14-bit Two-Step SA ADCs Using Pseudomultiple Sampling Method. IEEE Trans. Circuits Syst. II Express Briefs 2015, 62, 451–455. [Google Scholar] [CrossRef]

- Zhao, S.; Gao, J.; Chen, Q.; Nie, K.; Xu, J. 12-bit 2.5-bit/phase two-stage cyclic ADC with phase scaling and low-power Sub-ADC for CMOS image sensor. Microelectron. J. 2024, 150, 106282. [Google Scholar] [CrossRef]

- Cheng, K.-C.; Chang, S.-J.; Chen, C.-C.; Hung, S.-H. A 94.3-dB SNDR 184-dB FoMs 4th-Order Noise-Shaping SAR ADC With Dynamic-Amplifier-Assisted Cascaded Integrator. IEEE Solid State Circuits Lett. 2025, 8, 65–68. [Google Scholar] [CrossRef]

- Catania, A.; Gagliardi, F.; Piotto, M.; Bruschi, P.; Dei, M. Ultralow-Power Inverter-Based Delta-Sigma Modulator for Wearable Applications. IEEE Access 2024, 12, 80009–80019. [Google Scholar] [CrossRef]

- Furuta, M.; Nishikawa, Y.; Inoue, T.; Kawahito, S. A High-Speed, High-Sensitivity Digital CMOS Image Sensor with a Global Shutter and 12-bit Column-Parallel Cyclic A/D Converters. IEEE J. Solid State Circuits 2007, 42, 766–774. [Google Scholar] [CrossRef]

- Bae, J.; Kim, D.; Ham, S.; Chae, Y.; Song, M. A Two-Step A/D Conversion and Column Self-Calibration Technique for Low Noise CMOS Image Sensors. Sensors 2014, 14, 11825–11843. [Google Scholar] [CrossRef]

- Ling, Y.H.; Wei, Y.H.; Jun, W. Design of high frame rate CMOS image acquisition system based on PCI Express. Appl. Electron. Tech. 2009, 35, 91–94. [Google Scholar]

- Hernandez-Gutierrez, C.A.; Avila-Avendano, C.; Solis-Cisneros, H.I.; Conde, J.; Sevilla-Camacho, P.Y.; Quevedo-Lopez, M.A. Modeling and SPICE Simulation of the CdS/CdTe Neutron Detectors Integrated with Si-Poly TFTs Amplifiers. IEEE Trans. Nucl. Sci. 2022, 69, 1310–1315. [Google Scholar] [CrossRef]

- Zhou, S.; Zhang, X.; Wang, Y.; Lin, D.; Zou, S.; Wang, J.; Xiao, L.; Zhang, D.; Jiang, J.; Zhang, P.; et al. Opto-Electrical Decoupled Phototransistor for Starlight Detection. Adv. Mater. 2024, 37, e2413247. [Google Scholar] [CrossRef]

- Li, H.; Hu, A.; Nie, Z.; Liu, D.; Niu, G.; Gao, L.; Tang, J. A 640 × 512 ROIC with optimized BDI input stage and low power output buffer for CQDs-based infrared image sensor. Microelectron. J. 2022, 124, 123–130. [Google Scholar] [CrossRef]

- Sun, T.-P.; Lu, Y.-C.; Kang, L.-L.; Shieh, H.-L. A buffer direct injection and direct injection readout circuit with mode selection design for infrared focal plane arrays. Infrared Phys. Technol. 2014, 63, 140–146. [Google Scholar] [CrossRef]

- Selim, E.; Samet, I.O.; Nusret, B.; Murat, I.; Soyer, S.T.; Ustundag, C.M.B.; Kocak, S.; Turan, O.; Eksi, U.; Akin, T. A 640 × 512-20 um Dual-Polarity ROIC for MWIR and LWIR Hybrid FPAs. In SPIE Defense + Security; SPIE: Bellingham, WA, USA, 2016. [Google Scholar]

- Yazici, M.; Ceylan, O.; Shafique, A.; Abbasi, S.; Gurbuz, Y. High Dynamic Range Smart Pixel Architecture for Infrared Focal Plane Arrays. In Proceedings of the 2018 IEEE International Symposium on Circuits and Systems (ISCAS), Florence, Italy, 27–30 May 2018; pp. 1–5. [Google Scholar]

- Woo, D.H.; Nam, I.K.; Lee, H.C. Smart reset control for wide-dynamic-range LWIR FPAs. IEEE Sens. J. 2010, 11, 131–136. [Google Scholar] [CrossRef]

- Ikebe, M.; Uchida, D.; Take, Y.; Someya, M.; Chikuda, S.; Matsuyama, K.; Asai, T.; Kuroda, T.; Motomura, M. Image Sensor/Digital Logic 3D Stacked Module Featuring Inductive Coupling Channels for High Speed/Low-Noise Image Transfer. In Proceedings of the Symposia on VLSI Technology and Circuits, Kyoto, Japan, 16–19 June 2015; pp. C82–C83. [Google Scholar]

| Parameter | Pre-Layout | Post-Layout | Silicon Data |

|---|---|---|---|

| SFDR (dB) | 81.55 | 87.67 | 48.3 |

| SNDR (dB) | 73.26 | 73.14 | 38.65 |

| ENOB (bit) | 11.87 | 11.75 | 6.12 |

| Parameter | [25] | [26] | [27] | [28] | [29] | [30] | This Work |

|---|---|---|---|---|---|---|---|

| Process | 180 nm CMOS | 350 nm CMOS | 180 nm CMOS | 180 nm CMOS | 350 nm CMOS | 180 nm CMOS | 180 nm CMOS |

| Pixel array | 640 × 512 | 10 × 8 | 640 × 512 | 32 × 32 | 128 × 128 | 200 × 200 | 64 × 64 |

| Pixel size (μm2) | 15 × 15 | 30 × 30 | 20 × 20 | 22.5 × 22.5 | 50 × 50 | 5 × 5 | 15 × 15 |

| Supply (V) | 1.8 | 5 | 3.3/1.8 | NA | NA | 3.3/1.8 | 3.3 |

| Voltage Swing (V) | 1 | 2 | <2 | 1.5 | 1.4 | / | 1.5 |

| Pixel input type | BDI | DI/BDI | DI | SFD/CTIA | BDI | / | DI/BDI |

| Input current (A) | 100f-100n | 1p-10n | N/A | 15p-3n | 22n-112n | / | 100p-100n |

| Power (mW) | N/A | 9.94 | N/A | N/A | N/A | 0.108 (only column ADC) | 74.976/81.048 |

| Linearity | 99.95% | 98%/99% | N/A | 98.9% | 95.8% | / | 98.7%/99.5% |

| Area (mm × mm) | 11.13 × 8.78 | / | 15 × 15.6 | / | / | / | 2.1 × 2.88 |

| ADC type | / | / | / | / | / | Column parallel SS ADC | TS-SS ADC |

| ADC resolution (bit) | / | / | / | / | / | 11 | 6.12 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhang, Y.; Chen, Z.; Yang, Y.; Chen, H.; Gao, J.; Zhang, Z.; Chen, C. A Multimodal CMOS Readout IC for SWIR Image Sensors with Dual-Mode BDI/DI Pixels and Column-Parallel Two-Step Single-Slope ADC. Micromachines 2025, 16, 773. https://doi.org/10.3390/mi16070773

Zhang Y, Chen Z, Yang Y, Chen H, Gao J, Zhang Z, Chen C. A Multimodal CMOS Readout IC for SWIR Image Sensors with Dual-Mode BDI/DI Pixels and Column-Parallel Two-Step Single-Slope ADC. Micromachines. 2025; 16(7):773. https://doi.org/10.3390/mi16070773

Chicago/Turabian StyleZhang, Yuyan, Zhifeng Chen, Yaguang Yang, Huangwei Chen, Jie Gao, Zhichao Zhang, and Chengying Chen. 2025. "A Multimodal CMOS Readout IC for SWIR Image Sensors with Dual-Mode BDI/DI Pixels and Column-Parallel Two-Step Single-Slope ADC" Micromachines 16, no. 7: 773. https://doi.org/10.3390/mi16070773

APA StyleZhang, Y., Chen, Z., Yang, Y., Chen, H., Gao, J., Zhang, Z., & Chen, C. (2025). A Multimodal CMOS Readout IC for SWIR Image Sensors with Dual-Mode BDI/DI Pixels and Column-Parallel Two-Step Single-Slope ADC. Micromachines, 16(7), 773. https://doi.org/10.3390/mi16070773