Correction: Hsieh et al. Single-Grain Gate-All-Around Si Nanowire FET Using Low-Thermal-Budget Processes for Monolithic Three-Dimensional Integrated Circuits. Micromachines 2020, 11, 741

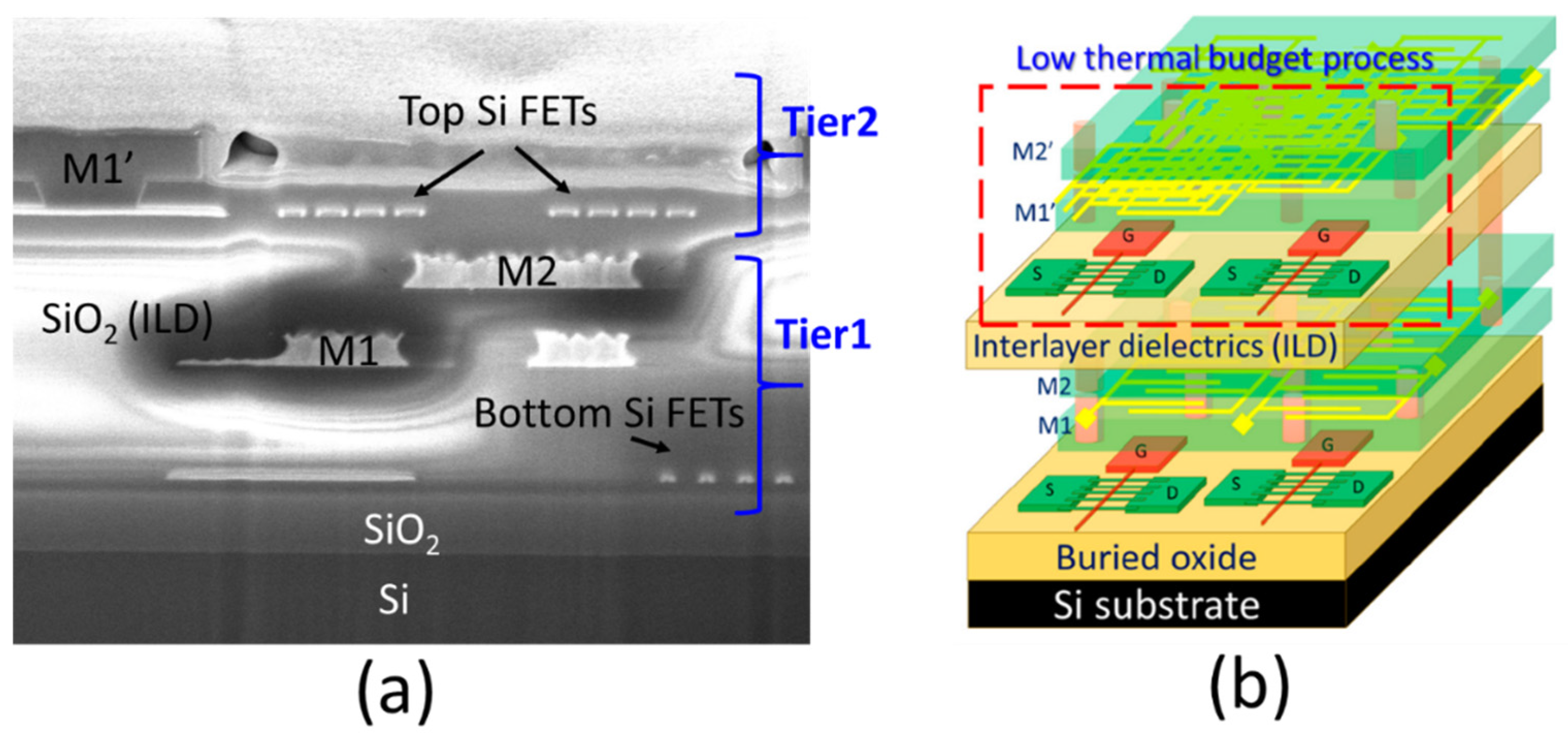

1. Error in Figure 2

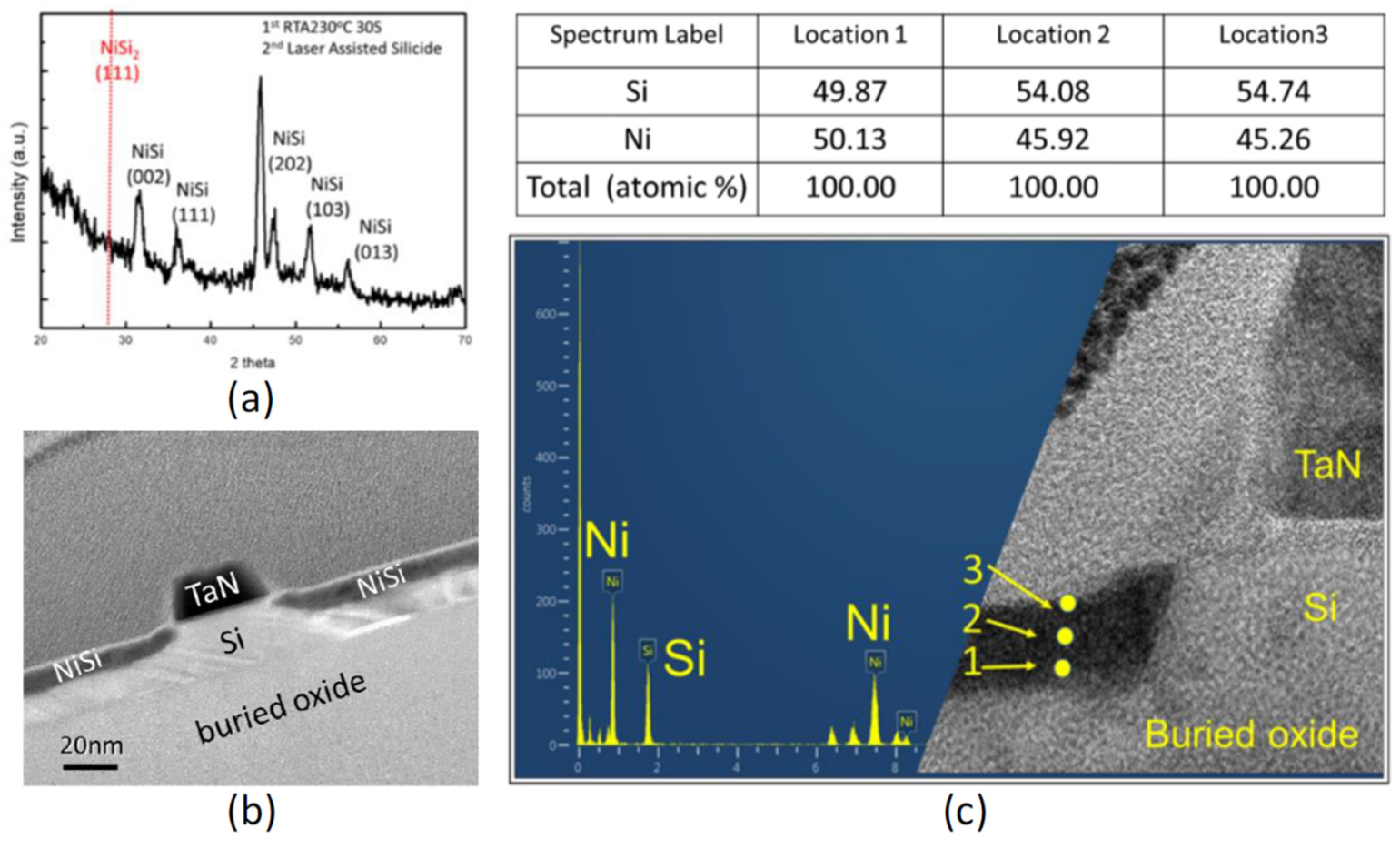

2. Error in Figure 6

3. Text Correction

4. Missing Citation

References

- Hsieh, T.-Y.; Hsieh, P.-Y.; Yang, C.-C.; Shen, C.-H.; Shieh, J.-M.; Yeh, W.-K.; Wu, M.-C. Single-Grain Gate-All-Around Si Nanowire FET Using Low-Thermal-Budget Processes for Monolithic Three-Dimensional Integrated Circuits. Micromachines 2020, 11, 741. [Google Scholar] [CrossRef]

- Yang, C.; Shieh, J.; Hsieh, T.; Huang, W.; Wang, H.; Shen, C.; Hsueh, F.; Hsieh, P.; Wu, M.; Yeh, W. Footprint-efficient and power-saving monolithic IoT 3D+ IC constructed by BEOL-compatible sub-10nm high aspect ratio (AR > 7) single-grained Si FinFETs with record high Ion of 0.35 uA/μm and steep-swing of 65 mV/dec and Ion/Ioff ratio of 8. In Proceedings of the 2016 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016; pp. 224–227. [Google Scholar]

- Yang, C.; Shieh, J.; Hsieh, T.; Huang, W.; Wang, H.; Shen, C.; Wu, T.; Hou, Y.; Chen, Y.; Lee, Y.; et al. Enabling low power BEOL compatible monolithic 3D+ nano- electronics for IoTs using local and selective far-infrared ray laser anneal technology. In Proceedings of the 2015 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015; pp. 205–208. [Google Scholar]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Hsieh, T.-Y.; Hsieh, P.-Y.; Yang, C.-C.; Shen, C.-H.; Shieh, J.-M.; Yeh, W.-K.; Wu, M.-C. Correction: Hsieh et al. Single-Grain Gate-All-Around Si Nanowire FET Using Low-Thermal-Budget Processes for Monolithic Three-Dimensional Integrated Circuits. Micromachines 2020, 11, 741. Micromachines 2025, 16, 537. https://doi.org/10.3390/mi16050537

Hsieh T-Y, Hsieh P-Y, Yang C-C, Shen C-H, Shieh J-M, Yeh W-K, Wu M-C. Correction: Hsieh et al. Single-Grain Gate-All-Around Si Nanowire FET Using Low-Thermal-Budget Processes for Monolithic Three-Dimensional Integrated Circuits. Micromachines 2020, 11, 741. Micromachines. 2025; 16(5):537. https://doi.org/10.3390/mi16050537

Chicago/Turabian StyleHsieh, Tung-Ying, Ping-Yi Hsieh, Chih-Chao Yang, Chang-Hong Shen, Jia-Min Shieh, Wen-Kuan Yeh, and Meng-Chyi Wu. 2025. "Correction: Hsieh et al. Single-Grain Gate-All-Around Si Nanowire FET Using Low-Thermal-Budget Processes for Monolithic Three-Dimensional Integrated Circuits. Micromachines 2020, 11, 741" Micromachines 16, no. 5: 537. https://doi.org/10.3390/mi16050537

APA StyleHsieh, T.-Y., Hsieh, P.-Y., Yang, C.-C., Shen, C.-H., Shieh, J.-M., Yeh, W.-K., & Wu, M.-C. (2025). Correction: Hsieh et al. Single-Grain Gate-All-Around Si Nanowire FET Using Low-Thermal-Budget Processes for Monolithic Three-Dimensional Integrated Circuits. Micromachines 2020, 11, 741. Micromachines, 16(5), 537. https://doi.org/10.3390/mi16050537