Abstract

This paper introduces a fully integrated memristive chaotic circuit, which is based on a voltage-controlled oscillator (VCO). The circuit employs a fully integrated architecture that offers reduced power consumption and a smaller footprint compared to the use of discrete components. Specifically, the VCO is utilized to generate the oscillatory signal, whereas the memristor emulator circuit serves as the nonlinear element. The memristor emulator circuit is constructed using a single operational transconductance amplifier (OTA), two transistors, and a grounded capacitor. This straightforward design contributes to diminished power usage within the chip’s area. The VCO incorporates a dual delay unit and implements current compensation to enhance the oscillation frequency and to broaden the VCO’s tunable range. Fabricated using the SMIC 180 nm CMOS process, this chaotic circuit occupies a mere 0.0072 mm2 of chip area, demonstrating a design that is both efficient and compact. Simulation outcomes indicate that the proposed memristor emulator is capable of operating at a maximum frequency of 300 MHz. The memristive chaotic circuit is able to produce a chaotic oscillatory signal with an operational frequency ranging from 158 MHz to 286 MHz, powered by a supply of 0.9 V, and with a peak power consumption of 3.5553 mW. The Lyapunov exponent of the time series within the resultant chaotic signal spans from 0.2572 to 0.4341.

1. Introduction

In 1971, Chua identified the absence of symmetry in the interrelation of circuit variables and introduced an element with the ability to delineate the correlation between magnetic flux and electric charge, known as the memristor [1]. Subsequently, in 1976, he delivered a comprehensive elucidation of its structural principles and functional attributes [2]. Owing to the nonexistence of tangible memristors, research pertaining to the memristor within the scientific and engineering disciplines remained constrained. It was not until 2008 that researchers at HP Labs devised a mathematical model for devices within the conceptual framework of a memristor system, thereby inciting a proliferation of fervent research endeavors among a multitude of researchers [3]. Considering their capacity to retain information in the absence of a power supply, memristors have been the subject of extensive research for potential applications in nonlinear circuits [4,5], logic circuits [6,7,8], artificial neural networks [9,10,11], and nonvolatile memory [12,13,14].

Currently, memristors are becoming an important part of research in chaos science due to their unique nonlinear properties. Guseinov et al. [15] proposed a second-order hybrid memory system with capacitive and resistive components, in which hyper-periodic, intermittent, and chaotic behaviors may occur under periodic voltages. Ostrovskii et al. [16] introduced a dynamic threshold voltage function and a chaos generator based on the MMS model, and applied the proposed chaotic memristor model to develop an FPGA-based hardware memristor emulator. At the same time, adding a memristor to chaotic circuits has become a hot research topic. Guo et al. [17] proposed a modified Chua’s circuit in which a physical memristor is used instead of the Chua’s diode in the Chua’s circuit. Laskaridis et al. [18] proposed a chaotic circuit based on a physical memristor that can behave as a static nonlinear resistor. Minati et al. [19] implemented a fully autonomous chaotic oscillatory circuit based on a physical memristor and a processed tungsten/carbon-based SDC memristor, and verified the bifurcation and multistable behavior in conjunction with variational equations. Meanwhile, discrete component-based memristive chaotic circuits have certain advantages in terms of applicability and portability, and much literature has been reported. Kengne et al. [20] designed a memristor-based chaotic oscillator, which is derived from the Shinriki circuit by substituting the nonlinear positive conductance with a first-order memristive diode bridge. Wu et al. [21] proposed a new memristor, and a new simple chaotic circuit was designed using the proposed memristor and other circuit components, which generates a chaotic attractor using only linear negative resistors, capacitors, inductors, and a memristor. Parnab Das et al. [22] present a novel four-dimensional chaotic system based on physical amnesia (), and a novel and efficient colour image encryption algorithm is developed based on this system. Ma et al. [23] present a simple novel chaotic oscillatory circuit that can generate 19 different types of attractors by building them in parallel with a memristor, memcapacitor, and inductor. Ostrovskii et al. [24] proposed a bio-inspired neuron model based on a threshold selector and tunnel diode, with a bidirectional threshold switch selector device, as an example of a non-volatile memristor that mimics the dynamic behavior of neurons. The above-mentioned memristive chaotic circuits are designed by replacing the nonlinear item in the original system with a memristor. Furthermore, the study of memristive Chua’s circuits has also aroused much interest. Escudero et al. [25] proposed a physical implementation of a tunable memristor Chua’s circuit, based on a non-volatile memristor device, by programming the non-volatile memory device into different states to select between different oscillation modes. Bao et al. [26] designed a fifth-order two-memristor Chua’s circuit and hyperchaos was observed.

Integrated circuits provide advantages such as reduced power consumption and compact designs. The aforementioned chaotic circuits, which predominantly utilize commercial discrete devices, not only suffer from high power consumption, high costs, and extensive footprint, but also have instability issues. The integration of chaotic circuits can significantly mitigate these shortcomings. Consequently, over the past few decades, numerous researchers have conducted rigorous research on this subject. Nguyen et al. [27] presented a low-power hyperchaos-based true random number generator, which is based on 130 nm CMOS technology. Valencia [28] proposed a chaotic system based on approximate fractional derivatives and implemented the circuit using 180nm CMOS integrated circuit technology. Eduardo et al. [29] proposed a CMOS implementation of a Lorentzian system circuit, which is implemented by operational transconductance amplifiers as well as multipliers, and used this Lorentzian system to implement a CMOS secure communication system. Joshi et al. [30] proposed a simple CMOS-based chaotic oscillator with a circuit structure consisting of capacitors as well as MOS tubes and an external comparator circuit as a nonlinear term. Although the mentioned integrated chaotic circuits have achieved integration, they still exhibit notable flaws in power consumption and footprint, with pronounced deficiencies in oscillation frequency. Meanwhile, most proposed integrated chaotic circuits have exhibited low oscillation frequencies. Consequently, this paper introduces a fully integrated memristive chaotic circuit based on a ring oscillator and a memristor emulator. The circuit comprises a ring oscillator, a memristor emulator circuit, two ground capacitors, and a resistor. By introducing a ring oscillator to generate high-frequency oscillation signals, the performance of the chaotic circuit is improved. Meanwhile, we designed the integrated circuit of the memristor; thus, the integration level of the chaotic circuit can be guaranteed.

The subsequent sections of this paper are organized as follows. Section 2 delineates the architecture of the proposed memristive chaotic circuit and the memristor emulator. Section 3 describes the architecture of the proposed voltage-controlled ring oscillator circuit, along with the comprehensive topology and mathematical model of the memristive chaotic circuit. The simulation outcomes and performance validation of the proposed memristive chaotic circuit are presented in Section 4. Finally, the conclusion is succinctly summarized in Section 5.

2. Design of a Memristive Chaotic Circuit

2.1. The Simplest Memristive Chaotic Circuit

Muthuswamy et al. [31] designed a memristive chaotic circuit, as depicted in Figure 1, which they refer to as the simplest memristive chaotic circuit. As shown in Figure 1, the circuit comprises a capacitor denoted as C, an inductor labeled as L, and a current-controlled memristor designated as M.

Figure 1.

The simplest memristive chaotic circuit.

In the architecture of the memristive chaotic circuit under examination, capacitors and inductors serve as dual-purpose energy repositories, simultaneously establishing the requisite oscillatory conditions for chaotic phenomena and preserving their energy storage functionalities. The memristor acts as a generator of nonlinear dynamics, thus completing the foundational triad that forms the essential configuration for the generation of chaos. The traditional approach utilizes a multi-component architecture that includes operational amplifiers, analog multipliers, and discrete passive elements. Nevertheless, this modular design introduces significant constraints regarding power efficiency and spatial compactness, essentially limiting its suitability for integration into contemporary system-on-chip architectures.

In order to mitigate these limitations, we propose a monolithic integrated memristive chaotic circuit, depicted in Figure 2. The suggested architecture amalgamates three principal components: (1) an active oscillation core responsible for generating foundational chaotic signals, (2) resistively coupled capacitive banks functioning as synchronized energy storage nodes, and (3) a CMOS-compatible memristor emulator performing essential nonlinear transformations. This architectural synthesis attains compactness while maintaining chaotic operational characteristics through the amalgamation of functions.

Figure 2.

The proposed memristive chaotic circuit.

2.2. Design of the Memristor Emulator

2.2.1. The Memristor Emulator Circuit

The memristor emulator circuit replicates the characteristics of the memristor through correlation within the circuitry, and its voltage–current characteristics exhibit nonlinear properties. The resistance of the memristor can be modulated by regulating the intensity and duration of the electrical pulse signals that pass through it.

The memristor emulators delineated in this article consist of an operational transconductance amplifier (OTA), a variable resistor (VR), and ground capacitors, which utilize a DC voltage supply of V and V. The circuit topology is depicted in the accompanying Figure 3, wherein the blue box signifies the OTA circuit, and the green box signifies the VR circuit.

Figure 3.

Circuit topology of memristor emulator.

The variable resistor, composed of the two source–drain connected PMOS and NMOS transistors discussed in this article, has a resistance value that is contingent upon two control voltages. Specifically, the gate voltage of M2 represents the capacitor voltage value, denoted as , while the voltage at the source–drain junction of M1 and M2 constitutes the control voltage, denoted as . Within this configuration, constitutes the structure of the MOS diode. When operates within the saturated region and within the linear region, the input current can be articulated as

where k is the process parameter of the MOS transistor and can be expressed as

Here, , , and are the mobility of charge carrier, the aspect ratio, and the oxide capacitance per unit area of MOS, respectively. According to the drain current formula of the two MOS transistors, it can be concluded that and are the same. They have good matching characteristics, and the total current flowing through the VR can be expressed as

The output current of the OTA for an input is expressed as

in the above equation is the transconductance value of the OTA. The analysis results in the expression of Gm as

The current flowing into the grounding capacitor can be expressed as

Bias voltage can be expressed as

As ≤ − , Equation (4) can be expressed as

So, the model for the proposed memristor emulator circuit can be expressed as

2.2.2. Simulation Results

To scrutinize the frequency response of the proposed emulator design, encompassing both time-invariant and time-variant components, a bipolar input signal = was applied. The computation of the input flux is executed in accordance with the following procedure:

Substituting the value of flux of Equation (11) in Equation (10), the memductance can be calculated as follows:

This approach allows us to analyze the emulator’s behavior under different frequency conditions, providing valuable insights into its performance characteristics.

According to Equation (12), the first part is a time-varying quantity and the second part is a constant. This complies with the generalized memristor simulator equation.

In order to verify the characteristics of the proposed memristor, frequency characteristic and non-volatile analysis of the memristor are carried out. In the frequency characteristic analysis, we applied a sine signal with a frequency variation from 100 to 350 MHz to the circuit, with a fixed MOS capacitor dimension value of 5 × 5 m; the resulting pinch hysteresis curves are shown in Figure 4.

Figure 4.

Pinch hysteresis curve for different frequencies, when frequency is (a) 100 MHz, (b) 150 MHz, (c) 200 MHz, (d) 250 MHz, (e) 300 MHz, and (f) 350 MHz.

Examination of the graph reveals that the proposed memristor circuit displays an “8”−shaped hysteresis loop, but distortion emerges with increasing signal frequency. However, within the frequency range of 100 MHz to 200 MHz, the memristor circuit demonstrates a superior hysteresis curve. Consequently, the operating frequency for this integrated chaotic circuit was chosen to fall within this frequency range.

The non-volatile properties are one of the most important properties of the memristor. In order to further verify the non-volatile properties of the memristor circuit, a series of voltage pulses as input and the corresponding changes in the memductance values were observed. Figure 5 shows the pulse of the applied input voltage along with the voltage of the capacitor. According to Equations (8) and (10), we can obtain the memductance values. Table 1 shows the CMOS dimension of the memristor simulator. This amnesia simulator has the advantages of a high operating frequency and low number of active components.

Figure 5.

Non−volatility analysis for proposed memristor circuit.

Table 1.

Transistor dimensions for memristor emulator.

Finally, we give a comparison between the memristor emulator circuit proposed in this paper and the previously proposed memristor emulator circuits, and the results of the analysis are shown in Table 2. A comparison of the structure of the memristor emulator circuits in the table reveals that the memristor emulator proposed in this paper employs fewer circuit modules and passive components than other models. Furthermore, it is capable of achieving a higher operating frequency while using a straightforward OTA structure, which is more straightforward than the overall circuit.

Table 2.

Transistor width−to−length ratio in memristor emulator.

3. Integrated Circuit Design and Its Analysis

3.1. The Voltage−Controlled Oscillator

3.1.1. Implementation of the Voltage−Controlled Oscillator

In integrated circuits, signal generators are commonly embodied by oscillators. Ring oscillators offer numerous significant advantages over LC voltage-controlled oscillators (LC VCOs). They eliminate the need for inductive components, conserve chip real estate, reduce costs, provide a broad tuning range, and facilitate easy multiphase implementation. However, ring oscillators typically exhibit slightly inferior phase noise performance. Considering its benefits of low power consumption, a small footprint, and high integration, a ring oscillator is chosen as the voltage-controlled oscillator for implementation.

Figure 6 illustrates the circuit structure of the ring voltage-controlled oscillator, where the red line indicates the second loop of the delay unit. The VCO consists of eight basic delay units, and the circuit structure of the delay units is shown in Figure 7, and the transistor widths and lengths of the delay cells are shown in the Table 3. The delay unit uses a dual delay path, with the input path Vin1+ (Vin1−) connected to the output of the previous delay unit, and the input path Vin2+ (Vin2−) connected to the input path Vin1+ (Vin1−) of the previous level. The input path Vin2, because it is connected to the input Vin1 of the previous level, provides an advance phase to compensate for the slow turn−on of the pull−up pMOS transistor as a means of speeding up the pmos tubes and thus increasing the oscillation frequency of the VCO [40]. A pair of PMOS load transistors, M5 and M6, are incorporated into the delay cell to construct the latch. Furthermore, the cross-coupled NMOS pass transistors, M7 and M8, govern the maximum gate voltage of the PMOS load transistors (M5 and M6), and modulate the strength and operating frequency of the added latch. An additional pair of PMOS transistors, M9 and M10, are employed to enhance the frequency control range of the VCO, mitigating the limited frequency control range resulting from the reduced latch strength at lower control voltages.

Figure 6.

Implementation of voltage-controlled oscillators.

Figure 7.

Circuit topology of double delay cells in voltage−controlled oscillators.

Table 3.

Transistor dimensions for delay cell.

The integration of these components not only optimizes the performance of the latch but also ensures a more stable and efficient operation across a wide range of frequencies. This design approach enhances the overall functionality and reliability of the VCO, making it suitable for applications that demand precise frequency control and stable operation.

The tuning gain represents the output frequency versus the input reference voltage, written as , and expressed as

When the of the VCO is large, the VCO is more sensitive to the control voltage . Since the input voltage is not an ideal signal, the spuriousness of the input voltage is amplified, which affects the noise characteristics and thus the tuning range of the VCO. The output frequency of the control voltage is expressed as

where refers to the output frequency when V, () is the maximum and minimum value of the control voltage , and K is a constant. It can be seen from the equation that a large can be obtained and a small change in the voltage can be controlled to cause a large change in the output frequency. Figure 8 represents the two output waveforms of the VCO proposed in this paper, with a supply of V and a control voltage of V. The frequency of the oscillating signal generated is 284 MHz.

Figure 8.

Out1−Out2 output curve of VCO.

3.1.2. Process Corner Simulation

The parameters of MOSFETs can vary significantly across different wafers, posing challenges for circuit designers. To address this, process engineers are dedicated to ensuring that equipment performance remains within acceptable parameters. They achieve this by rigorously controlling the expected parameter variations, ensuring they remain within the maximum range that the chip’s performance envelope can withstand. This acceptable range of performance is commonly referred to as a “process corner” and is provided to designers to help them account for these variations in their circuit designs.

As shown in Figure 9, we carried out process corner experiments for the variation in oscillator output frequency with control voltage; as shown in the figure, we carried out the experiments for Fast MOS, Typical MOS, and Slow MOS processes, respectively [41]. We found that the oscillator has differences in various process angles but the overall performance is very close.

Figure 9.

curves under different PVT processes.

3.2. Design of the Proposed Memristive Chaotic Circuit Based on a VCO

The structure of the proposed chaotic circuit based on a VCO is shown in Figure 10. The signal generator comprises eight connected delay cells on the left side of the circuit, with the nonlinear component being formed by a memristor circuit on the right side. Because a voltage-controlled oscillator is used instead of an external input signal, the chaotic system can be considered as an autonomous chaotic system. In order to meet the conditions of chaos in the autonomous chaotic system, an energy storage component capacitor is added to the oscillator.

Figure 10.

Proposed memristive chaotic circuit dased on VCO.

Based on Kirchhoff’s law, we can derive the following equation of state for the circuit in Figure 10:

where is the voltage at the point where the oscillator and capacitor are connected in parallel, is the voltage at the parallel connection of the nonlinear term and capacitor , is the output impedance of the oscillator, and denotes the memductance value of the memristor emulator, which can be expressed by the following equation:

where represents the capacitor voltage in the memristive circuit. In this formulation, the variables and components interact to determine the overall behavior of the circuit, highlighting the role of each element in the system.

The above equations can be used to derive dimensionless parametric equations that are applicable to chaotic systems:

In the above dimensionless parametric equations, the parameters are determined by the device parameters in the circuit:

where = 50 fF, = 861.29 S, k = 1.6308 mA/V2, c = 904.9 mV, = 12 k, R = 2 k∼7 k, = 400 fF, and = 800 fF.

In this paper, an integrated voltage-controlled oscillator is used to generate oscillating signals in place of the sinusoidal signal generator in the non-autonomous chaotic circuit. The nonlinear term is used in an integrated memristor circuit, which mimics the nonlinear characteristics of the memristor. The integrated design of the overall circuit makes the proposed chaotic circuit advantageous in terms of power consumption, footprint, and stability.

4. Layout Design and Simulation Verifications

4.1. The Layout Design

The layout of the proposed VCO−based memristive chaotic circuit in this paper is shown in Figure 11. The overall area occupied by the layout is 0.0072 mm2. In this work, a fully integrated VCO−based memristive chaotic circuit is realized using the SMIC 180 nm CMOS process technology.

Figure 11.

Proposed memristive chaotic circuit layout.

4.2. Simulation Verifications

In this section, we discuss SPICE simulations performed on the proposed fully CMOS oscillator−based memristive chaotic circuit and present the results. The total power consumption of the integrated circuit comprises both static and dynamic components. The static power dissipation , primarily attributed to device leakage currents, can be expressed as follows: , where denotes the cumulative leakage current through all transistors.The dynamic power consumption , arising from switching activities, is determined by , where represents the effective load capacitance, and is the operating frequency. Key parameters influencing power consumption include supply voltage, operating frequency, and nodal capacitance. SPICE simulations at ±0.9 V dual supply voltages yield a total power dissipation of 3.5553 mW.

To generate chaotic phenomena, adjustments are made to various circuit parameters, including capacitance, resistance, and the aspect ratio of the transistors. Determining the correct parameter settings has become crucial, as these are not only based on design constraints but also take into account the characteristics of the entire system. We individually adjusted the system’s operating frequency and device parameters to achieve various chaotic phenomena. Subsequently, we employed Rosenstein’s small-data method to calculate the Lyapunov exponent and utilized the 0–1 test to validate its chaotic effects.

4.2.1. Chaotic Phenomena at Different Oscillation Frequencies

Figure 12 illustrates the phase diagram showing the relationship between outputs , , and . Each phase diagram corresponds to different device parameters and oscillation frequencies. In the simulation experiments, we vary the device parameters () and give three sets of chaotic phase diagrams and Lyapunov exponents . In the first set of phase diagrams (a), the control voltage of the voltage-controlled oscillator is 0.4 V, the oscillation frequency is 158 M, and the device parameters are as follows: R = 2 K, = 50 fF, = 300 fF, = 500 fF, and = 0.2572. In the second set of phase diagrams (b), the control voltage of the voltage-controlled oscillator is −0.1 V, the oscillation frequency is 211 M, and the device parameters are as follows: R = 5 K, = 50 fF, = 500 fF, = 1200 fF, and = 0.4047. Finally, in the phase diagram of the third group (c), the control voltage of the voltage-controlled oscillator is −0.4 V, the oscillation frequency is 284 M, and the device parameters are as follows: R = 5.2 K, = 50 fF, = 400 fF, = 800 fF, and = 0.4341.

Figure 12.

Chaotic phenomena with different oscillation frequencies at Tran = 1 ps, T = 5 µs, and = 0.3 V: (a) f = 158 MHz, R = 2 K, = 50 fF, = 300 fF, = 500 fF, and = 0.2572; (b) f = 211 MHz, R = 5 K, = 50 fF, = 500 fF, = 1200 fF, and = 0.4047; and (c) f = 284 MHz, R = 5.2 K, = 50 fF, = 400 fF, = 800 fF, and = 0.4341.

Examining these phase diagrams, we observe distinct chaotic behaviors at varying operating frequencies of the oscillator. The phase diagrams exhibit a certain complexity. Moreover, the Lyapunov exponent being greater than zero confirms that the system is in a chaotic state. Despite the chaotic behaviors observed at various operating frequencies, the corresponding Lyapunov exponents are not high. The reason is that simply adjusting the operating frequency and the parameters of the coupling device between the oscillator and the nonlinear term is not sufficient to continuously amplify the chaotic phenomenon. Therefore, to achieve the desired chaotic effect, adjustments must be made to the parameters of each circuit component and the voltage bias. By observing the phase diagram, we can infer that chaotic behavior may be present in the system, but these observations are not sufficient to fully assess the chaotic sophistication of the system.

4.2.2. Effect of Different Device Parameters on Chaotic Phenomena

In Figure 13, we maintain the parameters of all the devices of the system except the resistance constant and systematically increase the resistance value to investigate the effect of the device parameters on the chaotic phenomena. From Figure 13a,b, the phase diagram becomes progressively more complex, with a resistance range of 4 K to 4.5 K. From Figure 13c,d, the phase diagram shows a notable complexity, with a resistance range of 4.8–5.5 K. The resistance range from Figure 13a,d results in the beginnings of chaos that gradually increase in intensity. From Figure 13e,f, with a resistance range of 7 K to 10 K, the phase diagram shows a diminishing chaotic behavior that stabilizes in Figure 13f, indicating that it is no longer in a chaotic state.

Figure 13.

Chaotic phenomena with different values of R and operating frequency of 298 MHz: (a) R = 4 K, < 0; (b) R = 4.5 K; (c) R = 4.8 K; (d) R = 5.5 K; (e) R = 7 K; and (f) R = 10 K, < 0.

In summary, chaotic systems feature a specific range of variables that greatly influence chaotic phenomena. The complexity of a phase diagram does not necessarily indicate pronounced chaotic effects in a system. Identifying a range of variables alone does not lead to the best chaotic phenomenon. To attain the desired chaotic effect, one must employ mathematical tools, such as the Lyapunov exponent, to determine the precise parameters of the system.

4.2.3. Validation of Chaos

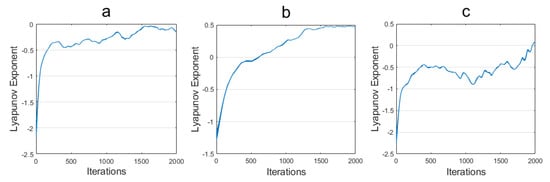

In order to validate the chaotic effects of the proposed fully integrated memristive chaotic circuit, the Lyapunov exponent and 0−1 chaos tests were conducted. The Lyapunov exponent is a crucial quantitative measure of a system’s dynamic properties; this is a numerical feature that represents the mean exponential divergence of adjacent trajectories in phase space. In this study, the orbit tracking method is utilized to monitor orbits of the system, thereby enabling the determination of their evolutionary patterns and the extraction of Lyapunov exponents.

In addition, the 0−1 chaos test was performed to further confirm the chaotic behavior. This test involves analyzing the system’s response to initial conditions, as minute variations can lead to significantly different outcomes, a hallmark of chaotic systems. The outcomes of these two analytical procedures were found to be concordant, thus providing substantial evidence for the existence of chaos in the aforementioned circuit.

The Lyapunov exponent in Figure 13a,d,e, with a data length of 2000, was extracted and analyzed. The results are presented in Figure 14, which shows that the Lyapunov exponent is consistently less than 0 and has not entered the chaotic state in part (a). In part (b), the Lyapunov exponent is observed to increase and subsequently stabilize at approximately 0.5, indicative of a chaotic state. In contrast, the Lyapunov exponent in part (c) is predominantly negative and exceeds 0 in the final segment.

The 0−1 test is a test algorithm for measuring the presence of chaotic time series in a time series. It was first proposed by Li and Yorke (1975) [42] in their study of periodic solutions in nonlinear dynamical systems. The algorithm is specifically defined by the following equation:

Furthermore, the displacement mean square error is utilized as a measurement tool, which is calculated in accordance with the following Equation (20). Consequently, the K-value equation is obtained.

We use the Matlab tool for simulation verification of the 0−1 test algorithm. The plots of p and q of the phase diagram of Figure 13c proposed in this paper are given in Figure 15b, and the dynamics is chaotic.

Figure 15.

(a) The verification result graph of the 0−1 test algorithm. (b) The p−q planar graph of the 0–1 test algorithm.

By calculating the value of K, the result is shown in Figure 15a. It can be seen that its value is close to 1, indicating that the system is indeed in a chaotic state.

4.2.4. Performance Comparison

Table 4 shows the comparison of this work with other chaotic work. It is clear from the table that for the realization of chaotic circuits, more studies have chosen to build them using separated devices, which are not comparable to integrated chaotic circuits in all aspects of performance. Compared with other chaotic circuits implemented using CMOS integrated circuits, the work in this paper outperforms the other articles in terms of circuit power consumption, footprint, and output frequency. It is certain that integration, as well as high performance and low power consumption, are inevitable trends in the development of circuits.

Table 4.

Comparison of CMOS chaotic circuit proposed in this paper with other chaotic circuits.

5. Conclusions

To align with current industry developments, circuits must meet key requirements, including power consumption, stability, portability, and performance. Because there are many shortcomings in circuits composed of discrete components, the implementation of integrated circuits is a new trend. Therefore, this paper introduces a chaotic integrated circuit that utilizes memristive circuits and voltage-controlled oscillators, effectively reducing power consumption and footprint while enhancing stability and performance. The circuit is fabricated using SMIC 180 nm CMOS technology, occupies an area of 0.0072 mm2, consumes 3.5553 mW of power, and operates at a maximum frequency of 286 MHz. As a result, when the polyphase output signals and low-mode area are more of a concern, a VCO is preferable in conventional circuits. Meanwhile, with the continuous reduction in the CMOS feature size, the transistor size is smaller and faster, which can meet the trend of integrated circuit development and market demand. In the future, we will design chaotic chips for secure communication to face even greater challenges and opportunities.

Author Contributions

Conceptualization, Z.D. and S.H.; methodology, S.H. and X.Y.; validation, J.C., Q.W. and P.X.; formal analysis, J.C. and X.Z.; investigation, Z.D.; resources, Z.D.; data curation, Z.D. and S.H.; writing—original draft preparation, J.C.; writing—review and editing, Z.D. and S.H.; visualization, J.C.; supervision, X.Y.; project administration, Z.D.; funding acquisition, Z.D. and S.H. All authors have read and agreed to the published version of the manuscript.

Funding

This work was supported by the Key Laboratory in the higher education institutions of the educational commission of Guangdong Province, China (Grant No.2021KSYS008), the Key-Area Research and Development Program of Guangdong Province (No. 2019B010153001), the Guangzhou Innovation and Entrepreneurship Leader Team (No.CXLJTD-201608), the basic research on Shenzhen Science and technology Funds (general program) (JCYJ20210324122202007), and the central government guides local science and technology development funds to freely explore basic research projects (2021Szvup174).

Institutional Review Board Statement

Not applicable.

Informed Consent Statement

Not applicable.

Data Availability Statement

The original contributions presented in this study are included in the article. Further inquiries can be directed to the corresponding authors.

Acknowledgments

The authors would like to thank the editors and the anonymous reviewers for their valuable comments.

Conflicts of Interest

The authors declare no conflicts of interest.

References

- Chua, L.O. Memristor-the missing circuit element. IEEE Trans. Circuit Theory 1971, 18, 507–519. [Google Scholar] [CrossRef]

- Chua, L.O. Memristive devices and systems. Proc. IEEE 1976, 64, 209–223. [Google Scholar] [CrossRef]

- Strukov, D.B.; Snider, G.S.; Stewart, D.R.; Williams, R.S. The missing memristor found. Nature 2008, 453, 80–83. [Google Scholar] [CrossRef] [PubMed]

- Wei, X.; Zhang, J.; Li, H.; Zuo, J. Nonlinear analysis, circuit design, and chaos optimisation application of multiscroll chaotic attractors based on novel locally active non-polynomial memristor. Nonlinear Dyn. 2024, 11, 5773–5810. [Google Scholar] [CrossRef]

- Yang, F.; Ma, J.; Wu, F. Review on memristor application in neural circuit and network. Chaos Solitons Fractals 2024, 187, 115361. [Google Scholar] [CrossRef]

- Youn, S.; Lee, J.; Kim, S.; Park, J.; Kim, K.; Kim, H. Programmable threshold logic implementations in a memristor crossbar array. Nano Lett. 2024, 24, 3581–3589. [Google Scholar] [CrossRef]

- Wang, J.; Wang, H.; Cao, Z.; Zhu, S.; Du, J.; Yang, C.; Ke, C.; Zhao, Y.; Sun, B. Logic Gate Circuits Based on CeOx/WOy Memristor for the Odd/Even Checker and Encryption/Decryption of Image Applications. Adv. Funct. Mater. 2024, 34, 2313219. [Google Scholar] [CrossRef]

- Su, B.; Cai, J.; Zhang, Y.; Wang, Y.; Wang, S.; Wen, K. A 1T2M memristor-based logic circuit and its applications. Microelectron. J. 2023, 132, 105674. [Google Scholar] [CrossRef]

- Lu, C.; Meng, J.; Yu, J.; Song, J.; Wang, T.; Zhu, H.; Sun, Q.Q.; Zhang, D.W.; Chen, L. Novel three-dimensional artificial neural network based on an eight-layer vertical memristor with an ultrahigh rectify ratio (>107) and an ultrahigh nonlinearity (>105) for neuromorphic computing. Nano Lett. 2024, 24, 2018–2024. [Google Scholar] [CrossRef]

- Jeon, K.; Ryu, J.J.; Im, S.; Seo, H.K.; Eom, T.; Ju, H.; Yang, M.K.; Jeong, D.S.; Kim, G.H. Purely self-rectifying memristor-based passive crossbar array for artificial neural network accelerators. Nat. Commun. 2024, 15, 129. [Google Scholar] [CrossRef]

- Cao, Z.; Sun, B.; Zhou, G.; Mao, S.; Zhu, S.; Zhang, J.; Ke, C.; Zhao, Y.; Shao, J. Memristor-based neural networks: A bridge from device to artificial intelligence. Nanoscale Horiz. 2023, 8, 716–745. [Google Scholar] [CrossRef] [PubMed]

- Khot, A.C.; Nirmal, K.A.; Dongale, T.D.; Kim, T.G. GeTe/MoTe2 Van der Waals Heterostructures: Enabling Ultralow Voltage Memristors for Nonvolatile Memory and Neuromorphic Computing Applications. Small 2024, 2400791. [Google Scholar] [CrossRef] [PubMed]

- Sattar, K.; Tahir, R.; Huang, H.; Akinwande, D.; Rizwan, S. Ferroelectric MXene-assisted BiFeO3 based free-standing memristors for multifunctional non-volatile memory storage. Carbon 2024, 221, 118931. [Google Scholar] [CrossRef]

- Koncha, G.; Das, N.K.; Badhulika, S. Ni3C nanosheets and PVA nanocomposite based memristor for low-cost and flexible non-volatile memory devices. Mater. Sci. Semicond. Process. 2024, 184, 108804. [Google Scholar] [CrossRef]

- Guseinov, D.; Matyushkin, I.; Chernyaev, N.; Mikhaylov, A.; Pershin, Y. Capacitive effects can make memristors chaotic. Chaos Solitons Fractals 2021, 144, 110699. [Google Scholar] [CrossRef]

- Ostrovskii, V.; Fedoseev, P.; Bobrova, Y.; Butusov, D. Structural and parametric identification of knowm memristors. Nanomaterials 2021, 12, 63. [Google Scholar] [CrossRef]

- Guo, M.; Yang, W.; Xue, Y.; Gao, Z.; Yuan, F.; Dou, G.; Li, Y. Multistability in a physical memristor-based modified Chua’s circuit. Chaos Interdiscip. J. Nonlinear Sci. 2019, 29, 043114. [Google Scholar] [CrossRef]

- Laskaridis, L.; Volos, C.; Stouboulos, I. Study of a chaotic circuit with a physical memristor as a nonlinear resistor. In Proceedings of the 2022 11th International Conference on Modern Circuits and Systems Technologies (MOCAST), Bremen, Germany, 8–10 June 2022; IEEE: New York, NY, USA, 2022; pp. 1–4. [Google Scholar]

- Minati, L.; Gambuzza, L.; Thio, W.; Sprott, J.; Frasca, M. A chaotic circuit based on a physical memristor. Chaos Solitons Fractals 2020, 138, 109990. [Google Scholar] [CrossRef]

- Kengne, J.; Njitacke Tabekoueng, Z.; Kamdoum Tamba, V.; Nguomkam Negou, A. Periodicity, chaos, and multiple attractors in a memristor-based Shinriki’s circuit. Chaos Interdiscip. J. Nonlinear Sci. 2015, 25. [Google Scholar] [CrossRef]

- Wu, R.; Wang, C. A new simple chaotic circuit based on memristor. Int. J. Bifurc. Chaos 2016, 26, 1650145. [Google Scholar] [CrossRef]

- Das, P.; Mandal, S. A physical memristor-based chaotic system and its application in colour image encryption scheme. Phys. Scr. 2023, 98, 115252. [Google Scholar] [CrossRef]

- Ma, X.; Mou, J.; Liu, J.; Ma, C.; Yang, F.; Zhao, X. A novel simple chaotic circuit based on memristor–memcapacitor. Nonlinear Dyn. 2020, 100, 2859–2876. [Google Scholar] [CrossRef]

- Ostrovskii, V.; Karimov, T.; Rybin, V.; Bobrova, Y.; Arlyapov, V.; Butusov, D. Bio-inspired neuron based on threshold selector and tunnel diode capable of excitability modulation. Neurocomputing 2025, 624, 129454. [Google Scholar] [CrossRef]

- Escudero, M.; Spiga, S.; Di Marco, M.; Forti, M.; Innocenti, G.; Tesi, A.; Corinto, F.; Brivio, S. Chua’s circuit with tunable nonlinearity based on a nonvolatile memristor: Design and realization. IEEE Trans. Circuits Syst. I Regul. Pap. 2023, 71, 62–72. [Google Scholar] [CrossRef]

- Bao, B.; Jiang, T.; Wang, G.; Jin, P.; Bao, H.; Chen, M. Two-memristor-based Chua’s hyperchaotic circuit with plane equilibrium and its extreme multistability. Nonlinear Dyn. 2017, 89, 1157–1171. [Google Scholar] [CrossRef]

- Nguyen, N.; Kaddoum, G.; Pareschi, F.; Rovatti, R.; Setti, G. A fully CMOS true random number generator based on hidden attractor hyperchaotic system. Nonlinear Dyn. 2020, 102, 2887–2904. [Google Scholar] [CrossRef]

- Valencia-Ponce, M.A.; González-Zapata, A.M.; de la Fraga, L.G.; Sanchez-Lopez, C.; Tlelo-Cuautle, E. Integrated Circuit Design of Fractional-Order Chaotic Systems Optimized by Metaheuristics. Electronics 2023, 12, 413. [Google Scholar] [CrossRef]

- Juarez-Mendoza, E.; del Angel-Diaz, F.A.; Diaz-Sanchez, A.; Tlelo-Cuautle, E. CMOS design of chaotic systems using biquadratic OTA-C filters. J. Low Power Electron. Appl. 2024, 14, 14. [Google Scholar] [CrossRef]

- Joshi, M.; Ranjan, A. Low power chaotic oscillator employing CMOS. Integration 2022, 85, 57–62. [Google Scholar] [CrossRef]

- Muthuswamy, B.; Chua, L.O. Simplest chaotic circuit. Int. J. Bifurc. Chaos 2010, 20, 1567–1580. [Google Scholar] [CrossRef]

- Gupta, S.; Rai, S.K. New grounded and floating decremental/incremental memristor emulators based on CDTA and its application. Wirel. Pers. Commun. 2020, 113, 773–798. [Google Scholar] [CrossRef]

- Sharma, P.K.; Prasad, S.S.; Tasneem, S.; Priyadarshini, B.; Ranjan, R.K. Resistive tunable memristor emulator model and its application. AEU-Int. J. Electron. Commun. 2023, 160, 154500. [Google Scholar] [CrossRef]

- Raj, N.; Ranjan, R.K.; Khateb, F. Flux-controlled memristor emulator and its experimental results. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2020, 28, 1050–1061. [Google Scholar] [CrossRef]

- Yadav, N.; Rai, S.K.; Pandey, R. New grounded and floating memristor emulators using OTA and CDBA. Int. J. Circuit Theory Appl. 2020, 48, 1154–1179. [Google Scholar] [CrossRef]

- Ghosh, M.; Mondal, P.; Borah, S.S.; Kumar, S. Resistorless memristor emulators: Floating and grounded using OTA and VDBA for high-frequency applications. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2022, 42, 978–986. [Google Scholar] [CrossRef]

- Petrović, P.B. Tunable flux-controlled floating memristor emulator circuits. IET Circuits Devices Syst. 2019, 13, 479–486. [Google Scholar] [CrossRef]

- Ranjan, R.K.; Kang, S.M. Resistorless Floating/Grounded Memristor Emulator Model with Electronic Tunability. IEEE Trans. Circuits Syst. II Express Briefs 2023, 70, 2340–2344. [Google Scholar]

- Kanyal, G.; Kumar, P.; Paul, S.K.; Kumar, A. OTA based high frequency tunable resistorless grounded and floating memristor emulators. AEU-Int. J. Electron. Commun. 2018, 92, 124–145. [Google Scholar] [CrossRef]

- Kumar, N.; Kumar, M. Low power CMOS differential ring VCO designs using dual delay stages in 0.13 μm technology for wireless applications. Microelectron. J. 2021, 111, 105025. [Google Scholar] [CrossRef]

- Jirsa, J.; Marcisovsky, M.; Jakovenko, J. Multi-threshold window discriminator based on SAR logic. J. Instrum. 2022, 17, C01042. [Google Scholar] [CrossRef]

- Fontanela, F.; Grolet, A.; Salles, L.; Hoffmann, N. Computation of quasi-periodic localised vibrations in nonlinear cyclic and symmetric structures using harmonic balance methods. J. Sound Vib. 2019, 438, 54–65. [Google Scholar] [CrossRef]

- Duan, Z.; Wang, H.; He, S.; Li, S.; Yan, S.; Zhao, X.; Yu, X.; Yang, G.; Tan, H. A fully integrated chaos generator based on voltage controlled oscillator. Microelectron. J. 2022, 126, 105514. [Google Scholar] [CrossRef]

- Joshi, M.; Ranjan, A. An autonomous chaotic and hyperchaotic oscillator using OTRA. Analog. Integr. Circuits Signal Process. 2019, 101, 401–413. [Google Scholar] [CrossRef]

- Kushwaha, A.K.; Paul, S.K. Inductorless realization of Chua’s oscillator using DVCCTA. Analog. Integr. Circuits Signal Process. 2016, 88, 137–150. [Google Scholar] [CrossRef]

- Nguyen, V.H.; Huynh, H.A.; Kim, S.; Song, H. Active EMI reduction using chaotic modulation in a buck converter with relaxed output LC filter. Electronics 2018, 7, 254. [Google Scholar] [CrossRef]

- Wannaboon, C.; Tachibana, M.; San-Um, W. A 0.18-µm CMOS high-data-rate true random bit generator through δσ modulation of chaotic jerk circuit signals. Chaos Interdiscip. J. Nonlinear Sci. 2018, 28, 063126. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).