Preparation and Performance Exploration of MoS2/WSe2 Van Der Waals Heterojunction Tunneling Field-Effect Transistor

Abstract

1. Introduction

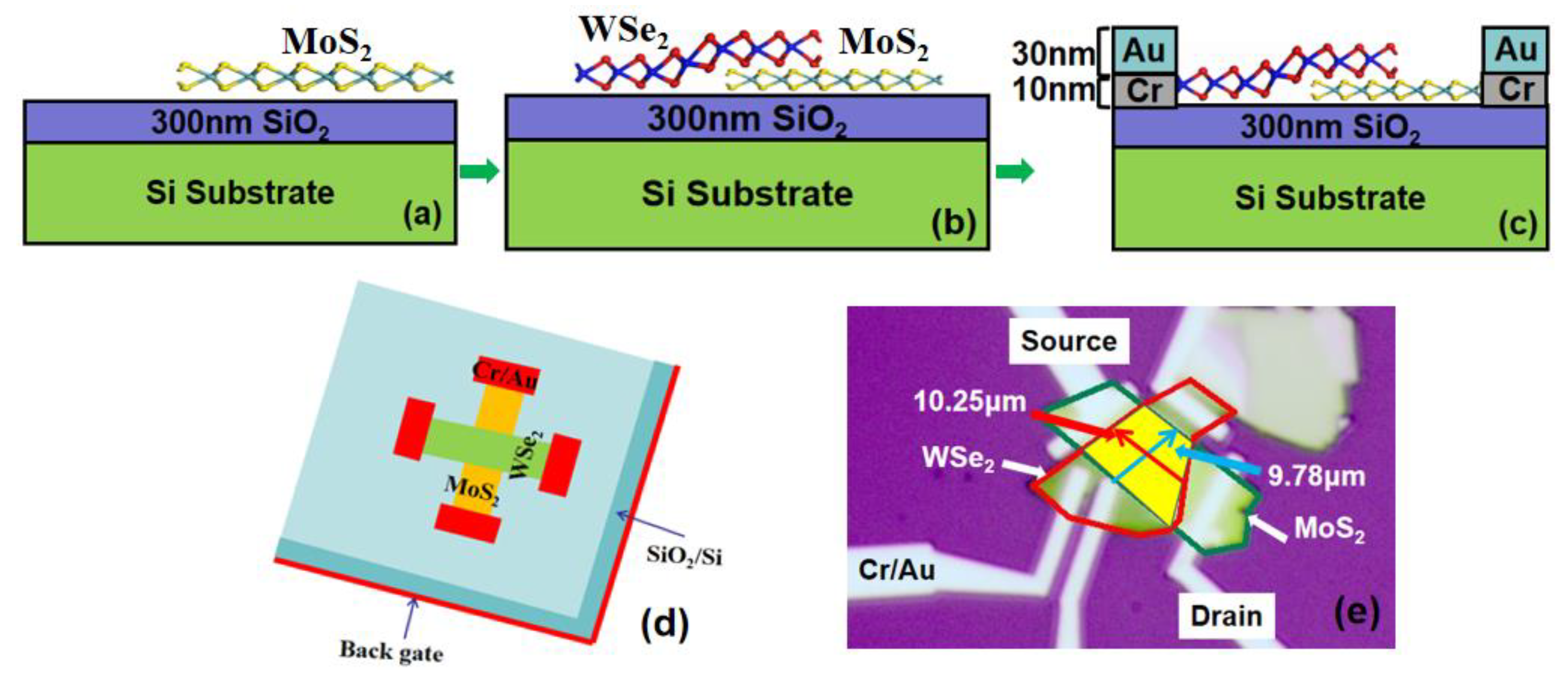

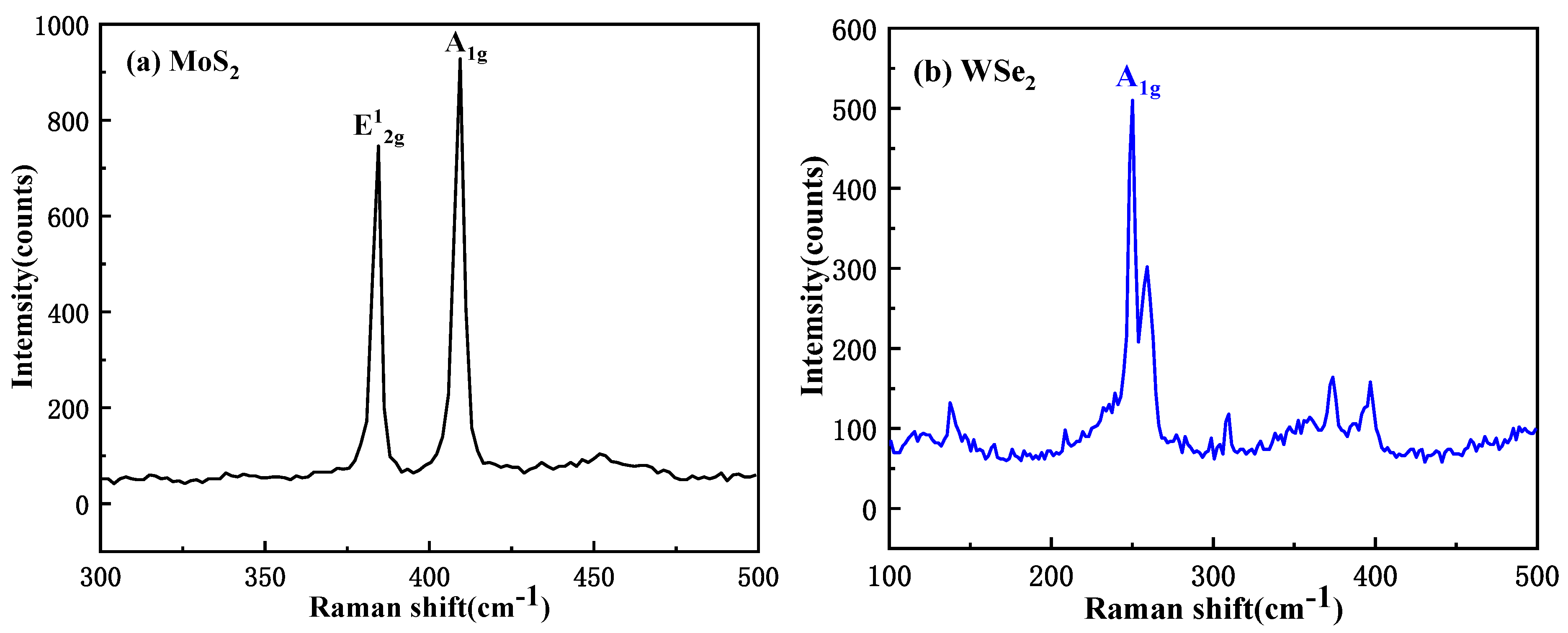

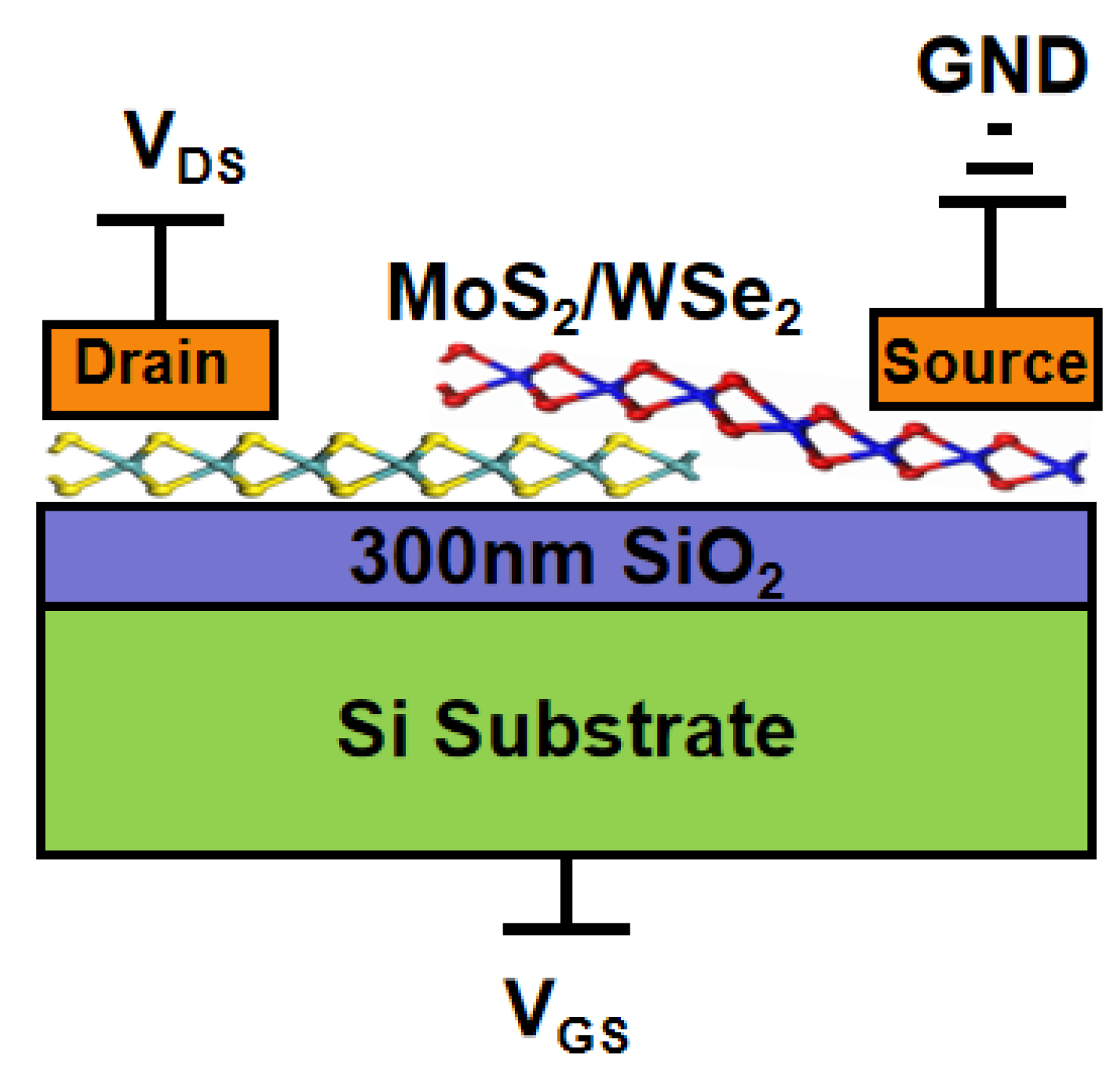

2. Material Synthesis and Device Fabrication

- (a)

- Photolithographic patterning was performed on a p+-Si substrate with 300 nm thermal oxide to define alignment markers.

- (b)

- Few-layer MoS2 flakes were mechanically exfoliated from bulk crystal and precisely transferred onto designated coordinates using a dry-transfer technique.

- (c)

- Similarly, WSe2 flakes were exfoliated onto a polydimethylsiloxane (PDMS) elastomer stamp.

- (d)

- Using a micro-manipulator under an optical microscope, WSe2 was aligned and transferred onto the pre-placed MoS2 flake through thermal release to form an intimate van der Waals heterojunction.

- (e)

- Electron-beam lithography followed by electron-beam evaporation of Cr/Au (10/30 nm) was used to define electrical contacts.

3. Results and Discussion

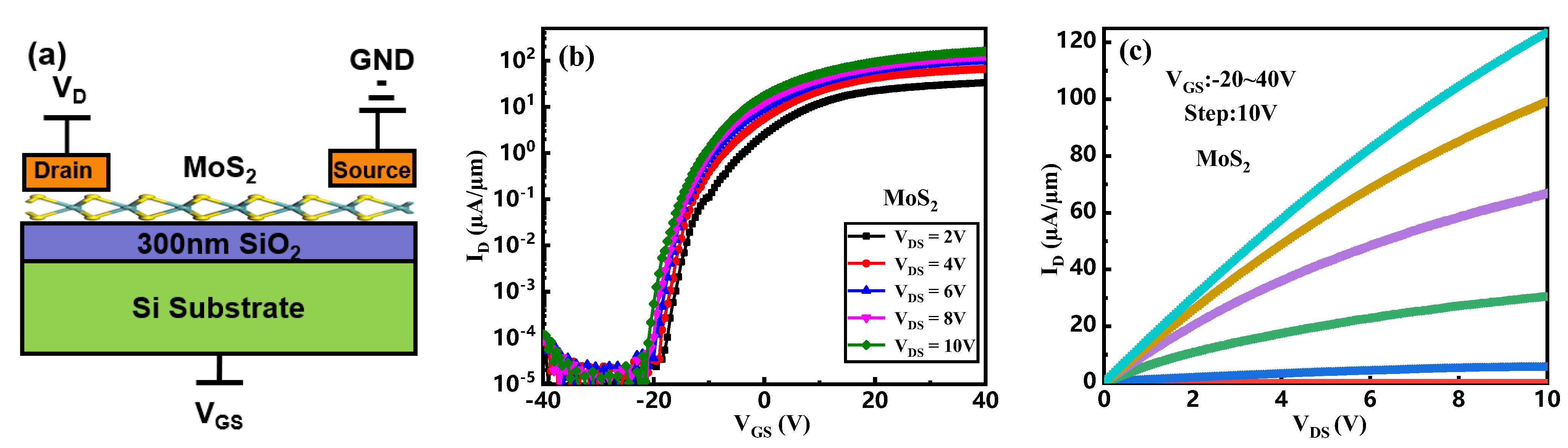

3.1. MoS2 FET

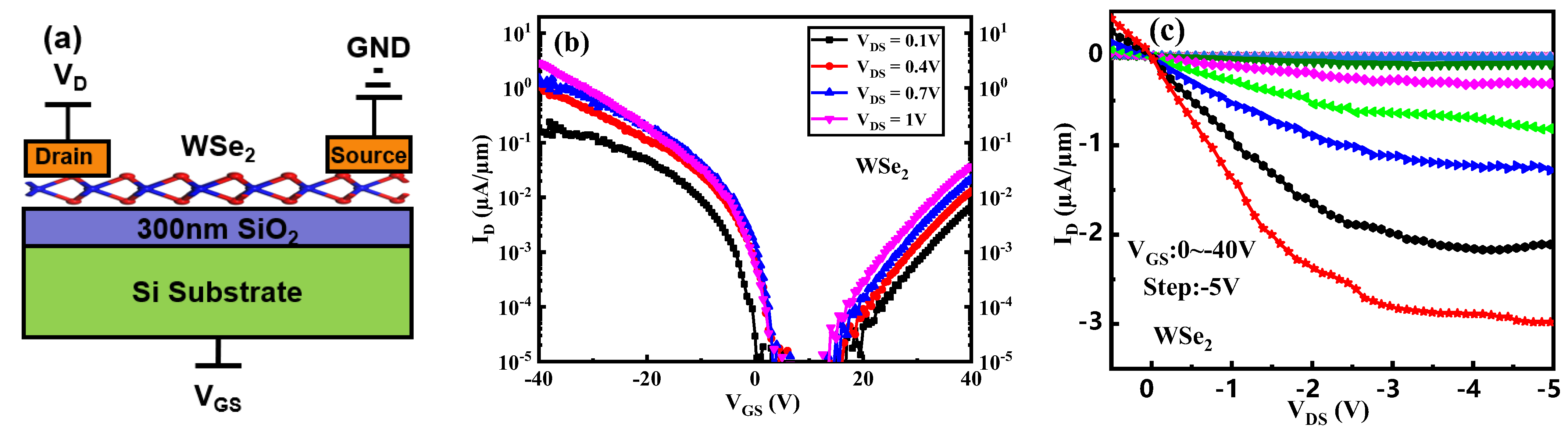

3.2. WSe2 FET

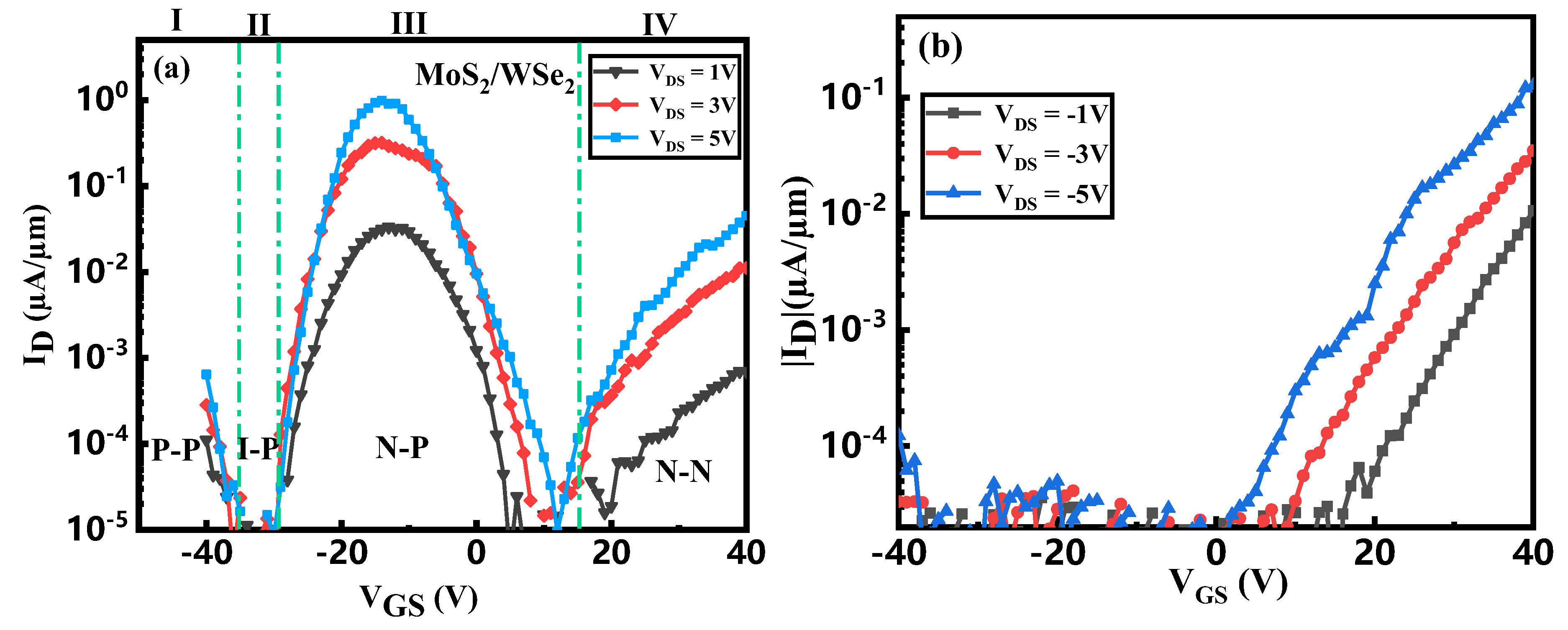

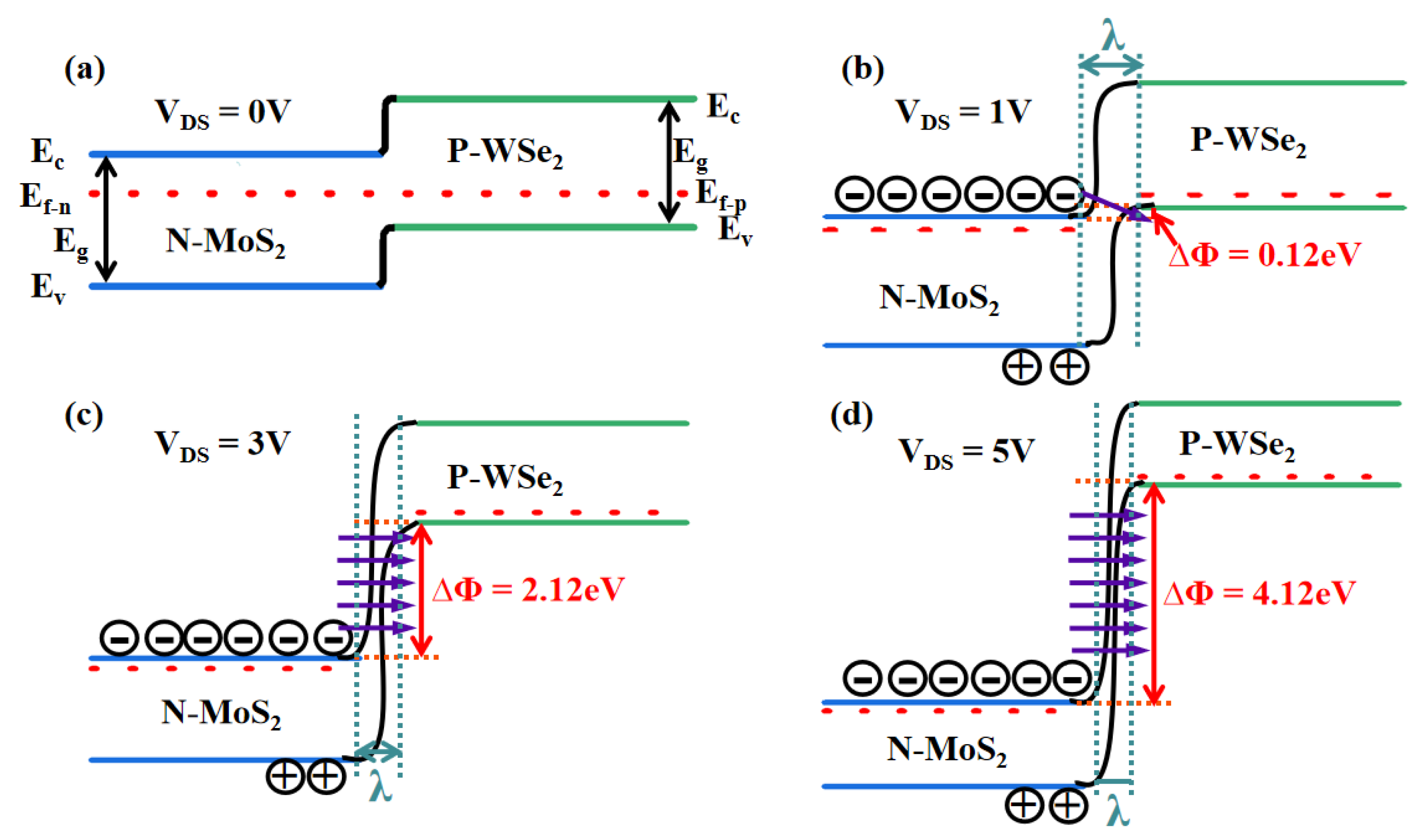

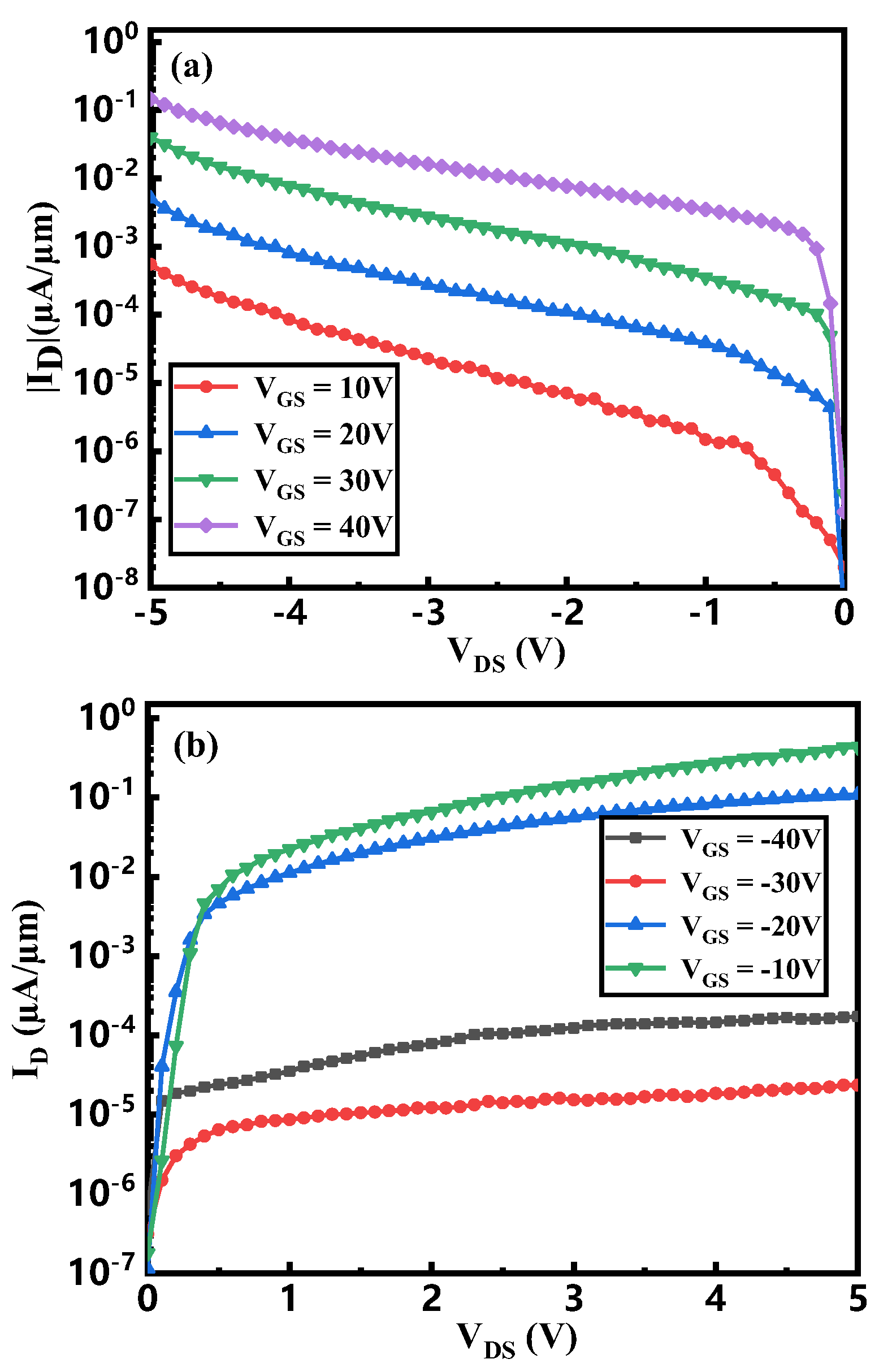

3.3. MoS2/WSe2 Vdwh TFET

- For VGS < −35 V, the device operates in a P–P state, characterized by strong hole accumulation in WSe2 and weak hole accumulation in MoS2.

- Within the range of −35 V < VGS < −30 V, the device enters an I–P state, where WSe2 maintains strong hole accumulation while MoS2 remains in the off-state.

- Over the interval −30 V < VGS < 15 V, an N–P state emerges, featuring strong hole accumulation in WSe2 and pronounced electron accumulation in MoS2. This regime further divides into two sub-regions: the heterostructure exhibits n-channel FET behavior for −30 V < VGS < −14 V and p-channel FET behavior for −14 V < VGS < 15 V.

- For VGS > 15 V, the device operates in an N–N state, with strong electron accumulation in MoS2 and weak electron accumulation in WSe2.

3.4. Comparison of Key Parameters of Four Different 2Dl FETs

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Ieong, M.; Doris, B.; Kedzierski, J.; Rim, K.; Yang, M. Silicon device scaling to the sub-10-nm regime. Science 2004, 306, 2057–2060. [Google Scholar] [CrossRef] [PubMed]

- Hiblot, G.; Dutta, T.; Rafhay, Q.; Lacord, J.; Akbal, M.; Boeuf, F.; Ghibaudo, G. Accurate Boundary Condition for Short-Channel Effect Compact Modeling in MOS Devices. IEEE Trans. Electron Devices 2015, 62, 28–35. [Google Scholar] [CrossRef]

- Chander, S.; Sinha, S.K.; Chaudhary, R. Comprehensive review on electrical noise analysis of TFET structures. Superlattices Microstruct. 2022, 161, 107101. [Google Scholar] [CrossRef]

- Nasani, K.; Bhowmick, B.; Pukhrambam, P.D. Effect of lateral straggle parameter on Hetero Junction Dual Gate Vertical TFET. Microelectron. J. 2023, 138, 105845. [Google Scholar] [CrossRef]

- Gorla, S.R.K.; Pandey, C.K. Reduced OFF-state current and suppressed ambipolarity in a dopingless vertical TFET with dual-drain for high-frequency circuit applications. AEU-Int. J. Electron. Commun. 2024, 177, 155229. [Google Scholar] [CrossRef]

- Malvika; Choudhuri, B.; Mummaneni, K. A new pocket-doped NCFET for low power applications: Impact of ferroelectric and oxide thickness on its performance. Micro Nanostruct. 2022, 169, 207360. [Google Scholar] [CrossRef]

- Kaushal, S. Introduction to Newly Adopted NCFET and Ferroelectrics for Low-Power Application. In Advanced Ultra Low-Power Semiconductor Devices: Design and Applications; Scrivener Publishing LLC.: Beverly, MA, USA, 2023; pp. 207–234. [Google Scholar]

- Giubileo, F.; Di Bartolomeo, A. The role of contact resistance in graphene field-effect devices. Prog. Surf. Sci. 2017, 92, 143–175. [Google Scholar] [CrossRef]

- Geim, A.; Grigorieva, I. Van der Waals heterostructures. Nature 2013, 499, 419–425. [Google Scholar] [CrossRef]

- Cao, W.; Kang, J.; Sarkar, D.; Liu, W.; Banerjee, K. 2D semiconductor FETs—Projections and design for sub-10 nm VLSI. IEEE Trans. Electron Devices 2015, 62, 3459–3469. [Google Scholar] [CrossRef]

- Berahman, M.; Aghasi, H. Tunneling Field Effect Transistors Based on Janus Monolayer PtSSe. IEEE Trans. Nanotechnol. 2025, 24, 369–377. [Google Scholar] [CrossRef]

- Wang, Q.H.; Kalantar-Zadeh, K.; Kis, A.; Coleman, J.N.; Strano, M.S. Electronics and optoelectronics of two-dimensional transition metal dichalcogenides. Nat. Nanotechnol. 2012, 7, 699–712. [Google Scholar] [CrossRef]

- Liu, L.; Liu, C.; Huang, X.; Zeng, S.; Tang, Z.; Zhang, D.W.; Zhou, P. Tunable Current Regulative Diode Based on Van der Waals Stacked MoS2/WSe2 Heterojunction–Channel Field-Effect Transistor. Adv. Electron. Mater. 2022, 8, 2100869. [Google Scholar] [CrossRef]

- Nourbakhsh, A.; Zubair, A.; Dresselhaus, M.S.; Palacios, T. Transport properties of a MoS2/WSe2 heterojunction transistor and its potential for application. Nano Lett. 2016, 16, 1359–1366. [Google Scholar] [CrossRef]

- Zhao, J.; Li, N.; Yu, H.; Wei, Z.; Liao, M.; Chen, P.; Wang, S.; Shi, D.; Sun, Q.; Zhang, G. Highly Sensitive MoS2 Humidity Sensors Array for Noncontact Sensation. Adv. Mater. 2017, 29, 1702076. [Google Scholar] [CrossRef]

- Di Bartolomeo, A.; Kumar, A.; Durante, O.; Sessa, A.; Faella, E.; Viscardi, L.; Intonti, K.; Giubileo, F.; Martucciello, N.; Romano, P.; et al. Temperature-dependent photoconductivity in two-dimensional MoS2 transistors. Mater. Today Nano 2023, 24, 100382. [Google Scholar] [CrossRef]

- Chava, P.; Kateel, V.; Watanabe, K.; Taniguchi, T.; Helm, M.; Mikolajick, T.; Erbe, A. Electrical characterization of multi-gated WSe2/MoS2 van der Waals heterojunctions. Sci. Rep. 2024, 14, 5813. [Google Scholar] [CrossRef]

- Yang, M.; Lu, Y.; Zhang, Q.; Han, Z.; Zhang, Y.; Liu, M.; Zhang, N.; Hu, H.; Wang, L. Charge transport behaviors in a multi-gated WSe2/MoS2 heterojunction. Appl. Phys. Lett. 2022, 121, 043501. [Google Scholar] [CrossRef]

- Silvestri, L.; Palsgaard, M.; Rhyner, R.; Frey, M.; Wellendorff, J.; Smidstrup, S.; Gull, R.; El Sayed, K. Hierarchical modeling for TCAD simulation of short-channel 2D material-based FETs. Solid-State Electron. 2023, 200, 108533. [Google Scholar] [CrossRef]

- Mounir, A.; Iñiguez, B.; Lime, F.; Kloes, A.; Knobloch, T.; Grasser, T. Compact I-V model for back-gated and double-gated TMD FETs. Solid-State Electron. 2023, 207, 108702. [Google Scholar] [CrossRef]

- Bedia, A.; Bedia, F.Z.; Benyoucef, B. 2D Device Modeling and Simulation/FET for Biomedical Applications. Phys. Procedia 2011, 21, 35–41. [Google Scholar] [CrossRef][Green Version]

- Wang, Q.; Sang, P.; Li, Y.; Chen, J. Impacts of Biaxial Tensile Strain in Double-gate Tunneling Field-effect-transistor (DG-TFET) with a Monolayer WSe2 Channel. In Proceedings of the 2020 IEEE Silicon Nanoelectronics Workshop (SNW), Honolulu, HI, USA, 13–14 June 2020. [Google Scholar]

- Chen, F.; Ilatikhameneh, H.; Tan, Y.; Valencia, D.; Klimeck, G.; Rahman, R. Transport in vertically stacked hetero-structures from 2D materials. J. Phys. Conf. Ser. 2016, 864, 012053. [Google Scholar] [CrossRef]

- Afzalian, A.; Akhoundi, E.; Gaddemane, G.; Duflou, R.; Houssa, M. Advanced DFT–NEGF Transport Techniques for Novel 2-D Material and Device Exploration Including HfS2/WSe2 van der Waals Heterojunction TFET and WTe2/WS2 Metal/Semiconductor Contact. IEEE Trans. Electron Devices 2021, 68, 5372–5379. [Google Scholar] [CrossRef]

- Roy, T.; Tosun, M.; Cao, X.; Fang, H.; Lien, D.H.; Zhao, P.; Chen, Y.; Chuen, Y.; Guo, J.; Javey, A. Dual-gated MoS2/WSe2 van der Waals tunnel diodes and transistors. ACS Nano 2015, 9, 2071–2079. [Google Scholar] [CrossRef]

- Roy, T.; Tosun, M.; Hettick, M.; Ahn, G.H.; Hu, C.; Javey, A. 2D-2D tunneling field-effect transistors using WSe2/SnSe2 heterostructures. Appl. Phys. Lett. 2016, 108, 083111. [Google Scholar] [CrossRef]

- Kanungo, S.; Ahmad, G.; Sahatiya, P.; Mukhopadhyay, A.; Chattopadhyay, S. 2D materials-based nanoscale tunneling field effect transistors: Current developments and future prospects. NPJ 2D Mater. Appl. 2022, 6, 83. [Google Scholar] [CrossRef]

- Si, K.; Ma, J.; Lu, C.; Zhou, Y.; He, C.; Yang, D.; Wang, X.; Xu, X. A two-dimensional MoS2/WSe2 van der Waals heterostructure for enhanced photoelectric performance. Appl. Surf. Sci. 2020, 507, 145082. [Google Scholar] [CrossRef]

- Yang, S.H.; Yao, Y.T.; Xu, Y.; Lin, C.Y.; Chang, Y.M.; Suen, Y.W.; Sun, H.; Lien, C.; Li, W.; Lin, Y. Atomically thin van der waals tunnel field-effect transistors and its potential for applications. Nanotechnology 2018, 30, 105201. [Google Scholar] [CrossRef] [PubMed]

- Sarkar, D.; Xie, X.; Liu, W.; Cao, W.; Kang, J.; Gong, Y.; Kraemer, S.; Ajayan, P.M.; Banerjee, K. A subthermionic tunnel field-effect transistor with an atomically thin channel. Nature 2015, 526, 91–95. [Google Scholar] [CrossRef]

- Han, T.; Liu, H.; Wang, S.; Chen, S.; Xie, H.; Yang, K. Probing the Field-Effect Transistor with Monolayer MoS2 Prepared by APCVD. Nanomaterials 2019, 9, 1209. [Google Scholar] [CrossRef]

- Mbisike, S.C.; Tsiamis, A.; Lomax, P.; Cheung, R. Anodic tantalum: Fabrication, breakdown characteristics of capacitor and integration with a WSe2 field effect transistor. Solid-State Electron. 2022, 196, 108423. [Google Scholar] [CrossRef]

- Kumar, A.; Faella, E.; Durante, O.; Giubileo, F.; Pelella, A.; Viscardi, L.; Intonti, K.; Sleziona, S.; Schleberger, M.; Di Bartolomeo, A. Optoelectronic memory in 2D MoS2 field effect transistor. J. Phys. Chem. Solids 2023, 179, 111406. [Google Scholar] [CrossRef]

- Schenk, A.; Heiser, G. Modeling and simulation of tunneling through ultra-thin gate dielectrics. J. Appl. Phys. 1997, 81, 7900–7908. [Google Scholar] [CrossRef]

- Oezcelik, V.O.; Azadani, J.G.; Yang, C.; Koester, S.J.; Low, T. Band Alignment of 2D Semiconductors for Designing Heterostructures with Momentum Space Matching. Phys. Rev. B 2016, 16, 02619. [Google Scholar]

- He, F.; Qin, Y.; Wan, L.; Su, J.; Lin, Z.; Zhang, J.; Chang, J.; Wu, J.; Hao, Y. Metal oxide heterojunctions for high performance solution grown oxide thin film transistors. Appl. Surf. Sci. 2020, 527, 146774. [Google Scholar] [CrossRef]

| FET | µsat (cm2 V−1 s−1) | Vth (V) | SS (V/Dec) | Ion/Ioff | Ion (µA/µm) | Ioff (µA/µm) |

|---|---|---|---|---|---|---|

| MoS2 NFET | 26 ± 2 | −21~−18 | 3.3 | 2.4 × 108 | 157 | 6.5 × 10−6 |

| WSe2 PFET | 0.3 ± 0.1 | 0~5 | 4.7 | 2.9 × 104 | 2.9 | 1 × 10−4 |

| MoS2/WSe2 NTFET | 0.8 ± 0.1 | −32~−30 | 4.0 | 1.15 × 105 | 0.99 | 8.6 × 10−6 |

| MoS2/WSe2 PTFET | 0.5 ± 0.2 | 5~10 | 5.2 | 1.03 × 105 | 0.99 | 9.6 × 10−6 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chong, C.; Liu, H.; Wang, S.; Chen, S.; Yan, C. Preparation and Performance Exploration of MoS2/WSe2 Van Der Waals Heterojunction Tunneling Field-Effect Transistor. Micromachines 2025, 16, 1108. https://doi.org/10.3390/mi16101108

Chong C, Liu H, Wang S, Chen S, Yan C. Preparation and Performance Exploration of MoS2/WSe2 Van Der Waals Heterojunction Tunneling Field-Effect Transistor. Micromachines. 2025; 16(10):1108. https://doi.org/10.3390/mi16101108

Chicago/Turabian StyleChong, Chen, Hongxia Liu, Shulong Wang, Shupeng Chen, and Cong Yan. 2025. "Preparation and Performance Exploration of MoS2/WSe2 Van Der Waals Heterojunction Tunneling Field-Effect Transistor" Micromachines 16, no. 10: 1108. https://doi.org/10.3390/mi16101108

APA StyleChong, C., Liu, H., Wang, S., Chen, S., & Yan, C. (2025). Preparation and Performance Exploration of MoS2/WSe2 Van Der Waals Heterojunction Tunneling Field-Effect Transistor. Micromachines, 16(10), 1108. https://doi.org/10.3390/mi16101108