Design of an RRAM-Based Joint Model for Embedded Cellular Smartphone Self-Charging Device

Abstract

1. Introduction

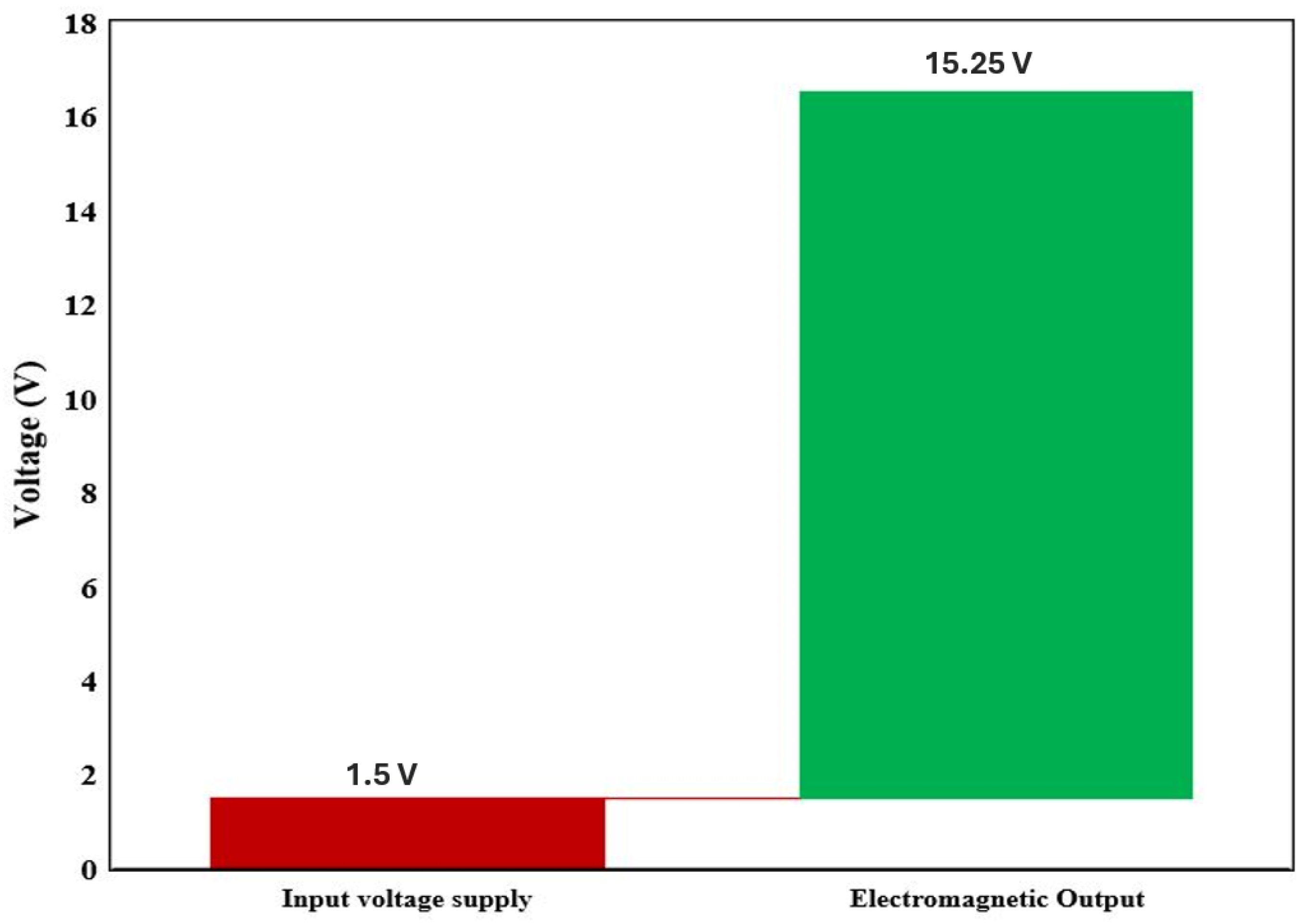

- The successful simulation of the joint RRAM device and the proposed in-built permanent magnet validates its potential for smartphone self-charging. applications.

2. Background and Related Work

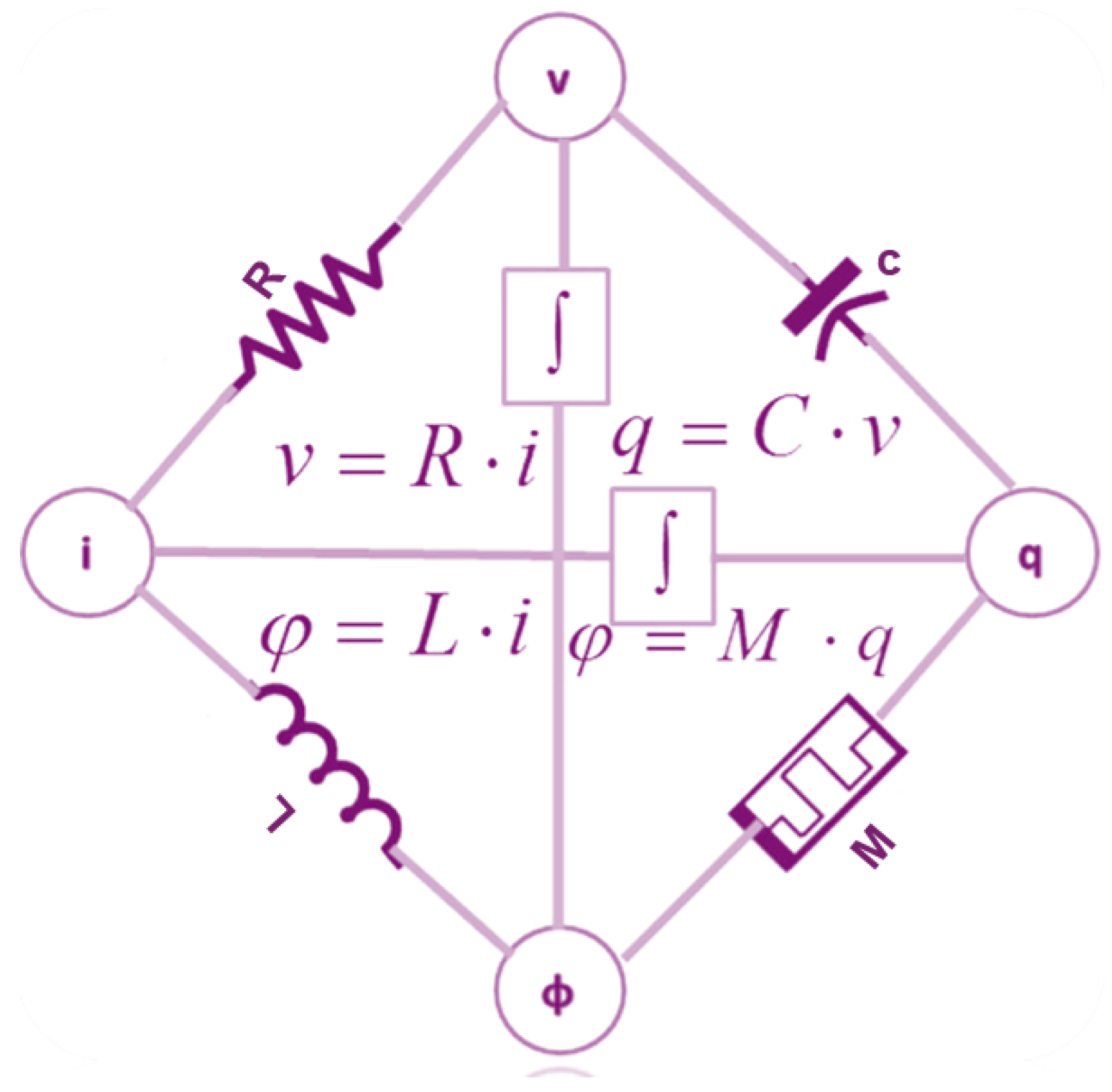

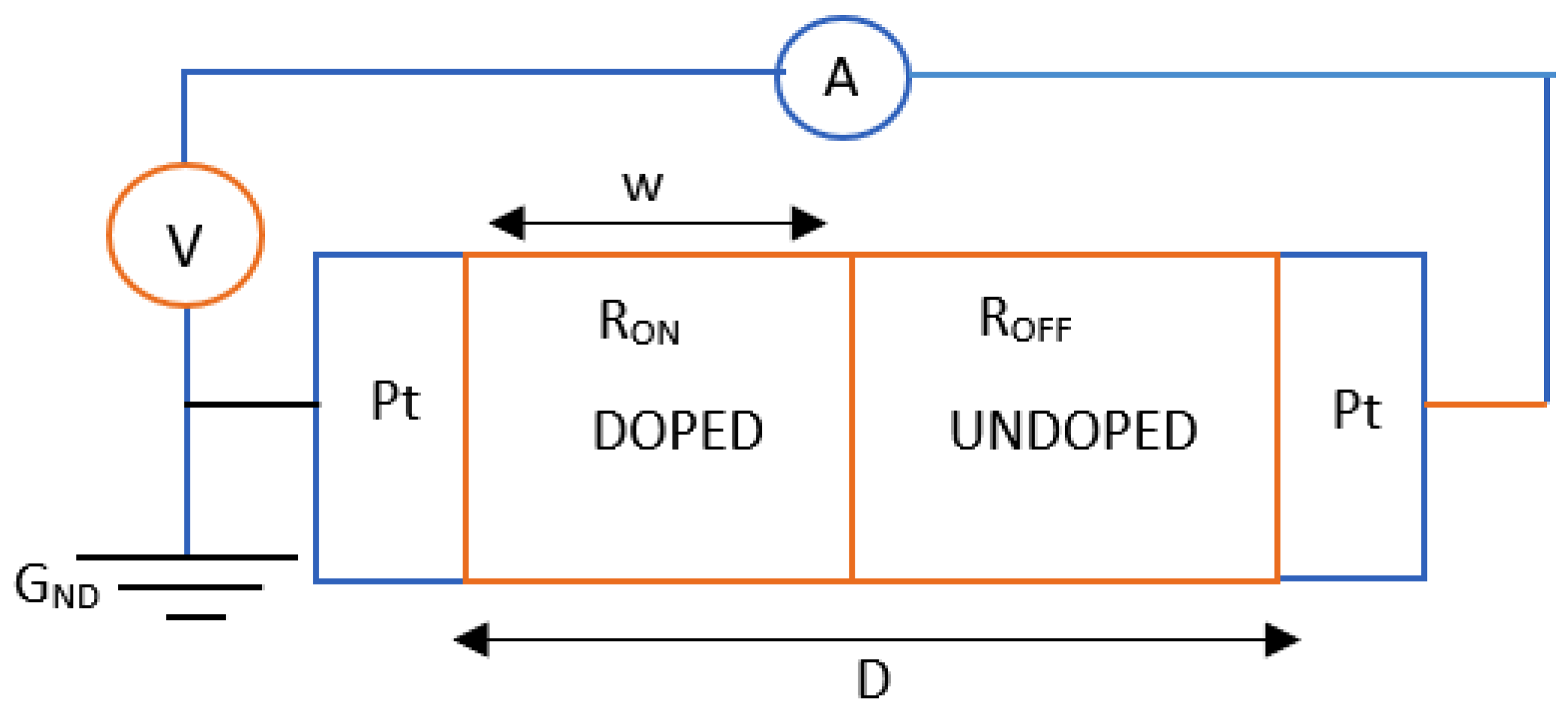

2.1. Memristor Modelling

2.2. Related Work

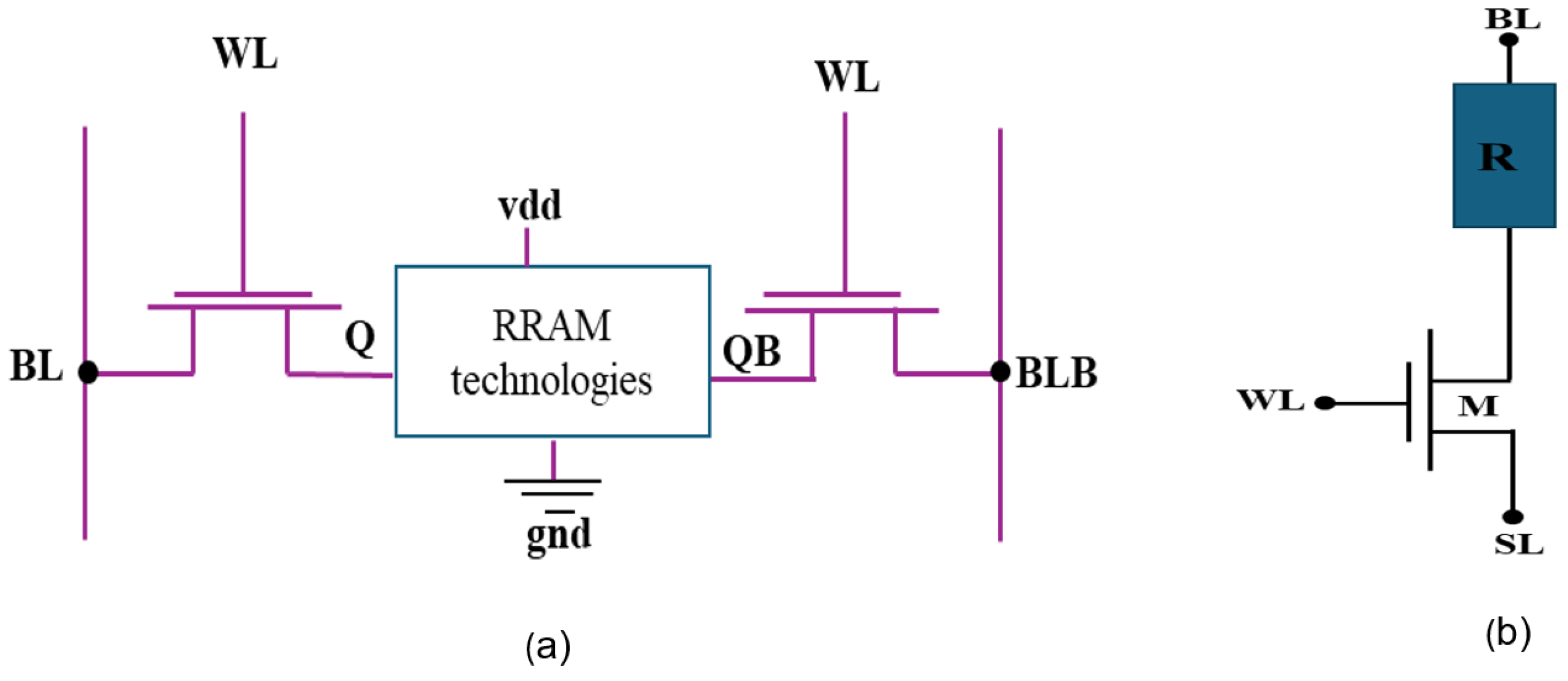

2.3. Existing Structures of NVSRAM Cells

1T1R

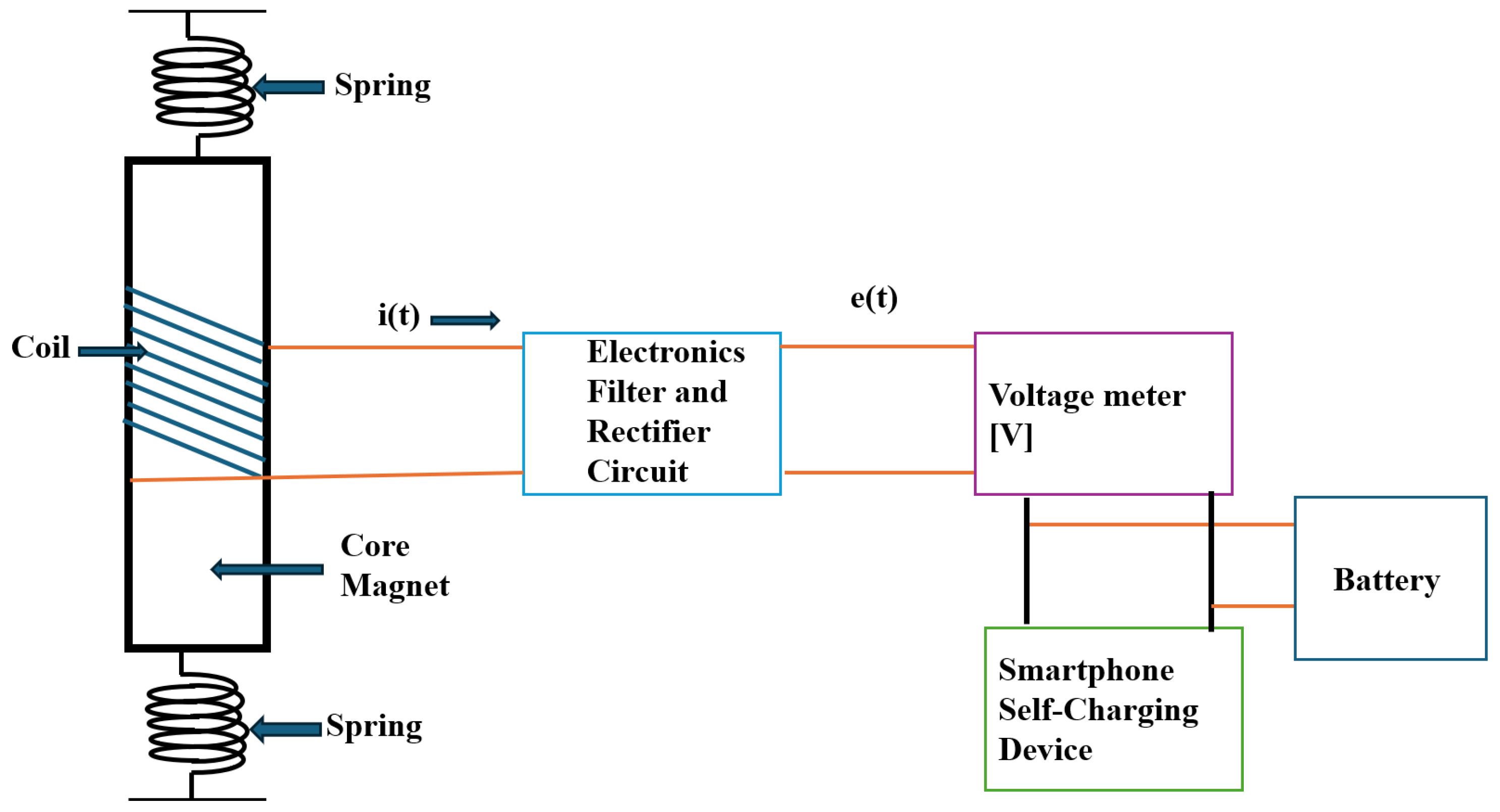

2.4. Energy Generation System

The Self-Generating System Based on Electromagnetic Mechanisms

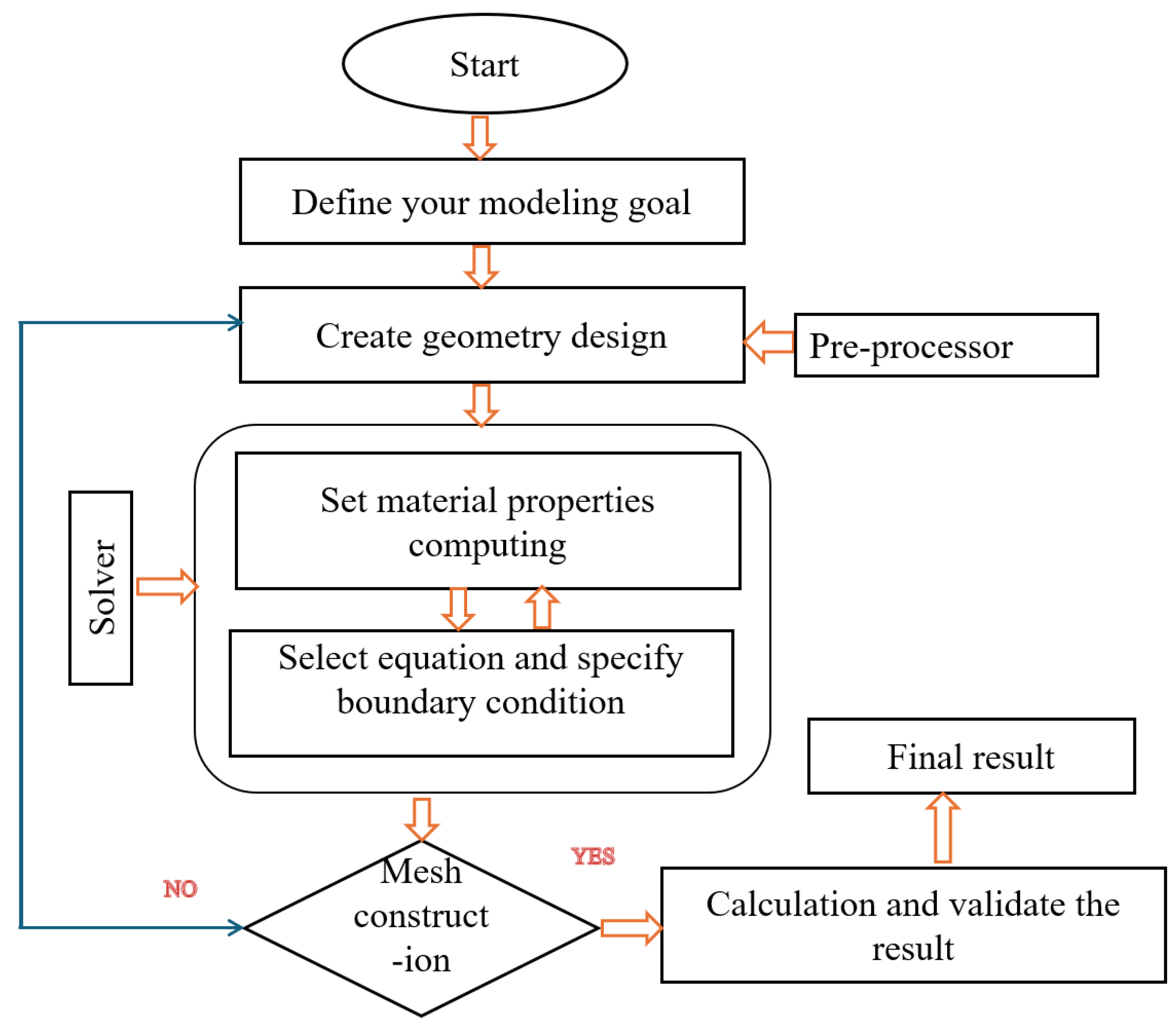

3. Methodology

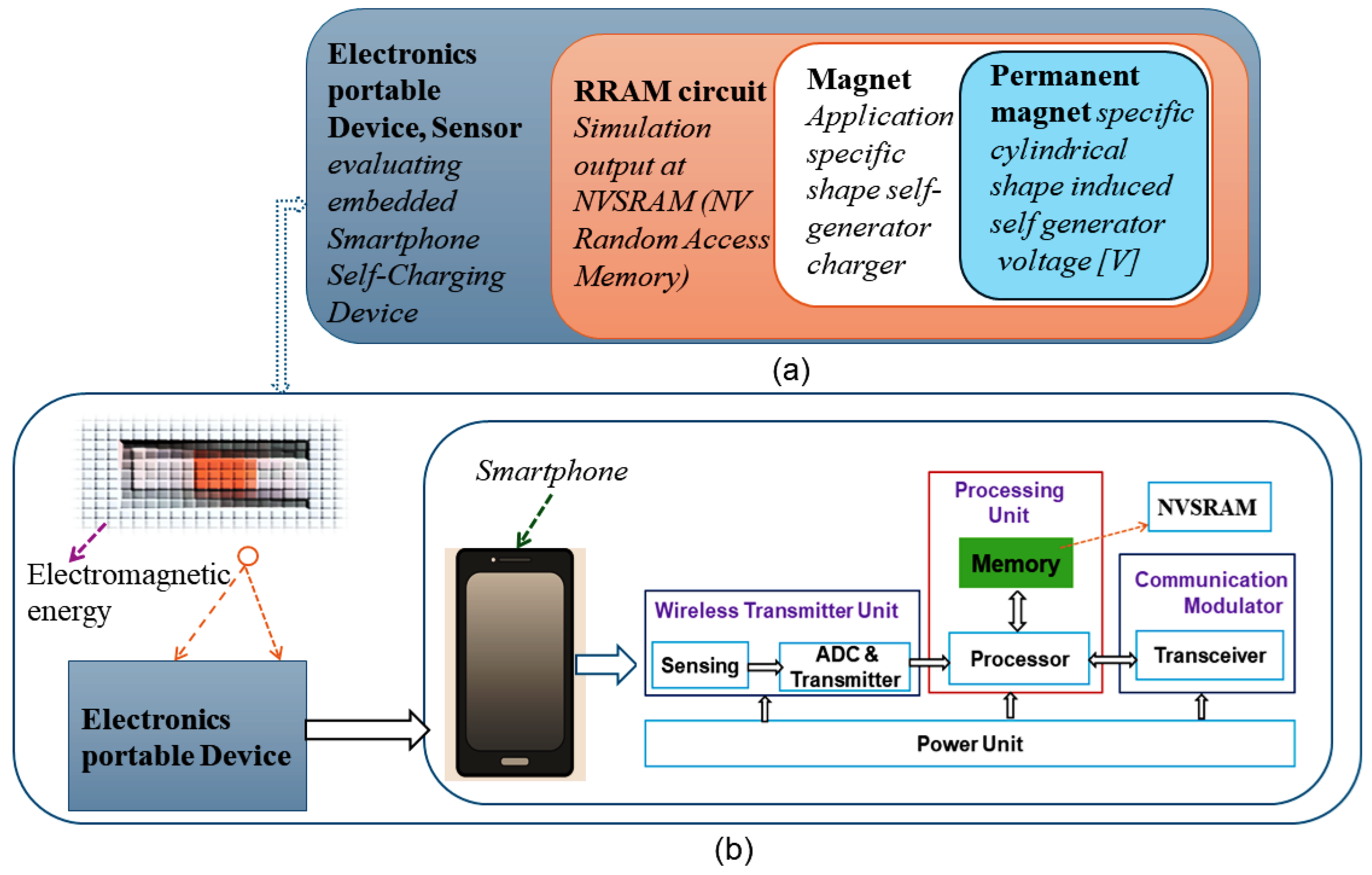

3.1. Concept

3.1.1. The Conventional 6T Cell

- Hold or Standby mode: During standby mode, the world line signal deactivates the access transistors, disconnecting the bit lines voltage from the storage nodes [42].

- Read Mode: During read operation, the WL signal remains active to switch on the access transistors, and the bit lines are pre-charged to vdd. The storage node Q supplies a discharge channel to the matching bit line BL, and the sense amplifier at the read output port detects the voltage difference between the two bitlines [10].

- Write Mode: The bit line is used with the value of be stored in SRAM. The world line control signal activates the cell through the access transistors, which can change the last state of the cross-coupled inverter with the weaker transistor. Therefore, the substitute value is saved [42].

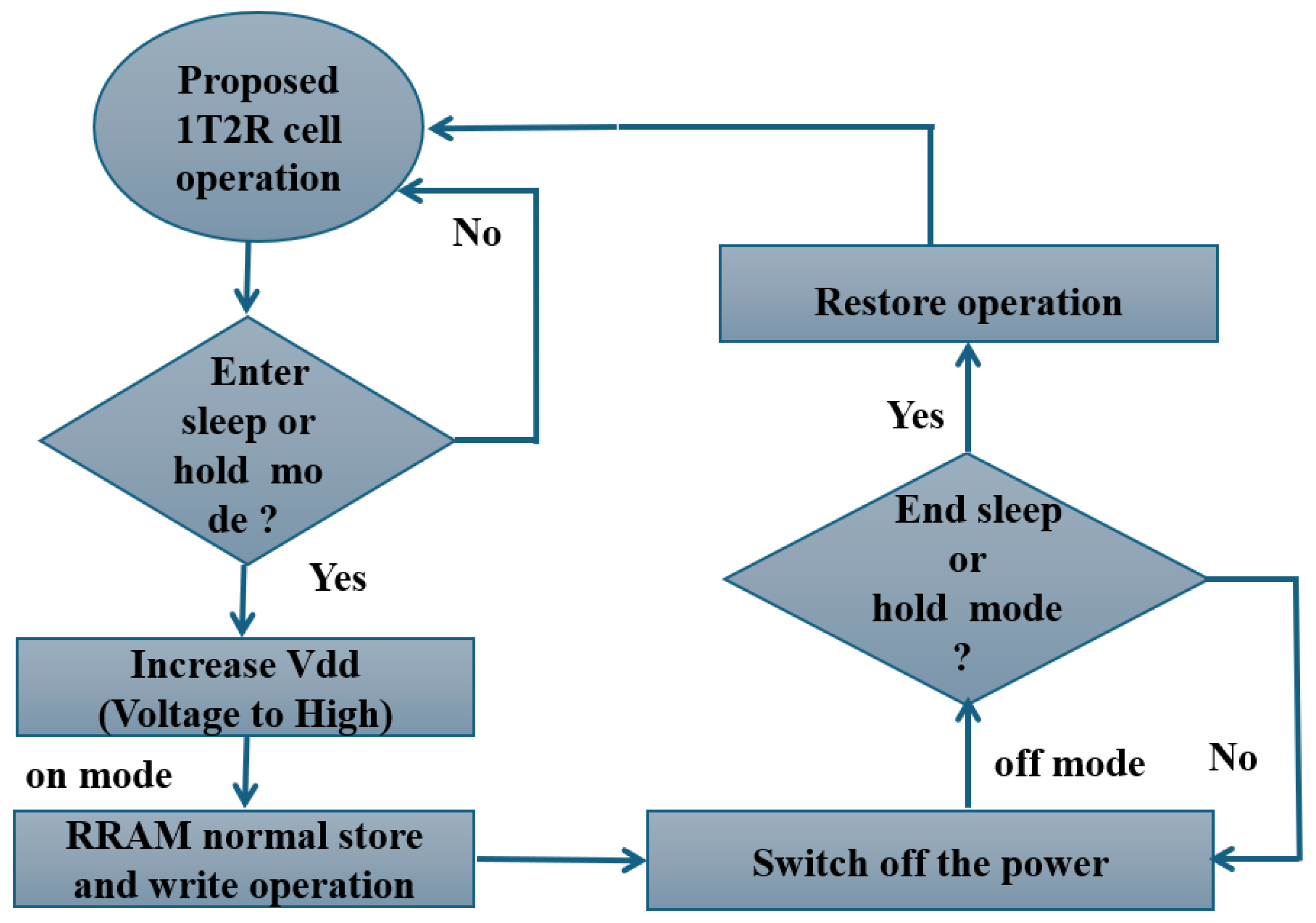

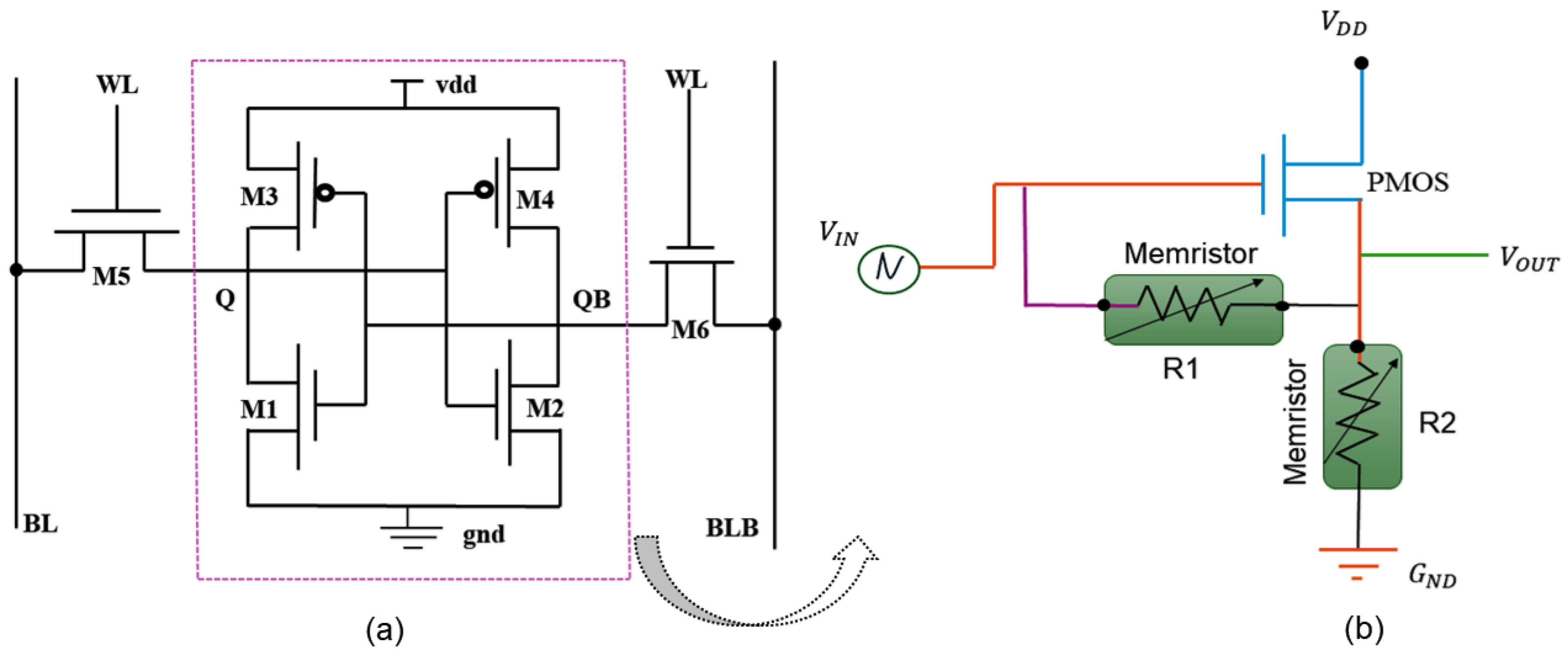

3.1.2. Proposed 1T2R Structure

3.1.3. Proposed Novel Schematic Design for the Self-Energy Generator

4. Simulation Results and Discussions

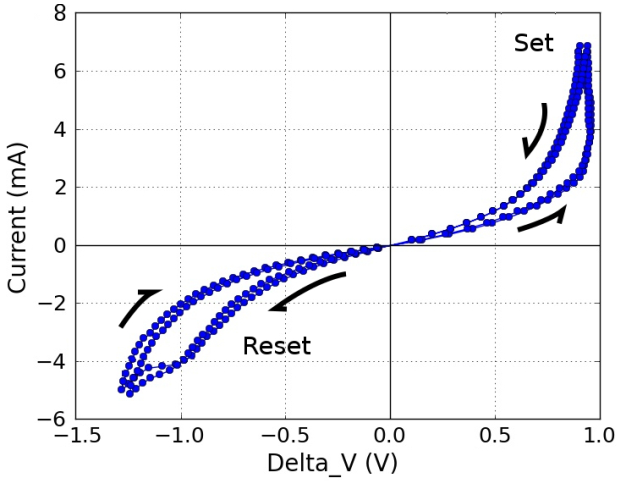

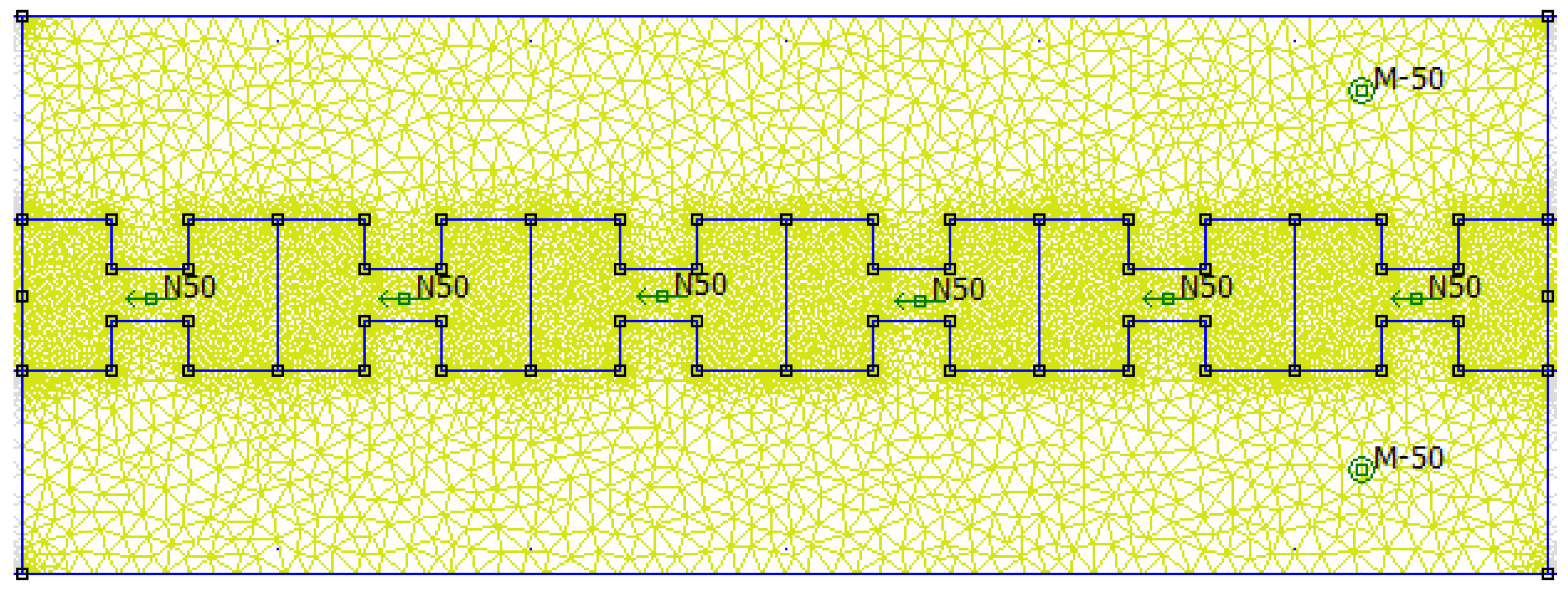

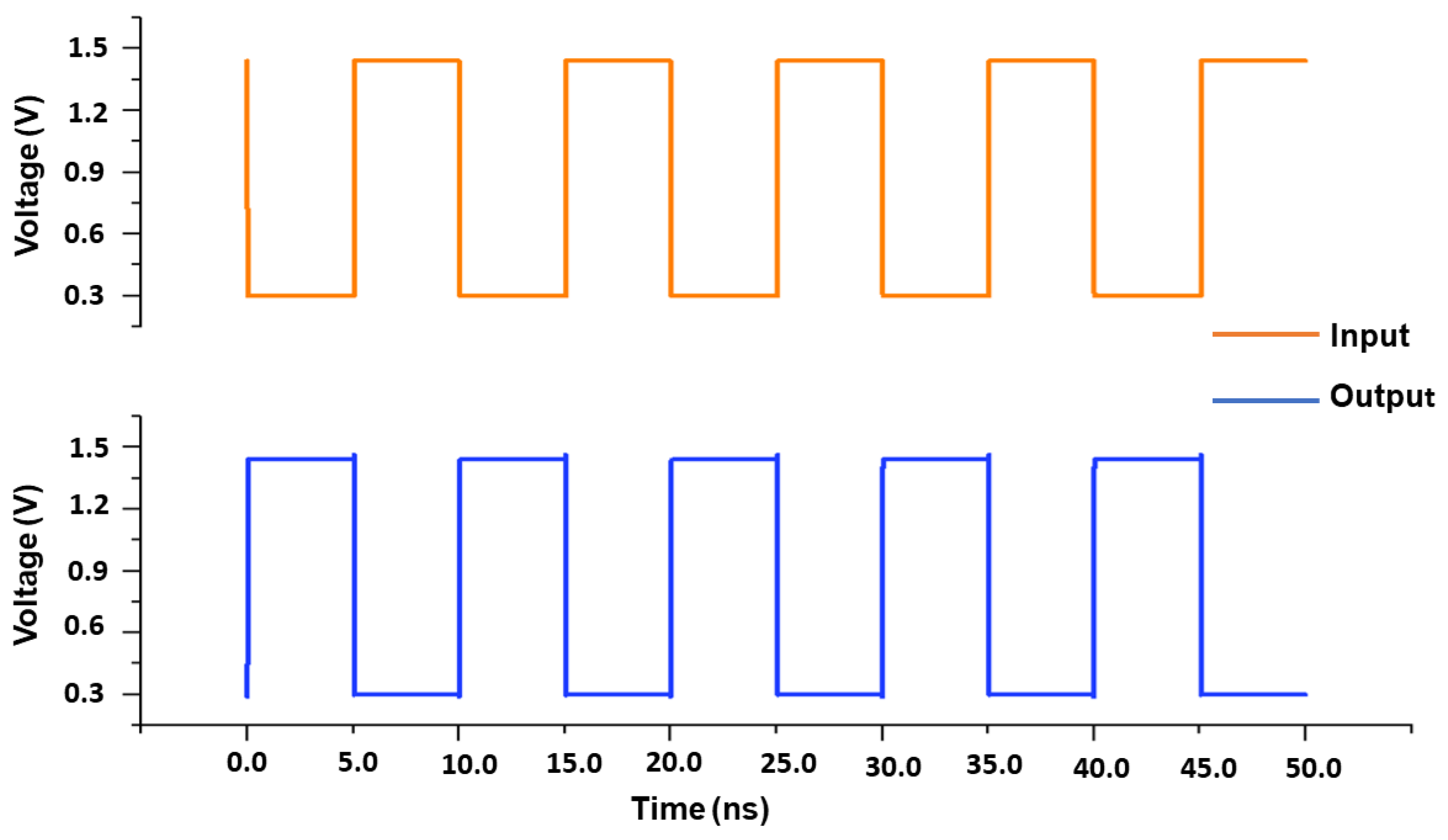

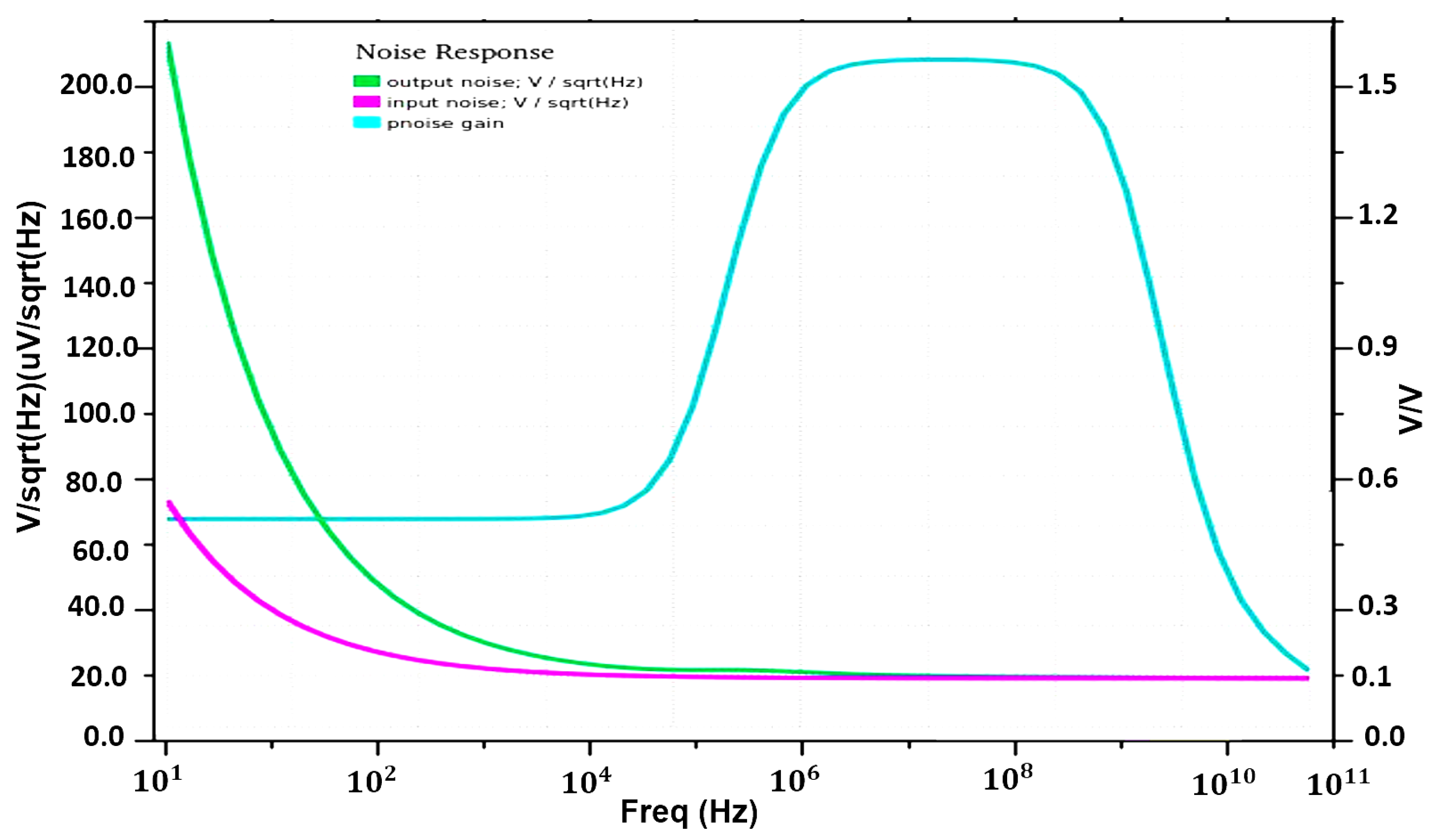

4.1. 1T2R RRAM Simulation

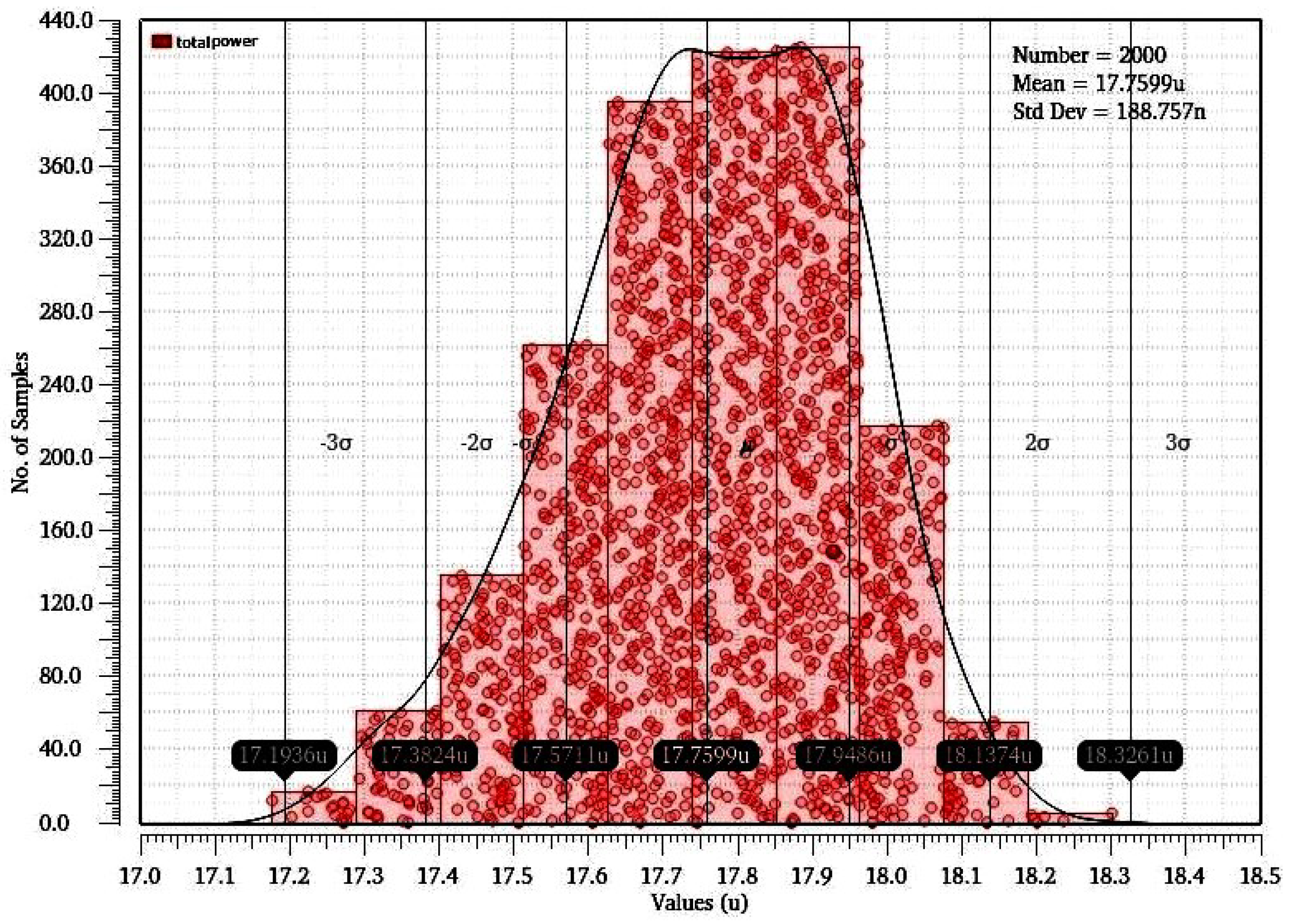

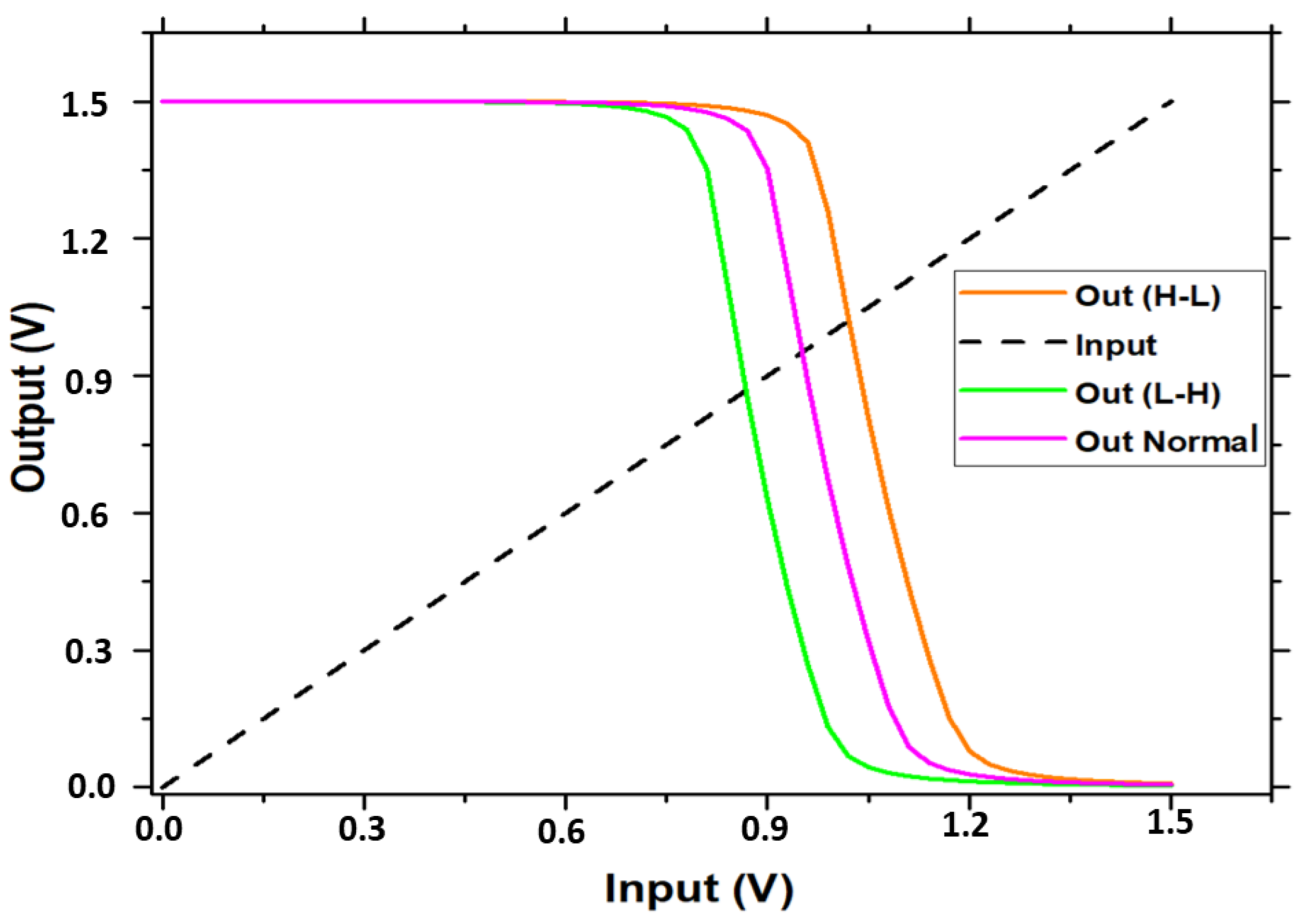

Monte Carlo and Voltage Transfer Characteristic Simulation

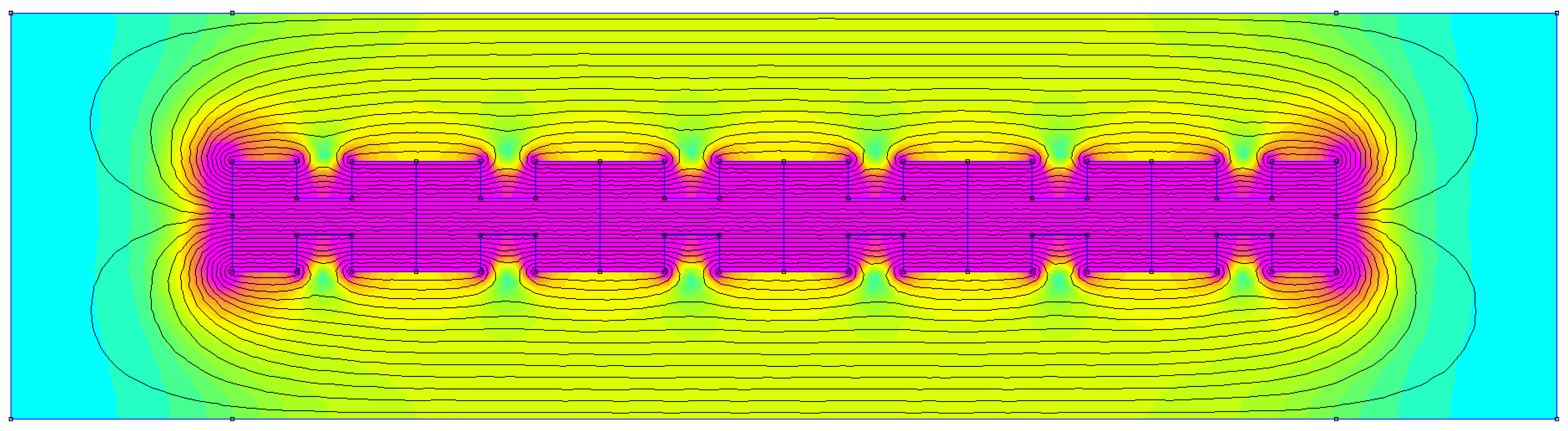

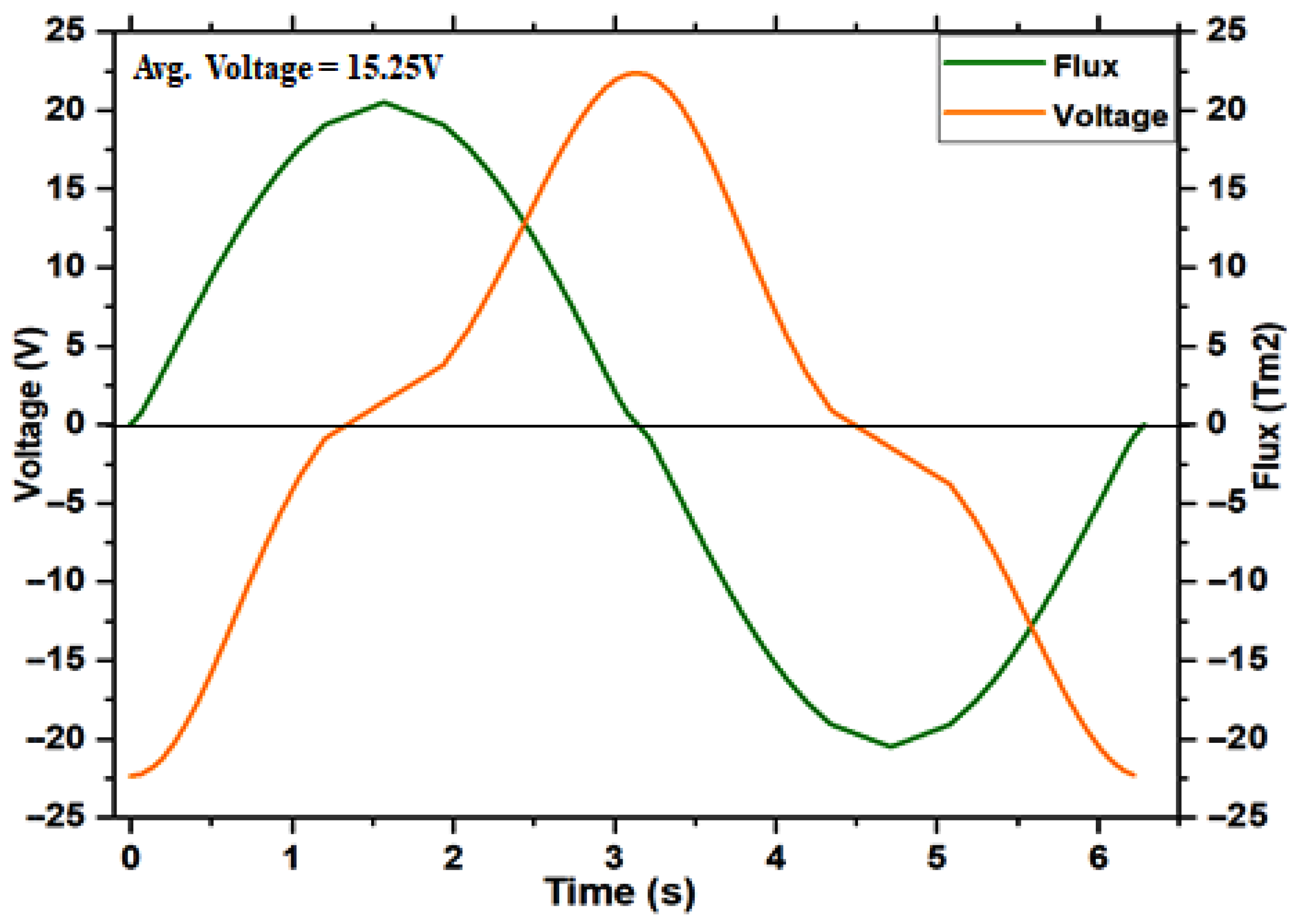

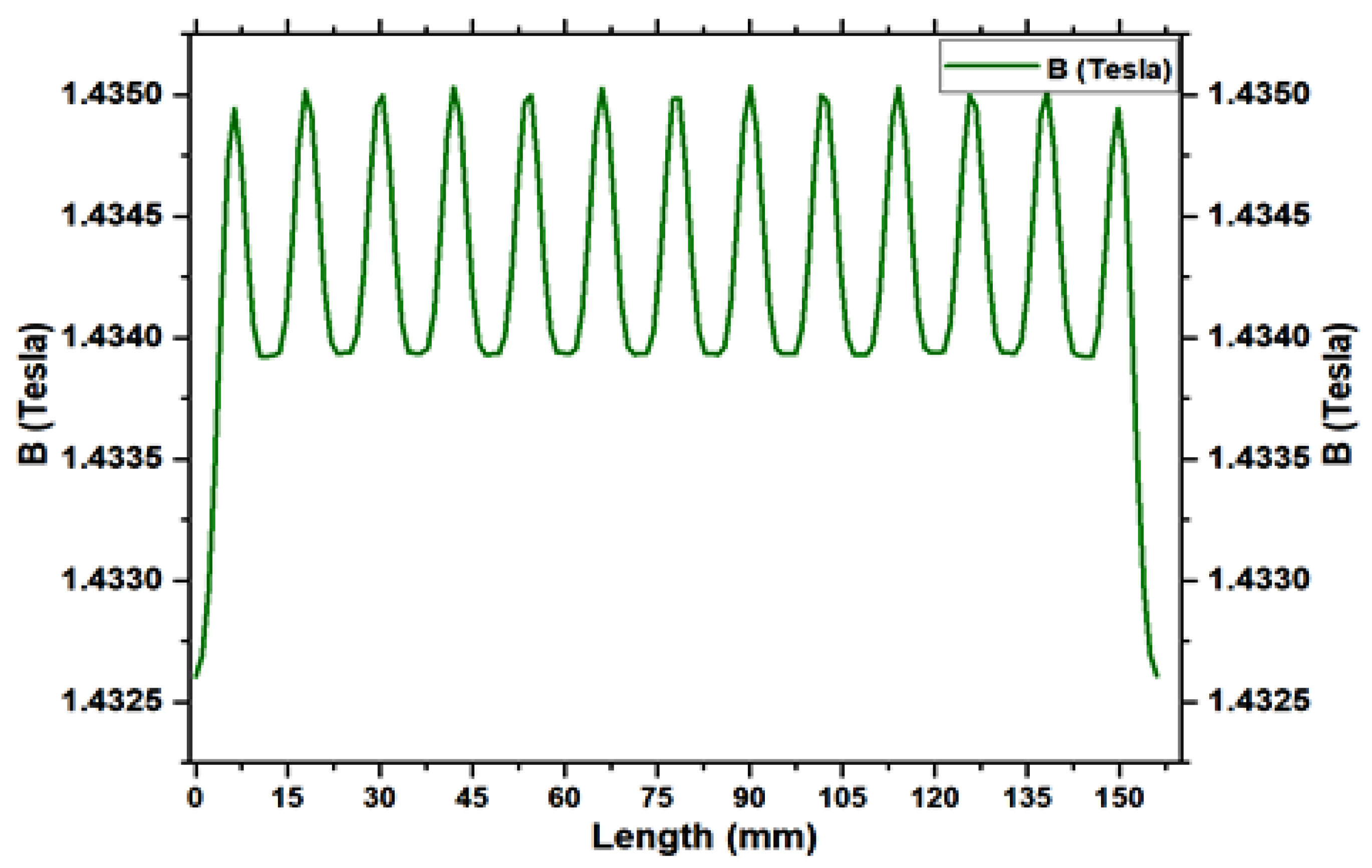

4.2. Magnet Self Generator Optimizations

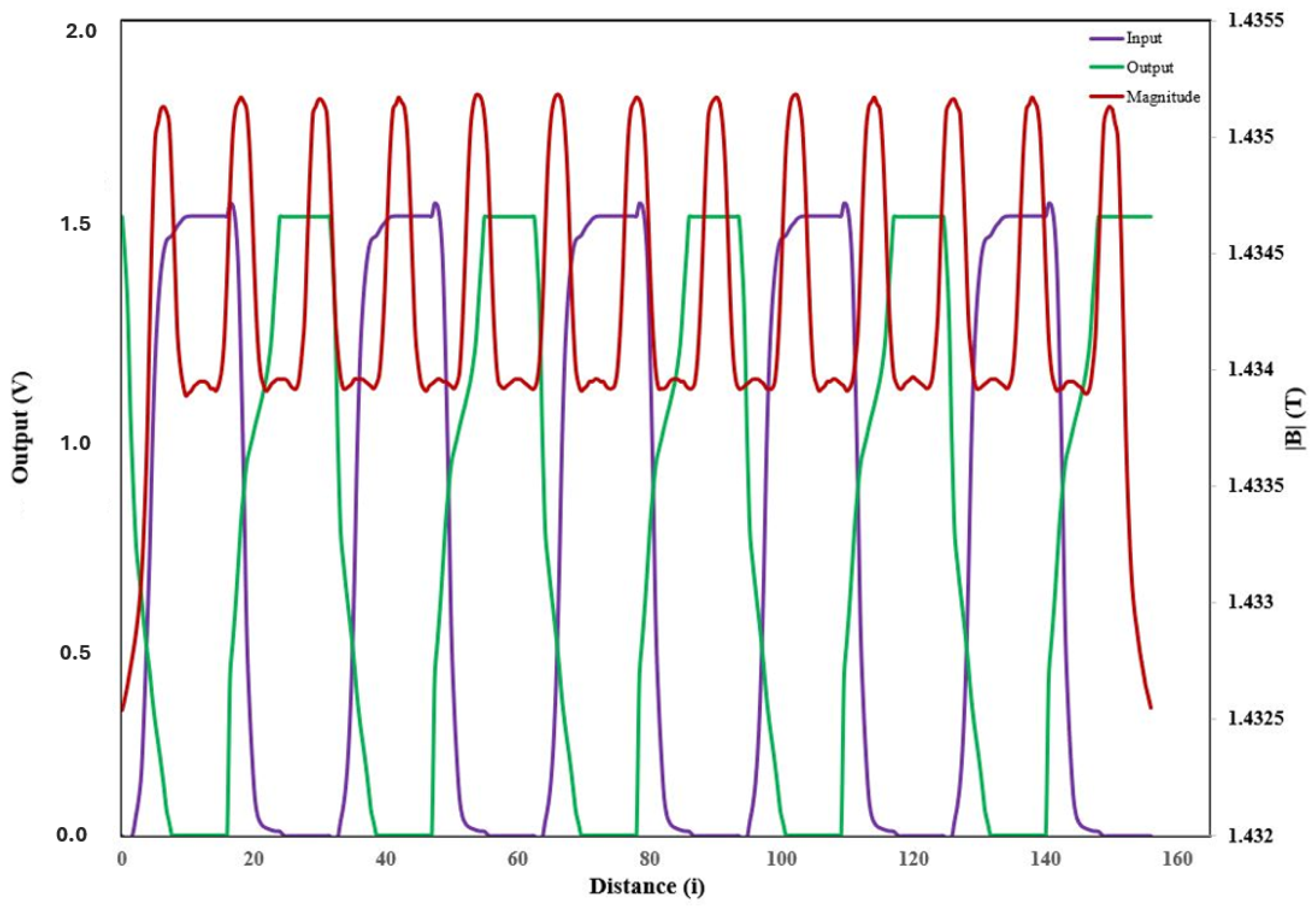

4.3. RRAM Joint Model Optimization

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Bazzi, H.; Harb, A.; Aziza, H.; Moreau, M.; Kassem, A. RRAM-based non-volatile SRAM cell architectures for ultra-low-power applications. Analog. Integr. Circuits Signal Process. 2021, 106, 351–361. [Google Scholar] [CrossRef]

- Hamdioui, S.; Aziza, H.; Sirakoulis, G.C. Memristor-based memories: Technology, design, and test. In Proceedings of the 9th IEEE International Conference on Design & Technology of Integrated Systems in Nanoscale Era (DTIS), Santorini, Greece, 6–8 May 2014; pp. 1–7. [Google Scholar]

- Akerman, J. Applied physics: Toward a universal memory. Science 2005, 308, 508–510. [Google Scholar] [CrossRef]

- Waser, R.; Aono, M. Nanoionics-based resistive switching memories. Nature 2007, 6, 833–840. [Google Scholar] [CrossRef]

- Bazzi, H.; Harb, A.; Aziza, H.; Moreau, M. Non-volatile SRAM memory cells based on ReRAM technology. SN Appl. Sci. 2020, 2, 1485. [Google Scholar] [CrossRef]

- Li, Q.; Liu, S. Adaptive Modified Function Projective Lag Synchronization of Memristor-Based Five-Order Chaotic Circuit Systems. Adv. Math. Phys. 2017, 2017, 1843179. [Google Scholar] [CrossRef]

- MacVittie, K.; Katz, E. Self-powered electrochemical memristor based on a biofuel cell-towards memristors integrated with biocomputing systems. Chem. Commun. 2014, 50, 4816–4819. [Google Scholar] [CrossRef]

- Yang, X.; Xiong, Z.; Chen, Y.; Ren, Y.; Zhou, L.; Li, H.; Zhou, Y.; Pan, F.; Han, S. A self-powered artificial retina perception system for image preprocessing based on photovoltaic devices and memristive arrays. Nano Energy 2020, 78, 105246. [Google Scholar] [CrossRef]

- Shi, J.; Wang, Z.; Tao, Y.; Xu, H.; Zhao, X.; Lin, Y.; Liu, Y. Self-Powered Memristive Systems for Storage and Neuromorphic Computing. Front. Neurosci. 2021, 15, 662457. [Google Scholar] [CrossRef]

- Sun, B.; Zhou, G.; Xu, K.; Yu, Q.; Duan, S. Self-Powered Memory Systems. ACS Mater. Lett. 2020, 2, 1669–1690. [Google Scholar] [CrossRef]

- Lee, B.; Cho, H.; Park, K.T.; Kim, J.; Park, M.; Kim, H.; Hong, Y.; Chung, S. High-performance compliant thermoelectric generators with magnetically self-assembled soft heat conductors for self-powered wearable electronics. Nat. Commun. 2020, 11, 5948. [Google Scholar] [CrossRef] [PubMed]

- Yin, J.; Li, X.; Yu, J.; Zhang, Z.; Zhou, J.; Guo, W. Generating electricity by moving a droplet of ionic liquid along graphene. Nat. Nanotechnol. 2014, 9, 378–383. [Google Scholar] [CrossRef] [PubMed]

- Yoon, J.H.; Wang, Z.; Kim, K.M.; Wu, H.; Ravichandran, V.; Xia, Q.; Hwang, C.S.; Yang, J.J. An artificial nociceptor based on a diffusive memristor. Nat. Commun. 2018, 9, 417. [Google Scholar] [CrossRef]

- Zhang, J.; Yang, C.; Liang, H.; Cao, Z.; Duan, X.; Ya, W.; Zhao, Y.; Sun, B. Memristor-based electronic devices towards biomedical applications. J. Mater. Chem. 2024, 12, 50–59. [Google Scholar] [CrossRef]

- Shearwood, C.; Yates, R.B. Development of an electromagnetic micro-generator. Electron. Lett. 1997, 33, 1883–1884. [Google Scholar] [CrossRef]

- Amirtharajah, R.; Chandrakasan, A.P. Self-powered signal processing using vibration-based power generation. IEEE J. Solid-State Circuits 1998, 33, 687–695. [Google Scholar] [CrossRef]

- Ching, N.N.; Wong, H.Y.; Li, W.J.; Leong, P.H.; Wen, Z. A laser-micromachined multi-modal resonating power transducer for wireless sensing systems. Sens. Actuators A Phys. 2002, 97–98, 685–690. [Google Scholar] [CrossRef]

- Choi, S.; Yang, J.; Wang, G. Emerging Memristive Artificial Synapses and Neurons for Energy-Efficient Neuromorphic Computing. Adv. Mater. 2020, 32, 2004659. [Google Scholar] [CrossRef] [PubMed]

- Vishwakarma, A.; Komelj, M. Design of a Smart Phone Self-Charging Device Based on Permanent Magnets. Adv. Transdiscipl. Eng. 2022, 27, 507–513. [Google Scholar]

- Vishwakarma, A.; Komelj, M. A permanent magnet-based design for a smartphone self-charger. Mater. Today Proc. 2022, 65 Pt 8, 3642–3645. [Google Scholar] [CrossRef]

- Vishwakarma, A.; Komelj, M. Optimum Design of a Permanent-Magnet-Based Self-Charging Device for a Smartphone. MatTech Mater. Technol. 2023, 57, 627–630. [Google Scholar] [CrossRef]

- Vishwakarma, A.; Ampadu, K.O.; Huebner, M.; Vishvakarma, S.; Reichenbach, M. Memristor-Based CMOS Hybrid Circuit Design and Analysis. Procedia Comput. Sci. 2023, 218, 563–573. [Google Scholar] [CrossRef]

- Abdoli, B.; Amirsoleimani, A.; Shamsi, J.; Mohammadi, K.; Ahmadi, A. A novel CMOS-memristor based inverter circuit design. In Proceedings of the 22nd Iranian Conference on Electrical Engineering (ICEE), Tehran, Iran, 20–22 May 2014; pp. 276–371. [Google Scholar]

- Sharma, G.; Bhargava, L. CMOS-memristor inverter circuit design and analysis using Cadence Virtuoso. In Proceedings of the International Conference on Recent Advances and Innovations in Engineering (ICRAIE), Jaipur, India, 23–25 December 2016; pp. 1–5. [Google Scholar] [CrossRef]

- Khalid, M. Review on Various Memristor Models, Characteristics, Potential Applications, and Future Works. Trans. Electr. Electron. Mater. 2019, 20, 289–298. [Google Scholar] [CrossRef]

- Sanca, G.A.; Di Francesco, F.; Caroli, N.; Garcia-Inza, M.; Golmar, F. Design of a Simple Readout Circuit for Resistive Switching Memristors Based on CMOS Inverters. In Proceedings of the IEEE 4th International Forum on Research and Technology for Society and Industry (RTSI), Palermo, Italy, 24–26 August 2018; pp. 1–6. [Google Scholar] [CrossRef]

- Biolek, Z.; Biolek, D.; Biolkova, V. SPICE model of memristor with nonlinear dopant drift. Radioengineering 2009, 18, 210–214. [Google Scholar]

- Strukov, D.B.; Snider, G.S.; Stewart, D.R.; Williams, R.S. The missing memristor found. Nature 2008, 453, 80–83. [Google Scholar] [CrossRef]

- Vishwakarma, A.; Fritscher, M.; Hagelauer, A.; Reichenbach, M. An RRAM-based building block for reprogrammable non-uniform sampling ADCs. it-Inf. Technol. 2023, 65, 39–51. [Google Scholar] [CrossRef]

- Zhang, X.; Cao, Y.; Peng, L.; Li, J.; Ahmad, N.; Yu, S. Mobile Charging as a Service: A Reservation-Based Approach. IEEE Trans. Autom. Sci. Eng. 2020, 17, 1976–1988. [Google Scholar] [CrossRef]

- Wu, C.; Kim, T.W.; Park, B.; Sung, S.; Shao, J.; Zhang, C.; Wang, Z.L. Self-powered tactile sensor with learning and memory. ACS Nano 2019, 14, 1390–1398. [Google Scholar] [CrossRef]

- Nekui, O.D.; Wang, W.; Liu, C.; Wang, Z.; Ding, B. IoT-Based Heartbeat Rate-Monitoring Device Powered by Harvested Kinetic Energy. Sensors 2024, 24, 4249. [Google Scholar] [CrossRef]

- Saha, C.R.; O’donnell, T.; Wang, N.; McCloskey, P. Electromagnetic generator for harvesting energy from human motion. Sens. Actuators A Phys. 2008, 147, 248–253. [Google Scholar] [CrossRef]

- Park, S.; Kim, B.; Kim, S.; Lee, K.; Kim, J. Electric generator embedded in cellular phone for self-recharge. J. Vibroengineering 2014, 16, 3797–3806. [Google Scholar]

- Liu, Y.; Yang, W.; Yan, Y.; Wu, X.; Wang, X.; Zhou, Y.; Hu, Y.; Chen, H.; Guo, T. Self-powered high-sensitivity sensory memory actuated by triboelectric sensory receptor for real-time neuromorphic computing. Nano Energy 2020, 75, 104930. [Google Scholar] [CrossRef]

- Dastgeer, G.; Nisar, S.; Rasheed, A.; Akbar, K.; Chavan, V.D.; Kim, D.; Wabaidur, S.M.; Zulfiqar, M.W.; Eom, J. Atomically engineered, high-speed non-volatile flash memory device exhibiting multibit data storage operations. Nano Energy 2024, 119, 109106. [Google Scholar] [CrossRef]

- Dastgeer, G.; Nisar, S.; Zulfiqar, M.W.; Eom, J.; Imran, M.; Akbar, K. A review on recent progress and challenges in high-efficiency perovskite solar cells. Nano Energy 2024, 132, 110401. [Google Scholar] [CrossRef]

- Jiang, Z.; Wu, Y.; Yu, S.; Yang, L.; Song, K.; Karim, Z.; Wong, H.S.P. A compact model for metal oxide resistive random access memory with experiment verification. IEEE Trans. Electron Devices 2016, 63, 1884–1892. [Google Scholar] [CrossRef]

- Reuben, J.; Fey, D.; Wenger, C. A modeling methodology for resistive RAM based on the Stanford PKU model with extended multilevel capability. IEEE Trans. Nanotechnol. 2019, 18, 647–656. [Google Scholar] [CrossRef]

- Majumdar, S.; Kingra, S.K.; Suri, M.; Tikyani, M. Hybrid CMOS-OxRAM-based 4T-2R NVSRAM with efficient programming scheme. In Proceedings of the 16th Non-Volatile Memory Technology Symposium (NVMTS), Pittsburgh, PA, USA, 17–19 October 2016; pp. 1–4. [Google Scholar] [CrossRef]

- Janniekode, U.M.; Somineni, R.P.; Khalaf, O.I.; Itani, M.M.; Chinna Babu, J.; Abdulsahib, G.M. A Symmetric Novel 8T3R Non-Volatile SRAM Cell for Embedded Applications. Symmetry 2022, 14, 768. [Google Scholar] [CrossRef]

- Yadav, M.; Handa, P. Design and Comparative Power Analysis of Conventional 6T SRAM with 7T2M nv-SRAM at 180 nm Technology. Adv. Intell. Syst. Comput. 2022, 1373, 373–383. [Google Scholar] [CrossRef]

- Pérez-Bosch Quesada, E.; Romero-Zaliz, R.; Pérez, E.; Kalishettyhalli Mahadevaiah, M.; Reuben, J.; Schubert, M.A.; Jiménez-Molinos, F.; Roldán, J.B.; Wenger, C. Toward Reliable Compact Modeling of Multilevel 1T-1R RRAM Devices for Neuromorphic Systems. Electronics 2021, 10, 645. [Google Scholar] [CrossRef]

| go = 5 × 10−10 | Vo = 0.27 V | Io = 0.0003 |

|---|---|---|

| vo = 0.8 m/s | B = 5.2 | A = 2.1 |

| gapini = 1.5 × 10−10 | To = 300 K | Y= 22 |

| gapmax = 1.5 × 10−10 | tox = 6 nm | Io = 0.003 |

| Ea = 0.6 eV | Rth = 1500 K/W | Y= Yreset = 15.3 nm |

| Supply Voltage | R1 | R2 |

|---|---|---|

| = 0 | ||

| = 1 | ||

| PMOS | W/L = 0.15 /0.13 μm | =1.5 V, = 0 V |

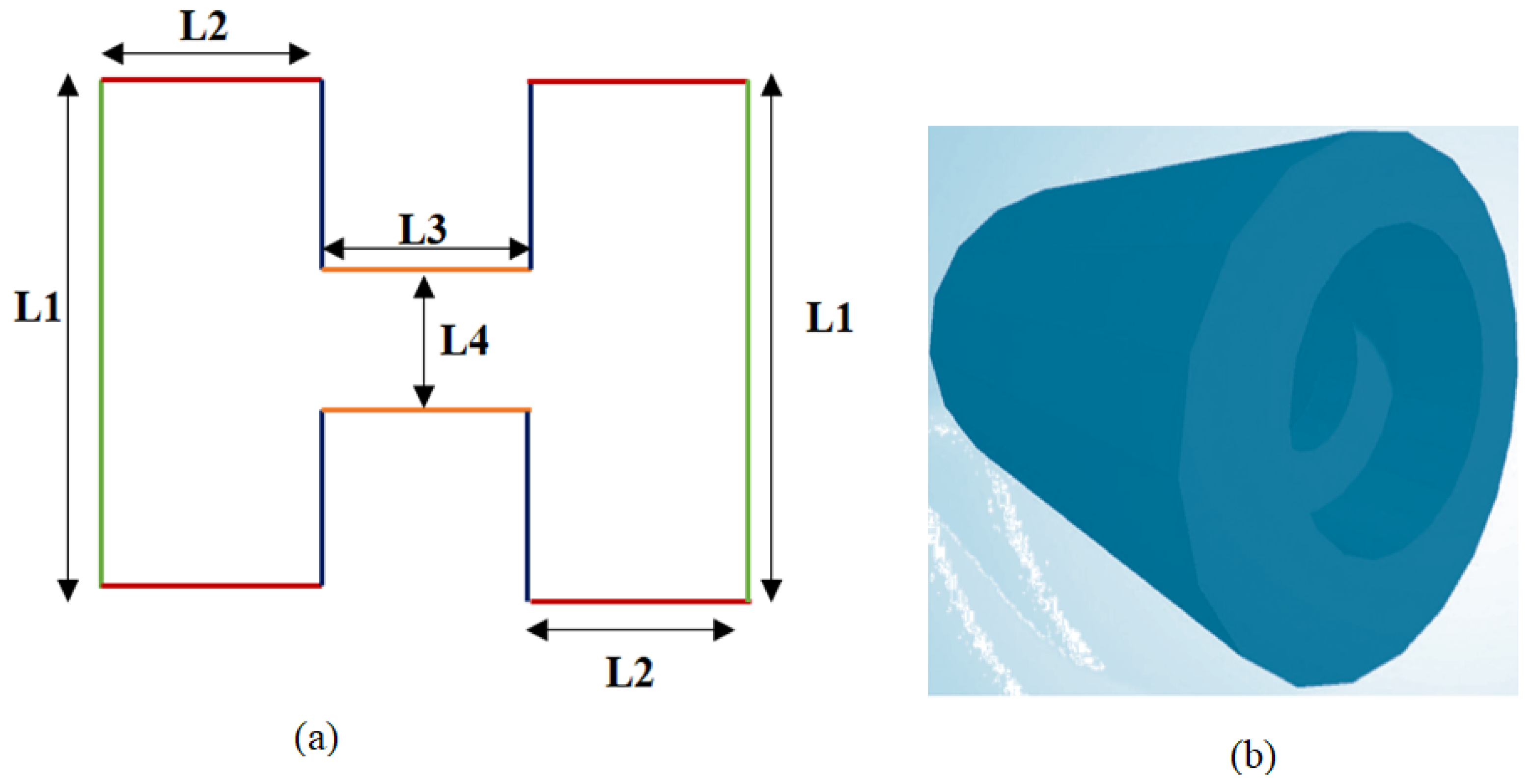

| Specifications for Geometry | Length (mm) |

|---|---|

| L1 | 8 mm |

| L2 | 4 mm |

| L3 | 4 mm |

| L4 | 2 mm |

| Process File | Propsed 1T2R Design |

|---|---|

| Power supply | 1.5 V, = 0 V |

| Reference voltage | Vref = 0–1.5 V |

| Clock signal (CLK) | High = 1.5 V; low = 0 V |

| Power Consumption (µW) | ∼17.75 |

| Rise and fall time | 5 ps |

| This Work | 2014 [23] | 2023 [22] | |

|---|---|---|---|

| Technology CMOS (nm) | 130 | 90/180 | 130 |

| Power supply | 1.5 V | 1.2/1.8 V | 1.9 V |

| Power consumption Power Consumption (µW) | 17.75 | 31/95 | 35.76 |

| W/L | 0.15 /0.13 µ | 8/8 | 8 |

| Vomax | ≈1.5 V | ≈1.2/1.8 V | ≈1.9 V |

| Process Stage | Voltage (V) |

|---|---|

| 1T2R Power supply | 1.5 V, = 0 V |

| Reference voltage | Vref = 0–1.5 V |

| Self-Charging energy generation via permanent magnet | ∼Avg. 15.25 V |

| Voltage amplitude (permanent magnet) | 17 V |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Vishwakarma, A.; Vishwakarma, A.; Komelj, M.; Vishvakarma, S.K.; Hübner, M. Design of an RRAM-Based Joint Model for Embedded Cellular Smartphone Self-Charging Device. Micromachines 2025, 16, 1101. https://doi.org/10.3390/mi16101101

Vishwakarma A, Vishwakarma A, Komelj M, Vishvakarma SK, Hübner M. Design of an RRAM-Based Joint Model for Embedded Cellular Smartphone Self-Charging Device. Micromachines. 2025; 16(10):1101. https://doi.org/10.3390/mi16101101

Chicago/Turabian StyleVishwakarma, Abhinav, Anubhav Vishwakarma, Matej Komelj, Santosh Kumar Vishvakarma, and Michael Hübner. 2025. "Design of an RRAM-Based Joint Model for Embedded Cellular Smartphone Self-Charging Device" Micromachines 16, no. 10: 1101. https://doi.org/10.3390/mi16101101

APA StyleVishwakarma, A., Vishwakarma, A., Komelj, M., Vishvakarma, S. K., & Hübner, M. (2025). Design of an RRAM-Based Joint Model for Embedded Cellular Smartphone Self-Charging Device. Micromachines, 16(10), 1101. https://doi.org/10.3390/mi16101101