Figure 1.

Resin mixing and circuit carrier printing.

Figure 1.

Resin mixing and circuit carrier printing.

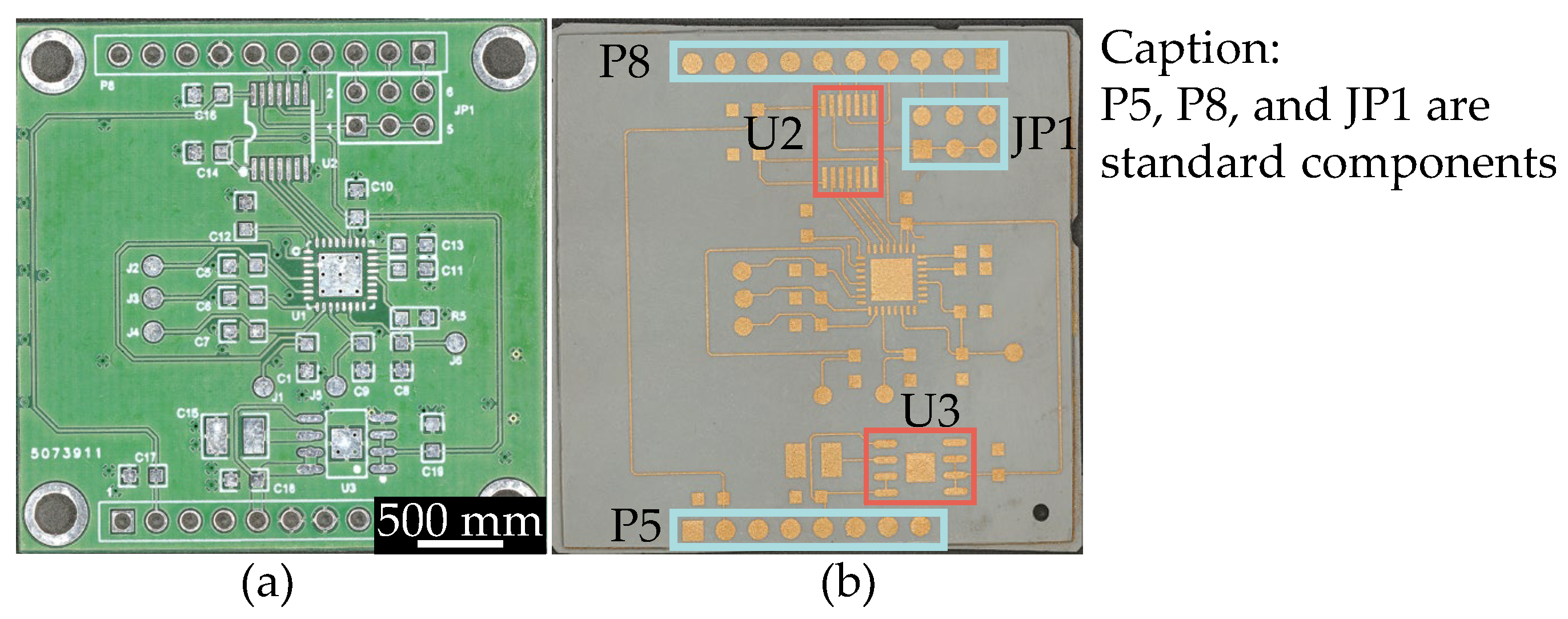

Figure 2.

The circuit board with U2 in a (a) QFN package and (b) BGA package; (c) schematic diagram of the circuit board area.

Figure 2.

The circuit board with U2 in a (a) QFN package and (b) BGA package; (c) schematic diagram of the circuit board area.

Figure 3.

Schematic representation of laser activation [

11].

Figure 3.

Schematic representation of laser activation [

11].

Figure 4.

Schematic diagram of the metallization process.

Figure 4.

Schematic diagram of the metallization process.

Figure 5.

Schematic diagram of sensor circuit carrier dimensions.

Figure 5.

Schematic diagram of sensor circuit carrier dimensions.

Figure 6.

Box plot of the impact of different post-processing methods on circuit carrier dimensions.

Figure 6.

Box plot of the impact of different post-processing methods on circuit carrier dimensions.

Figure 7.

(a) MID components with FDM-printed substrate as circuit carriers, (b) FDM-printed substrate, (c) SLA-printed substrate placed at different angles, (d) line chart of surface roughness for SLA substrates.

Figure 7.

(a) MID components with FDM-printed substrate as circuit carriers, (b) FDM-printed substrate, (c) SLA-printed substrate placed at different angles, (d) line chart of surface roughness for SLA substrates.

Figure 8.

Schematic diagram of a via hole in the circuit carrier.

Figure 8.

Schematic diagram of a via hole in the circuit carrier.

Figure 9.

Microscopic close-up of via holes in the circuit.

Figure 9.

Microscopic close-up of via holes in the circuit.

Figure 10.

Experimental substrate with via holes for TR300 and UW.

Figure 10.

Experimental substrate with via holes for TR300 and UW.

Figure 11.

Pareto chart analysis of via holes’ resistances on TR300 substrate.

Figure 11.

Pareto chart analysis of via holes’ resistances on TR300 substrate.

Figure 12.

(a) Via hole showing excessive metallization around the surrounding area; (b) via hole showing no excessive metallization around the surrounding area.

Figure 12.

(a) Via hole showing excessive metallization around the surrounding area; (b) via hole showing no excessive metallization around the surrounding area.

Figure 13.

Experimental substrate with traces for TR300 and UW.

Figure 13.

Experimental substrate with traces for TR300 and UW.

Figure 14.

3D response surface plot of resistance for different factors between TR300 and UW.

Figure 14.

3D response surface plot of resistance for different factors between TR300 and UW.

Figure 15.

(a) Optimized circuit and (b) over-metallized circuit.

Figure 15.

(a) Optimized circuit and (b) over-metallized circuit.

Figure 16.

(a) Schematic diagram of the experimental structure for a single minimum circuit spacing; (b) Schematic diagram of conductive trace distance; (c) Schematic diagram of via metallization; (d) Experimental substrate for minimum circuit spacing.

Figure 16.

(a) Schematic diagram of the experimental structure for a single minimum circuit spacing; (b) Schematic diagram of conductive trace distance; (c) Schematic diagram of via metallization; (d) Experimental substrate for minimum circuit spacing.

Figure 17.

The circuit on the (a) traditional circuit board and (b) SLA-printed circuit carrier.

Figure 17.

The circuit on the (a) traditional circuit board and (b) SLA-printed circuit carrier.

Figure 18.

The front (a) and back (b) views of the miniaturized circuit using a QFN package (UW), and the front (c) and back (d) views of the miniaturized circuit using a BGA package (TR300).

Figure 18.

The front (a) and back (b) views of the miniaturized circuit using a QFN package (UW), and the front (c) and back (d) views of the miniaturized circuit using a BGA package (TR300).

Figure 19.

AU for circuit miniaturization and chip packages in original and miniaturized circuits.

Figure 19.

AU for circuit miniaturization and chip packages in original and miniaturized circuits.

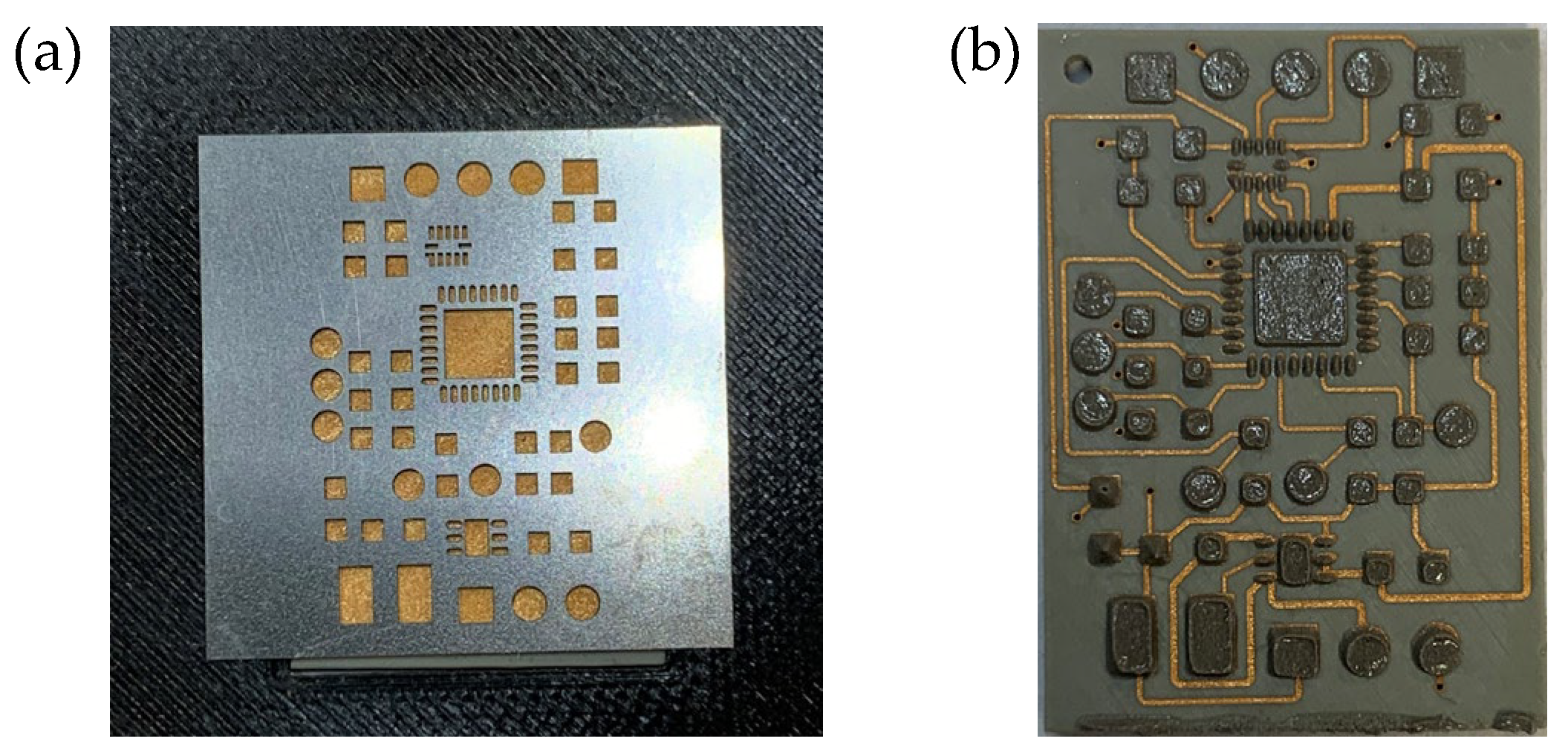

Figure 20.

(a) Solder paste stencil; (b) circuit board with applied solder paste.

Figure 20.

(a) Solder paste stencil; (b) circuit board with applied solder paste.

Figure 21.

(a) Cracks on the circuit board (Material: UW), (b) flow of solder along the circuit.

Figure 21.

(a) Cracks on the circuit board (Material: UW), (b) flow of solder along the circuit.

Figure 22.

The complete circuit board.

Figure 22.

The complete circuit board.

Figure 23.

(a) Schematic diagram of 3D pads, (b) real-life images of 3D pads for different chips.

Figure 23.

(a) Schematic diagram of 3D pads, (b) real-life images of 3D pads for different chips.

Figure 24.

Using 3D pads on circuits with (a) BGA/(b) QFN packaged chips.

Figure 24.

Using 3D pads on circuits with (a) BGA/(b) QFN packaged chips.

Figure 25.

(a) Wire connections on the SLA-MID circuit board, (b) validation circuit (standard PCB board).

Figure 25.

(a) Wire connections on the SLA-MID circuit board, (b) validation circuit (standard PCB board).

Figure 26.

(a–d) X-ray scan of the resin circuit board.

Figure 26.

(a–d) X-ray scan of the resin circuit board.

Table 1.

The mixing ratio and stirring method of the resin.

Table 1.

The mixing ratio and stirring method of the resin.

| Resin | LDS Additives | Stirring Method |

|---|

| Phrozen TR300 (TR300) | 3% | Planetary Mixer and Ultrasonic Water Bath |

| Siraya Tech Ultra White (UW) | 3% | Planetary Mixer and Ultrasonic Water Bath |

Table 2.

First-layer and normal-layer exposure times for mixed resins.

Table 2.

First-layer and normal-layer exposure times for mixed resins.

| Resin | First-Layer (s) | Normal Layer (s) |

|---|

| TR300 | 75 | 1.2 |

| UW | 55 | 2.5 |

Table 3.

The names and areas of the electronic components.

Table 3.

The names and areas of the electronic components.

| Component | Name | Area (mm2) |

|---|

| C1, C5–C14, C16–C19 | Capacitance | 3 |

| C15 | Capacitance | 11.9 |

| J1–J6 | Measurement Point | 2.7 |

| R5 | Resistance | 3 |

| JP1/JP1 Standard Component | Pin header | 2.7/26.6 |

| P5/P5 Standard Component | Pin header | 11/32.04 |

| P8/P8 Standard Component | Pin header | 16/40.4 |

| U1 | Chip | 31.3 |

| U2 BGA/U2 QFN | Chip | 2/3.42 |

| U2 TSSOP (Original circuit) | Chip | 31.4 |

| U3 | Chip | 5 |

| U3 SOIC (Original circuit) | Chip | 32.5 |

Table 4.

Summary of metallization process operating steps.

Table 4.

Summary of metallization process operating steps.

| Number in Figure 4 | Solution | Temperature (°C) | Time |

|---|

| 1 | Copper | 55 | 60 min |

| 2 | Acid | - | 30 s |

| 3 | Palladium | - | 1 min |

| 4 | Nickel | 62 | 60 min |

| 5 | Gold | 90 | 30 min |

Table 5.

Factors and levels in the RSM method (via).

Table 5.

Factors and levels in the RSM method (via).

| Factor | Level |

|---|

| Frequency | 20, 110, 200 (kHz) |

| Operating power | 20, 60, 100 (%) |

| Speed | 1000, 2500, 4000 (mm/s) |

| Repetition | 750, 825, 900 (times) |

Table 6.

ANOVA analysis of resistance values of via holes on TR300 substrate (excerpt).

Table 6.

ANOVA analysis of resistance values of via holes on TR300 substrate (excerpt).

| Factor | Sum of Squares | df | Mean Square | F-Value | p-Value | |

|---|

| Model | 99.72 | 10 | 9.97 | 794.19 | <0.0001 | significant |

| Frequency | 0.0023 | 1 | 0.0023 | 0.1820 | 0.6845 | |

| Operating power | 0.0310 | 1 | 0.0310 | 2.47 | 0.1670 | |

| Speed | 0.0023 | 1 | 0.0023 | 0.1820 | 0.6845 | |

| Repetition | 38.48 | 1 | 38.48 | 3064.79 | <0.0001 | |

| … | … | … | … | … | … | … |

| Lack of Fit | 0.0633 | 2 | 0.0317 | 10.56 | 0.0254 | significant |

Table 7.

Laser parameters for via holes on both resin types.

Table 7.

Laser parameters for via holes on both resin types.

| Frequency (kHz) | Operating Power (W) | Speed (mm/s) | Repetition (Times) |

|---|

| 20 | 3.47 (100%) | 1500 | 900 |

Table 8.

Factors and levels in the RSM method (circuit).

Table 8.

Factors and levels in the RSM method (circuit).

| Factor | Level |

|---|

| Frequency | 20, 110, 200 (kHz) |

| Operating Power | 20, 60, 100 (%) |

| Speed | 1000, 2500, 4000 (mm/s) |

| Repetition | 1, 2, 3 (times) |

Table 9.

ANOVA analysis of resistance values of circuits on TR300/UW (excerpt).

Table 9.

ANOVA analysis of resistance values of circuits on TR300/UW (excerpt).

| Factor | Sum of Squares | df | Mean Square | F-Value | p-Value | |

|---|

| Model | 627.22 | 14 | 44.8 | 3.93 | 0.0113 | significant |

| Model | 1.43 | 14 | 0.1019 | 11.08 | <0.0001 | significant |

| Frequency | 1.62 | 1 | 1.62 | 0.1423 | 0.7126 | |

| Frequency | 0.0313 | 1 | 0.0313 | 3.40 | 0.0901 | |

| Operating Power | 347.98 | 1 | 347.98 | 30.56 | 0.0001 | significant |

| Operating Power | 0.9425 | 1 | 0.9425 | 102.50 | <0.0001 | significant |

| Speed | 2.80 | 1 | 2.80 | 0.2462 | 0.6288 | |

| Speed | 0.0033 | 1 | 0.0033 | 0.3625 | 0.5583 | |

| Repetition | 8.17 | 1 | 8.17 | 0.7172 | 0.4136 | |

| Repetition | 0.1008 | 1 | 0.1008 | 10.97 | 0.0062 | |

| … | … | … | … | … | … | … |

| Lack of Fit | 124.77 | 8 | 15.6 | 5.25 | 0.0633 | not significant |

| Lack of Fit | 0.0903 | 8 | 0.0113 | 2.26 | 0.2248 | not significant |

Table 10.

Laser parameters for TR300 and UW.

Table 10.

Laser parameters for TR300 and UW.

| Frequency (kHz) | Operating Power (W) | Speed (mm/s) | Repetition (times) |

|---|

| 110 | 9.67 (60%) | 2500 | 1 |

| 110 | 9.67 (60%) | 2500 | 1 |

Table 11.

Model and package type of U2 and U3 in the original circuit.

Table 11.

Model and package type of U2 and U3 in the original circuit.

| Chip | Model | Package Type |

|---|

| U2 | TXB0104PWR | TSSOP |

| U3 | ADP7156ARDZ3.0R7 | SOIC |

Table 12.

Soldering methods and principles.

Table 12.

Soldering methods and principles.

| Machine | Principle | Material |

|---|

IBL LC 280,

IBL-Löttechnik GmbH, Königsee, Germany | Condensation Soldering | TR300 |

ERSA Hotflow 2/14,

ERSA GmbH, Wertheim, Germany | Convection Soldering | TR300 and UW |