A Novel DTSCR Structure with High Holding Voltage and Enhanced Current Discharge Capability for 28 nm CMOS Technology ESD Protection

Abstract

:1. Introduction

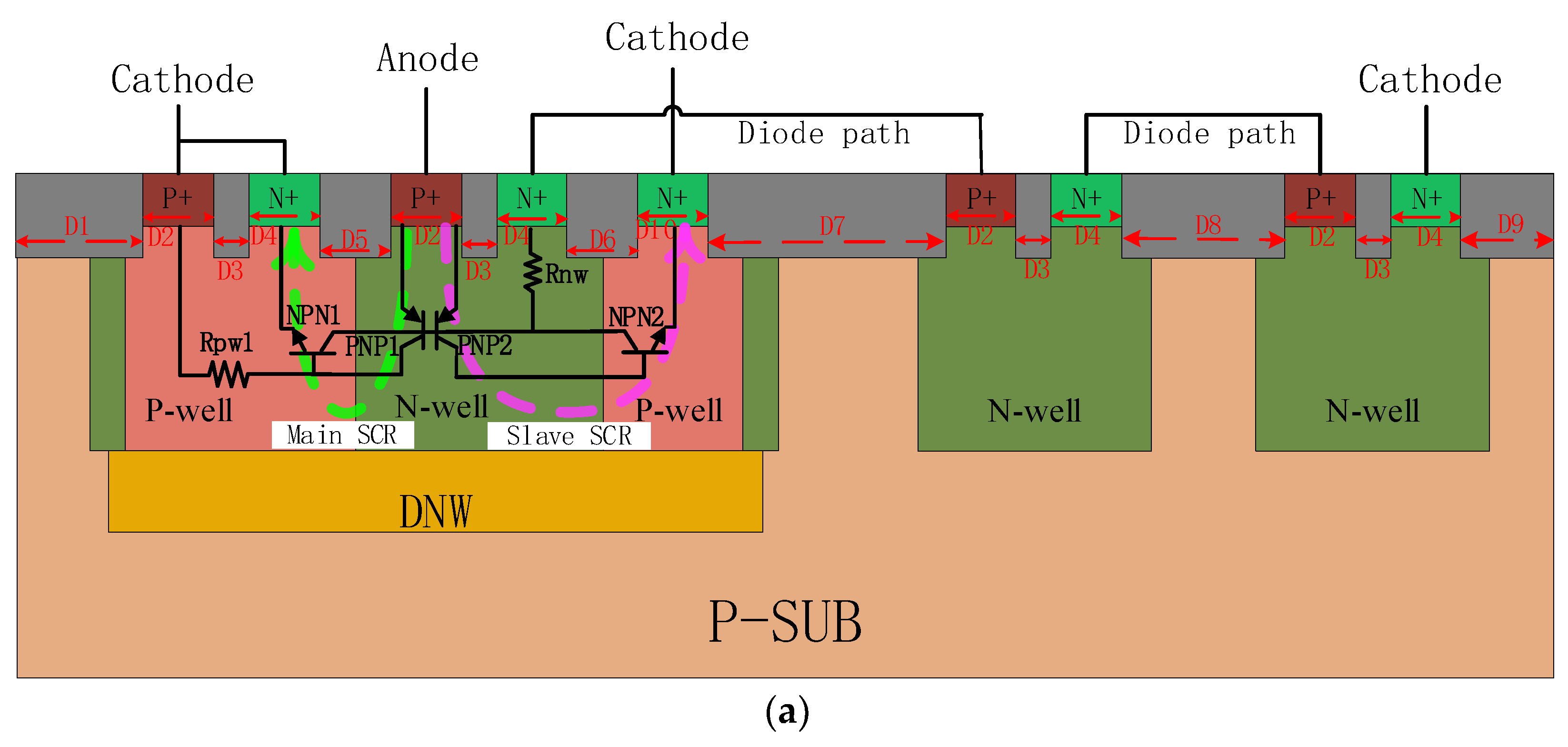

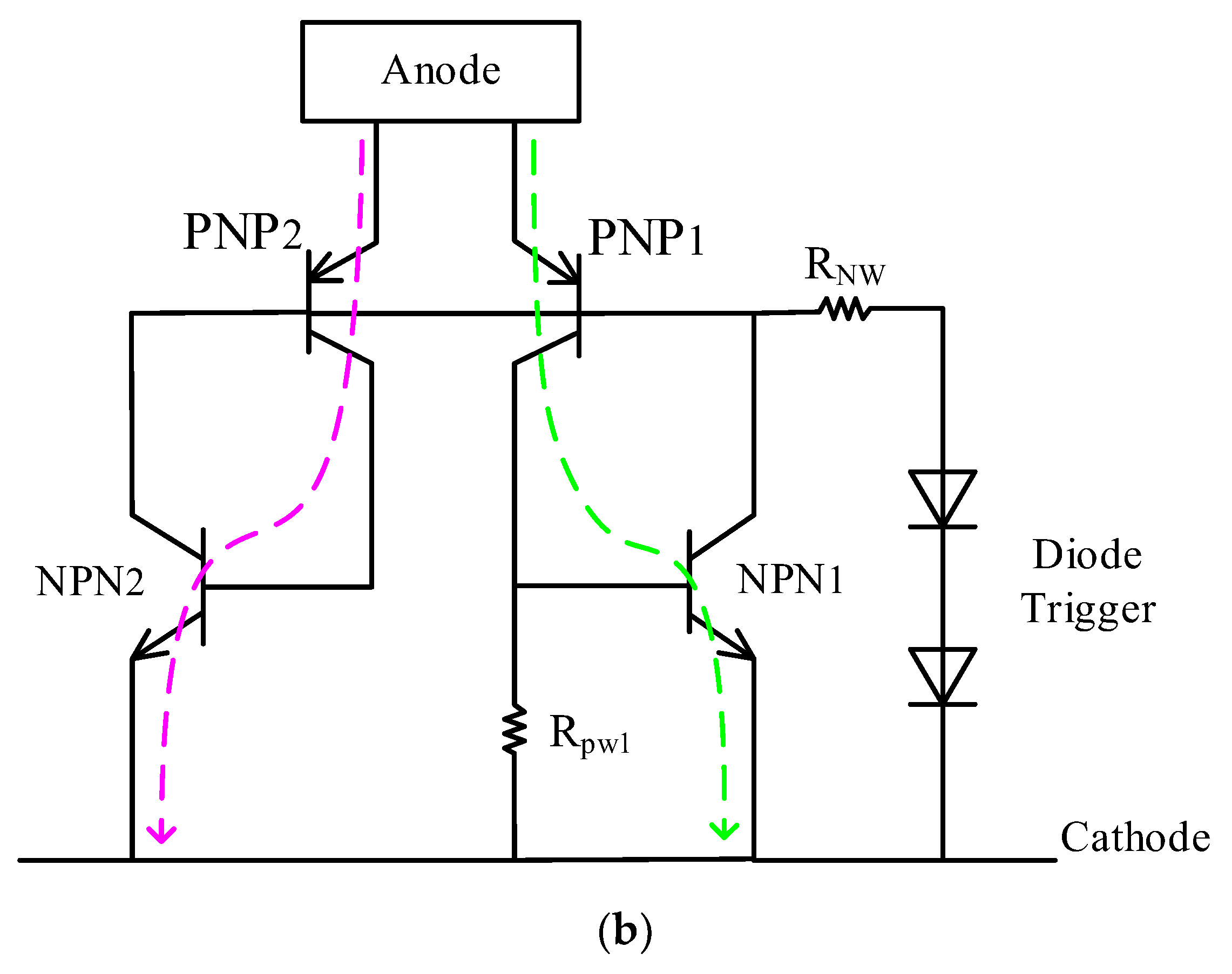

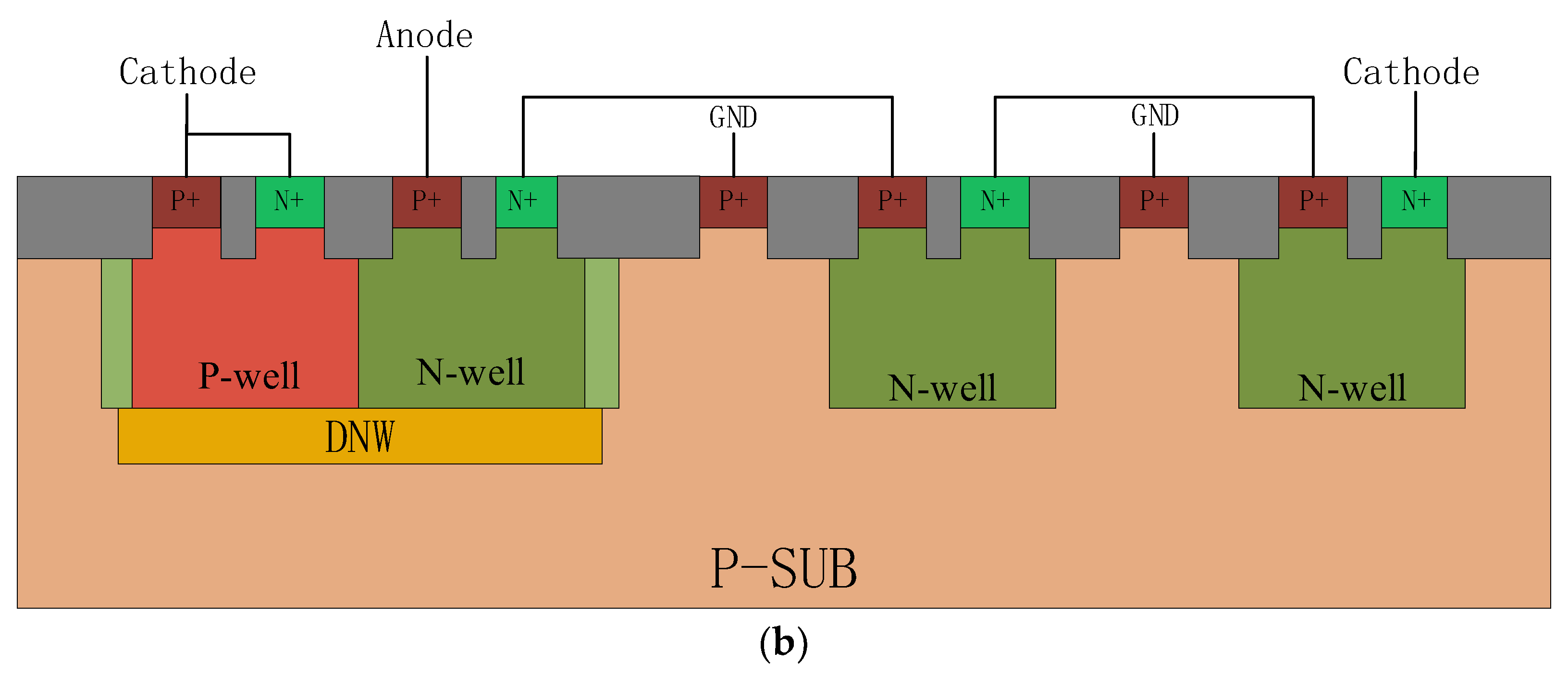

2. Device Structure Description

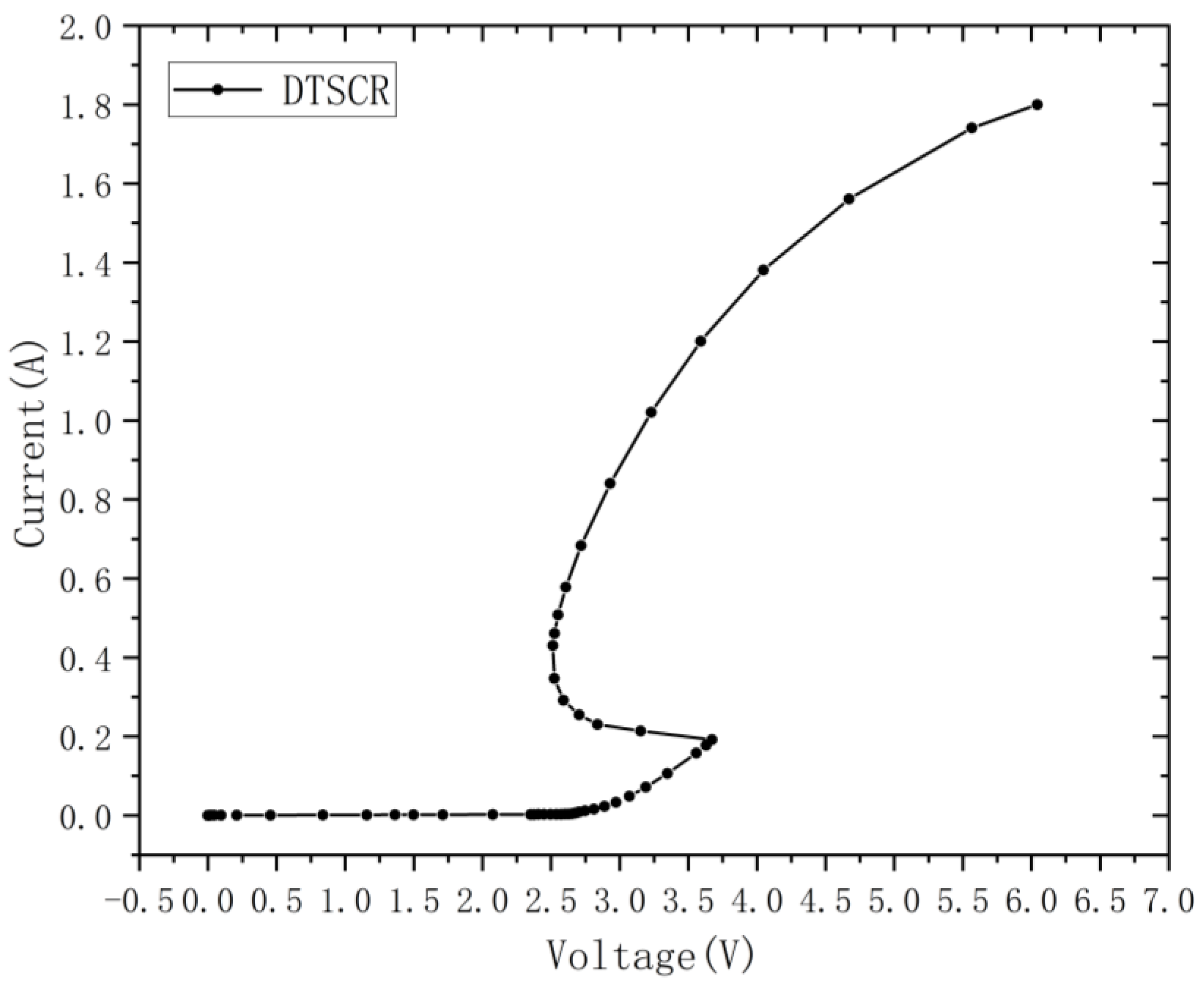

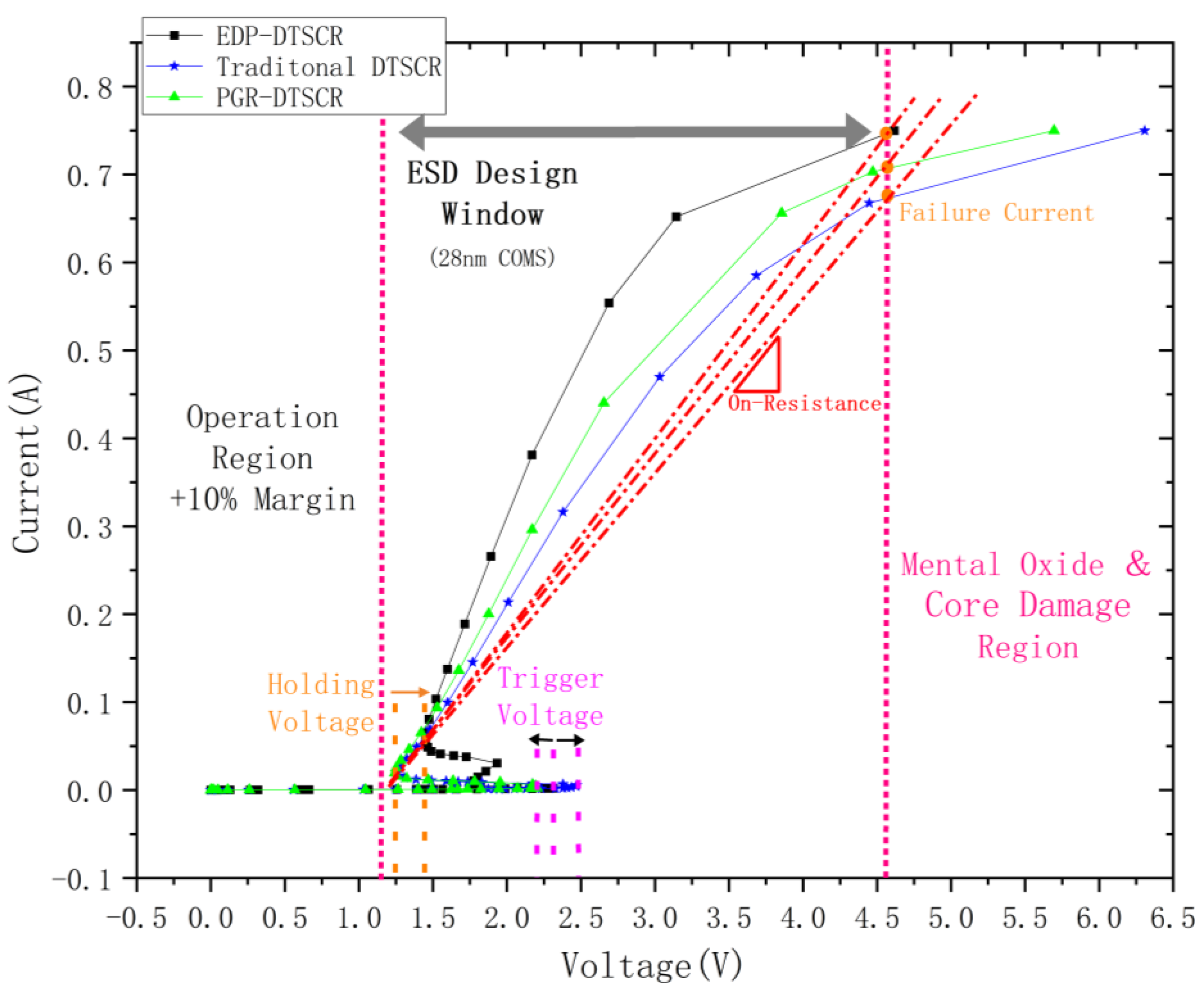

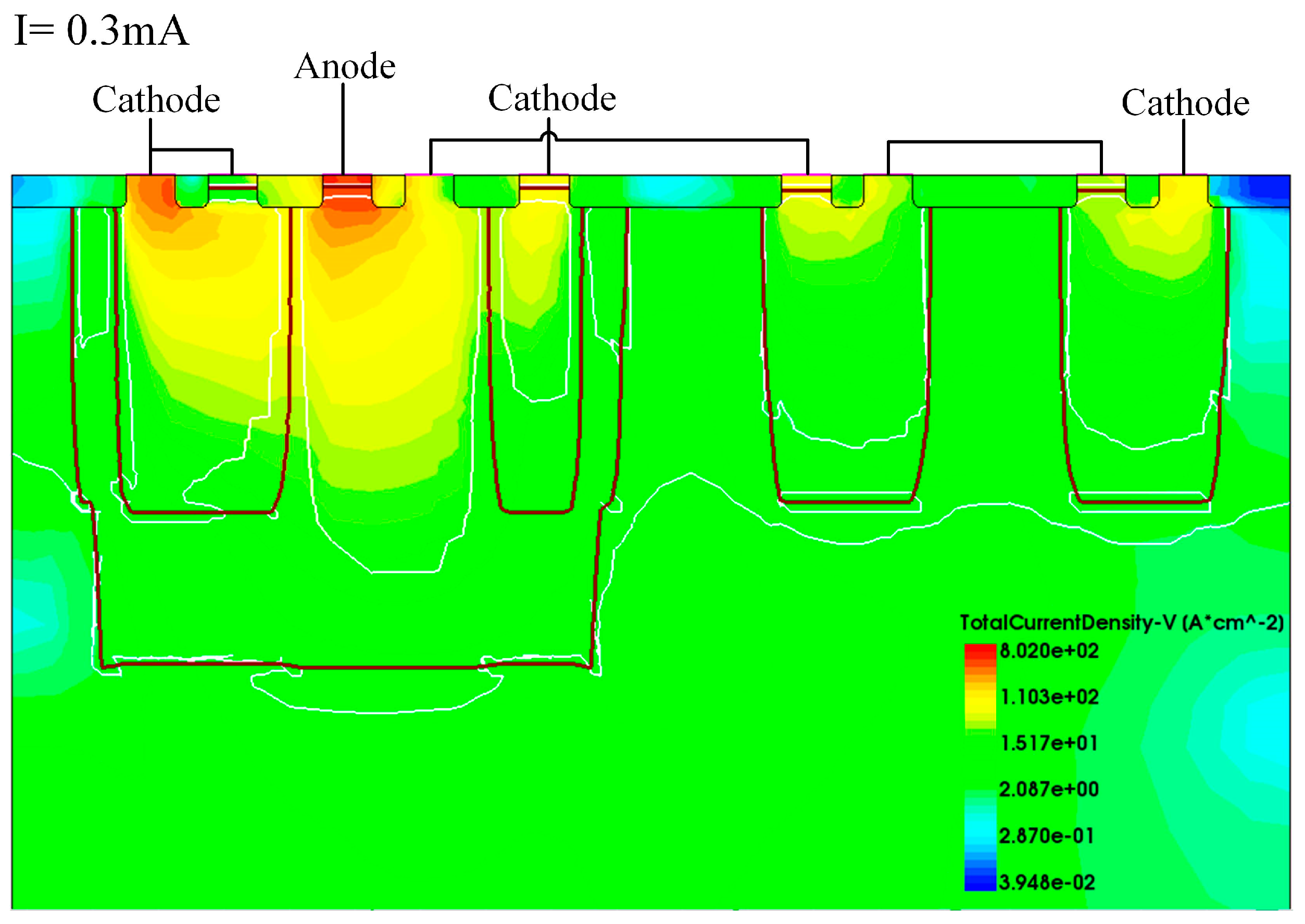

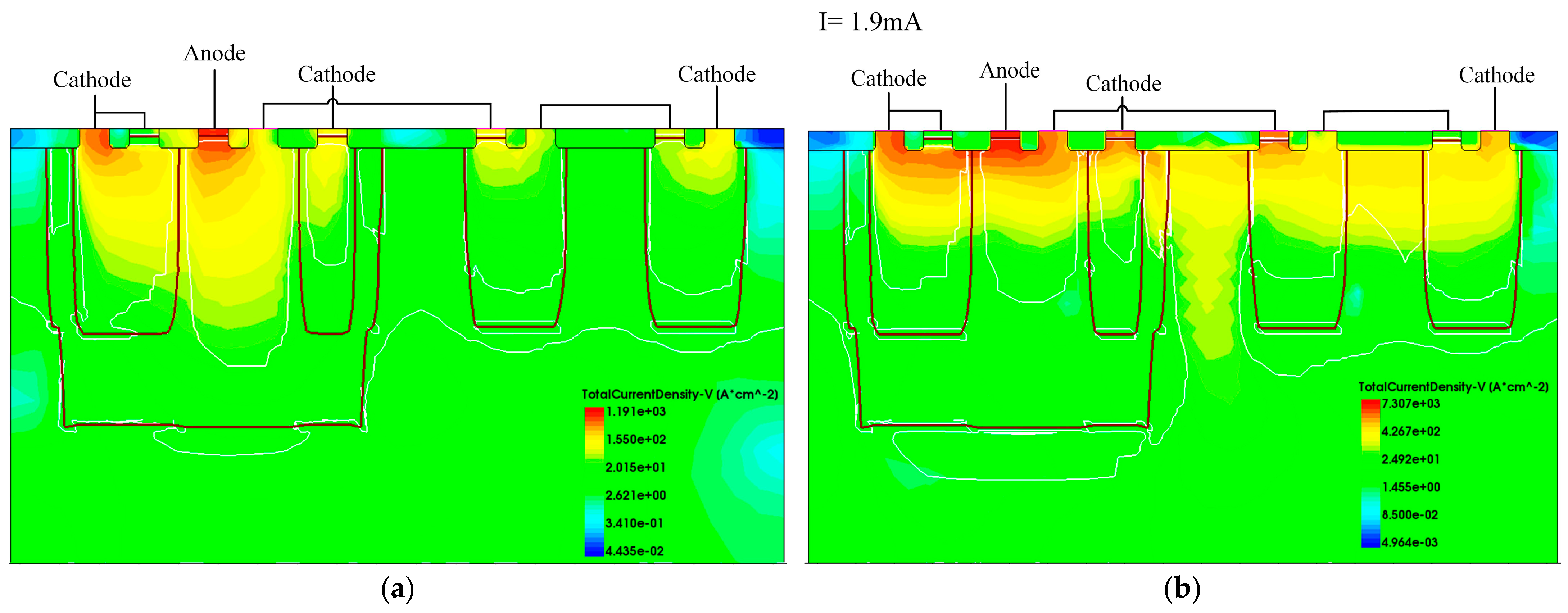

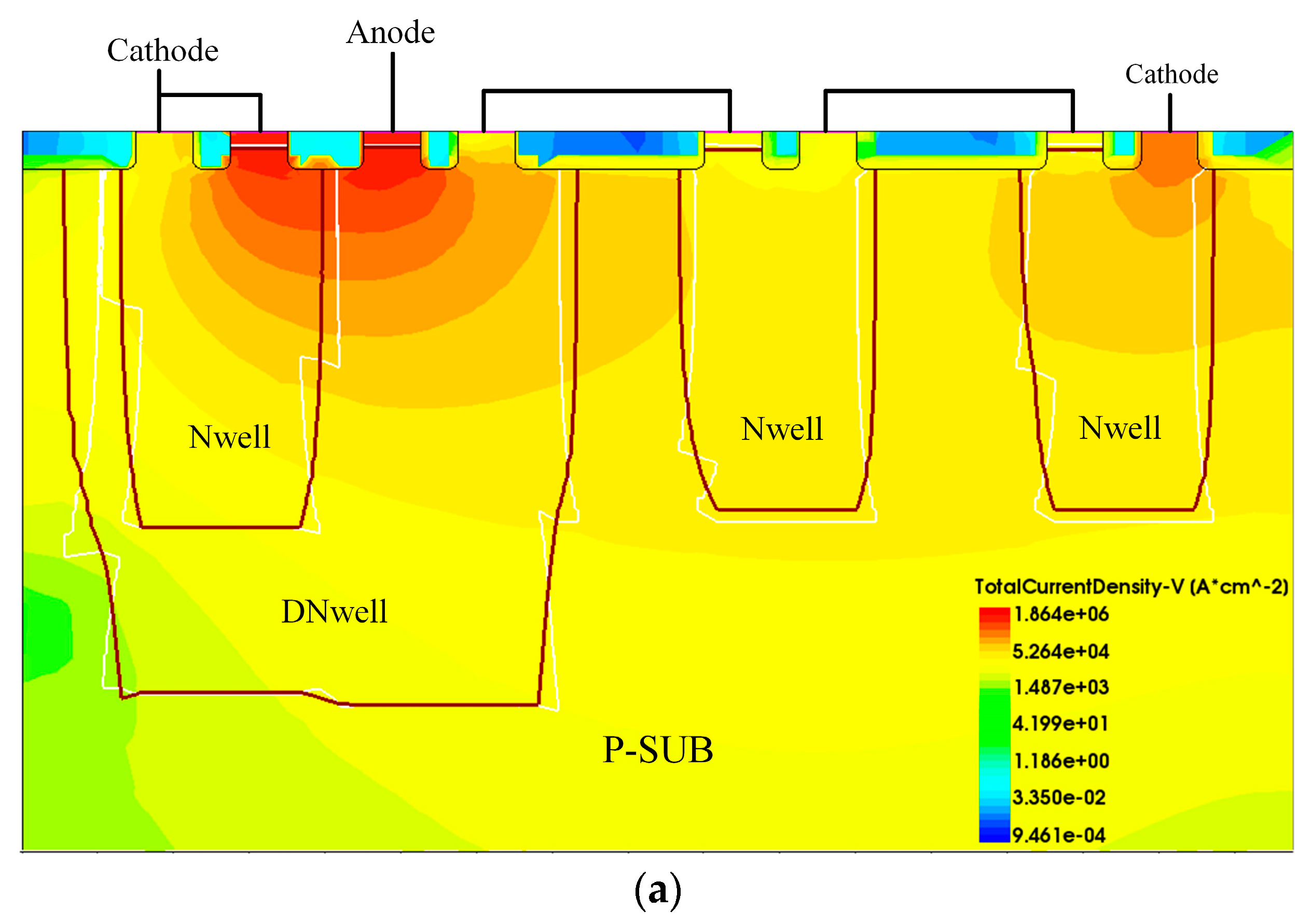

3. Results and Discussion

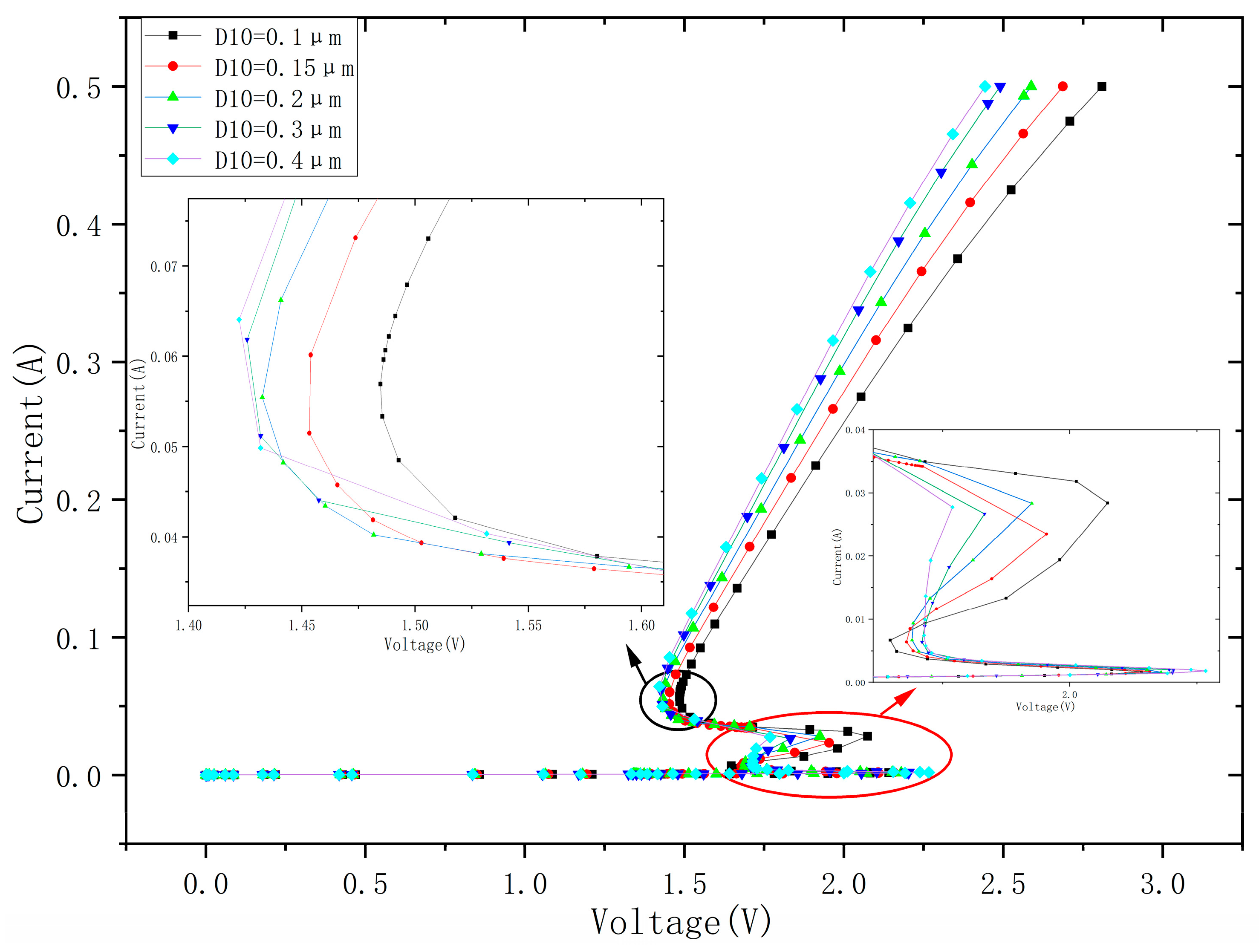

4. Optimization of Lateral Key Characteristics

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Lu, F.; Ma, R.; Dong, Z.; Wang, L.; Zhang, C.; Wang, C.; Chen, Q.; Wang, X.S.; Zhang, F.; Li, C.; et al. A Systematic Study of ESD Protection Co-Design with High-Speed and High-Frequency ICs in 28 nm CMOS. IEEE Trans. Circuits Syst. I 2016, 63, 1746–1757. [Google Scholar] [CrossRef]

- Ker, M.-D.; Hsu, K.-C. Overview of On-Chip Electrostatic Discharge Protection Design with SCR-Based Devices in CMOS Integrated Circuits. IEEE Trans. Device Mater. Relib. 2005, 5, 235–249. [Google Scholar] [CrossRef]

- Ker, M.-D. Lateral SCR Devices with Low-Voltage High-Current Triggering Characteristics for Output ESD Protection in Submicron CMOS Technology. IEEE Trans. Electron Devices 1998, 45, 849–860. [Google Scholar] [CrossRef]

- Du, F.; Hou, F.; Song, W.; Chen, R.; Liu, J.; Liu, Z.; Liou, J.J. An Enhanced MLSCR Structure Suitable for ESD Protection in Advanced Epitaxial CMOS Technology. IEEE Trans. Electron Devices 2019, 66, 2062–2067. [Google Scholar] [CrossRef]

- Huang, M.; Du, F.; Hou, F.; Song, W.; Liu, J.; Liu, Z. Enhanced LVTSCR with High Holding Voltage in Advanced CMOS Technology. In Proceedings of the 2019 IEEE International Conference on Electron Devices and Solid-State Circuits (EDSSC), Xi’an, China, 12–14 June 2019; pp. 1–2. [Google Scholar]

- Yang, K.; Liu, J.; Liu, Z. LVTSCR with High Holding Voltage for ESD Protection in 55nm CMOS Process. In Proceedings of the 2019 8th International Symposium on Next Generation Electronics (ISNE), Zhengzhou, China, 9–10 October 2019; pp. 1–3. [Google Scholar]

- Song, W.; Du, F.; Hou, F.; Liu, J.; Huang, X.; Liu, Z.; Liou, J.J. Design of a Novel Low Voltage Triggered Silicon Controlled Rectifier (SCR) for ESD Applications. In Proceedings of the 2020 International EOS/ESD Symposium on Design and System (IEDS), Chengdu, China, 23 June 2021; pp. 1–4. [Google Scholar]

- Xu, Z.-k.; Shen, H.-y.; Hu, T.; Guo, W.; Dong, S.-r. Vertical Silicon-Controlled Rectifier for ESD Protection under 28nm Ps Process. In Proceedings of the 2019 IEEE 26th International Symposium on Physical and Failure Analysis of Integrated Circuits (IPFA), Hangzhou, China, 2–5 July 2019; pp. 1–3. [Google Scholar]

- Ker, M.-D.; Hsu, K.-C. Substrate-Triggered SCR Device for on-Chip ESD Protection in Fully Silicided Sub-0.25-Μm CMOS Process. IEEE Trans. Electron Devices 2003, 50, 397–405. [Google Scholar] [CrossRef]

- Ker, M.-D.; Hsu, K.-C. Latchup-Free Esd Protection Design with Complementary Substrate-Triggered Scr Devices. IEEE J. Solid-State Circuits 2003, 38, 1380–1392. [Google Scholar] [CrossRef]

- Russ, C.C.; Mergens, M.P.J.; Verhaege, K.G.; Armer, J.; Jozwiak, P.C.; Kolluri, G.; Avery, L.R. GGSCRs: GGNMOS Triggered Silicon Controlled Rectifiers for ESD Protection in Deep Sub-Micron CMOS Processes. In Proceedings of the 2001 Electrical Overstress/Electrostatic Discharge Symposium, Portland, OR, USA, 11–13 September 2001. [Google Scholar]

- Ker, M.-D.; Hsu, K.-C. SCR Device with Double-Triggered Technique for on-Chip ESD Protection in Sub-Quarter-Micron Silicided CMOS Processes. IEEE Trans. Device Mater. Relib. 2003, 3, 58–68. [Google Scholar] [CrossRef]

- Rui, T.; JiZhi, L.; Liu, Z.; Hui, C.; Zhiwei, L. Self-Triggered Stacked Silicon-Controlled Rectifier Structure (STSSCR) for on-Chip Electrostatic Discharge (ESD) Protection. In Proceedings of the 2016 IEEE International Nanoelectronics Conference (INEC), Chengdu, China, 9–11 May 2016; pp. 1–2. [Google Scholar]

- Lin, C.-Y.; Ker, M.-D.; Chang, P.-H.; Wang, W.-T. Study on the ESD-Induced Gate-Oxide Breakdown and the Protection Solution in 28nm High-k Metal-Gate CMOS Technology. In Proceedings of the 2015 IEEE Nanotechnology Materials and Devices Conference (NMDC), Anchorage, AK, USA, 13–16 September 2015; pp. 1–4. [Google Scholar]

- Miao, M.; Li, Y.; Gauthier, R. Modeling and Simulation of Diode Triggered Silicon Controlled Rectifier Behavior under ESD Stresses. In Proceedings of the 2019 IEEE 26th International Symposium on Physical and Failure Analysis of Integrated Circuits (IPFA), Hangzhou, China, 2–5 July 2019; pp. 1–4. [Google Scholar]

- Liu, J.; Liao, C.; Liu, Z.; Hou, F. A Diode-Triggered Silicon-Controlled Rectifier with Small Diode Width for Electrostatic Discharge Applications. In Proceedings of the 2017 International Conference on Electron Devices and Solid-State Circuits (EDSSC), Hsinchu, Taiwan, 18–20 October 2017; pp. 1–2. [Google Scholar]

- Wang, C.; Zhang, F.; Lu, F.; Chen, Q.; Li, C.; Zhao, M.; Gu, H.; Feng, G.; Wu, H.; Tang, T.; et al. A Comparison Study of DTSCR by TCAD and VFTLP for CDM ESD Protection. In Proceedings of the 2017 IEEE 24th International Symposium on the Physical and Failure Analysis of Integrated Circuits (IPFA), Chengdu, China, 4–7 July 2017; pp. 1–4. [Google Scholar]

- Guo, J.; Liu, J.; Tian, R.; Zhao, L.; Liu, Z. Novel Diode-Triggered Silicon-Controlled Rectifier (DTSCR) for High-Temperature Low-Voltage Electrostatic Discharge (ESD) Applications. In Proceedings of the 2016 IEEE International Nanoelectronics Conference (INEC), Chengdu, China, 9–11 May 2016; pp. 1–2. [Google Scholar]

- Glaser, U.; Esmark, K.; Streibl, M.; Russ, C.; Domański, K.; Ciappa, M.; Fichtner, W. SCR Operation Mode of Diode Strings for ESD Protection. Microelectron. Reliab. 2007, 47, 1044–1053. [Google Scholar] [CrossRef]

- Li, X.; Dong, S.; Jin, H.; Miao, M.; Hu, T.; Guo, W.; Wong, H. 28 nm CMOS Process ESD Protection Based on Diode-Triggered Silicon Controlled Rectifier. Solid-State Electron. 2017, 137, 128–133. [Google Scholar] [CrossRef]

- Du, F.; Song, W.; Hou, F.; Liu, J.; Liu, Z.; Liou, J.J.; Xiong, X.; Li, Q.; Liu, Y. Augmented DTSCR With Fast Turn-On Speed for Nanoscale ESD Protection Applications. IEEE Trans. Electron Devices 2020, 67, 1353–1356. [Google Scholar] [CrossRef]

- Liang, H.; Ma, Q.; Sun, J.; Liu, J.; Gu, X. A Novel DTSCR with Embedded MOS and Island Diodes for ESD Protection of High-Speed ICs. IEEE Trans. Device Mater. Relib. 2022, 22, 306–311. [Google Scholar] [CrossRef]

- Do, K.-I.; Koo, Y.-S. A New SCR Structure with High Holding Voltage and Low ON-Resistance for 5-V Applications. IEEE Trans. Electron Devices 2020, 67, 1052–1058. [Google Scholar] [CrossRef]

- Du, F.; Liu, Z.; Liou, J.J. Effect of P-Type Guard Ring on the Turn-on Characteristics of Diode-Triggered SCR. In Proceedings of the 2019 8th International Symposium on Next Generation Electronics (ISNE), Zhengzhou, China, 9–10 October 2019; pp. 1–3. [Google Scholar]

- Zhang, L.; Wang, Y.; Wang, Y.; He, Y. Insight into Multiple-Triggering Effect in DTSCRs for ESD Protection. J. Semicond. 2017, 38, 075001. [Google Scholar] [CrossRef]

- Zhang, L.; Wang, Y.; He, Y. A Novel Technique to Suppress Multiple-Triggering Effect in Typical DTSCRs under ESD Stress. IEICE Trans. Electron. 2020, E103.C, 274–278. [Google Scholar] [CrossRef]

- Chen, L.; Du, F.; Chen, R.; Liu, J.; Liu, Z.; Zhang, L. Novel Diode-Triggered SCR with Suppressed Multiple Triggering for ESD Applications. In Proceedings of the 2018 IEEE International Conference on Electron Devices and Solid State Circuits (EDSSC), Shenzhen, China, 6–8 June 2018; pp. 1–2. [Google Scholar]

- Miao, M.; Dong, S.; Wu, J.; Zeng, J.; Liou, J.J.; Ma, F.; Li, H.; Han, Y. Minimizing Multiple Triggering Effect in Diode-Triggered Silicon-Controlled Rectifiers for ESD Protection Applications. IEEE Electron Device Lett. 2012, 33, 893–895. [Google Scholar] [CrossRef]

| D | Length/μm |

|---|---|

| D1 | 0.8 |

| D2 | 0.3 |

| D3 | 0.2 |

| D4 | 0.3 |

| D5 | 0.4 |

| D6 | 0.4 |

| D7 | 1.3 |

| D8 | 1 |

| D9 | 0.5 |

| D10 | 0.3 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Han, Z.; Chen, S.; Liu, H.; Wang, S.; Ma, B.; Chen, R.; Fu, X. A Novel DTSCR Structure with High Holding Voltage and Enhanced Current Discharge Capability for 28 nm CMOS Technology ESD Protection. Micromachines 2024, 15, 96. https://doi.org/10.3390/mi15010096

Han Z, Chen S, Liu H, Wang S, Ma B, Chen R, Fu X. A Novel DTSCR Structure with High Holding Voltage and Enhanced Current Discharge Capability for 28 nm CMOS Technology ESD Protection. Micromachines. 2024; 15(1):96. https://doi.org/10.3390/mi15010096

Chicago/Turabian StyleHan, Zeen, Shupeng Chen, Hongxia Liu, Shulong Wang, Boyang Ma, Ruibo Chen, and Xiaojun Fu. 2024. "A Novel DTSCR Structure with High Holding Voltage and Enhanced Current Discharge Capability for 28 nm CMOS Technology ESD Protection" Micromachines 15, no. 1: 96. https://doi.org/10.3390/mi15010096

APA StyleHan, Z., Chen, S., Liu, H., Wang, S., Ma, B., Chen, R., & Fu, X. (2024). A Novel DTSCR Structure with High Holding Voltage and Enhanced Current Discharge Capability for 28 nm CMOS Technology ESD Protection. Micromachines, 15(1), 96. https://doi.org/10.3390/mi15010096