Built-In Packaging for Two-Terminal Devices

Abstract

1. Introduction

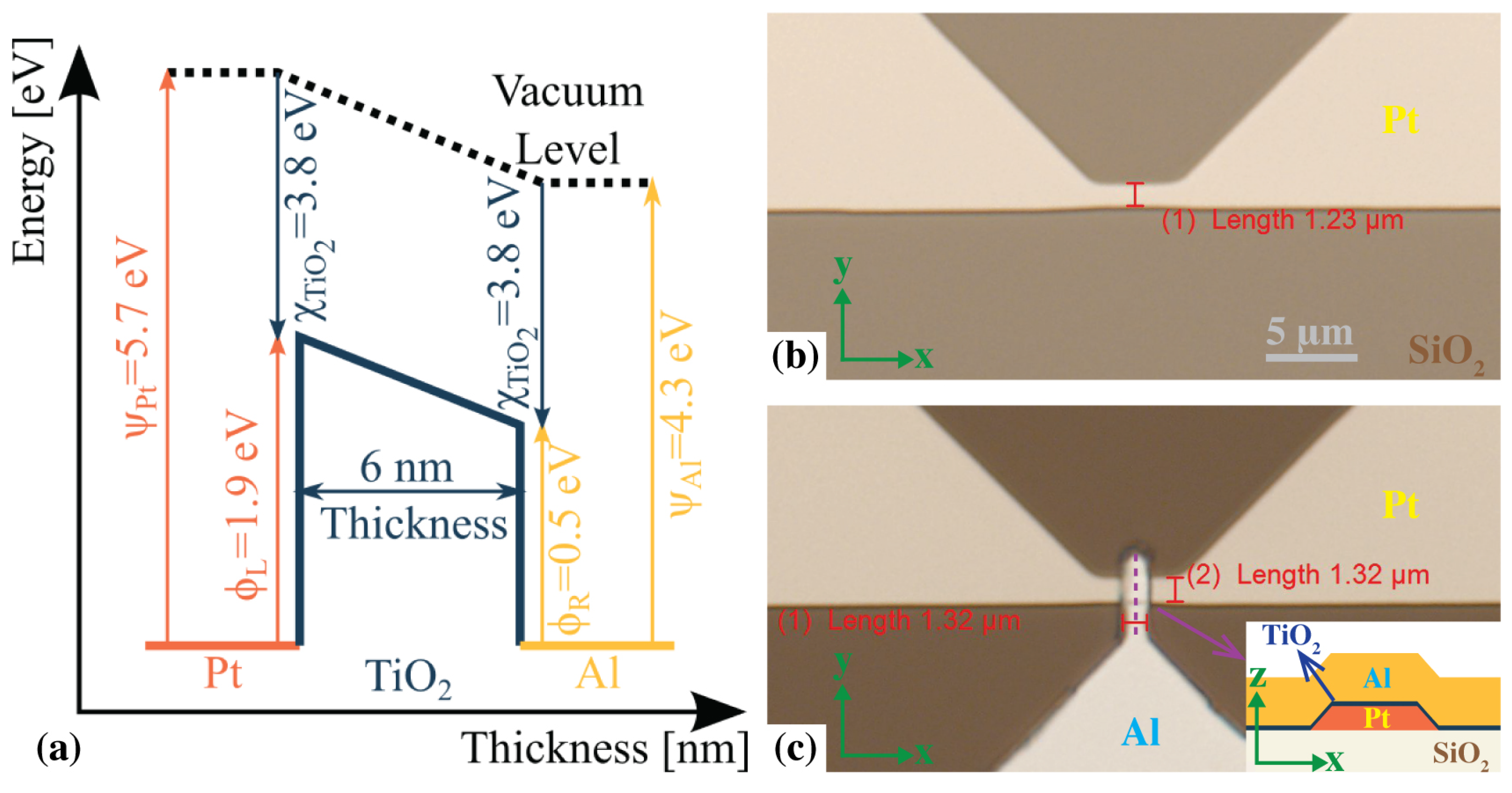

2. Materials and Methods

2.1. Fabrication

2.2. Packaging and Experimental Setup

3. Results and Discussion

4. Conclusions

Supplementary Materials

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

Appendix A. Python Code

import pandas as pd

import numpy as np

from scipy.signal import savgol_filter

import tkinter as tk

from tkinter import filedialog

import matplotlib.pyplot as plt

# Create a simple GUI for file selectionroot = tk.Tk()

root.withdraw()

# Ask the user to provide an Excel filefile_path = filedialog.askopenfilename()

# Load the data from the Excel filedata = pd.read_excel(file_path)

# Apply the Savitzky-Golay filter to the I datafiltered_I = savgol_filter(data[’I’], 2, 1)

# Calculate the first and second derivatives of the filtered I wrt. Vfirst_derivative = np.gradient(filtered_I, data[’V’])

second_derivative = np.gradient(first_derivative, data[’V’])

# Calculate the responsivityresponsivity = 2 ∗ second_derivative / first_derivative

# Apply the Savitzky-Golay filter to the responsivityfiltered_responsivity = savgol_filter(responsivity, 499, 3)

# Calculate non-linearitynon_linearity = first_derivative / (filtered_I / data[’V’])

# Apply the Savitzky-Golay filter to the non-linearityfiltered_non_linearity = savgol_filter(non_linearity, 499, 3)

# Calculate asymmetryasymmetry = np.abs(filtered_I / np.flip(filtered_I))

# Apply the Savitzky-Golay filter to the asymmetryfiltered_asymmetry = savgol_filter(asymmetry, 499, 3)

# Calculate resistanceresistance = np.gradient(data[’V’], filtered_I)

filtered_resistance = savgol_filter(resistance, 51, 1)

filtered_resistance = np.abs(filtered_resistance)

# Add calculated data to dataframedata[’filtered_I’] = filtered_I

data[’dI/dV’] = first_derivative

data[’d2I/dV2’] = second_derivative

data[’responsivity’] = responsivity

data[’filtered_responsivity’] = filtered_responsivity

data[’non_linearity’] = non_linearity

data[’filtered_non_linearity’] = filtered_non_linearity

data[’asymmetry’] = asymmetry

data[’filtered_asymmetry’] = filtered_asymmetry

data[’Resistance’] = resistance

data[’Filtered_Resistance’] = filtered_resistance

# Define indices for the plotsmarker_indices = np.arange(0, len(data[’V’]), len(data[’V’]) // 10)

# Start building the plotsplt.figure(figsize=(20, 15))

# Current plotplt.subplot(2, 3, 1)

plt.plot(data[’V’], np.log10(np.abs(data[’filtered_I’])), marker=’o’,

markevery=marker_indices)

plt.xlabel(’Voltage(V)’)

plt.ylabel(’Current(I)’)

plt.grid(True)

# Responsivity plotplt.subplot(2, 3, 2)

plt.plot(data[’V’], data[’filtered_responsivity’], marker=’o’,

markevery=marker_indices)

plt.xlabel(’Voltage(V)’)

plt.ylabel(’Responsivity(A/W)’)

plt.xlim(left=0, right=1)

plt.grid(True)

# Non-linearity plotplt.subplot(2, 3, 3)

plt.plot(data[’V’], data[’filtered_non_linearity’], marker=’o’,

markevery=marker_indices)

plt.xlabel(’Voltage(V)’)

plt.ylabel(’Non-linearity’)

plt.xlim(left=0, right=1)

plt.grid(True)

# Asymmetry plotplt.subplot(2, 3, 4)

plt.plot(data[’V’], data[’filtered_asymmetry’], marker=’o’,

markevery=marker_indices)

plt.xlabel(’Voltage(V)’)

plt.ylabel(’Asymmetry’)

plt.xlim(left=0, right=1)

plt.grid(True)

# Resistance plotplt.subplot(2, 3, 5)

plt.semilogy(data[’V’], data[’Filtered_Resistance’], marker=’o’,

markevery=marker_indices)

plt.xlabel(’Voltage(V)’)

plt.ylabel(’Resistance(Ohm)’)

plt.grid(True) # add grid lines

plt.xlim(left=0) # start x-axis at 0

# Save the figureplt.savefig(file_path.replace(’.xlsx’, ’-graph.png’))

# Write the filtered data to a new Excel filedata.to_excel(file_path.replace(’.xlsx’, ’-filtered.xlsx’), index=False)

References

- Tucker, J.; Millea, M. Photon detection in nonlinear tunneling devices. Appl. Phys. Lett. 1978, 33, 611–613. [Google Scholar] [CrossRef]

- Alshehri, A.H.; Shahin, A.; Mistry, K.; Ibrahim, K.H.; Yavuz, M.; Musselman, K.P. Metal-Insulator-Insulator-Metal Diodes with Responsivities Greater Than 30 AW- 1 Based on Nitrogen-Doped TiOx and AlOx Insulator Layers. Adv. Electron. Mater. 2021, 7, 2100467. [Google Scholar] [CrossRef]

- Grover, S.; Moddel, G. Applicability of metal/insulator/metal (MIM) diodes to solar rectennas. IEEE J. Photovoltaics 2011, 1, 78–83. [Google Scholar] [CrossRef]

- Khan, A.; Jayaswal, G.; Gahaffar, F.; Shamim, A. Metal-insulator-metal diodes with sub-nanometre surface roughness for energy-harvesting applications. Microelectron. Eng. 2017, 181, 34–42. [Google Scholar] [CrossRef]

- Tekin, S.B.; Weerakkody, A.; Sedghi, N.; Hall, S.; Werner, M.; Wrench, J.; Chalker, P.; Mitrovic, I. Single and triple insulator Metal-Insulator-Metal diodes for infrared rectennas. Solid-State Electron. 2021, 185, 108096. [Google Scholar] [CrossRef]

- Bhatt, K.; Tripathi, C. Comparative Analysis of Efficient Diode Design for Terahertz Wireless Power Transmission System; NISCAIR-CSIR: New Delhi, India, 2015. [Google Scholar]

- Liang, Z.; Wen, Y.; Zhang, Z.; Liang, Z.; Xu, Z.; Lin, Y.S. Plasmonic metamaterial using metal-insulator-metal nanogratings for high-sensitive refraction index sensor. Results Phys. 2019, 15, 102602. [Google Scholar] [CrossRef]

- Kazanskiy, N.; Khonina, S.; Butt, M. Plasmonic sensors based on Metal-insulator-metal waveguides for refractive index sensing applications: A brief review. Phys. E Low-Dimens. Syst. Nanostruct. 2020, 117, 113798. [Google Scholar] [CrossRef]

- Shriwastava, S.; Tripathi, C. Metal–insulator–metal diodes: A potential high frequency rectifier for rectenna application. J. Electron. Mater. 2019, 48, 2635–2652. [Google Scholar] [CrossRef]

- Chen, C.; Wang, G.; Zhang, Z.; Zhang, K. Dual narrow-band absorber based on metal–insulator–metal configuration for refractive index sensing. Opt. Lett. 2018, 43, 3630–3633. [Google Scholar] [CrossRef]

- Gulsaran, A.; Bastug Azer, B.; Kocer, S.; Rahmanian, S.; Saritas, R.; Abdel-Rahman, E.M.; Yavuz, M. Built-In Packaging for Single Terminal Devices. Sensors 2022, 22, 5264. [Google Scholar] [CrossRef]

- Vertyanov, D.V.; Belyakov, I.A.; Timoshenkov, S.P.; Borisova, A.V.; Sidorenko, V.N. Effects of Gold-aluminum Intermetallic Compounds on Chip Wire Bonding Interconnections Reliability. In Proceedings of the 2020 IEEE Conference of Russian Young Researchers in Electrical and Electronic Engineering (EIConRus), St. Petersburg and Moscow, Russia, 27–30 January 2020; pp. 2216–2220. [Google Scholar]

- Ji, B.; Pickert, V.; Cao, W.; Zahawi, B. In situ diagnostics and prognostics of wire bonding faults in IGBT modules for electric vehicle drives. IEEE Trans. Power Electron. 2013, 28, 5568–5577. [Google Scholar] [CrossRef]

- Goh, C.S.; Chong, W.L.E.; Lee, T.K.; Breach, C. Corrosion study and intermetallics formation in gold and copper wire bonding in microelectronics packaging. Crystals 2013, 3, 391–404. [Google Scholar] [CrossRef]

- Gan, C.L.; Francis, C.; Chan, B.L.; Hashim, U. Extended reliability of gold and copper ball bonds in microelectronic packaging. Gold Bull. 2013, 46, 103–115. [Google Scholar] [CrossRef]

- Fu, S.W.; Lee, C.C. A study on intermetallic compound formation in Ag–Al system and evaluation of its mechanical properties by micro-indentation. J. Mater. Sci. Mater. Electron. 2018, 29, 3985–3991. [Google Scholar] [CrossRef]

- Li, X.; Gao, L.; Ni, T.; Zhou, J.; Li, X.; Li, Y.; Xu, L.; Wang, R.; Zeng, C.; Li, B.; et al. Analysis of Degradation of Electromigration Reliability of Au-Al and OPM Wire Bonded Contacts at 250 °C Using Resistance Monitoring Method. Micromachines 2023, 14, 640. [Google Scholar] [CrossRef]

- Wu, C.; Wang, J.; Liu, X.; Li, M.; Zhu, Z.; Qi, Y. Au wire ball welding and its reliability test for high-temperature environment. Micromachines 2022, 13, 1603. [Google Scholar] [CrossRef]

- Bareiß, M.; Ante, F.; Kalblein, D.; Jegert, G.; Jirauschek, C.; Scarpa, G.; Fabel, B.; Nelson, E.M.; Timp, G.; Zschieschang, U.; et al. High-yield transfer printing of metal–insulator–metal nanodiodes. ACS Nano 2012, 6, 2853–2859. [Google Scholar] [CrossRef]

- Taghipour, A.; Heidarzadeh, H. Design and Analysis of Highly Sensitive LSPR-Based Metal–Insulator–Metal Nano-Discs as a Biosensor for Fast Detection of SARS-CoV-2. Photonics 2022, 9, 542. [Google Scholar] [CrossRef]

- Hackett, L.P.; Ameen, A.; Li, W.; Dar, F.K.; Goddard, L.L.; Liu, G.L. Spectrometer-free plasmonic biosensing with metal–insulator–metal nanocup arrays. ACS Sensors 2018, 3, 290–298. [Google Scholar] [CrossRef]

- Alshehri, A.H.; Mistry, K.; Nguyen, V.H.; Ibrahim, K.H.; Muñoz-Rojas, D.; Yavuz, M.; Musselman, K.P. Quantum-Tunneling Metal-Insulator-Metal Diodes Made by Rapid Atmospheric Pressure Chemical Vapor Deposition. Adv. Funct. Mater. 2019, 29, 1805533. [Google Scholar] [CrossRef]

- Periasamy, P.; Berry, J.J.; Dameron, A.A.; Bergeson, J.D.; Ginley, D.S.; O’Hayre, R.P.; Parilla, P.A. Fabrication and characterization of MIM diodes based on Nb/Nb2O5 via a rapid screening technique. Adv. Mater. 2011, 23, 3080–3085. [Google Scholar] [CrossRef]

- Azer, B.B.; Gulsaran, A.; Pennings, J.R.; Saritas, R.; Kocer, S.; Bennett, J.L.; Abhang, Y.D.; Pope, M.A.; Abdel-Rahman, E.; Yavuz, M. A Review: TiO2 based photoelectrocatalytic chemical oxygen demand sensors and their usage in industrial applications. J. Electroanal. Chem. 2022, 918, 116466. [Google Scholar] [CrossRef]

- Hu, X.; Liu, L.; Liu, S.; Ruan, M.; Chen, Z. Effects of Voids on Thermal Fatigue Reliability of Solder Joints on Inner Rings in Ball Grid Array Packaging by Finite Element Analysis. Micromachines 2023, 14, 588. [Google Scholar] [CrossRef] [PubMed]

- Le, X.L.; Le, X.B.; Hwangbo, Y.; Joo, J.; Choi, G.M.; Eom, Y.S.; Choi, K.S.; Choa, S.H. Mechanical Reliability Assessment of a Flexible Package Fabricated Using Laser-Assisted Bonding. Micromachines 2023, 14, 601. [Google Scholar] [CrossRef]

- Pelz, B.; Moddel, G. Demonstration of distributed capacitance compensation in a metal-insulator-metal infrared rectenna incorporating a traveling-wave diode. J. Appl. Phys. 2019, 125, 234502. [Google Scholar] [CrossRef]

- Bhatt, K.; Kumar, S.; Tripathi, C.C. Highly sensitive Al/Al2O3/Ag MIM diode for energy harvesting applications. AEU-Int. J. Electron. Commun. 2019, 111, 152925. [Google Scholar] [CrossRef]

- Kinzel, E.C.; Brown, R.L.; Ginn, J.C.; Lail, B.A.; Slovick, B.A.; Boreman, G.D. Design of an MOM diode-coupled frequency-selective surface. Microw. Opt. Technol. Lett. 2013, 55, 489–493. [Google Scholar] [CrossRef]

- Bean, J.A.; Tiwari, B.; Bernstein, G.H.; Fay, P.; Porod, W. Thermal infrared detection using dipole antenna-coupled metal-oxide-metal diodes. J. Vac. Sci. Technol. Microelectron. Nanometer Struct. Process. Meas. Phenom. 2009, 27, 11–14. [Google Scholar] [CrossRef]

- Tiwari, B.; Bean, J.A.; Szakmány, G.; Bernstein, G.H.; Fay, P.; Porod, W. Controlled etching and regrowth of tunnel oxide for antenna-coupled metal-oxide-metal diodes. J. Vac. Sci. Technol. Microelectron. Nanometer Struct. Process. Meas. Phenom. 2009, 27, 2153–2160. [Google Scholar] [CrossRef]

- Chin, M.L.; Periasamy, P.; O’Regan, T.P.; Amani, M.; Tan, C.; O’Hayre, R.P.; Berry, J.J.; Osgood, R.M.; Parilla, P.A.; Ginley, D.S.; et al. Planar metal–insulator–metal diodes based on the Nb/Nb2O5/X material system. J. Vac. Sci. Technol. 2013, 31. [Google Scholar] [CrossRef]

- Esfandiari, P.; Bernstein, G.; Fay, P.; Porod, W.; Rakos, B.; Zarandy, A.; Berland, B.; Boloni, L.; Boreman, G.; Lail, B.; et al. Tunable antenna-coupled metal-oxide-metal (MOM) uncooled IR detector. In Infrared Technology and Applications XXXI; SPIE: Bellingham, WA, USA, 2005; Volume 5783, pp. 470–482. [Google Scholar]

- Hocini, A.; Melouki, N.; Khedrouche, D. Design and analysis of near infrared high sensitive metal-insulator-metal plasmonic bio-sensor. In IOP Conference Series: Materials Science and Engineering, Proceedings of the 5th International Conference on Advanced Sciences ICAS5, Hurghada, Egypt, 10–12 November 2019; IOP Publishing: Bristol, UK, 2021; Volume 1046, p. 012003. [Google Scholar]

- Shinohara, N. Trends in wireless power transfer: WPT technology for energy harvesting, mllimeter-wave/THz rectennas, MIMO-WPT, and advances in near-field WPT applications. IEEE Microw. Mag. 2020, 22, 46–59. [Google Scholar] [CrossRef]

- Tran, L.G.; Cha, H.K.; Park, W.T. RF power harvesting: A review on designing methodologies and applications. Micro Nano Syst. Lett. 2017, 5, 14. [Google Scholar] [CrossRef]

| Layer | Step 1 | Step 2 | Step 3 | Step 4 |

|---|---|---|---|---|

| Bottom electrode | PR coating | Lithography | Deposition | Litfoff |

| Insulator | Deposition | PR coating | Lithography | Wet etch |

| Top electrode | PR coating | Lithography | Deposition | Litfoff |

| Structure | Insulator Thickness [nm] | Area [m] | Asym. ≈ V | Max. Nonlin. | Zero-Bias Respon [V] | Max. Respon. [V] | Max. J [A/cm] | Zero-Bias Resistance [] | Application | Interconnection | Ref. |

|---|---|---|---|---|---|---|---|---|---|---|---|

| Al/AlO/Ag | 0.75 | 1.2 | 9 | 9 | Rectenna | Probing | [28] | ||||

| Al/AlO/Pt | 0.1–0.2 | 1 | - | IR-detector | Probing | [29] | |||||

| Al/AlO/Pt | 1–2.5 | - | - | - | 4.8 | IR-detector | Probing/Wire bonding | [30] | |||

| Al/AlO/Pt | 2.5–3.5 | 1 | - | IR-detector | Probing/Wire bonding | [31] | |||||

| Nb/NbO/Pt | 15 | 4.7 | 15 | 16.9 | - | Probing | [32] | ||||

| Ni/NiO/Pt | 1–2 | - | 9 | - | 6.5 | ≈ | IR-detector | Probing | [33] | ||

| Al/TiO/Pt | 6 | 1.7 | 3.7 | 0.55 | 14.3 | - | Probing | ours | |||

| Al/TiO/Pt | 6 | 1.7 | 3.7 | 0.55 | 14.3 | - | Wire bonding | ours | |||

| Al/TiO/Pt | 6 | 1.7 | 3.7 | 0.55 | 14.3 | - | Built-in | ours |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Gulsaran, A.; Bastug Azer, B.; Ozyigit, D.; Saritas, R.; Kocer, S.; Abdel-Rahman, E.; Yavuz, M. Built-In Packaging for Two-Terminal Devices. Micromachines 2023, 14, 1473. https://doi.org/10.3390/mi14071473

Gulsaran A, Bastug Azer B, Ozyigit D, Saritas R, Kocer S, Abdel-Rahman E, Yavuz M. Built-In Packaging for Two-Terminal Devices. Micromachines. 2023; 14(7):1473. https://doi.org/10.3390/mi14071473

Chicago/Turabian StyleGulsaran, Ahmet, Bersu Bastug Azer, Dogu Ozyigit, Resul Saritas, Samed Kocer, Eihab Abdel-Rahman, and Mustafa Yavuz. 2023. "Built-In Packaging for Two-Terminal Devices" Micromachines 14, no. 7: 1473. https://doi.org/10.3390/mi14071473

APA StyleGulsaran, A., Bastug Azer, B., Ozyigit, D., Saritas, R., Kocer, S., Abdel-Rahman, E., & Yavuz, M. (2023). Built-In Packaging for Two-Terminal Devices. Micromachines, 14(7), 1473. https://doi.org/10.3390/mi14071473