Research of Vertical via Based on Silicon, Ceramic and Glass

Abstract

1. Introduction

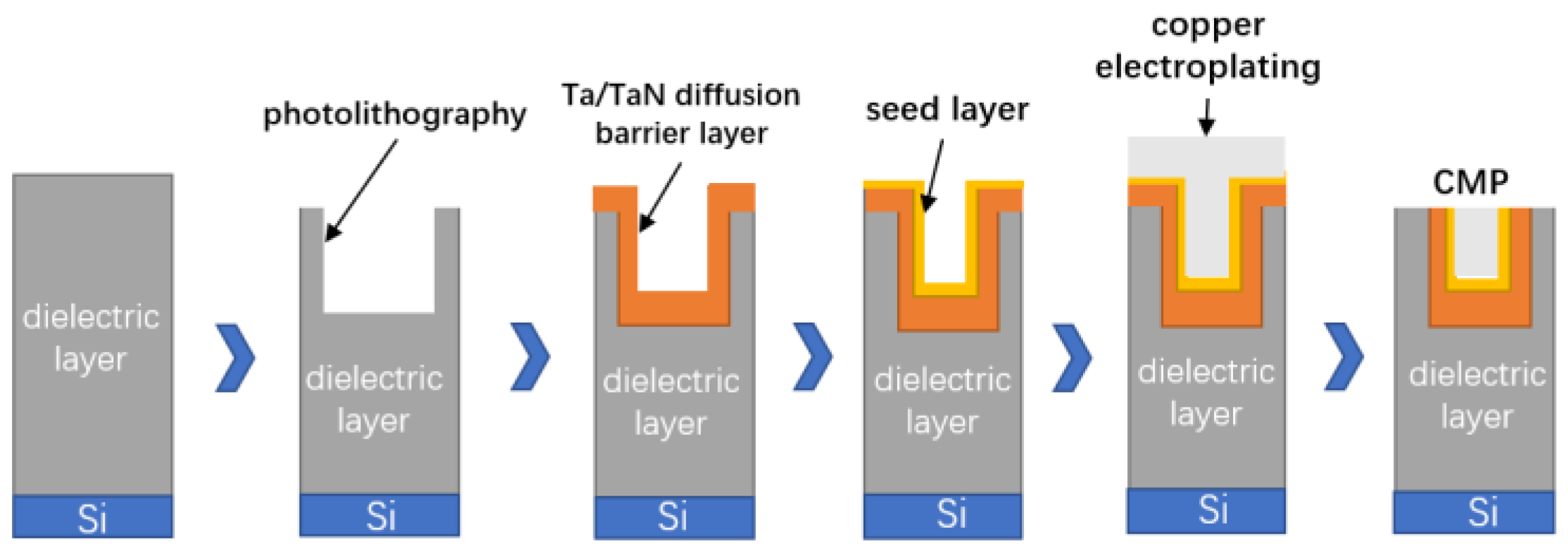

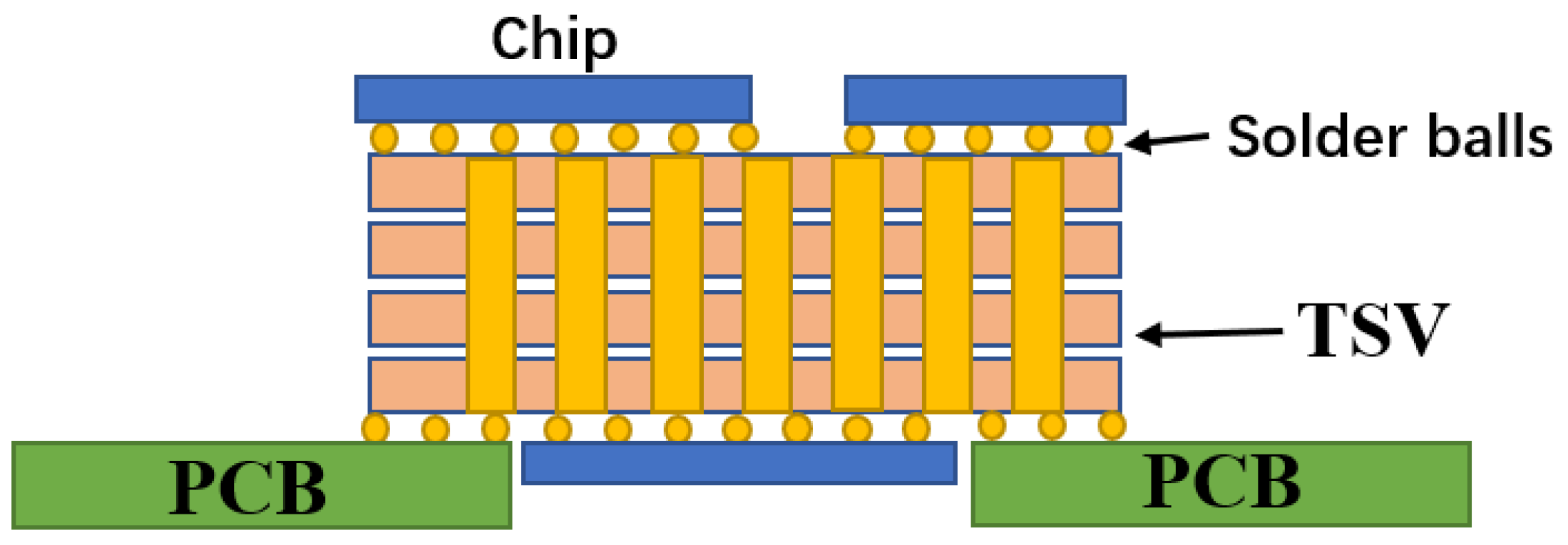

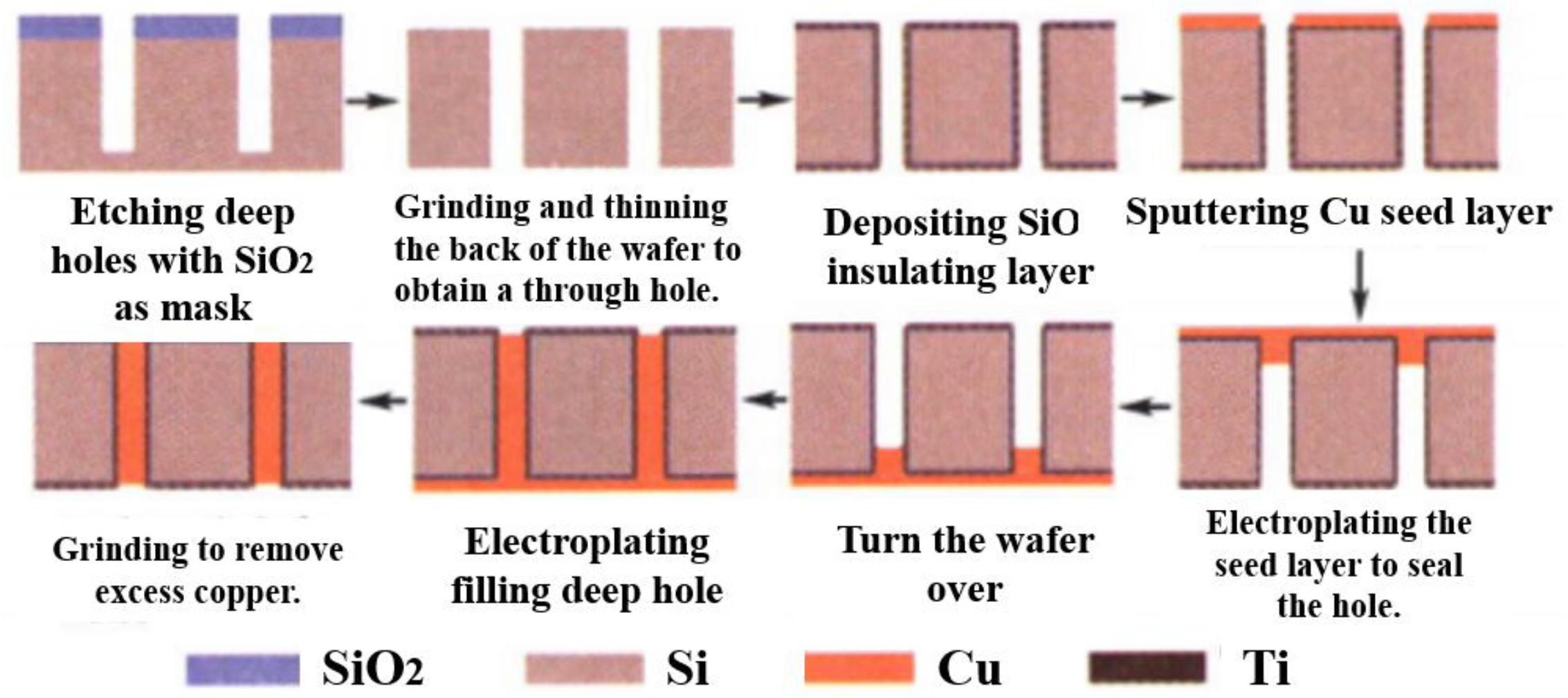

2. TSV Technology Process and Development

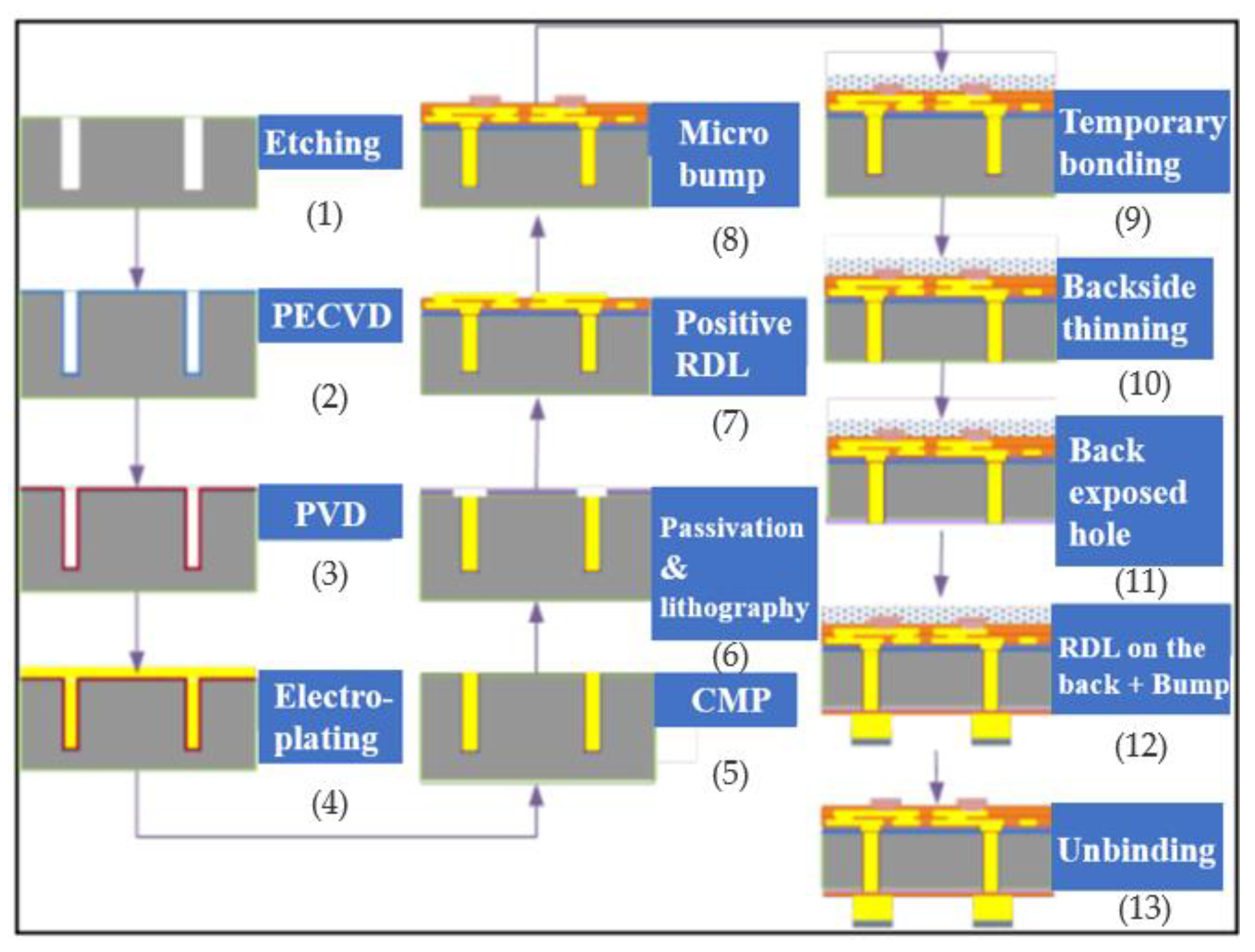

2.1. Silicon through Hole Manufacturing Process

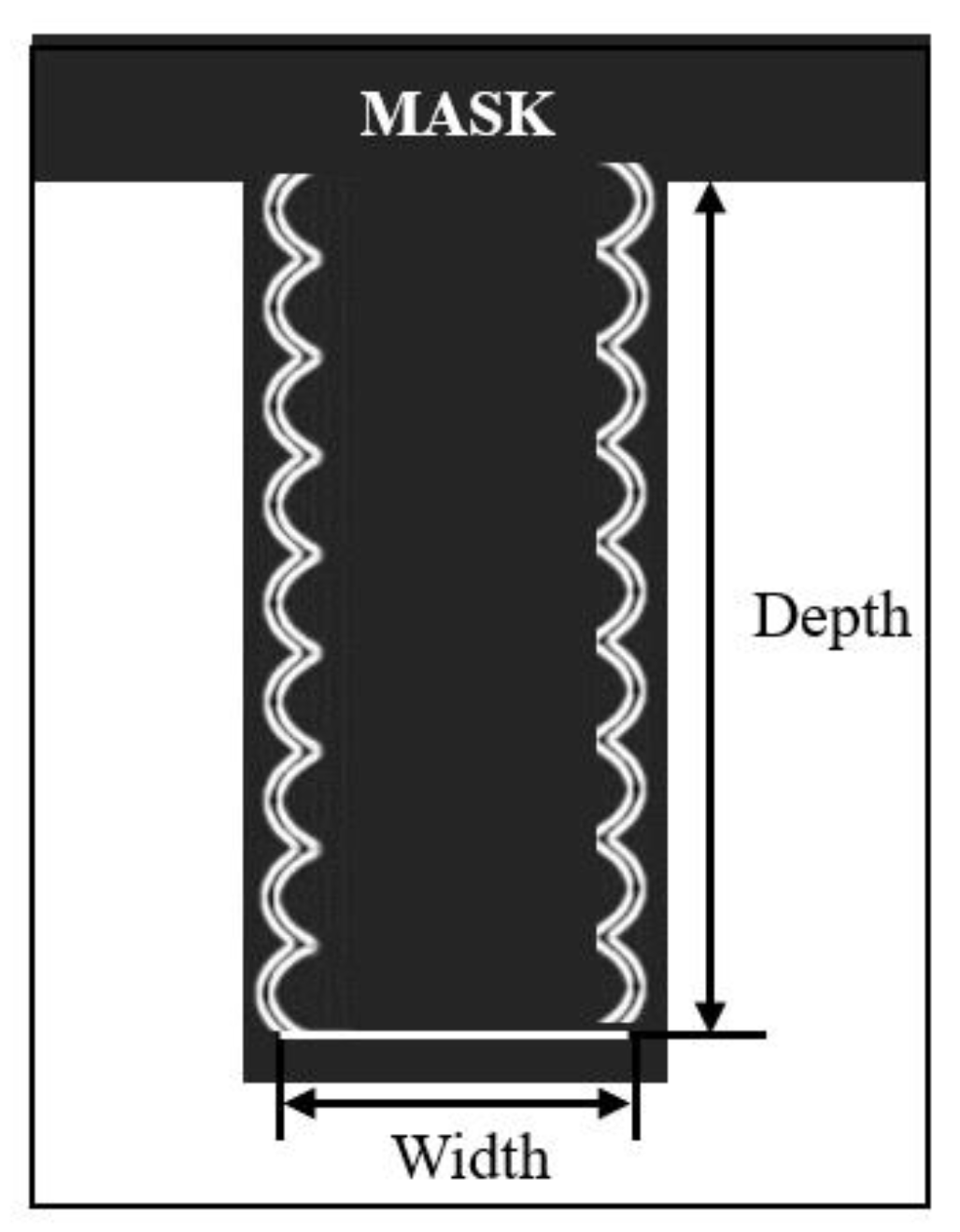

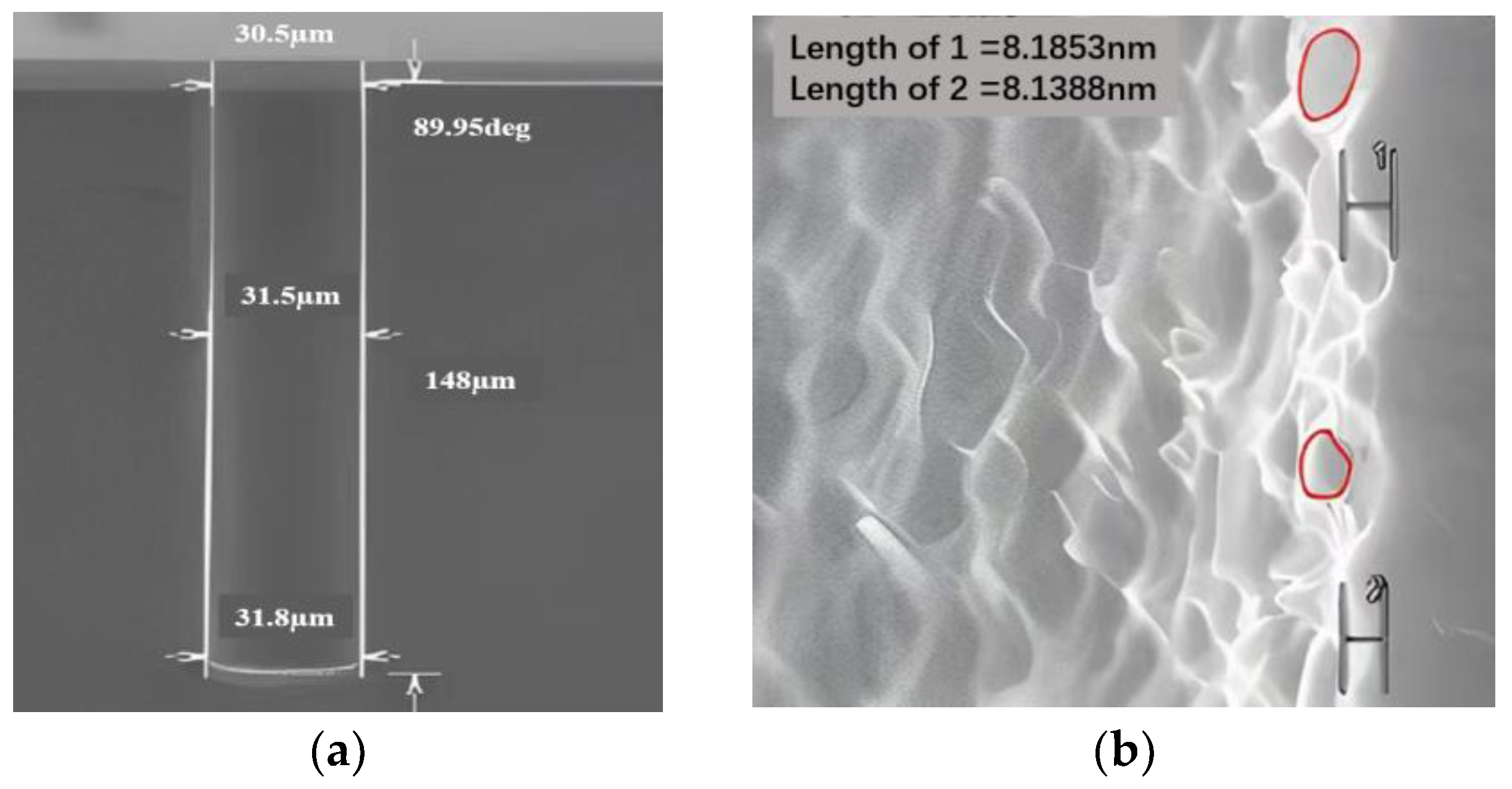

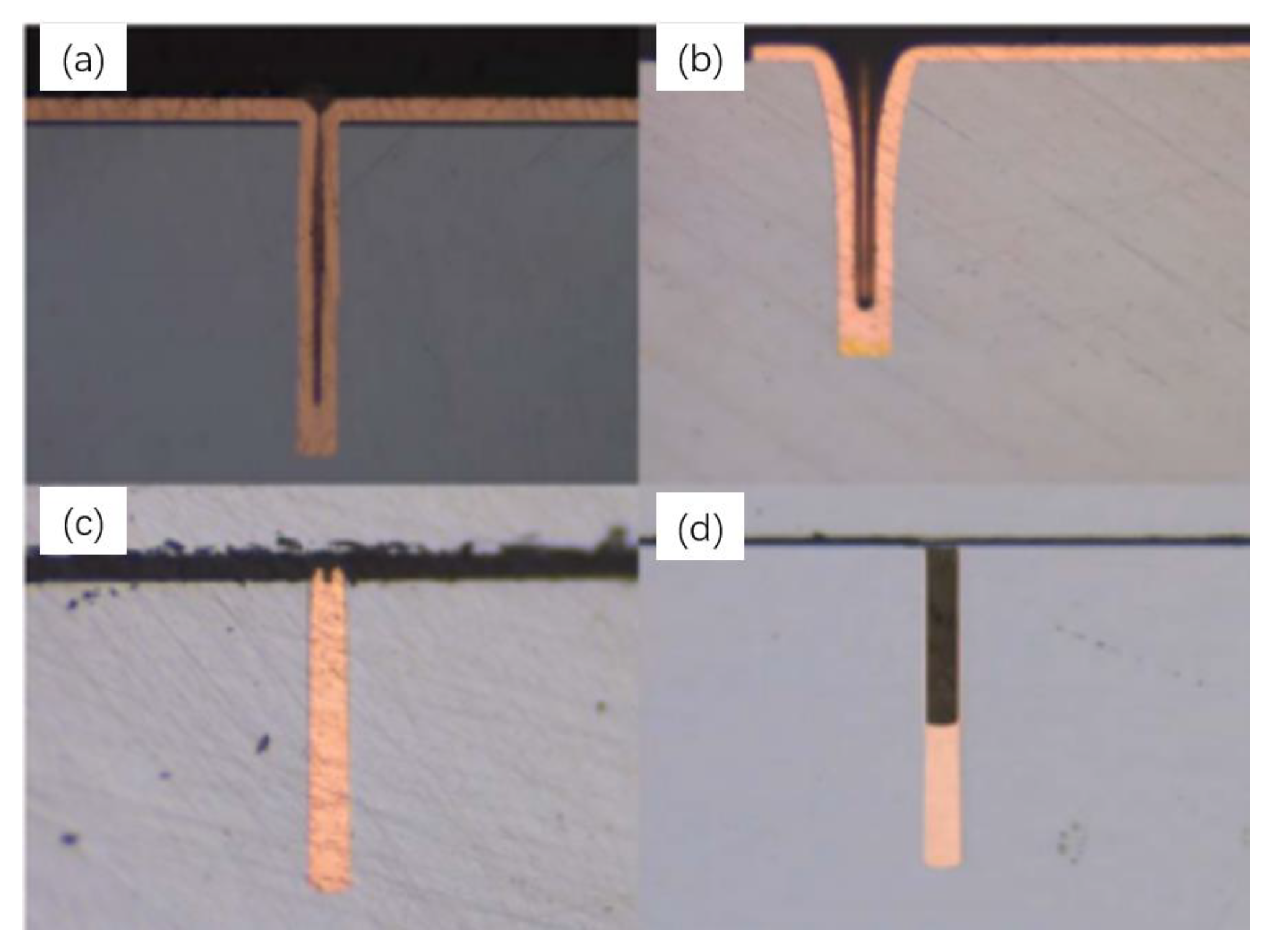

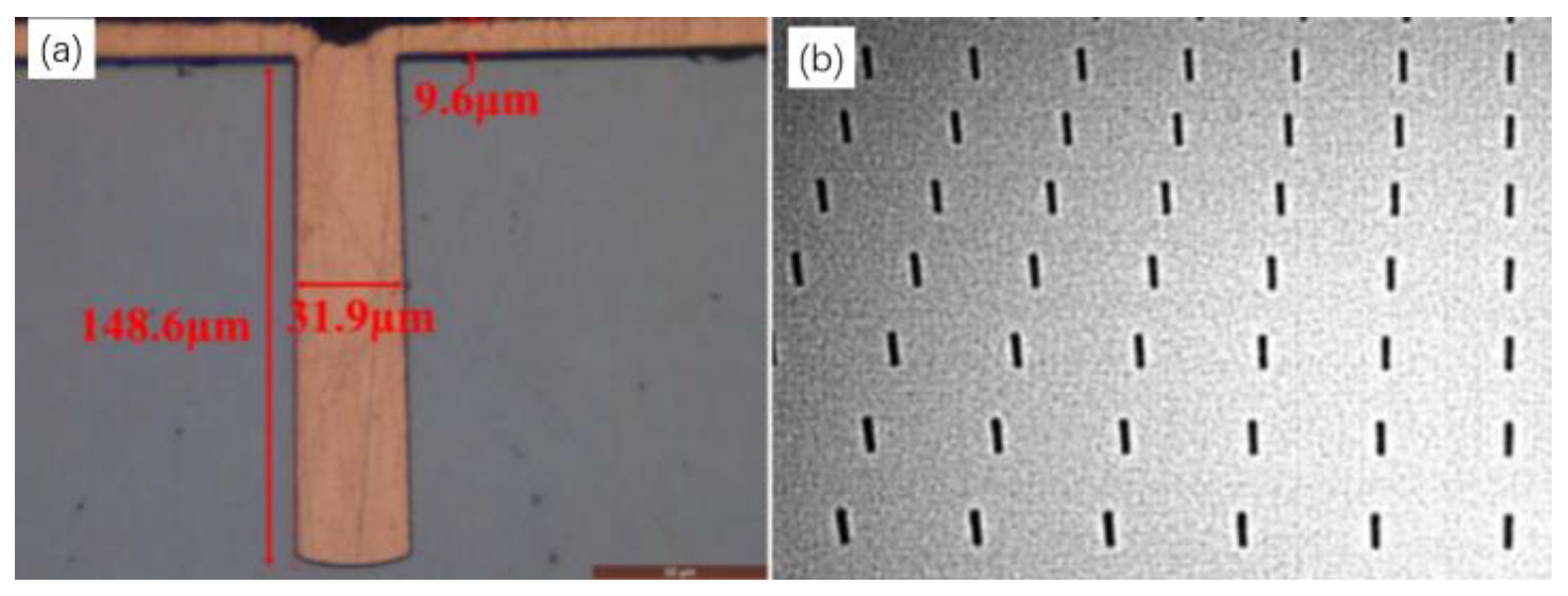

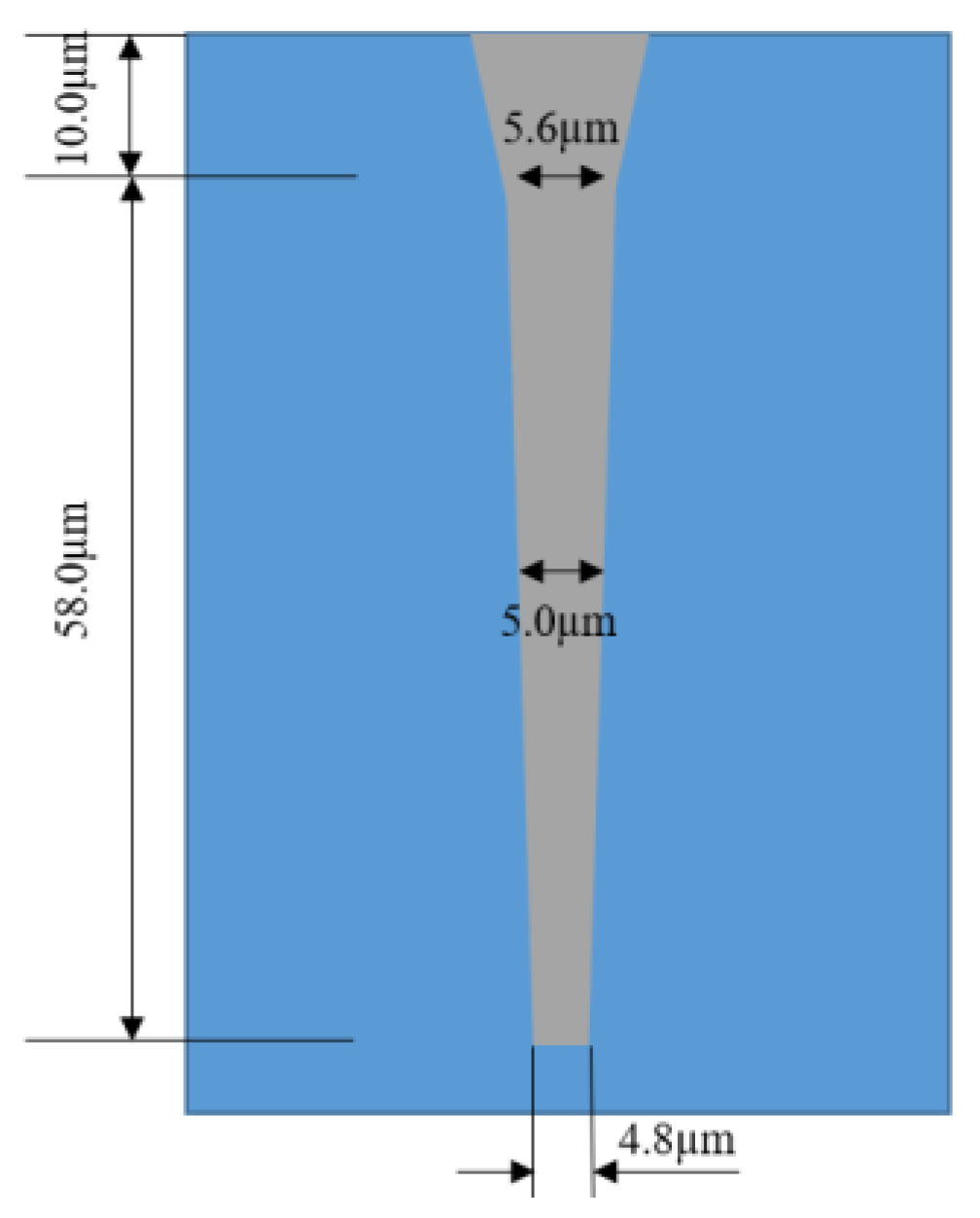

2.1.1. Deep Silicon Etching

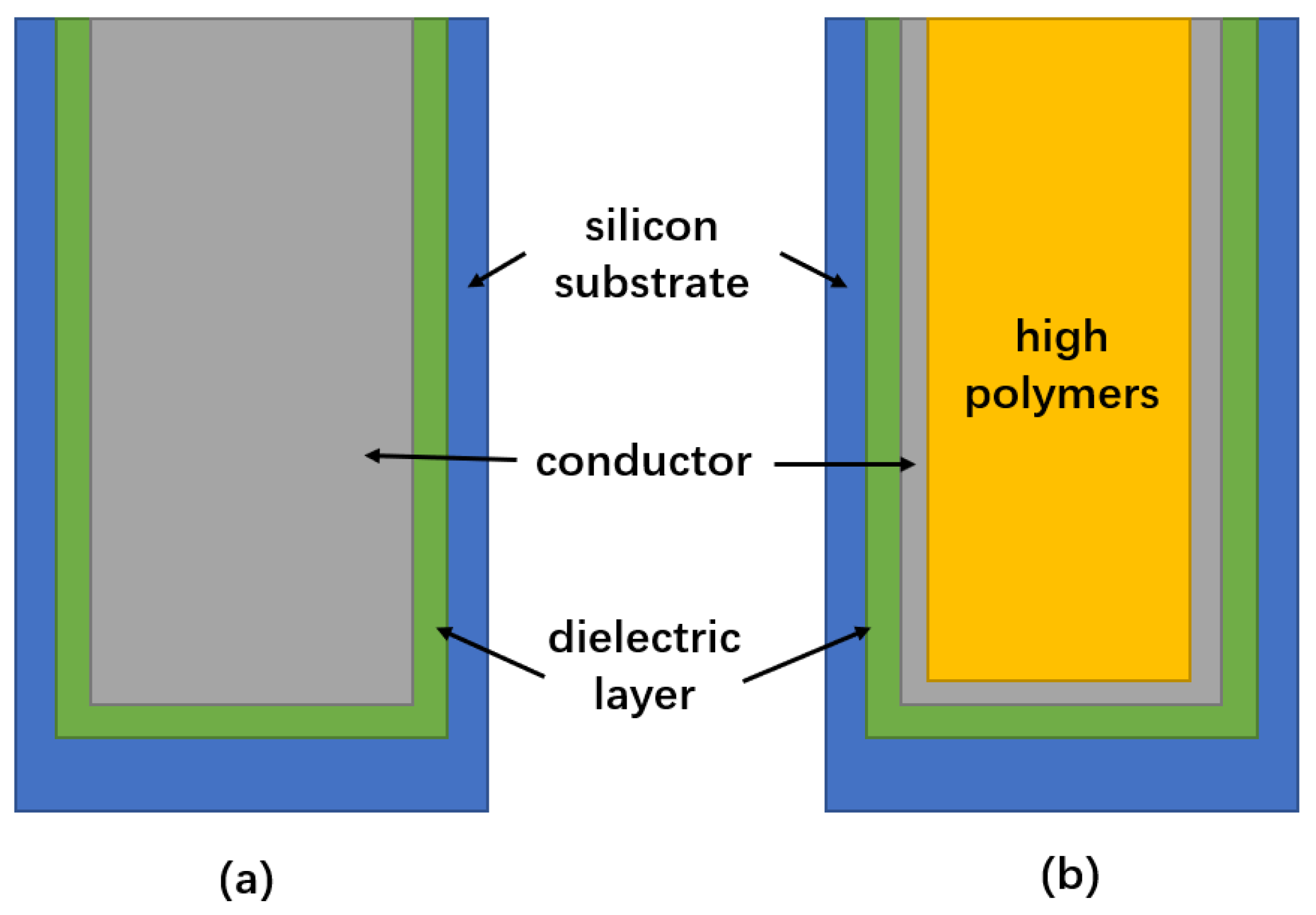

2.1.2. Insulating Layer Deposition Process

2.1.3. Metal Deposition of Barrier Layer and Seed Layer

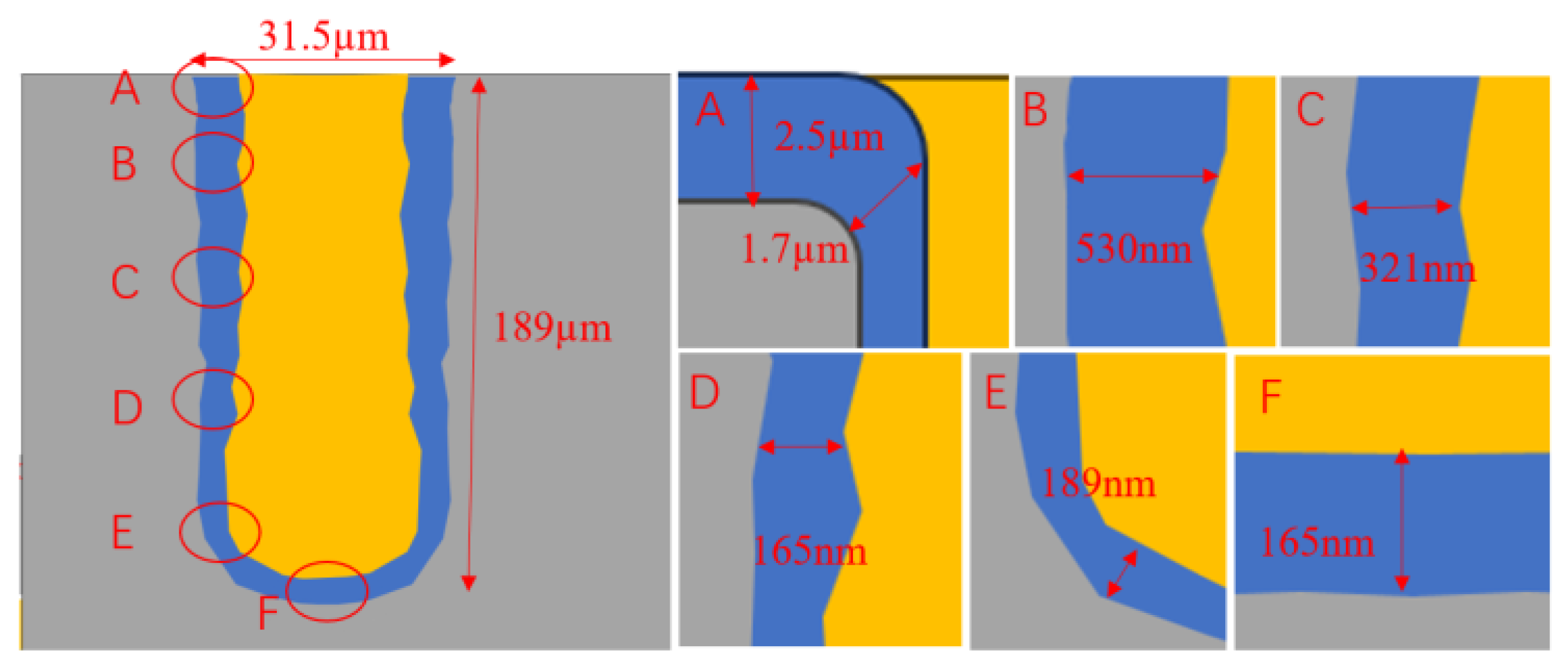

2.1.4. Center Conductor Filling

2.1.5. Wafer Front CMP Process

2.1.6. Wafer TSV Back Outcrop Process

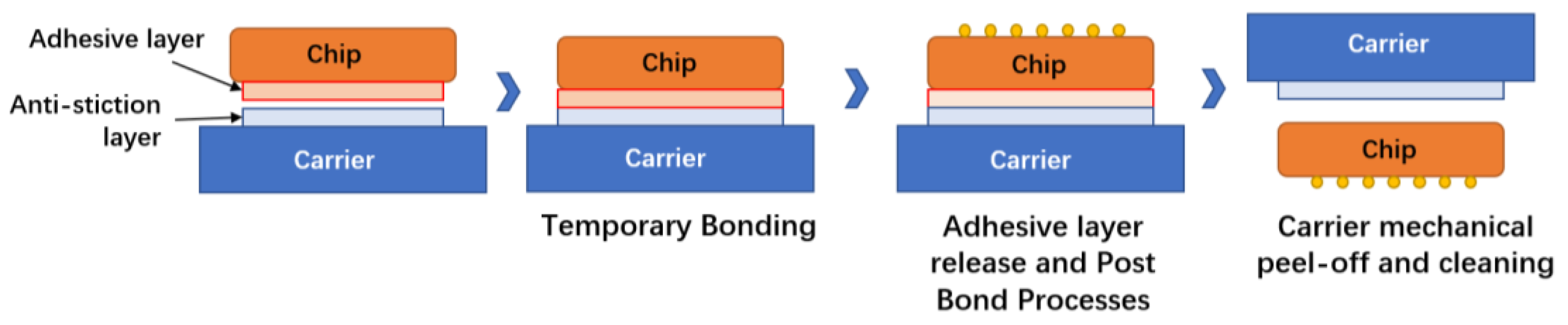

2.1.7. Temporary Bonding/De-Binding Process (TBDB) for Ultra-Thin Wafers

2.2. Development Status of TSV Technology at Home and Abroad

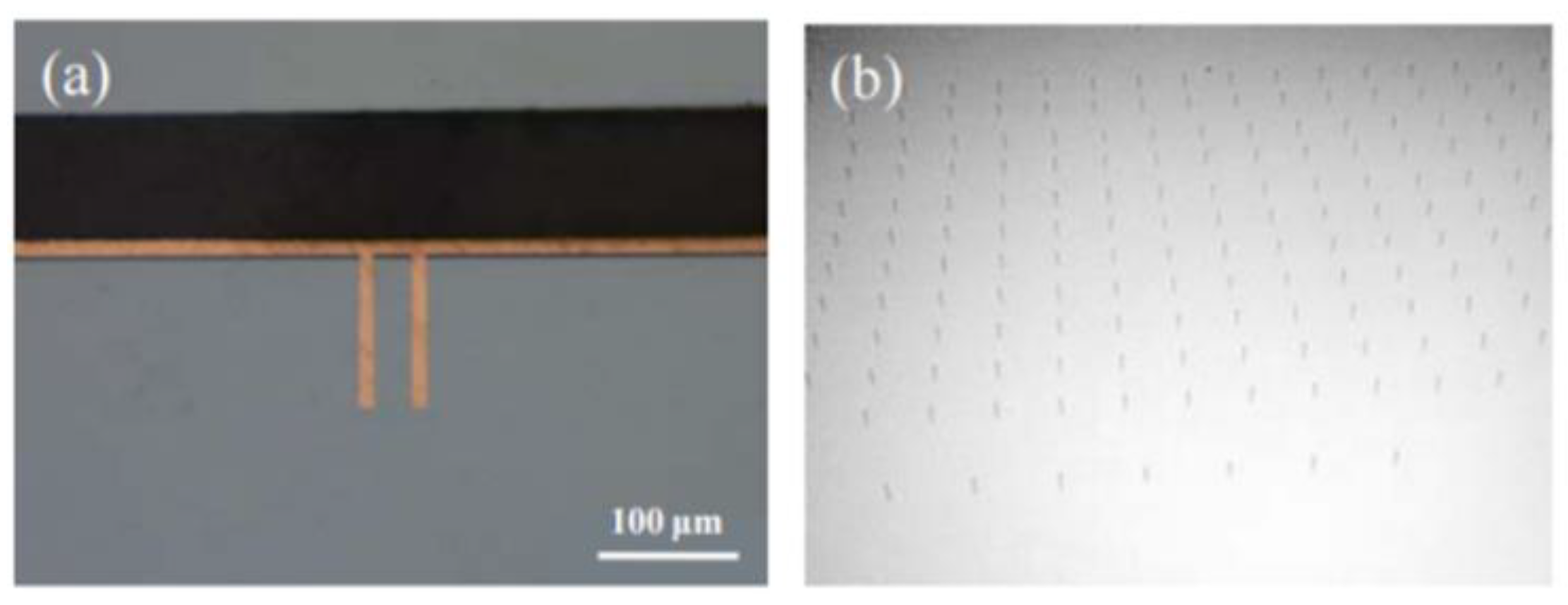

2.2.1. Domestic Development Status of TSV

- (1)

- Homogeneous high-density 3D integration has made a comprehensive breakthrough and is being industrialized.

- (2)

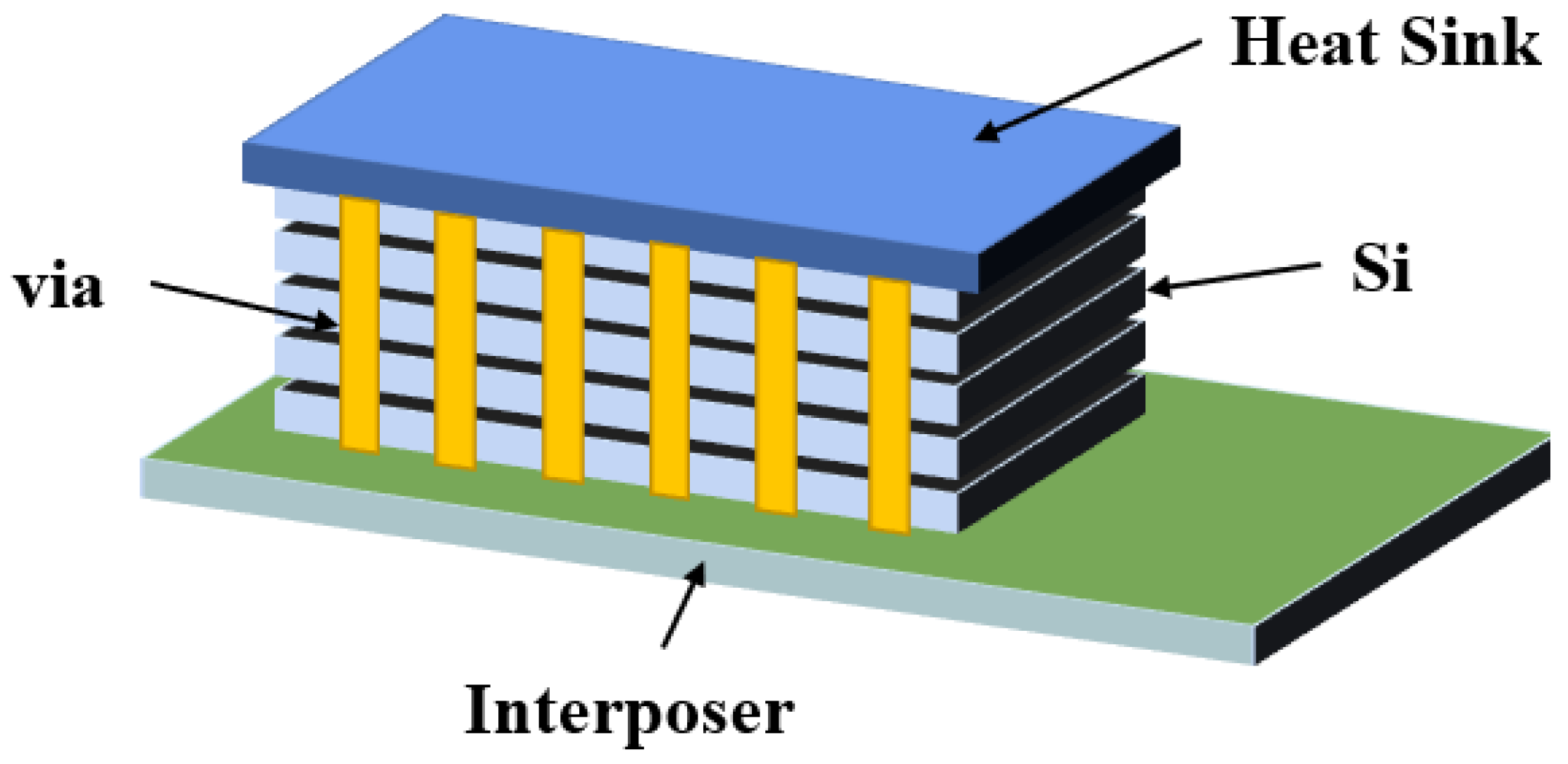

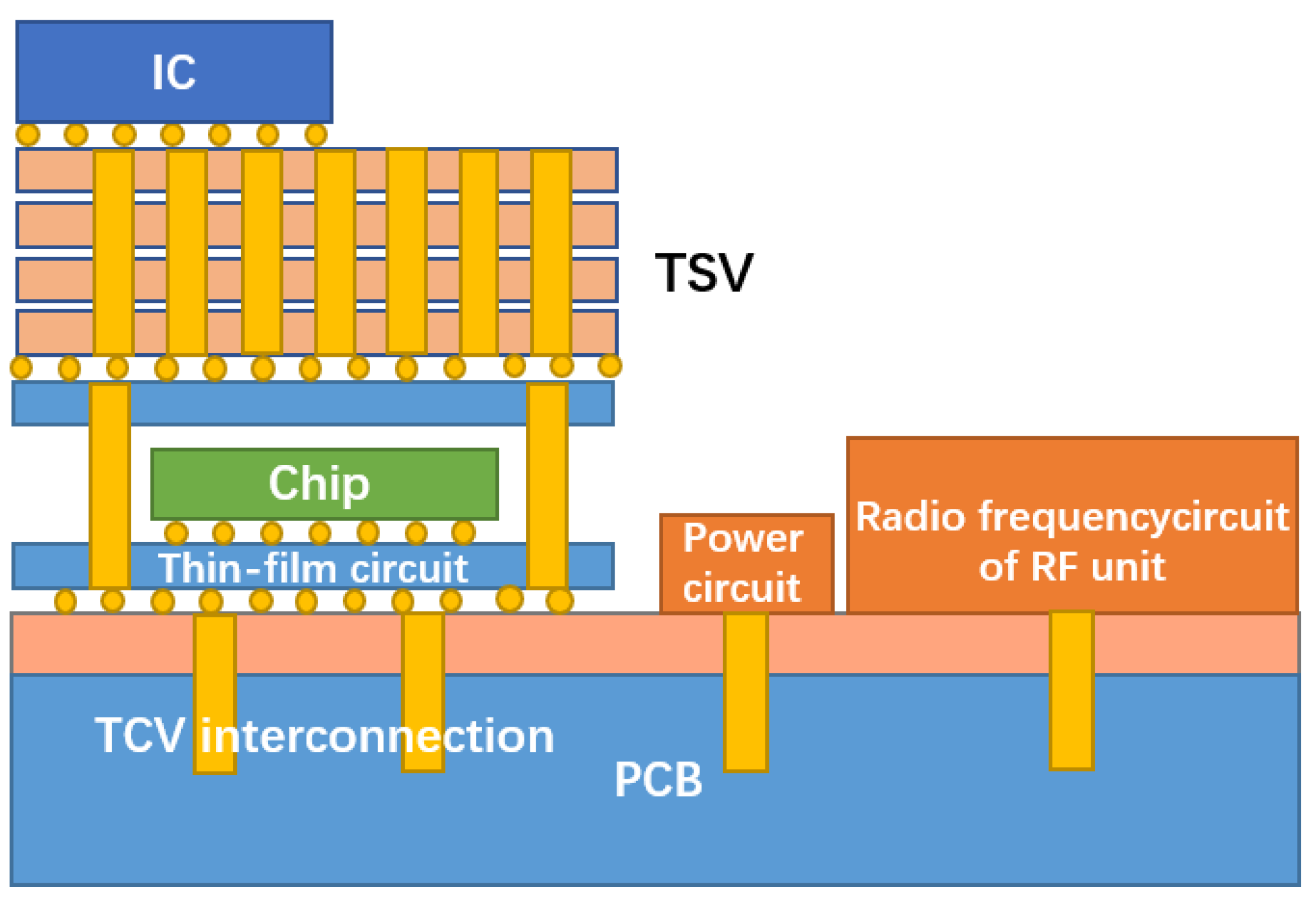

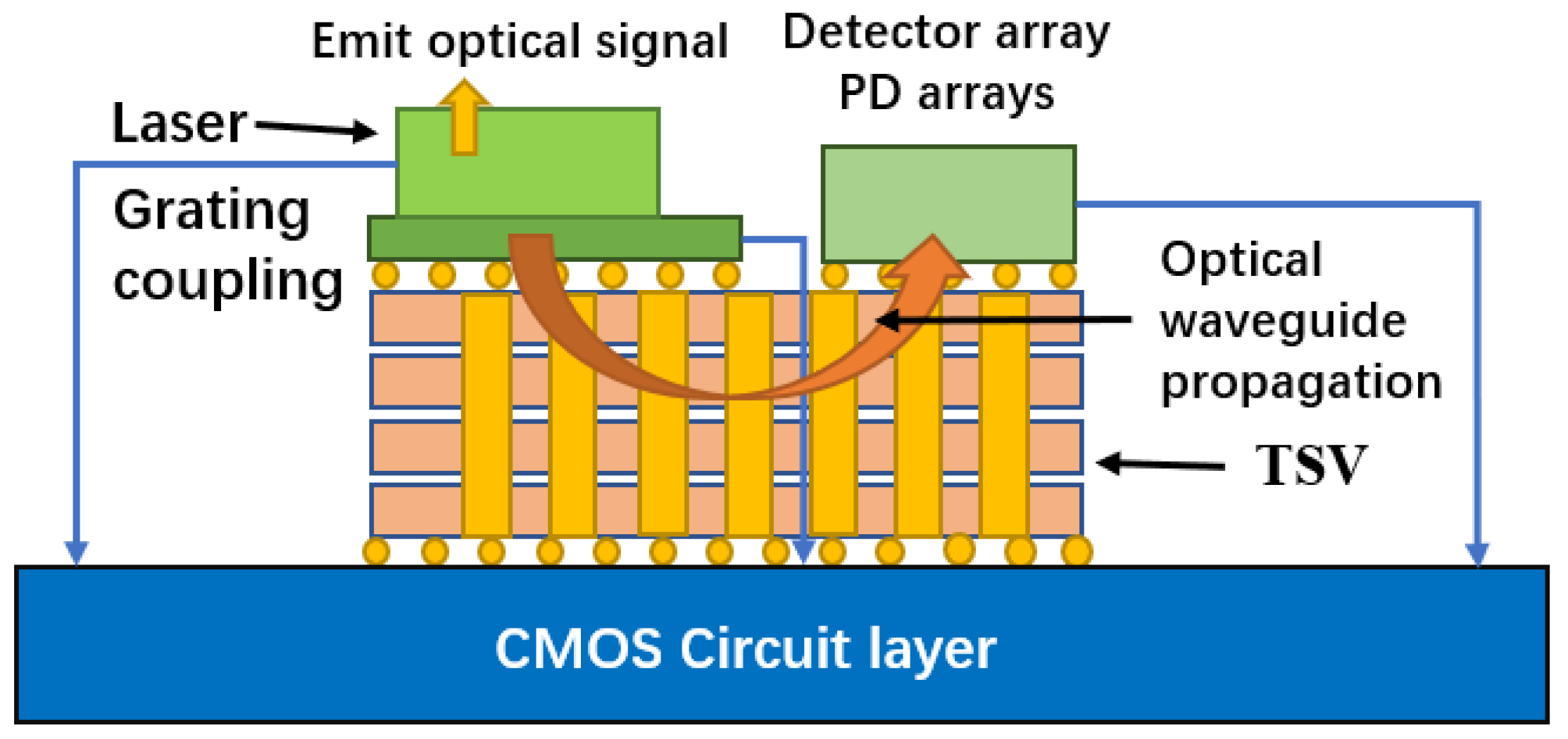

- The development status of heterogeneous 3D integration based on a silicon interposer.

2.2.2. Development Status of TSV Abroad

3. Optimization and Reliability Analysis of TSV Technology

3.1. TSV Technology Optimization

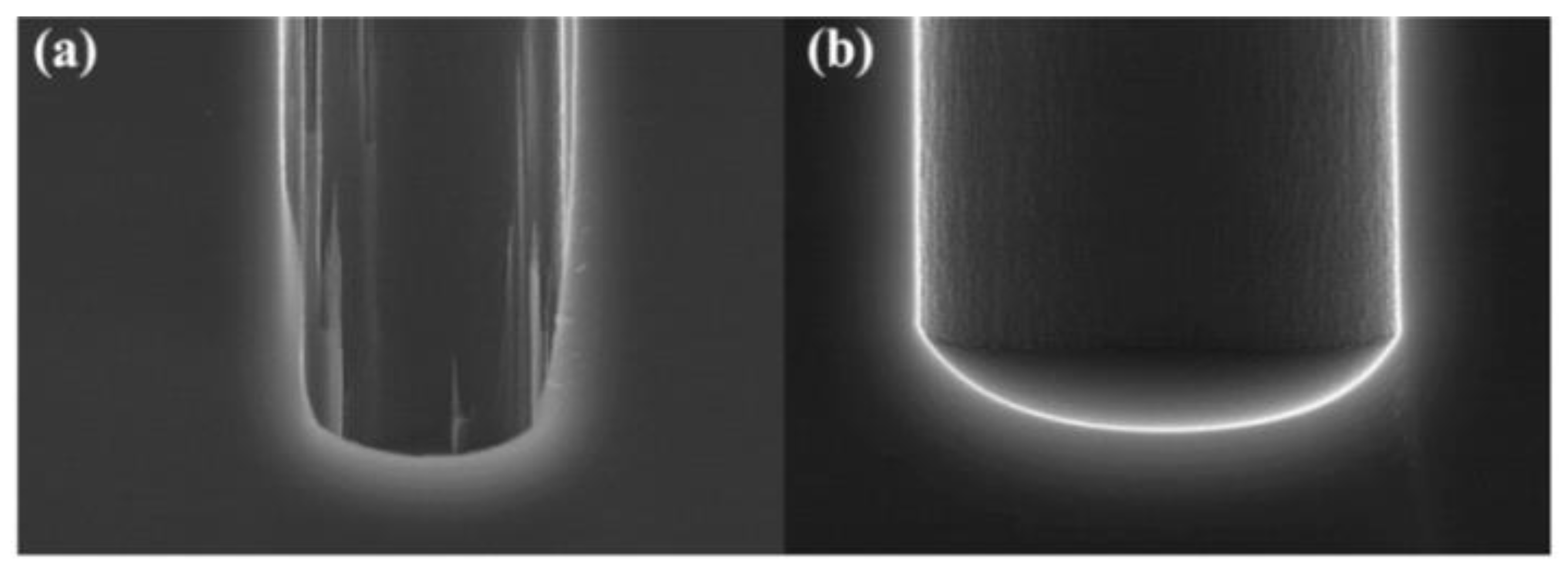

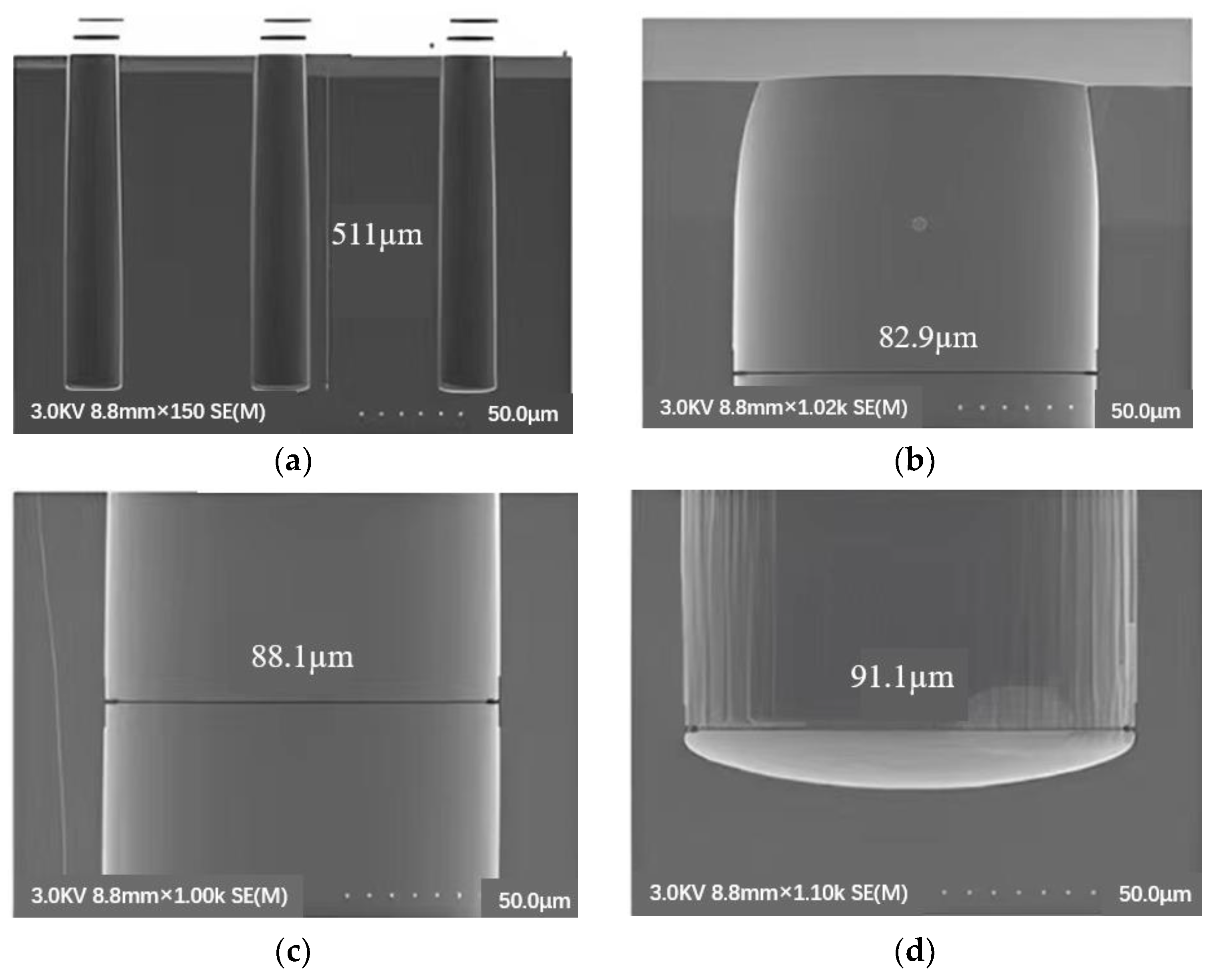

3.1.1. Optimization of the Etching Process

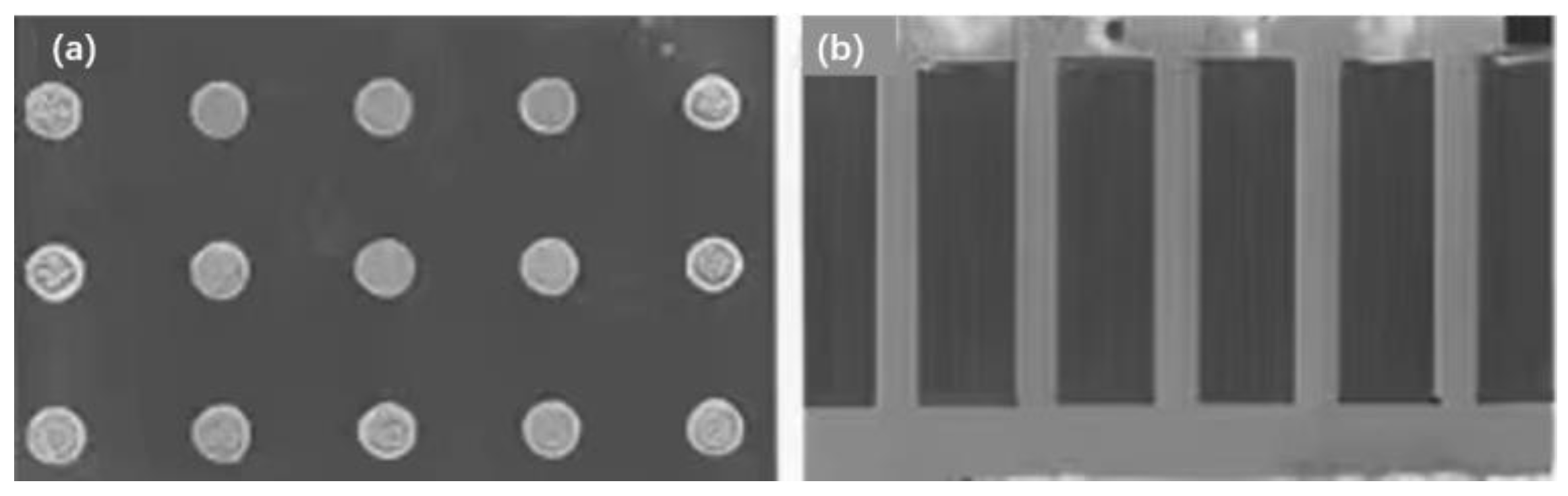

3.1.2. Optimization of Electroplating Filling Technology

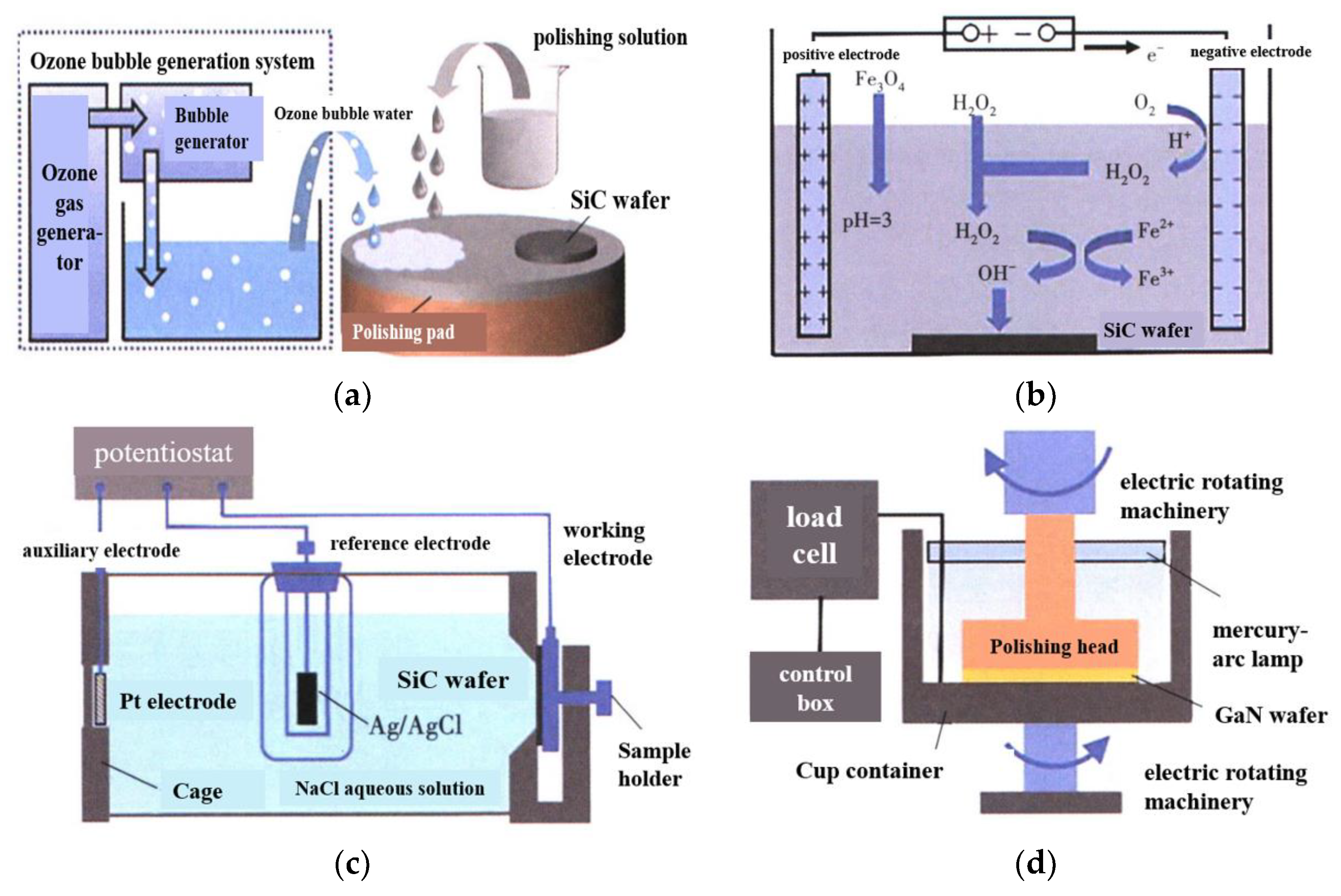

3.1.3. CMP Technology Optimization

3.2. TSV Reliability Analysis

3.2.1. Thermal Stress Analysis

3.2.2. Thermoelectric Coupling Analysis

3.2.3. Thermal Torsional Vibration Coupling Analysis

3.2.4. Analysis of Electrical Characteristics

3.3. Development of TSV Technology

- (1)

- In the future, polishing solutions for the TSV barrier layer, optimization of the polishing process, cost reduction and environmental protection will become research hotspots. With the development of the economy, science and technology in China, it is the direction for domestic researchers to gradually replace imported polishing solutions with domestic polishing solutions with the same effect;

- (2)

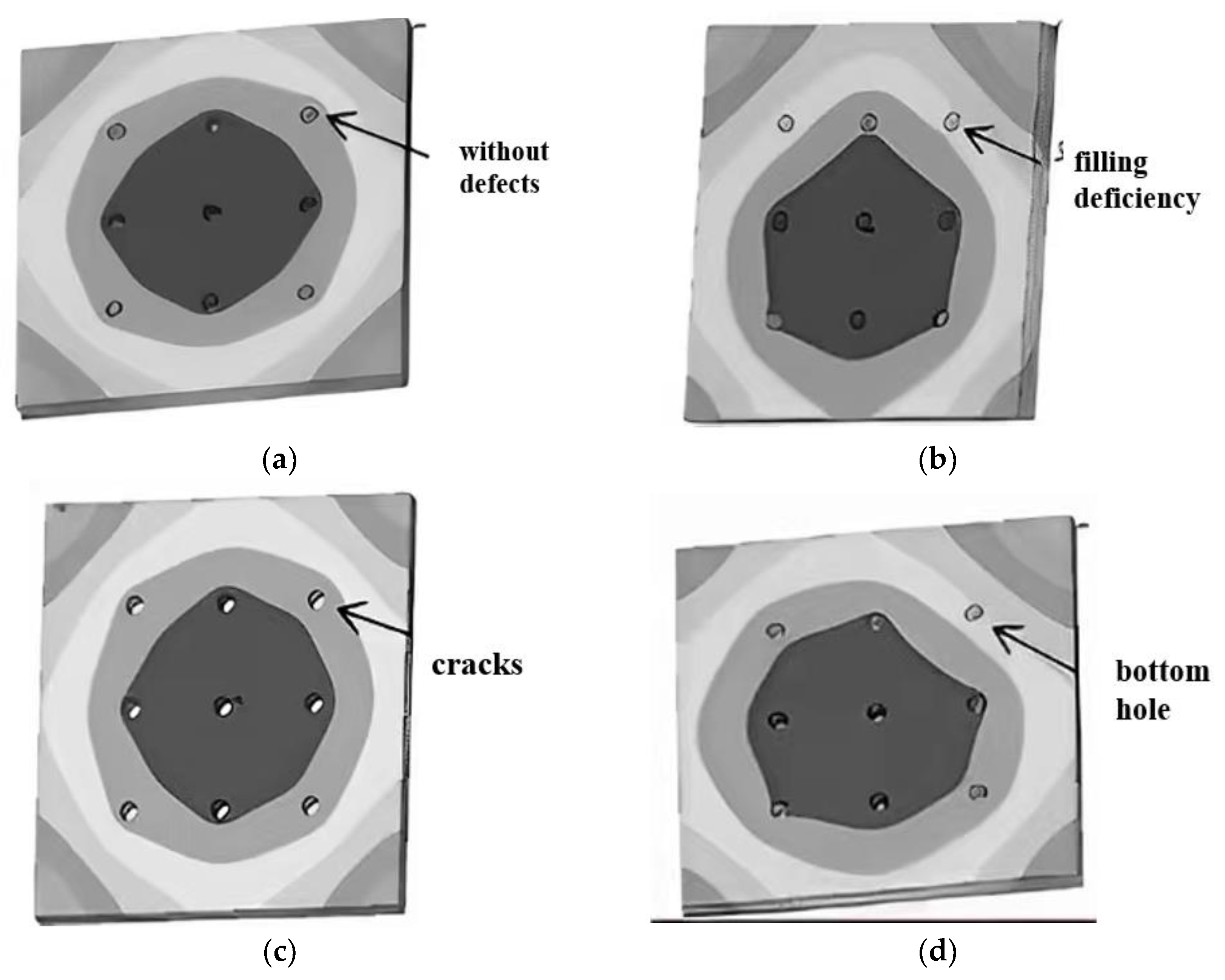

- The test architecture and repair mechanism of TSV. There will be various faults, such as interconnection disconnection, short circuits, bridges, gaps, and thermal and physical stress in the process of TSV manufacturing and superposition. The manufacturing defects of TSV lead to huge yield loss in the design process of TSV before and after combination [73]. If there is no complete testing system and TSV repair mechanism, TSV failures will continue to cause huge costs due to the dumping of bad molds. Among them, the repair mechanism provides a redundancy feature, which can replace the faulty TSV with a spare TSV in the design. Compared with the standard TSV testing method, this has a significant impact on the output. Some researchers have put forward online TSV repair technology based on chain TDMA, but it is not able to repair the cluster TSV fault, which limits its applicability. In order to achieve high-yield cluster TSV failures and cost-effective hardware overheads, a new bee–TDMATSV repair method without using RTSV has emerged, thus reducing area overheads and improving outputs. Among them, cellular-TDMA is a highly reliable repair mechanism, which allocates time slots for each TSV existing in the design and provides necessary control signals to pass a good path [74];

- (3)

- Compared with the prior achievements, the development of some new integrated circuit packaging structures and manufacturing methods can realize high-density wiring capability without forming an interlayer with the TSV; therefore, the required cost is lower;

- (4)

- Some new chip packaging structures and preparation methods of chip packaging structures realize the direct contact of the chips on both sides by directly opening staggered slots on the adapter plate. This allows for the chips on both sides to be directly electrically connected, avoiding opening TSV through holes to realize the interconnection of the chips on both sides and effectively utilizing the bearing and electrical connection functions of the adapter plate.

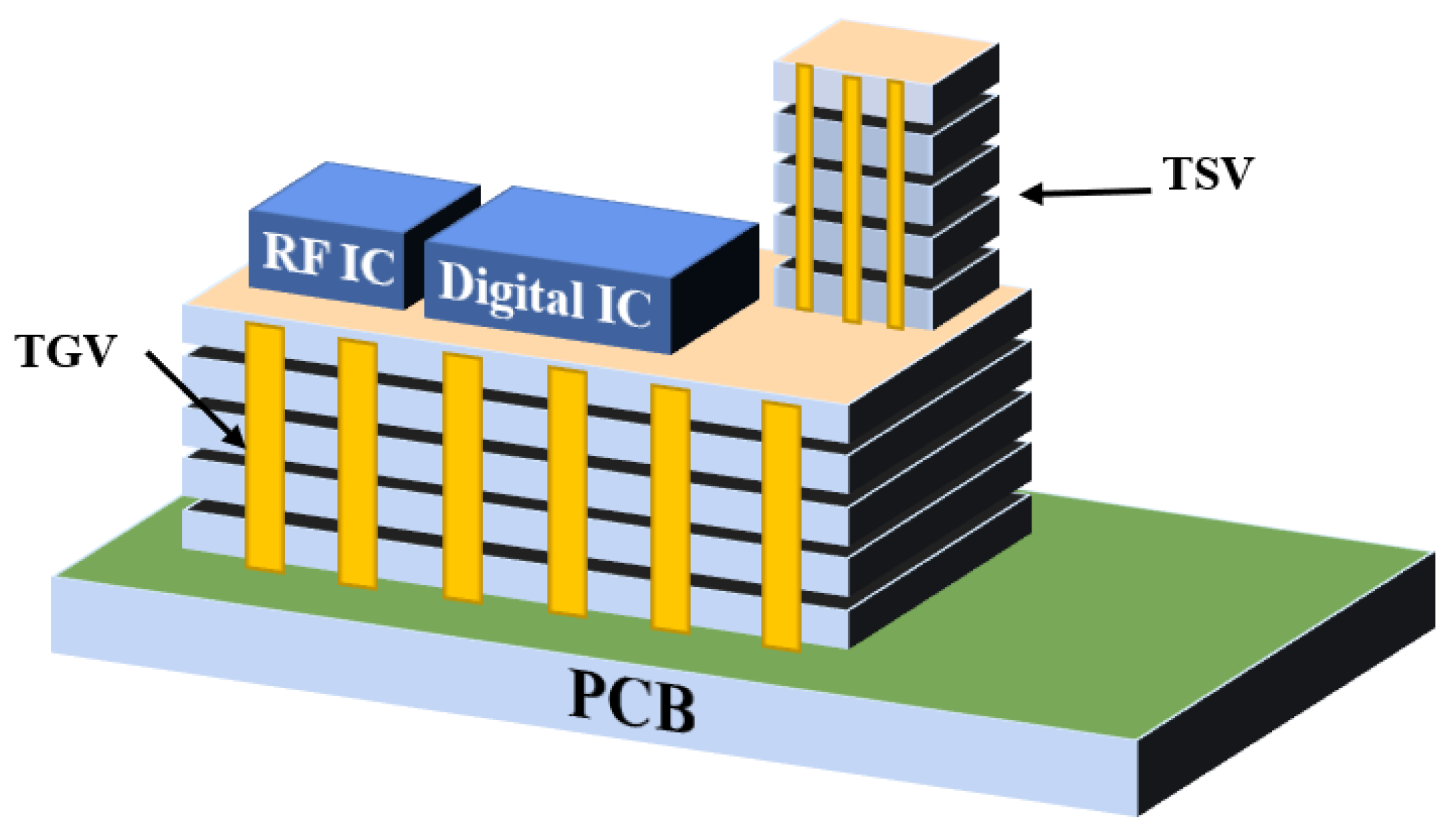

4. TCV and TGV Technology

4.1. Introduction of TCV

4.1.1. Process Flow Design

- (1)

- Slurry filling

- (2)

- Electroplating filling

4.1.2. TCV Process Optimization and Reliability

4.2. Introduction of TGV

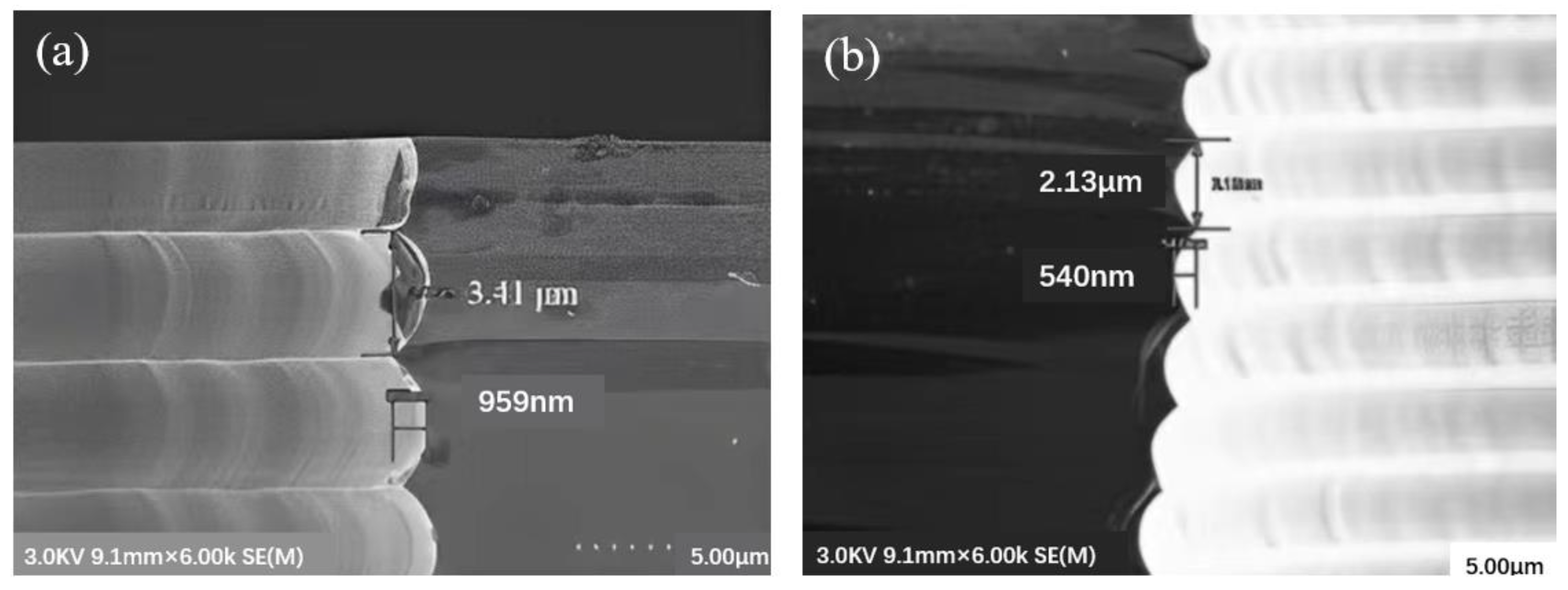

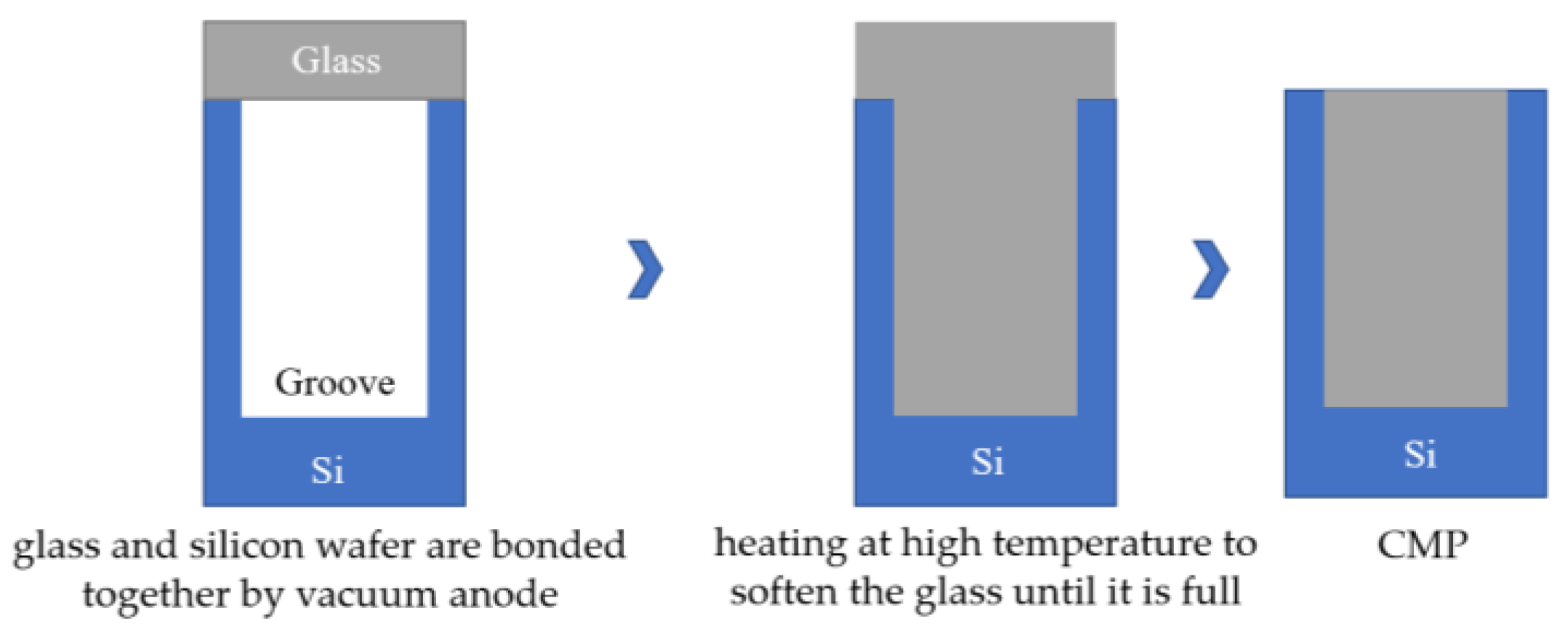

4.2.1. The TGV Process

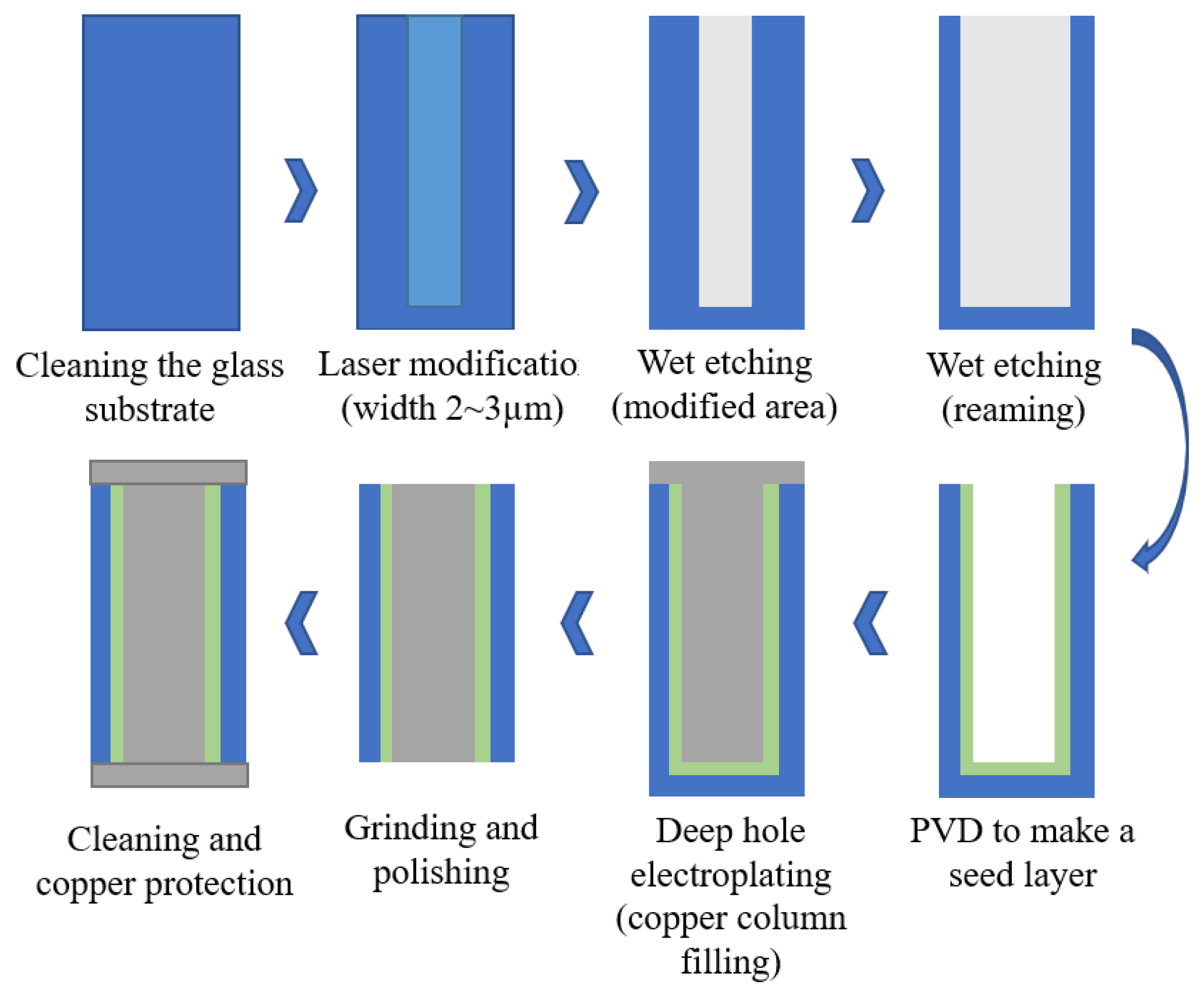

- (1)

- Selective laser modification is carried out on the clean glass substrate. The high-energy and high-power density laser focused inside the glass breaks the silicon–oxygen bond and forms a micro-activated region with a diameter of 2~3 μm on the glass substrate;

- (2)

- Then, the laser-modified substrate is wet etched by using a strong alkaline etching solution with a certain concentration. In the etching process, the uniformity of the etching solution is maintained by stirring and ultrasonic wave. The heating temperature is adjusted to control the reaction speed and the etching time accurately so as to obtain a through hole;

- (3)

- Then a seed layer with a Ti–Cu structure with good adhesion to the inner wall of the through hole and the surface of the substrate is deposited by physical vapor deposition (PVD);

- (4)

- Copper is plated on the surface of the through hole and the substrate through the deep hole electroplating process. Considering the huge difference in the thermal expansion coefficient between the glass and copper, in order to avoid the thermal mismatch between the copper column and glass substrate under high power conditions, the high temperature of the transfer plate could lead to the fracture of the transfer plate; however, through hole electroplating is carried out by a partially hollow process. The copper column in the through hole is not completely filled, leaving gaps at both ends of the copper column, which provides space for thermal expansion of the copper column under high power conditions;

- (5)

- Grinding the copper on the thinned surface with micron-sized grinding media: nano-alumina powder is used to polish and remove copper and crystal layer on the surface to ensure the smooth and clean surface of the substrate; Finally, clean the surface of the substrate and remove impurities (organic materials and polishing liquid residues attached to the surface), and use a copper protective agent to form a protective film on the upper and lower surfaces of the copper column to prevent the copper surface from oxidation.

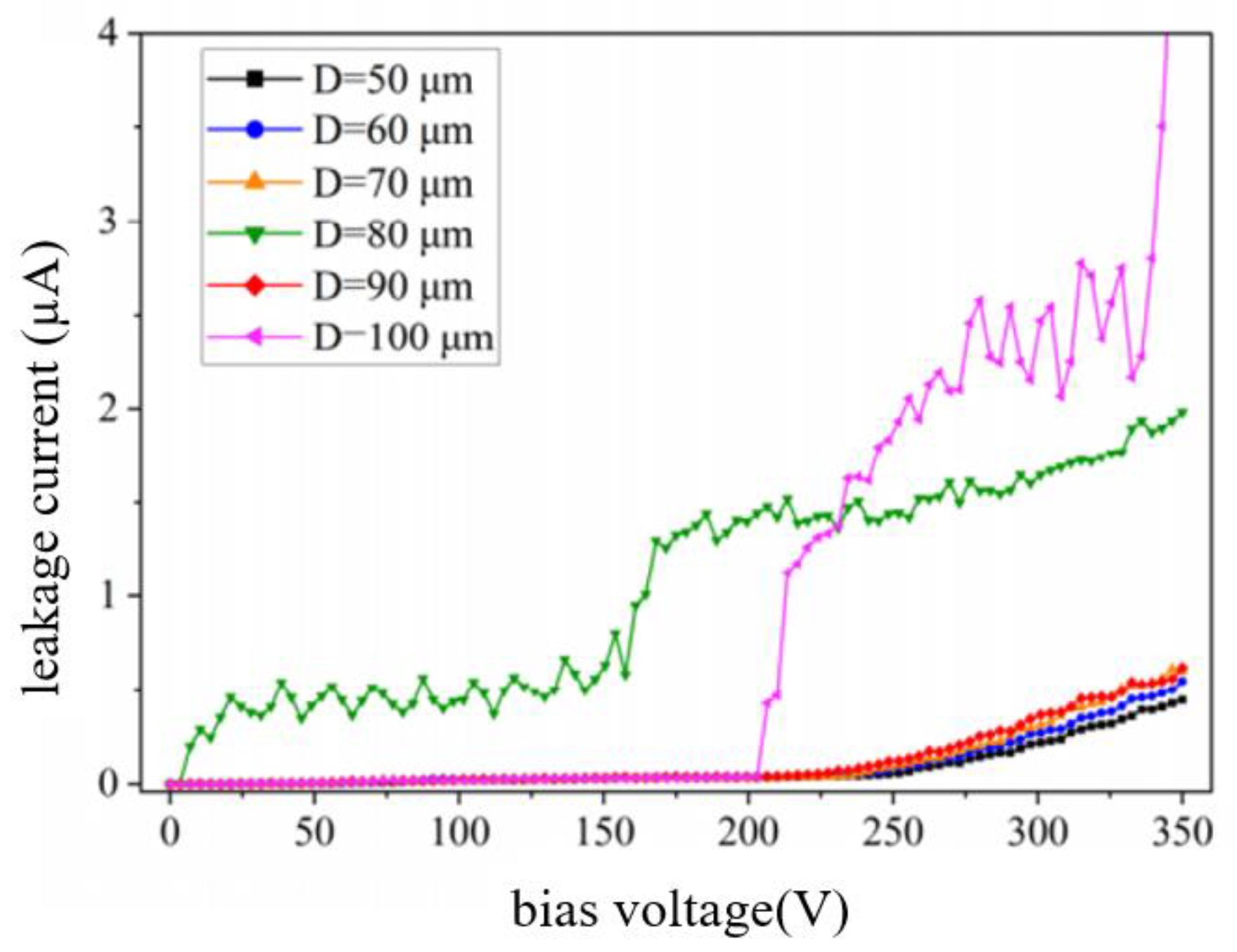

4.2.2. TGV Process Optimization

- (1)

- GISR process parameter optimization

- (2)

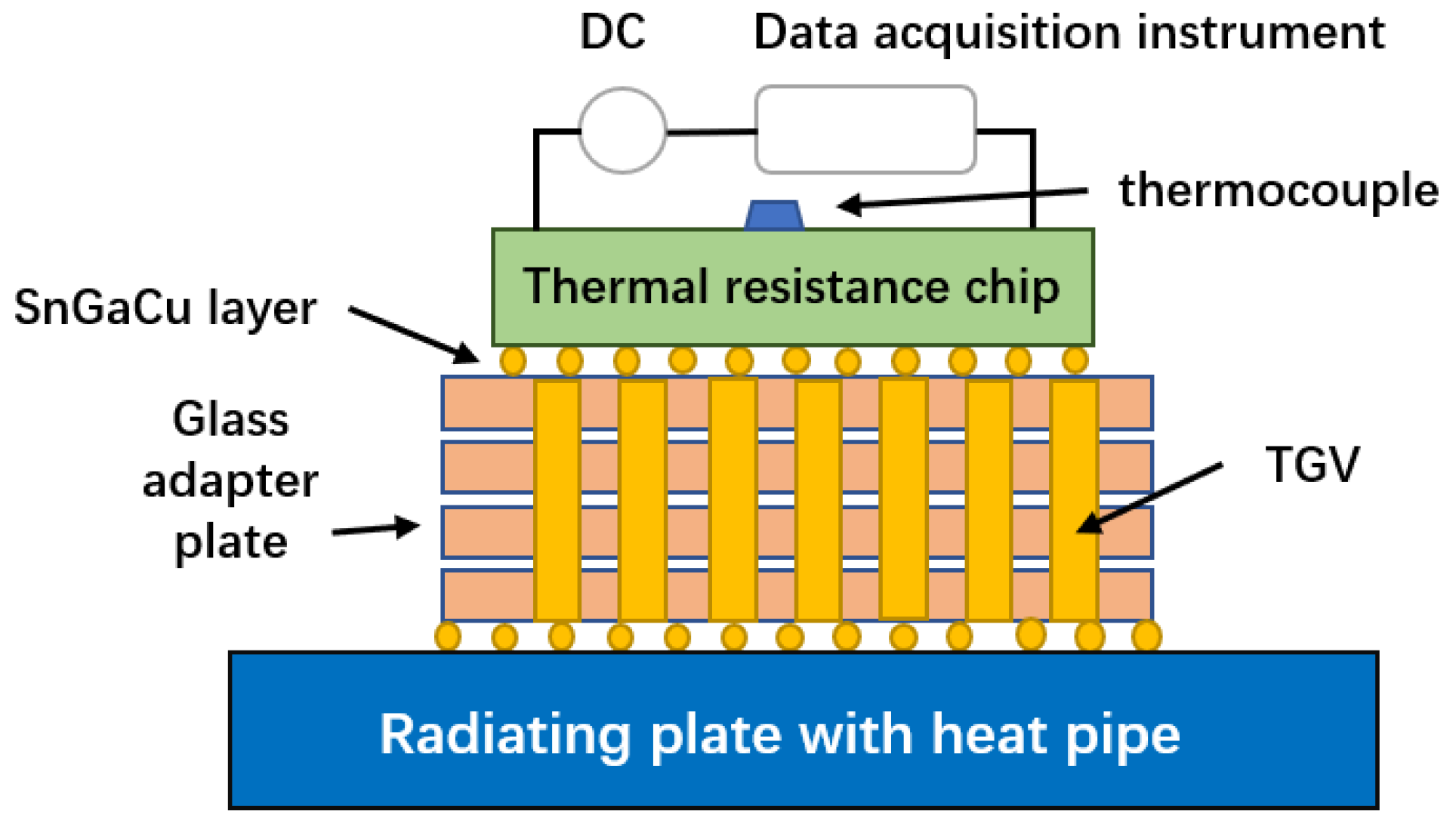

- Optimization of TGV heat dissipation structure

- (3)

- Optimization of TGV process parameters

- (4)

- Optimization of the preparation process of the TGV glass seed layer

4.2.3. Development of TGV Technology

4.3. Process Limitation

5. Summary

5.1. Process Optimization

5.1.1. Structural Problems

- -

- About TSV:

- (1)

- The problem of micro-grass on the bottom can be solved by mask technology, while the morphology problem can be optimized by shortening the etching time, prolonging passivation time, increasing bias power and increasing the C4F8 flow rate;

- (2)

- After the hole DRIE, the sidewall smoothing process, that is, thermal oxidation, using 40% potassium hydroxide at 60℃, shortening the etching time and passivation time under a one-step cycle, and replacing the through etching with the combination of blind etching and back thinning, can reduce the “scallop” size of the sidewall of the TSV hole.

- -

- About TCV:

- -

- About TGV:

5.1.2. Electroplating Filling

- -

- About TSV:

- (1)

- Electroplating is carried out in a segmented current mode, and the electro-plating effect can be ensured by adding jitter settings;

- (2)

- The bottom-up electro-plating process has improved the problem of the large stress caused by excessive edge thickness due to an uneven rate;

- (3)

- The problem of slit defects or bulge/void defects can be solved by two-step electroplating.

- -

- About TCV:

- -

- About TGV:

5.1.3. Polish

- -

- About TSV:

- (1)

- A step-by-step polishing process has the characteristics of a high removal rate, controllable polishing time, low risk of debris, low selectivity and few concave and convex defects.

- (2)

- The fine polishing of TSV can be realized by introducing the corrosion inhibitor TAZ and surfactant betaine into the glycine–H2O2 system. Adding HEDP, ozone bubbles, electro-Fenton reaction and anodic oxidation can all improve the CMP effect.

5.2. Reliability Thermal Stress Problem

5.2.1. Structural Parameter Influence

- -

- About TSV:

- -

- About TCV:

- -

- About TGV:

5.2.2. Material

- -

- About TSV:

- (1)

- The thermal stress of tungsten TSV in metal materials is the smallest;

- (2)

- Carbon nanotubes generate the least heat and can form relatively good filling materials.

- -

- About TCV:

- -

- About TGV:

5.2.3. Reduce Thermal Stress

- -

- About TSV:

- (1)

- The smaller the diameter of the TSV, the greater the temperature rise of the TSV silicon adapter plate. The smaller the spacing of TSVs, the greater the local heat flux density. In order to ensure electrical performance, we should, as far as is practical, use a TSV design scheme with a small size and wide spacing;

- (2)

- With the increase of TSV length, the Joule heat generated in TSV gradually decreases. The larger the pore size of TSV, the more obvious the influence on Joule heat, thus accelerating the failure of electromigration.

- -

- About TCV:

- -

- About TGV:

5.2.4. Reduce Capacitance

- -

- About TSV:

5.3. Contrast

- (1)

- Compared with ceramic and organic substrates, the manufacturing technology of a silicon-based adapter board has the following advantages: it has high compatibility with semiconductor technology, greatly improves the fan-out ability and realizes the requirements of high-precision technology. The thermal expansion coefficient of silicon material is highly matched to that of silicon chips; it has good mechanical stability. However, devices of the same size have more functions and better high-frequency performance in TCV technology.

- (2)

- Compared with TSV, glass material is an insulator material with a very small loss factor and excellent electrical properties, therefore, TGV technology has obvious advantages in high-frequency and high-speed applications. When TGV is filled with metal, the sidewall does not need to be oxidized and insulated, thus reducing the production cost. TGV has technical advantages in small volume and leadless packaging.

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Transactions, L.J.E. Recent Advances and New Trends in Nanotechnology and 3D Integration for Semiconductor Industry. In Proceedings of the 2011 IEEE International 3D Systems Integration Conference (3DIC), Osaka, Japan, 31 January–2 February 2012; Volume 44, pp. 1–23. [Google Scholar]

- Iyer, S.S.; Kirihata, T.J. Three-Dimensional Integration: A Tutorial for Designers. IEEE Solid-State Circuits Mag. 2015, 7, 63–74. [Google Scholar] [CrossRef]

- Tian, W.; Li, Z.; Wang, Y.; Zhang, G.J. Height uniformity simulation and experimental study of electroplating gold bump for 2.5 D/3D integrated packaging. Micromachines 2022, 13, 1537. [Google Scholar] [CrossRef] [PubMed]

- Hopkins, J.B.; Panas, R.M.; Song, Y.; White, C.D. A high-speed large-range tip-tilt-piston micromirror array. J. Microelectromech. Syst. 2016, 26, 196–205. [Google Scholar] [CrossRef]

- Tian, W.; Li, B.; Li, Z.; Cui, H.; Shi, J.; Wang, Y.; Zhao, J.J.M. Using Chiplet Encapsulation Technology to Achieve Processing-in-Memory Functions. Micromachines 2022, 13, 1790. [Google Scholar] [CrossRef] [PubMed]

- Lau, J.H. Fan-Out Wafer-Level Packaging; Springer: Berlin/Heidelberg, Germany, 2018. [Google Scholar]

- Farooq, M.G.; Iyer, S.S. 3D integration review. Sci. China Inf. Sci. 2011, 54, 1012–1025. [Google Scholar] [CrossRef]

- Cui, H.; Tian, W.; Zhang, Y.; Chen, Z.J. The Study of the Reliability of Complex Components during the Electromigration Process. Micromachines 2023, 14, 499. [Google Scholar] [CrossRef]

- Lee, S.H.; Chen, K.-N.; Lu, J.J.-Q. Wafer-to-wafer alignment for three-dimensional integration: A review. J. Microelectromech. Syst. 2011, 20, 885–898. [Google Scholar] [CrossRef]

- Wu, D.-W. The Research on Key Technologies of High-Density 2.5D TSV Interposer; Xidian University: Xi’an, China, 2021. [Google Scholar]

- Wang, M.-J.; Hung, C.-Y.; Kao, C.-L.; Lee, P.-N.; Chen, C.-H.; Hung, C.-P.; Tong, H.-M. TSV technology for 2.5 D IC solution. In Proceedings of the 2012 IEEE 62nd Electronic Components and Technology Conference, San Diego, CA, USA, 29 May–1 June 2012; pp. 284–288. [Google Scholar]

- Wang, Y.-Z.; Wang, X.-F.; Xu, M.-H.; Lv, Z.-C.; Xu, C.-L.; Hu, C.; Wang, Z.-Y.; Liu, S. Research of TSV Technology for MEMS Packaging. Micronanoelectron. Technol. 2012, 49, 62–67. [Google Scholar] [CrossRef]

- Wang, S.; Ma, K.; Yang, F.-S. A review on TSV reliability. Appl. Electron. Tech. 2021, 47, 1–6. [Google Scholar]

- Koh, W.J.A. 3D IC integration technology development in China. SMTA Proc. 2012, 8944, 6158. [Google Scholar]

- Cheng, S.-F.; Huang, P.-T.; Wang, L.-C.; Chang, M.-C.F.J. Built-in self-test/repair methodology for multiband RF-Interconnected TSV 3D integration. IEEE Des. Test 2019, 36, 63–71. [Google Scholar] [CrossRef]

- Tian, W.; Li, P.; Yuan, L.J. Research and analysis of MEMS switches in different frequency bands. Micromachines 2018, 9, 185. [Google Scholar] [CrossRef]

- Tang, J.; Sun, X.; Luo, L. A wafer-level multi-chip module process with thick photosensitive benzocyclobutene as the dielectric for microwave application. J. Micromech. Microeng. 2011, 21, 065035. [Google Scholar] [CrossRef]

- Qin, Y.-L.; Wang, C.-F.; Li, Y.-R.; Gao, Y.; Liao, A. Through Ceramic Via(TCV)Interconnection Technology. Electron. Process Technol. 2017, 38, 4. [Google Scholar] [CrossRef]

- Sukumaran, V.; Bandyopadhyay, T.; Sundaram, V.; Tummala, R. Low-cost thin glass interposers as a superior alternative to silicon and organic interposers for packaging of 3-D ICs. IEEE Trans. Compon. Packag. Manuf. Technol. 2012, 2, 1426–1433. [Google Scholar] [CrossRef]

- Sukumaran, V.; Bandyopadhyay, T.; Chen, Q.; Kumbhat, N.; Liu, F.; Pucha, R.; Sato, Y.; Watanabe, M.; Kitaoka, K.; Ono, M. Design, fabrication and characterization of low-cost glass interposers with fine-pitch through-package-vias. In Proceedings of the 2011 IEEE 61st Electronic Components and Technology Conference (ECTC), Lake Buena Vista, FL, USA, 31 May–3 June 2011; pp. 583–588. [Google Scholar]

- Kim, J.; Pak, J.S.; Cho, J.; Song, E.; Cho, J.; Kim, H.; Song, T.; Lee, J.; Lee, H.; Park, K.; et al. High-frequency scalable electrical model and analysis of a through silicon via (TSV). IEEE Trans. Compon. Packag. Manuf. Technol. 2011, 1, 181–195. [Google Scholar]

- Lau, J.H. Overview and outlook of through-silicon via (TSV) and 3D integrations. Microelectron. Int. 2011, 28, 8–22. [Google Scholar] [CrossRef]

- Cho, J.; Song, E.; Yoon, K.; Pak, J.S.; Kim, J.; Lee, W.; Song, T.; Kim, K.; Lee, J.; Lee, H.; et al. Modeling and analysis of through-silicon via (TSV) noise coupling and suppression using a guard ring. IEEE Trans. Compon. Packag. Manuf. Technol. 2011, 1, 220–233. [Google Scholar] [CrossRef]

- Song, W. Analysis of TSV Impact on MEMS Sensor Performance; Hangzhou University of Electronic Science and Technology: Hangzhou, China, 2022. [Google Scholar]

- Guo, H.; Cao, S.; Li, L.; Zhang, X. A review on the mainstream through-silicon via etching methods. Mater. Sci. Semicond. Process. 2022, 137, 106182. [Google Scholar] [CrossRef]

- Guo, M.; Chou, X.; Mu, J.; Liu, B.; Xiong, J. Fabrication of micro-trench structures with high aspect ratio based on DRIE process for MEMS device applications. Microsyst. Technol. 2013, 19, 1097–1103. [Google Scholar] [CrossRef]

- Fan, Z.; Liu, Y.; Chen, X.; Jiang, Y.; Zhang, S.; Wang, Y. Research on fatigue of TSV-Cu under thermal and vibration coupled load based on numerical analysis. Microelectron. Reliab. 2020, 106, 113590. [Google Scholar] [CrossRef]

- Sun, X.; Ji, M.; Ma, S.; Zhu, Y.; Kang, W.; Miao, M.; Jin, Y. Electrical characterization of sidewall insulation layer of TSV. In Proceedings of the 2010 11th International Conference on Electronic Packaging Technology & High Density Packaging, Xi’an, China, 16–19 August 2010; pp. 77–80. [Google Scholar]

- Ranganathan, N.; Lee, D.Y.; Youhe, L.; Lo, G.-Q.; Prasad, K.; Pey, K.L. Influence of Bosch etch process on electrical isolation of TSV structures. IEEE Trans. Compon. Packag. Manuf. Technol. 2011, 1, 1497–1507. [Google Scholar] [CrossRef]

- Motoyoshi, M. Through-silicon via (TSV). Proc. IEEE 2009, 97, 43–48. [Google Scholar] [CrossRef]

- Aithal, R.K.; Yenamandra, S.; Gunasekaran, R.; Coane, P.; Varahramyan, K. Electroless copper deposition on silicon with titanium seed layer. Mater. Chem. Phys. 2006, 98, 95–102. [Google Scholar] [CrossRef]

- Narayanan, B.; Li, C.Y.; Lee, K.; Yu, B.; Wu, J.J.; Foo, P.D.; Xie, J. IMP copper seed layer formation with TaN barrier for deep submicron. In Proceedings of the Multilevel Interconnect Technology III, Santa Clara, CA, USA, 22–23 September 1999; pp. 42–45. [Google Scholar]

- Li, Z.; Tian, Y.; Teng, C.; Cao, H. Recent advances in barrier layer of Cu interconnects. Materials 2020, 13, 5049. [Google Scholar] [CrossRef]

- Wu, H.; Wang, Y.; Li, Z.; Zhu, W. Investigations of the electrochemical performance and filling effects of additives on electroplating process of TSV. Sci. Rep. 2020, 10, 9204. [Google Scholar] [CrossRef]

- Triyoso, D.; Dao, T.; Kropewnicki, T.; Martinez, F.; Noble, R.; Hamilton, M. Progress and challenges of tungsten-filled through-silicon via. In Proceedings of the 2010 IEEE International Conference on Integrated Circuit Design and Technology, Grenoble, France, 2–4 June 2010; pp. 118–121. [Google Scholar]

- Wang, Z.; Obata, R.; Sakaue, H.; Takahagi, T.; Shingubara, S. Bottom-up copper fill with addition of mercapto alkyl carboxylic acid in electroless plating. Electrochim. Acta 2006, 51, 2442–2446. [Google Scholar] [CrossRef]

- Lee, D.; Lee, H.; Jeong, H. Slurry components in metal chemical mechanical planarization (CMP) process: A review. Int. J. Precis. Eng. Manuf. 2016, 17, 1751–1762. [Google Scholar] [CrossRef]

- Seo, Y.-J.; Lee, W.-S. Effects of oxidant additives for exact selectivity control of W-and Ti-CMP process. Microelectron. Eng. 2005, 77, 132–138. [Google Scholar] [CrossRef]

- Tsai, T.; Tsao, W.; Lin, W.; Hsu, C.; Lin, C.; Hsu, C.; Lin, J.; Huang, C.; Wu, J. CMP process development for the via-middle 3D TSV applications at 28 nm technology node. Microelectron. Eng. 2012, 92, 29–33. [Google Scholar] [CrossRef]

- Zheng, Q.; Xue, H.; Liu, F.; Cao, L.; Wang, Q.; He, H.; Dai, F.; Sun, P. Design, Manufacture and Assembly of 3D Integrated Optical Transceiver Module Based on an Active Photonic Interposer. Processes 2022, 10, 2342. [Google Scholar] [CrossRef]

- Ren, Q.; Loh, W.L.; Neo, S.K.; Chui, K.-J. Temporary bonding and de-bonding process for 2.5 D/3D applications. In Proceedings of the 2020 IEEE 22nd Electronics Packaging Technology Conference (EPTC), Singapore, 2–4 December 2020; pp. 27–31. [Google Scholar]

- Mo, Z.; Wang, F.; Li, J.; Liu, Q.; Zhang, G.; Li, W.; Yang, C.; Sun, R. Temporary Bonding and Debonding in Advanced Packaging: Recent Progress and Applications. Electronics 2023, 12, 1666. [Google Scholar] [CrossRef]

- Shi, S.; Wang, X.; Xu, C.; Yuan, J.; Fang, J.; Liu, S. Simulation and fabrication of two Cu TSV electroplating methods for wafer-level 3D integrated circuits packaging. Sens. Actuators A Phys. 2013, 203, 52–61. [Google Scholar] [CrossRef]

- Zhang, W.; Shan, G.-B.; Du, X.-R. Cu/Sn Bonding Technology for the TSV 3D Integration. Micronanoelectron. Technol. 2015, 52, 5. [Google Scholar] [CrossRef]

- Li, K.; Zhang, Q.-X.; Zhang, Y.-X.; Yang, Y.-J. Equivalent Modeling Simulation and Thermal Resistance Test for TSV Structure SiP Modules. Semicond. Technol. 2020, 45, 6. [Google Scholar] [CrossRef]

- Wang, B.; Hsieh, C.-H. Measuring the value of patents with fuzzy multiple criteria decision making: Insight into the practices of the Industrial Technology Research Institute. Technol. Forecast. Soc. Chang. 2015, 92, 263–275. [Google Scholar] [CrossRef]

- Wong, C.-Y.; Hu, M.-C.; Shiu, J.-W. Collaboration between public research institutes and universities: A study of industrial technology research institute, Taiwan. Sci. Technol. Soc. 2015, 20, 161–181. [Google Scholar] [CrossRef]

- Jacobs, K.; Li, Y.; Stucchi, M.; Wolf, I.D.; Beyne, E. Optical Beam-Based Defect Localization Methodologies for Open and Short Failures in Micrometer-Scale 3-D TSV Interconnects. IEEE Trans. Compon. Packag. Manuf. Technol. 2020, 10, 1542–1551. [Google Scholar] [CrossRef]

- Yao, M.-J. What Is the Prospect of TSV, and Which Companies or Institutions Are Currently Studying It? Available online: https://www.zhihu.com/question/40927060 (accessed on 12 January 2017).

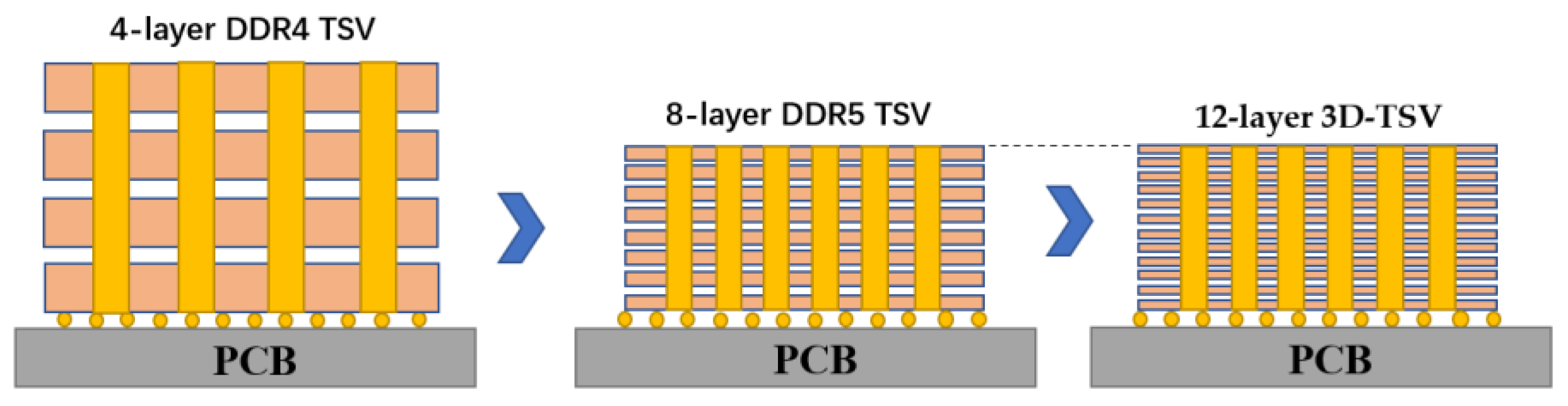

- Strike. Samsung Is Ready to Launch 512GB DDR5-7200 Memory, Which Is Packaged in 8-Layer TSV Stack. Available online: https://www.expreview.com/80143.html (accessed on 23 August 2021).

- Ni, J.-S. Samsung Announced the Industry’s First 12-Layer 3D-TSV Chip Packaging Process: To Help Meet the Needs of Large-capacity HBM. Available online: https://expreview.com/70809.html (accessed on 10 July 2019).

- Feng, L.; Zeng, S.; Su, Y.; Wang, L.; Xu, Y.; Guo, S.; Chen, S.; Ji, Y.; Peng, X.; Wu, Z. Process Optimization and Performance Evaluation of TSV Arrays for High Voltage Application. Micromachines 2022, 14, 102. [Google Scholar] [CrossRef]

- Park, J.S.; Kang, D.-H.; Kwak, S.M.; Kim, T.S.; Park, J.H.; Kim, T.G.; Baek, S.-H.; Lee, B.C. Low-temperature smoothing method of scalloped DRIE trench by post-dry etching process based on SF 6 plasma. Micro Nano Syst. Lett. 2020, 8, 14. [Google Scholar] [CrossRef]

- Frasca, S.; Leghziel, R.C.; Arabadzhiev, I.N.; Pasquier, B.; Tomassi, G.F.; Carrara, S.; Charbon, E. The Michelangelo step: Removing scalloping and tapering effects in high aspect ratio through silicon vias. Sci. Rep. 2021, 11, 3997. [Google Scholar] [CrossRef]

- Gerlt, M.S.; Läubli, N.F.; Manser, M.; Nelson, B.J.; Dual, J. Reduced etch lag and high aspect ratios by deep reactive ion etching (DRIE). Micromachines 2021, 12, 542. [Google Scholar] [CrossRef] [PubMed]

- Zhao, H.; Li, B.-X.; Fang, Y.-L.; Wang, W.-J.; Wu, W. TSV Etching Technology with Small Aperture and High Aspect Ratio Applied to Active Chip 3D Integration. Micronanoelectron. Technol. 2020, 57, 6. [Google Scholar] [CrossRef]

- Tian, M.; Luan, Z.-X.; Chen, S.-J.; Liu, M.; Wang, F.-D.; Cheng, X.-L. TSV Fabrication Method Based on Two-Step Double-Sided Filling of Through Vias. Semicond. Technol. 2022, 47. [Google Scholar] [CrossRef]

- Zhang, K.; Li, T.; Liu, X.-J.; Gao, Y.-X.; Liu, Y.-L. Application of CMP Process Optimization in TSV Technology. Equip. Electron. Prod. Manuf. 2019, 48, 5. [Google Scholar]

- Liu, X.-Y. Research on CMP Slurry for Wafers; Hebei University of Technology: Tianjin, China, 2020. [Google Scholar]

- Kwon, O.; Bae, K.; Byun, J.; Lim, T.; Kim, J.J. Study on effect of complexing agents on Co oxidation/dissolution for chemical-mechanical polishing and cleaning process. Microelectron. Eng. 2020, 227, 111308. [Google Scholar] [CrossRef]

- Hu, L.; Zhang, X.; Wang, H.; Zhang, J.; Xia, R.; Cao, J.; Pan, G. Experimental and density functional theory study of complexing agents on cobalt dissolution in alkaline solutions. Electrochim. Acta 2021, 375, 137977. [Google Scholar] [CrossRef]

- Uneda, M.; Fujii, K. Highly efficient chemical mechanical polishing method for SiC substrates using enhanced slurry containing bubbles of ozone gas. Precis. Eng. 2020, 64, 91–97. [Google Scholar] [CrossRef]

- Deng, J.; Lu, J.; Yan, Q.; Pan, J. Enhancement mechanism of chemical mechanical polishing for single-crystal 6H-SiC based on Electro-Fenton reaction. Diam. Relat. Mater. 2021, 111, 108147. [Google Scholar] [CrossRef]

- Yang, X.; Yang, X.; Kawai, K.; Arima, K.; Yamamura, K. Dominant factors and their action mechanisms on material removal rate in electrochemical mechanical polishing of 4H-SiC (0001) surface. Appl. Surf. Sci. 2021, 562, 150130. [Google Scholar] [CrossRef]

- Ou, L.W.; Wang, Y.H.; Hu, H.Q.; Zhang, L.L.; Shi, K. Photochemically combined mechanical polishing of N-type gallium nitride wafer in high efficiency. Precis. Eng. 2018, 55, 14–21. [Google Scholar] [CrossRef]

- Zhang, M.; Chen, F.; Qin, F.; Chen, S.; Dai, Y. Correlations between Microstructure and Residual Stress of Nanoscale Depth Profiles for TSV-Cu/TiW/SiO2/Si Interfaces after Different Thermal Loading. Materials 2023, 16, 449. [Google Scholar] [CrossRef]

- Xie, J. Reliability Analysis and Optimization of TSV Interconnection Structure under Combined Loading; Guilin University of Electronic Technology: Guilin, China, 2022. [Google Scholar]

- ZHang, T.; Wang, Y.; Feng, C.-L.; Zhou, Z.; Xia, J.-C.; Hu, P.-F. Multiphysics Coupling Analysis and Structural Optimization of TSVs in Microsystems. Navig. Control. 2022, 21. [Google Scholar] [CrossRef]

- Nie, L.; Jiang, C.-K.; Jia, W.; Zhong, T.-N. Influence of internal defects on temperature distribution in TSV. Electron. Compon. Mater. 2018, 37, 6. [Google Scholar] [CrossRef]

- Pak, J.; Pathak, M.; Lim, S.K.; Pan, D.Z. Modeling of electromigration in through-silicon-via based 3D IC. In Proceedings of the 2011 IEEE 61st Electronic Components and Technology Conference (ECTC), Lake Buena Vista, FL, USA, 31 May–3 June 2011; pp. 1420–1427. [Google Scholar]

- Frank, T.; Moreau, S.; Chappaz, C.; Arnaud, L.; Leduc, P.; Thuaire, A.; Anghel, L. Electromigration behavior of 3D-IC TSV interconnects. In Proceedings of the 2012 IEEE 62nd Electronic Components and Technology Conference, San Diego, CA, USA, 29 May–1 June 2012; pp. 326–330. [Google Scholar]

- Ma, R.; Su, M.-Y.; Liu, X.-F.; Wang, X.-G.; Cao, L.-Q. Finite element analysis of factors affecting TSV electromigration. Electron. Compon. Mater. 2019, 38, 5. [Google Scholar] [CrossRef]

- Vethamuthu Edward Alaises, R.S.; Sathasivam, S. Novel BIST Solution to Test the TSV Interconnects in 3D Stacked IC’s. Electronics 2023, 12, 908. [Google Scholar] [CrossRef]

- Ni, T.; Xu, Q.; Huang, Z.; Liang, H.; Yan, A.; Wen, X. A Cost-Effective TSV Repair Architecture for Clustered Faults in 3-D IC. IEEE Trans. Comput. Des. Integr. Circuits Syst. 2020, 40, 1952–1956. [Google Scholar] [CrossRef]

- Gong, T.; Qin, F.; Yan, X.; Gao, L.; Yang, Y.; Lei, Z.; Tan, H.; Li, J. Thermo-mechanical optimization of ceramic substrate with through ceramic vias by Taguchi-Grey method. Microelectron. Reliab. 2022, 132, 114535. [Google Scholar] [CrossRef]

- Takahashi, K.; Sekiguchi, M. Through Silicon Via and 3-D Wafer/Chip Stacking Technology. In Proceedings of the 2006 Symposium on VLSI Circuits, Honolulu, HI, USA, 15–17 June 2006. [Google Scholar]

- Yang, J.-P.; Zhou, J.; Shne, G.-C.; Wu, J.; Shen, Y.; Cai, M. RF Characterization of TSV Vertical Transition Structure. Res. Prog. Solid State Electron. 2016, 5. [Google Scholar]

- Wang, Q.; Cheng, T.; Chen, F.; Cheng, M. Study on direct current Cu electroplating in through ceramic holes for high-power LED packaging. In Proceedings of the 2020 21st International Conference on Electronic Packaging Technology (ICEPT), Guangzhou, China, 12–15 August 2020; pp. 1–5. [Google Scholar]

- Topper, M.; Ndip, I.; Erxleben, R.; Brusberg, L.; Reichl, H. 3-D Thin film interposer based on TGV (Through Glass Vias): An alternative to Si-interposer. In Proceedings of the 2010 Proceedings 60th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 1–4 June 2010. [Google Scholar]

- Chen, Y.-Z. Research of On-Chip Inductor Based on TGV Technology; University of Electronic Science and Technology of China: Chengdu, China, 2022. [Google Scholar]

- Hu, Q.-J.; Zhou, J.; Li, W.-Y.; Hou, Z.-Q.; Xiao, D.-B.; Wu, X.-Z. Modeling of glass-reflow facing TGV substrate. Transducer Microsyst. Technol. 2017, 36, 4. [Google Scholar] [CrossRef]

- Wang, W.-Q.; Guo, Y.-H.; Liu, J.-J.; Wang, Y.-L. High Heat Dissipation Performance of the TGV Interposer. Micronanoelectron. Technol. 2021, 58, 7. [Google Scholar] [CrossRef]

- Du, X.-H.; Liu, S.; Zhu, M.-J. Reflow Technology of Nano-Glass Powder for TGV Packaging. Micronanoelectron. Technol. 2020, 57, 6. [Google Scholar] [CrossRef]

- Okoro, C.; Jayaraman, S.; Pollard, S. Understanding and eliminating thermo-mechanically induced radial cracks in fully metallized through-glass via (TGV) substrates. Microelectron. Reliab. 2021, 120, 114092. [Google Scholar] [CrossRef]

- Zhao, J.; Chen, Z.; Qin, F.; Yu, D. Thermo-Mechanical Reliability Study of Through Glass Vias in 3D Interconnection. Micromachines 2022, 13, 1799. [Google Scholar] [CrossRef] [PubMed]

- Chen, Y.; Zhang, J.; Gao, L.; Zou, S.; Liang, K.; Liu, Z.; Fang, Z.; Chen, H.; Ye, Q. An optimized NiP seed layer coating method for through glass via (TGV). Microelectron. Eng. 2022, 257, 111735. [Google Scholar] [CrossRef]

| Current Density (A/m2) | Current (A) | Time (s) | |

|---|---|---|---|

| The first paragraph | 0 | 0 | 300 |

| The second paragraph | 0.08 | 0.24 | 120 |

| The third paragraph | 0.16 | 0.48 | 7200 |

| The Fourth paragraph | 0.18 | 0.54 | 1800 |

| Other conditions | Vacuum pretreatment: −90 KPa; Vibration frequency: 20 Hz | ||

| Silicon via Filling Material | Deposition Thickness/nm | Planarization Rate/(nm·min−1) | Disc Depression/nm |

|---|---|---|---|

| copper | 500∼60,000 | 100∼8000 | 1~300 |

| polysilicon | 400∼3000 | 200∼1500 | 30~120 |

| wolfram | 300∼900 | 300∼800 | 15~30 |

| platinum | 1500∼5000 | 150∼500 | 10~80 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Tian, W.; Wu, S.; Li, W. Research of Vertical via Based on Silicon, Ceramic and Glass. Micromachines 2023, 14, 1391. https://doi.org/10.3390/mi14071391

Tian W, Wu S, Li W. Research of Vertical via Based on Silicon, Ceramic and Glass. Micromachines. 2023; 14(7):1391. https://doi.org/10.3390/mi14071391

Chicago/Turabian StyleTian, Wenchao, Sixian Wu, and Wenhua Li. 2023. "Research of Vertical via Based on Silicon, Ceramic and Glass" Micromachines 14, no. 7: 1391. https://doi.org/10.3390/mi14071391

APA StyleTian, W., Wu, S., & Li, W. (2023). Research of Vertical via Based on Silicon, Ceramic and Glass. Micromachines, 14(7), 1391. https://doi.org/10.3390/mi14071391