A SiC Planar MOSFET with an Embedded MOS-Channel Diode to Improve Reverse Conduction and Switching

Abstract

:1. Introduction

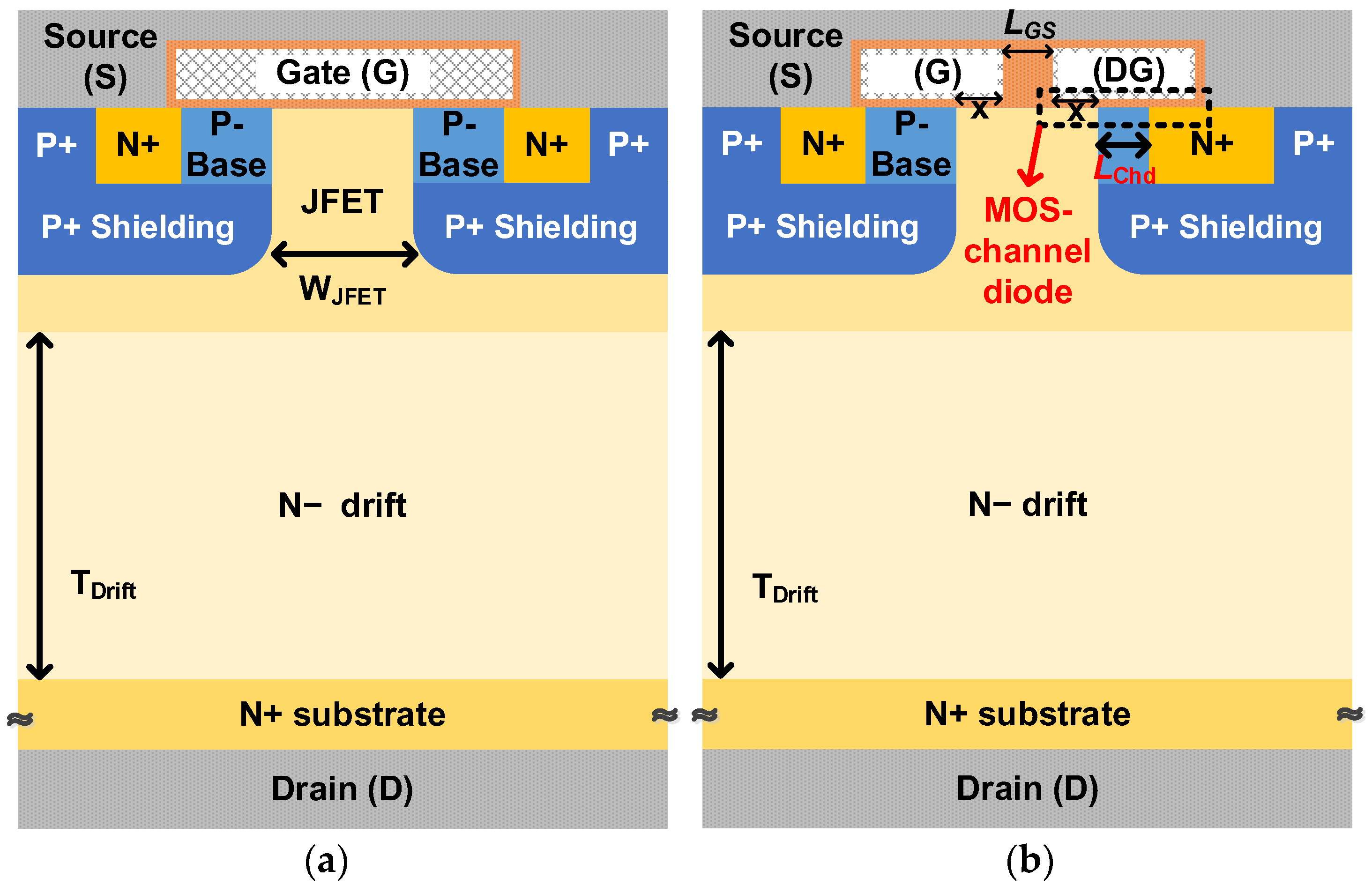

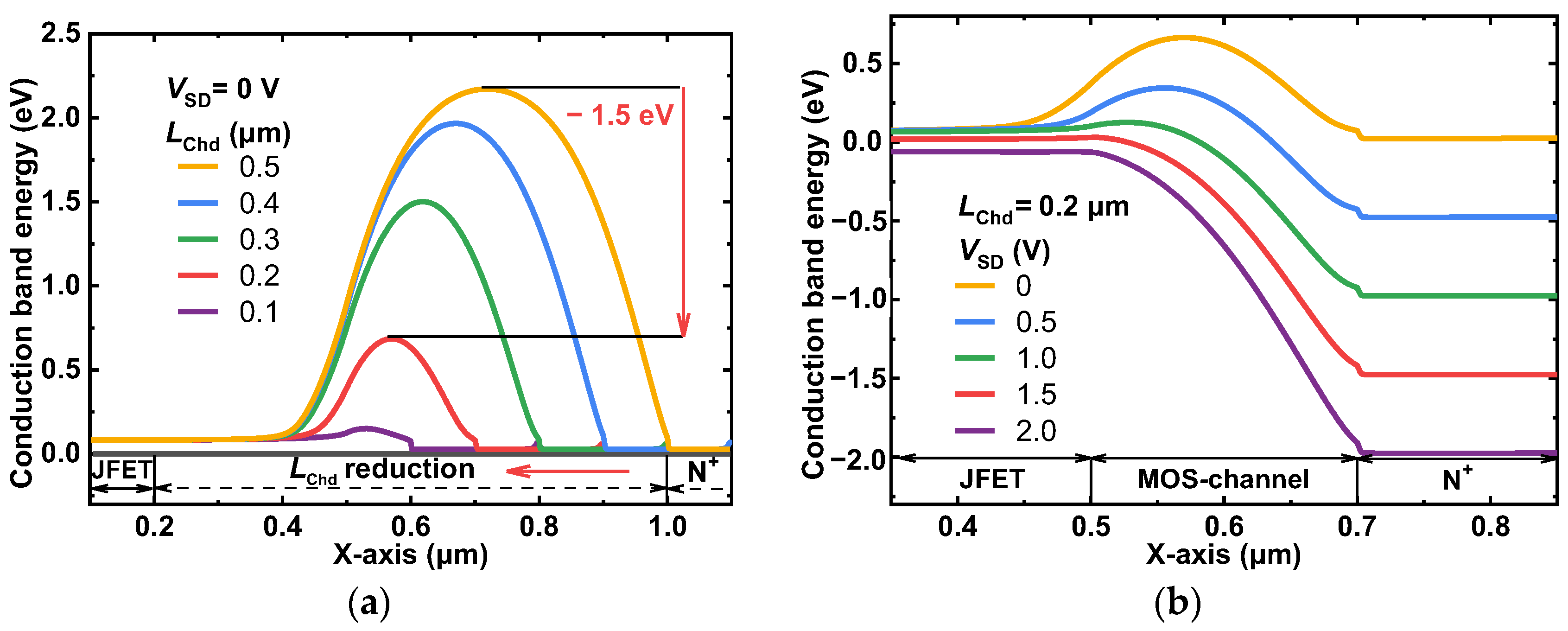

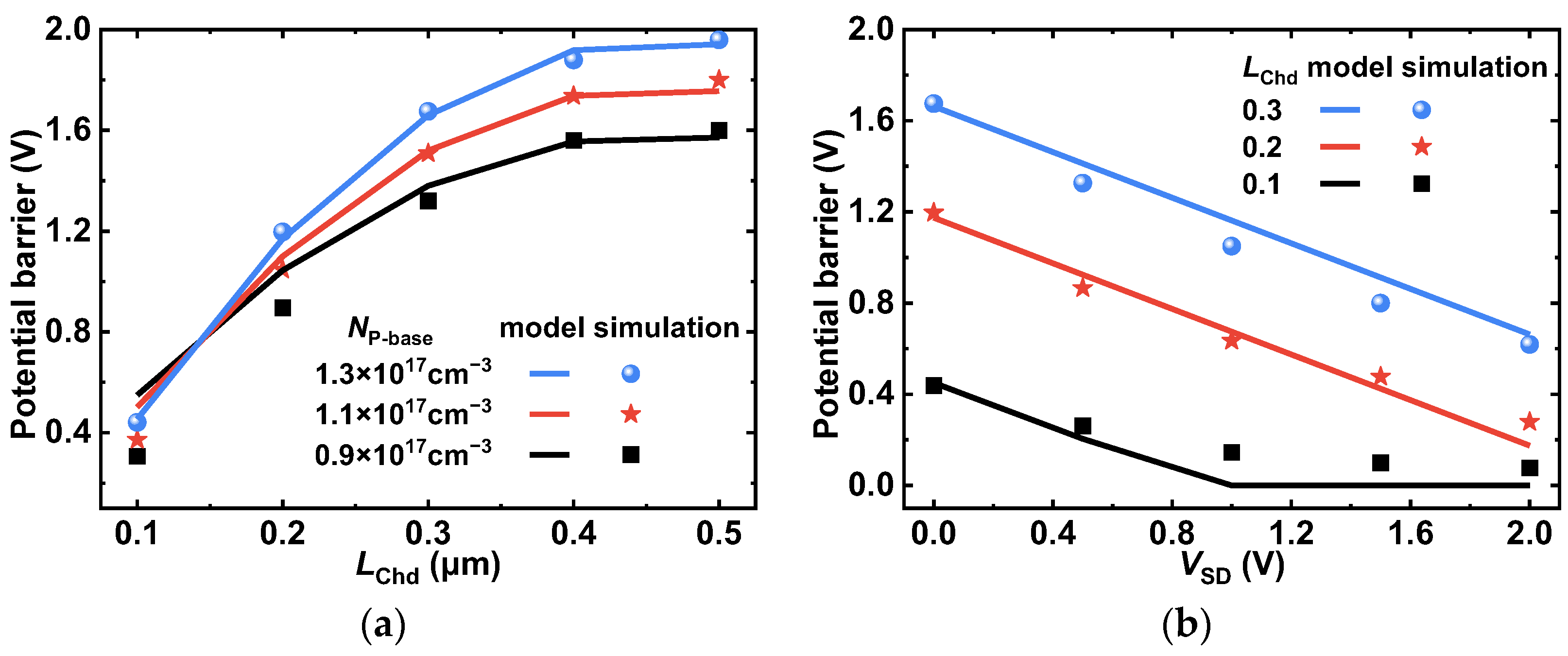

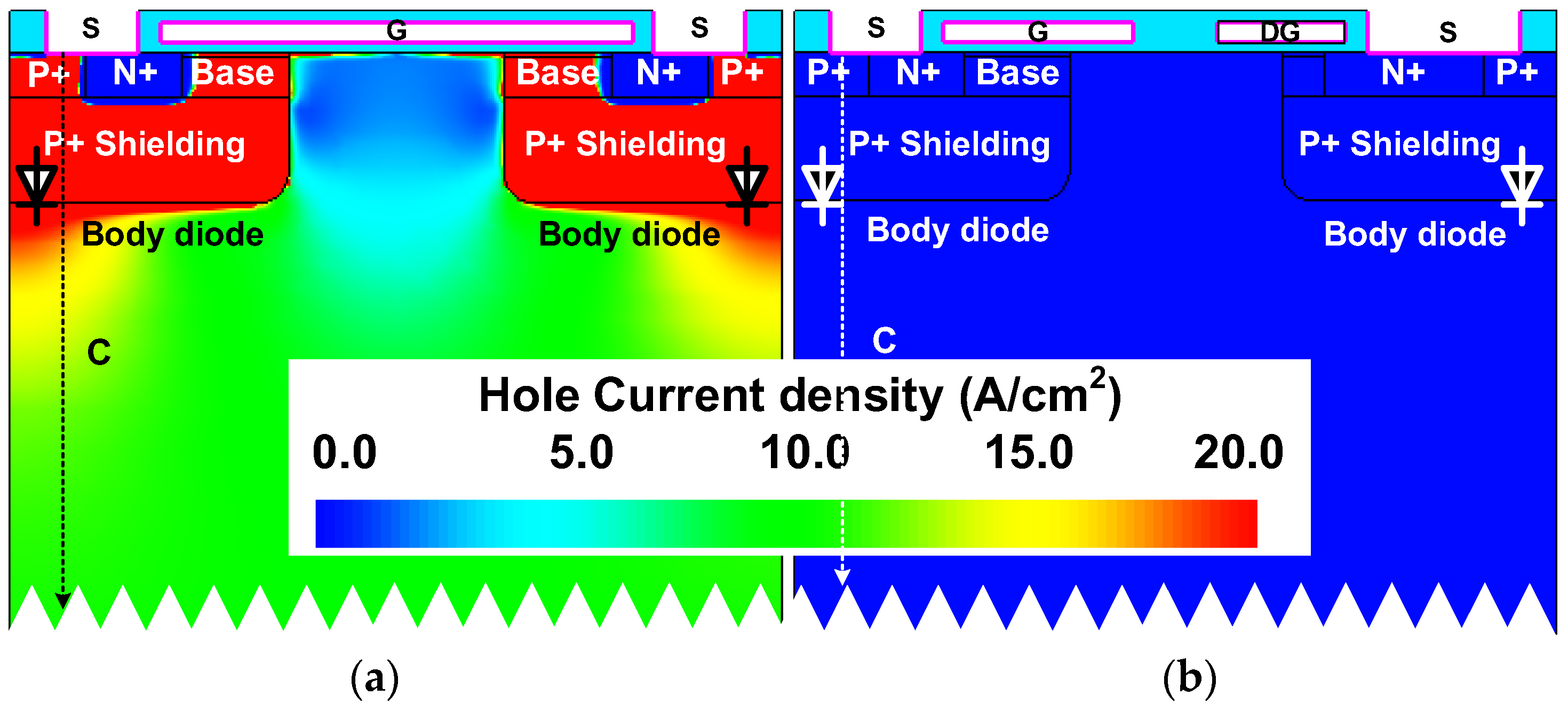

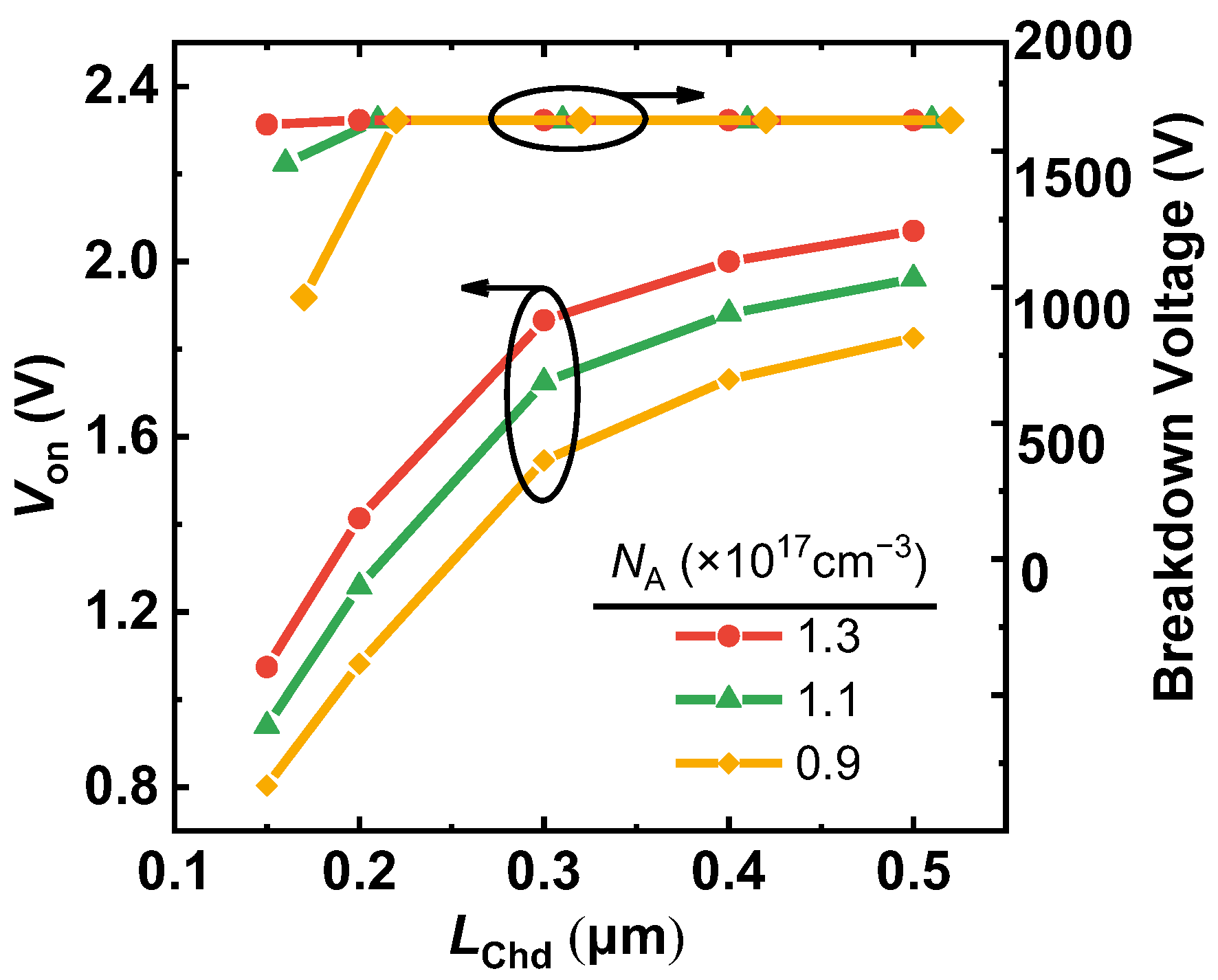

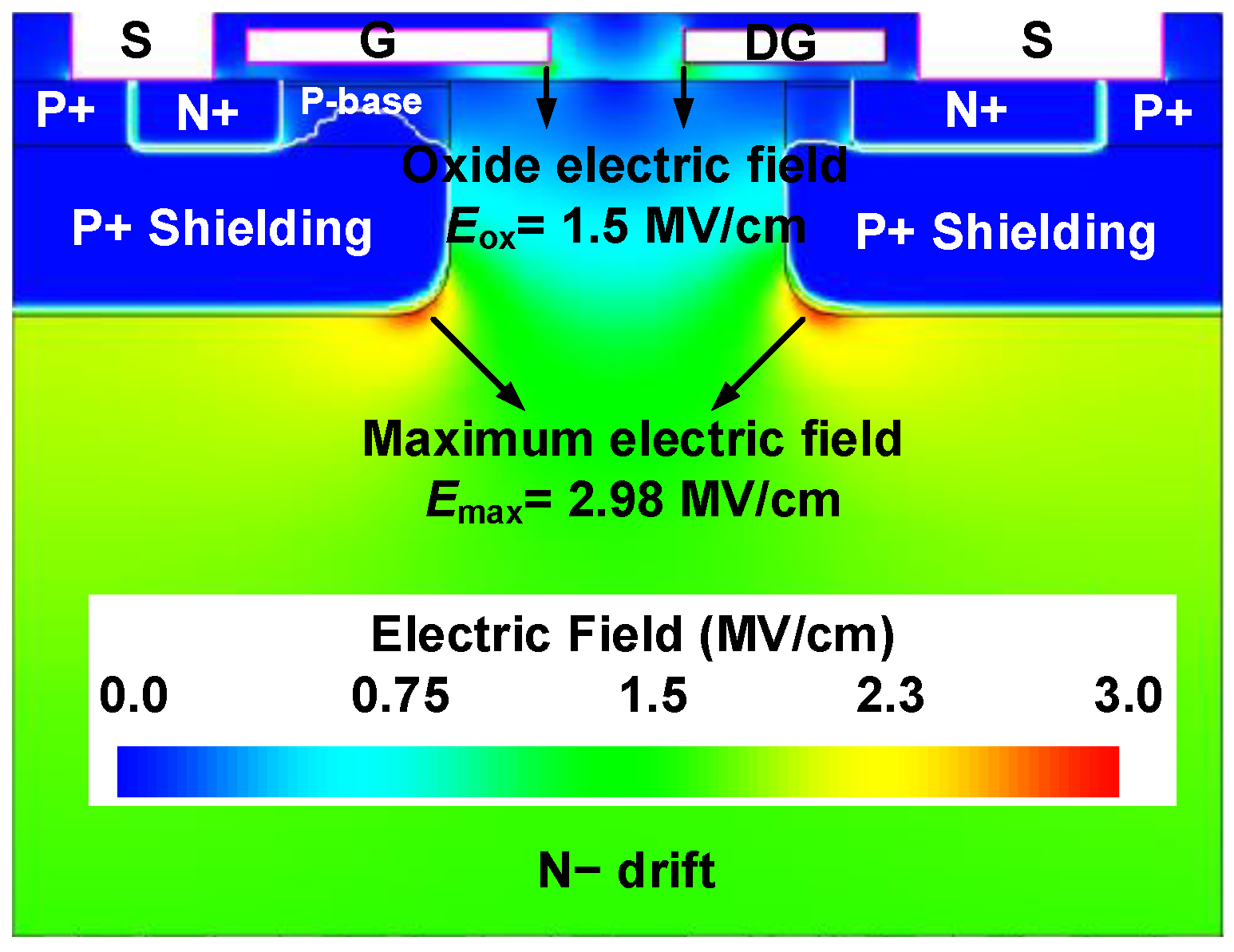

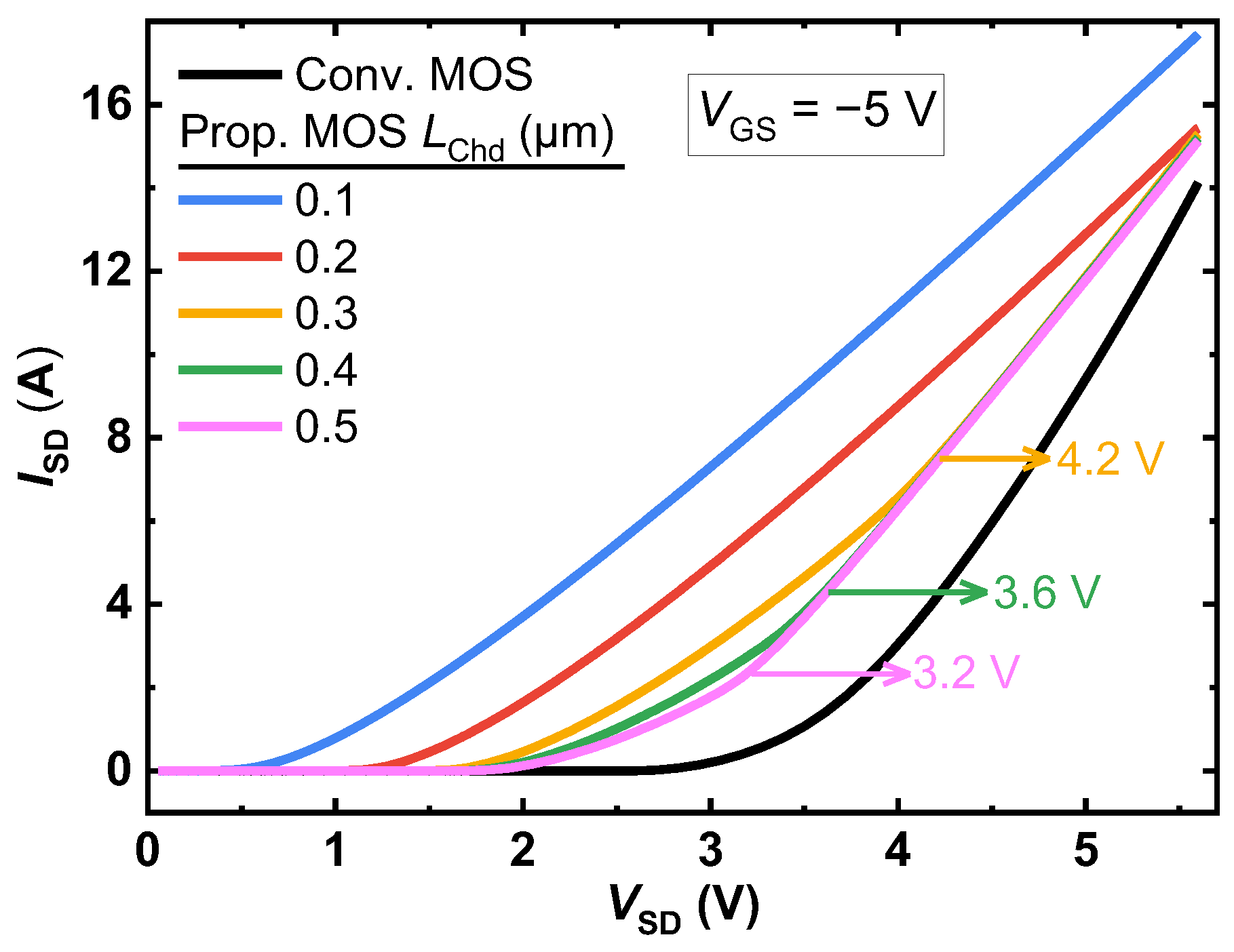

2. Device Structure and Mechanism

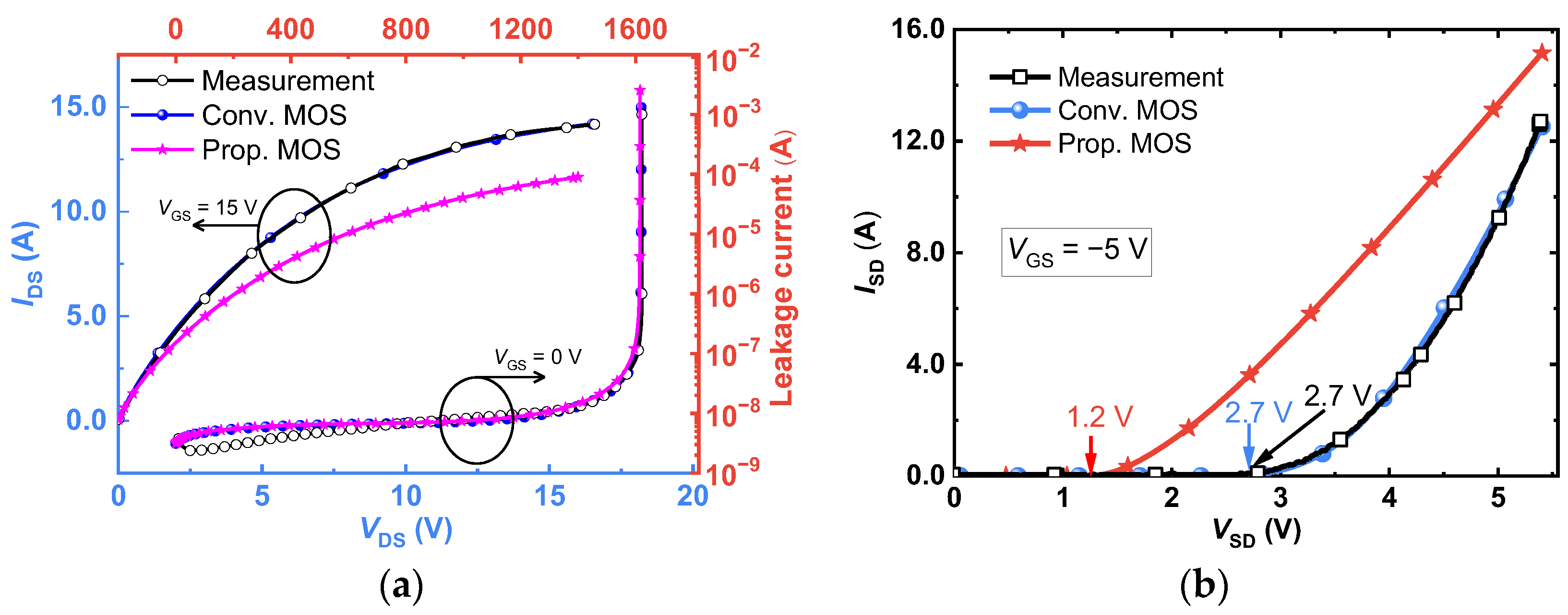

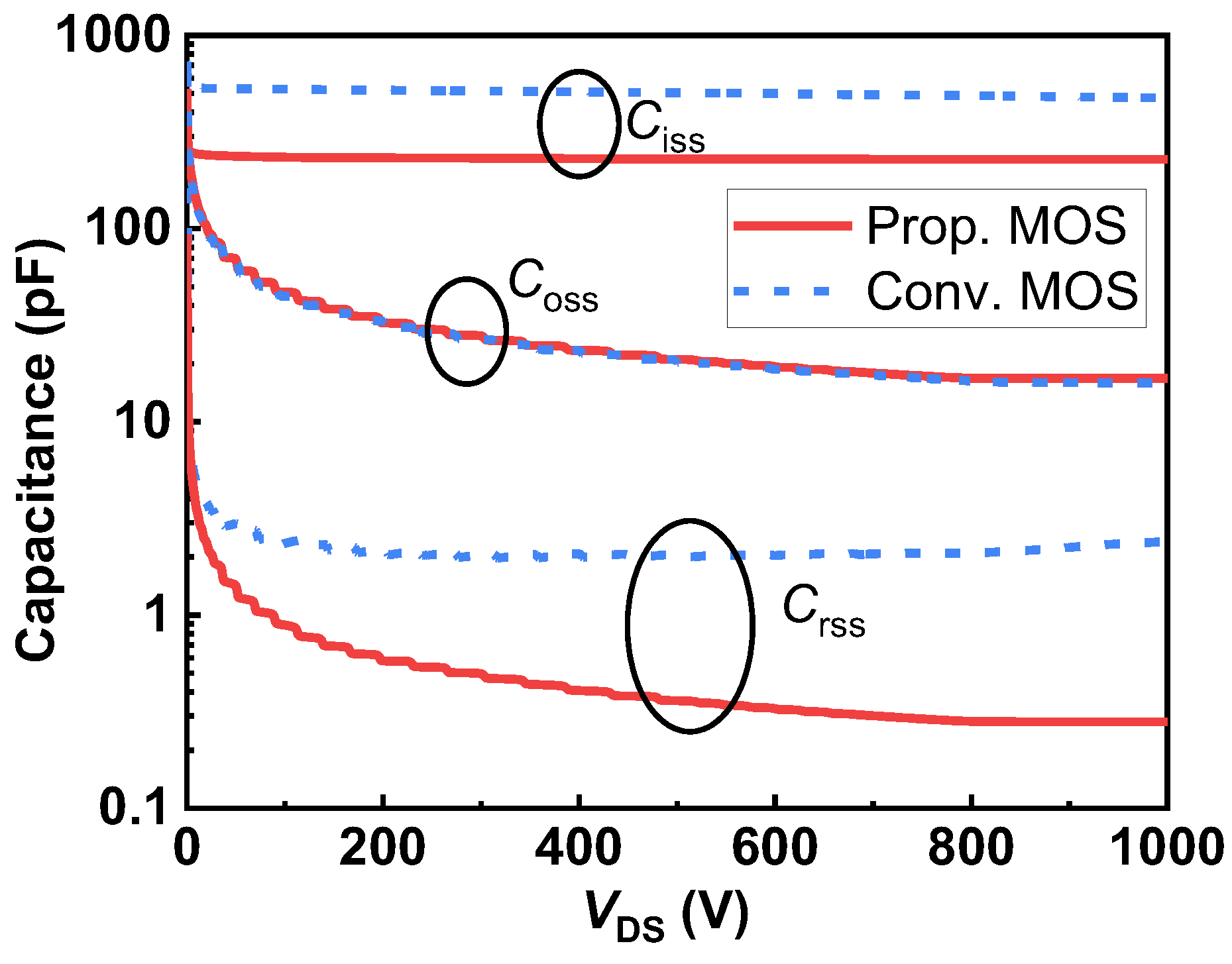

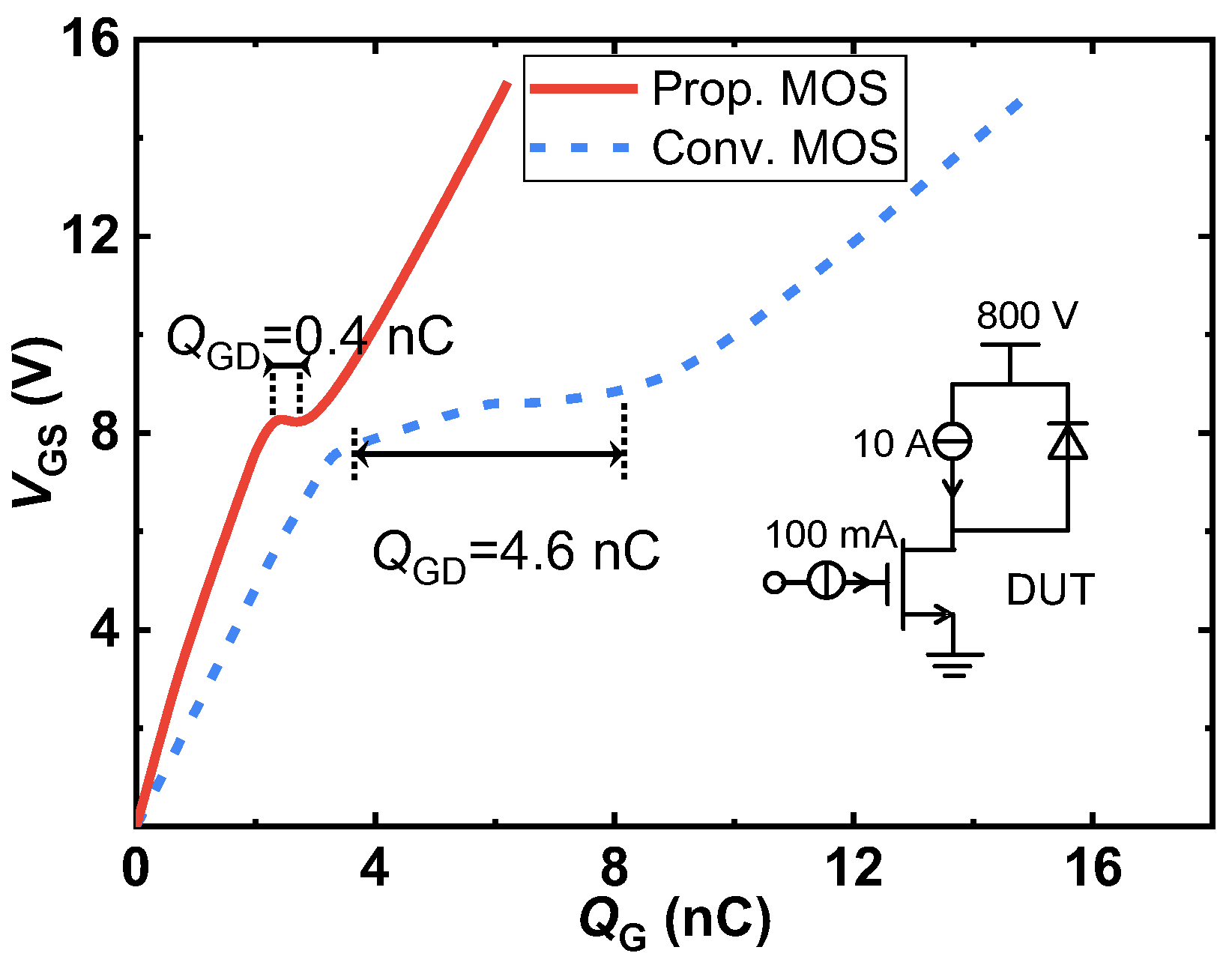

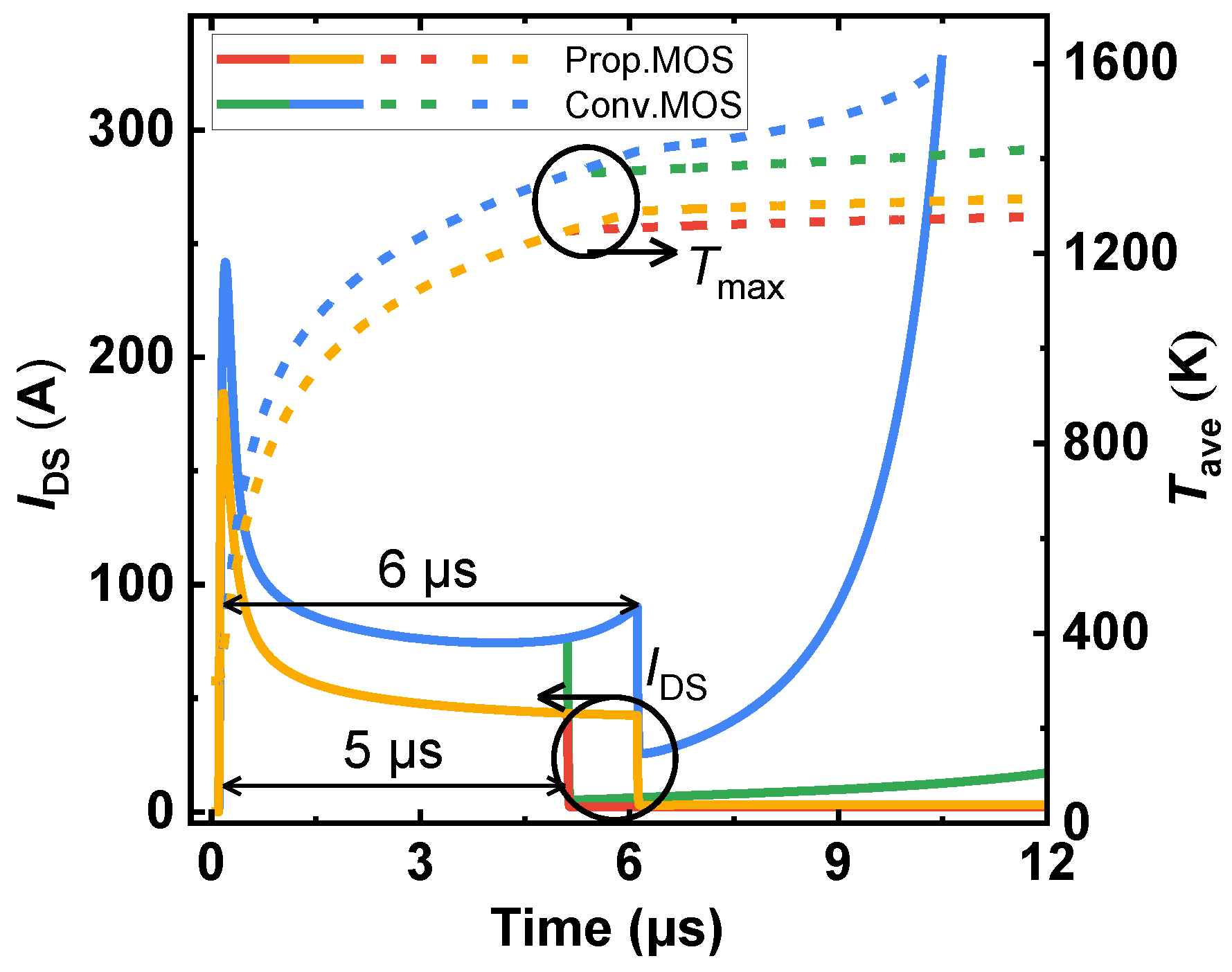

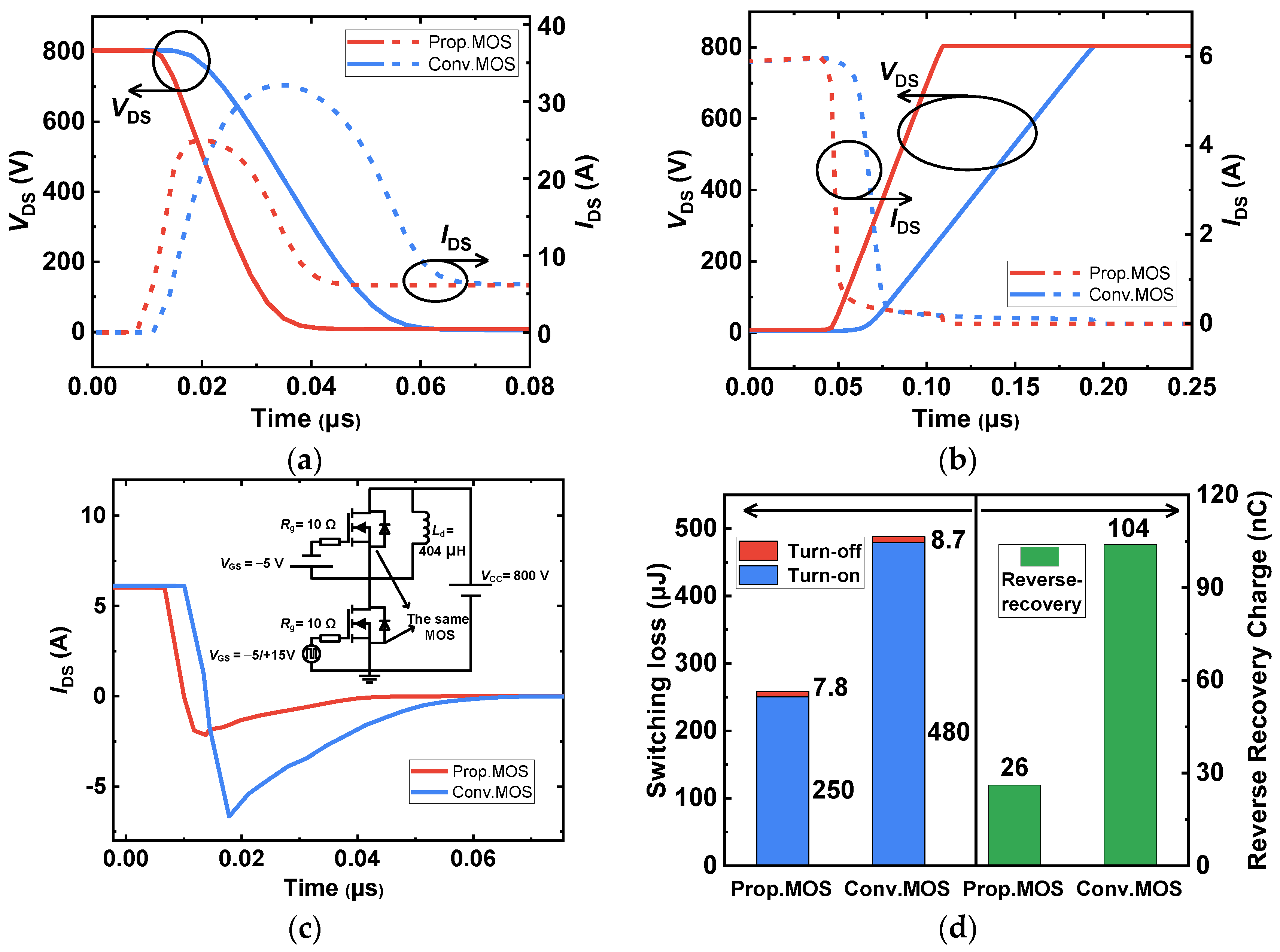

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Millan, J.; Godignon, P.; Perpina, X.; Perez-Tomas, A.; Rebollo, J. A Survey of Wide Bandgap Power Semiconductor Devices. IEEE Trans. Power Electron. 2014, 29, 2155–2163. [Google Scholar] [CrossRef]

- Agarwal, A.; Kanale, A.; Baliga, B.J. Advanced 650 V SiC Power MOSFETs with 10 V Gate Drive Compatible with Si Superjunction Devices. IEEE Trans. Power Electron. 2021, 36, 3335–3345. [Google Scholar] [CrossRef]

- Yin, S.; Liu, Y.; Liu, Y.; Tseng, K.J.; Pou, J.; Simanjorang, R. Comparison of SiC Voltage Source Inverters Using Synchronous Rectification and Freewheeling Diode. IEEE Trans. Ind. Electron. 2018, 65, 1051–1061. [Google Scholar] [CrossRef]

- Yamaguchi, K.; Katsura, K.; Yamada, T.; Sato, Y. Criteria for Using Antiparallel SiC SBDs With SiC MOSFETs for SiC-Based Inverters. IEEE Trans. Power Electron. 2020, 35, 619–629. [Google Scholar] [CrossRef]

- Zhang, M.; Wei, J.; Zhou, X.D.; Jiang, H.P.; Li, B.K.; Chen, K.J. Simulation Study of a Power MOSFET With Built-in Channel Diode for Enhanced Reverse Recovery Performance. IEEE Electron Device Lett. 2019, 40, 79–82. [Google Scholar] [CrossRef]

- Zhang, R.; Lin, X.; Liu, J.; Mocevic, S.; Dong, D.; Zhang, Y. Third Quadrant Conduction Loss of 1.2-10 kV SiC MOSFETs: Impact of Gate Bias Control. IEEE Trans. Power Electron. 2021, 36, 2033–2043. [Google Scholar] [CrossRef]

- Tang, L.; Jiang, H.; Zhong, X.; Qiu, G.; Mao, H.; Jiang, X.; Qi, X.; Du, C.; Peng, Q.; Liu, L.; et al. Investigation Into the Third Quadrant Characteristics of Silicon Carbide MOSFET. IEEE Trans. Power Electron. 2023, 38, 1155–1165. [Google Scholar] [CrossRef]

- Agarwal, A.; Fatima, H.; Haney, S.; Ryu, S.H. A New Degradation Mechanism in High-Voltage SiC Power MOSFETs. IEEE Electron Device Lett. 2007, 28, 587–589. [Google Scholar] [CrossRef]

- Fujita, R.; Tani, K.; Konishi, K.; Shima, A. Failure of Switching Operation of SiC-MOSFETs and Effects of Stacking Faults on Safe Operation Area. IEEE Trans. Electron Devices 2018, 65, 4448–4454. [Google Scholar] [CrossRef]

- Ishigaki, T.; Hayakawa, S.; Murata, T.; Masuda, T.; Oda, T.; Takayanagi, Y. Diode-Less SiC Power Module With Countermeasures Against Bipolar Degradation to Achieve Ultrahigh Power Density. IEEE Trans. Electron Devices 2020, 67, 2035–2043. [Google Scholar] [CrossRef]

- Pal, A.; Pilli, N.K.; Klumpner, C.; Ahmed, M.R. Improved Switching Performance of 3.3kV SiC MOSFETs using Synchronous Rectification in A Voltage Source Inverter. In Proceedings of the 2022 IEEE Applied Power Electronics Conference and Exposition (APEC), Houston, TX, USA, 20–24 March 2022; pp. 1–6. [Google Scholar]

- Hussein, A.; Mouawad, B.; Castellazzi, A. Dynamic Performance Analysis of a 3.3 kV SiC MOSFET Half-Bridge Module with Parallel Chips and Body-Diode Freewheeling. In Proceedings of the 2018 IEEE 30th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Chicago, IL, USA, 13–17 May 2018; pp. 463–466. [Google Scholar]

- Kumar, A.; Bhattacharya, S.; Baliga, J. Influence of the Inverter Dead-time on the Reverse Recovery Characteristics of 3.3-kV SiC MOSFETs and JBSFETs. In Proceedings of the 2022 IEEE Energy Conversion Congress and Exposition (ECCE), Detroit, MI, USA, 9–13 October 2022; pp. 1–7. [Google Scholar]

- Li, X.; Li, X.; Liu, P.K.; Guo, S.X.; Zhan, L.Q.; Huang, A.Q.; Deng, X.C.; Zhang, B. Achieving Zero Switching Loss in Silicon Carbide MOSFET. IEEE Trans. Power Electron. 2019, 34, 12193–12199. [Google Scholar] [CrossRef]

- Baliga, B.J. Wide Bandgap Semiconductor Power Devices: Materials, Physics, Design, and Applications; Woodhead Publishing: Cambridge, UK, 2018. [Google Scholar]

- Sung, W.; Baliga, B.J. On Developing One-Chip Integration of 1.2 kV SiC MOSFET and JBS Diode (JBSFET). IEEE Trans. Ind. Electron. 2017, 64, 8206–8212. [Google Scholar] [CrossRef]

- Kawahara, K.; Hino, S.; Sadamatsu, K.; Nakao, Y.; Yamashiro, Y.; Yamamoto, Y.; Iwamatsu, T.; Nakata, S.; Tomohisa, S.; Yamakawa, S. 6.5 kV Schottky-Barrier-Diode-Embedded SiC-MOSFET for Compact Full-Unipolar Module. In Proceedings of the 2017 29th International Symposium on Power Semiconductor Devices and IC’s (ISPSD), Sapporo, Japan, 28 May–1 June 2017; pp. 41–44. [Google Scholar]

- Hsu, F.; Yen, C.; Hung, C.; Hung, H.; Lee, C.; Lee, L.; Huang, Y.; Chen, T.; Chuang, P. High Efficiency High Reliability SiC MOSFET with Monolithically Integrated Schottky Rectifier. In Proceedings of the 2017 29th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Sapporo, Japan, 28 May–1 June 2017; pp. 45–48. [Google Scholar]

- Aiba, R.; Okawa, M.; Kanamori, T.; Yano, H.; Iwamuro, N.; Kobayashi, Y.; Harada, S. Experimental Demonstration on Superior Switching Characteristics of 1.2 kV SiC SWITCH-MOS. In Proceedings of the 2019 31st International Symposium on Power Semiconductor Devices and ICs (ISPSD), Shanghai, China, 19–23 May 2019; pp. 23–26. [Google Scholar]

- Bödeker, C.; Vogt, T.; Silber, D.; Kaminski, N. Criterion for the Stability Against Thermal Runaway During Blocking Operation and Its Application to SiC Diodes. IEEE J. Emerg. Sel. Top. Power Electron. 2016, 4, 970–977. [Google Scholar] [CrossRef]

- Uchida, M.; Horikawa, N.; Tanaka, K.; Takahashi, K.; Kiyosawa, T.; Hayashi, M.; Niwayama, M.; Kusumoto, O.; Adachi, K.; Kudou, C.; et al. Novel SiC Power MOSFET with Integrated Unipolar Internal Inverse MOS-Channel Diode. In Proceedings of the 2011 International Electron Devices Meeting, Washington, DC, USA, 5–7 December 2011; pp. 26.6.1–26.6.4. [Google Scholar]

- Ohoka, A.; Uchida, M.; Kiyosawa, T.; Horikawa, N.; Saitou, K.; Kanzawa, Y.; Sorada, H.; Sawada, K.; Ueda, T. Reduction of RonA Retaining High Threshold Voltage in SiC DioMOS by Improved Channel Design. In Proceedings of the 2018 IEEE 30th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Chicago, IL, USA, 13–17 May 2018; pp. 52–55. [Google Scholar]

- Zhou, X.T.; Pang, H.Y.; Jia, Y.P.; Hu, D.Q.; Wu, Y.; Tang, Y.; Xia, T.; Gong, H.; Zhao, Y.F. SiC Double-Trench MOSFETs With Embedded MOS-Channel Diode. IEEE Trans. Electron Devices 2020, 67, 582–587. [Google Scholar] [CrossRef]

- Deng, X.C.; Xu, X.J.; Li, X.; Li, X.; Wen, Y.; Chen, W.J. A Novel SiC MOSFET Embedding Low Barrier Diode With Enhanced Third Quadrant and Switching Performance. IEEE Electron Device Lett. 2020, 41, 1472–1475. [Google Scholar] [CrossRef]

- Ding, J.W.; Deng, X.C.; Li, S.J.; Wu, H.; Li, X.; Li, X.; Chen, W.J.; Zhang, B. A Low-Loss Diode Integrated SiC Trench MOSFET for Improving Switching Performance. IEEE Trans. Electron Devices 2022, 69, 6249–6254. [Google Scholar] [CrossRef]

- Han, K.; Baliga, B.J. Comprehensive Physics of Third Quadrant Characteristics for Accumulation- and Inversion-Channel 1.2-kV 4H-SiC MOSFETs. IEEE Trans. Electron Devices 2019, 66, 3923–3928. [Google Scholar] [CrossRef]

- Kim, D.; Yun, N.; Jang, S.Y.; Morgan, A.J.; Sung, W. Channel Design Optimization for 1.2-kV 4H-SiC MOSFET Achieving Inherent Unipolar Diode 3(rd) Quadrant Operation. IEEE J. Electron Devices Soc. 2022, 10, 495–503. [Google Scholar] [CrossRef]

- Han, K.; Baliga, B.J. Operation of 1.2-kV 4H-SiC Accumulation and Inversion Channel Split-Gate (SG) MOSFETs at Elevated Temperatures. IEEE Trans. Electron Devices 2018, 65, 3333–3338. [Google Scholar] [CrossRef]

- TCAD Sentaurus Device Manual. 2016. Available online: https://www.synopsys.com/zh-cn/silicon/tcad/device-simulation/sentaurus-device.html (accessed on 10 June 2018).

- Han, K.; Baliga, B.J.; Sung, W. Split-Gate 1.2-kV 4H-SiC MOSFET: Analysis and Experimental Validation. IEEE Electron Device Lett. 2017, 38, 1437–1440. [Google Scholar] [CrossRef]

- Vudumula, P.; Kotamraju, S. Design and Optimization of 1.2-kV SiC Planar Inversion MOSFET Using Split Dummy Gate Concept for High-Frequency Applications. IEEE Trans. Electron Devices 2019, 66, 5266–5271. [Google Scholar] [CrossRef]

- Zhang, J.; Chen, Z.; Tu, Y.; Deng, X.; Zhang, B. A Novel SiC Asymmetric Cell Trench MOSFET With Split Gate and Integrated JBS Diode. IEEE J. Electron Devices Soc. 2021, 9, 713–721. [Google Scholar] [CrossRef]

- Han, K.; Baliga, B.J. Analysis and Experimental Quantification of 1.2-kV 4H-SiC Split-Gate Octagonal MOSFET. IEEE Electron Device Lett. 2019, 40, 1163–1166. [Google Scholar] [CrossRef]

- CREE/WOLFSPEED. C2M0280120D Datasheets. 2021. Available online: https://www.wolfspeed.com/products/power/sic-mosfets/1200v-silicon-carbide-mosfets/ (accessed on 1 February 2021).

- Romano, G.; Fayyaz, A.; Riccio, M.; Maresca, L.; Breglio, G.; Castellazzi, A.; Irace, A. A Comprehensive Study of Short-Circuit Ruggedness of Silicon Carbide Power MOSFETs. IEEE J. Emerg. Sel. Top. Power Electron. 2016, 4, 978–987. [Google Scholar] [CrossRef]

- Yu, H.Y.; Wang, J.; Deng, G.Q.; Liang, S.W.; Liu, H.Z.; Shen, Z.J. A Novel 4H-SiC JBS-Integrated MOSFET With Self-Pinching Structure for Improved Short-Circuit Capability. IEEE Trans. Electron Devices 2022, 69, 5104–5109. [Google Scholar] [CrossRef]

| Device Parameters | Unit | Conv. MOS | Prop. MOS |

|---|---|---|---|

| Gate poly-Si width | μm | 1.9 | 0.9 |

| Source poly-Si width | μm | - | 0.5 |

| Gate/Source gap width (LGS) | μm | - | 0.4 |

| P-base depth | μm | 0.2 | 0.2 |

| P-base doping concentration | cm−3 | 1.1 × 1017 | 1.1 × 1017 |

| JFET region width (WJFET) | μm | 1.0 | 1.0 |

| JFET region thickness | μm | 1.0 | 1.0 |

| P+ shielding region depth | μm | 0.5 | 0.5 |

| P+ shielding doping concentration | cm−3 | 5.0 × 1018 | 5.0 × 1018 |

| Cell pitch | μm | 3.6 | 3.6 |

| Conditions | Prop. MOS | Conv. MOS | Unit | |

|---|---|---|---|---|

| Von | VGS = −5 V, ISD = 0.1 A | 1.2 | 2.7 | V |

| BV | IDS = 1 μA | 1612 | 1618 | V |

| Ron,sp | VGS = 15 V, IDS = 6 A | 13.3 | 10.2 | mΩ·cm2 |

| CGD,sp | VDS = 800 V, f = 1 MHz | 14 | 105 | pF/cm2 |

| QG,sp | VDS = 800 V, IDS = 10 A | 310 | 755 | nC/cm2 |

| QGD,sp | VDS = 800 V, IDS = 10 A | 20 | 230 | nC/cm2 |

| Qrr,sp | VDS = 800 V, IDS = 6 A | 1.3 | 5.2 | μC/cm2 |

| ESW | VDS = 800 V, IDS = 6 A | 12.9 | 24.4 | mJ/cm2 |

| Ron × CGD | - | 186.2 | 1068.9 | mΩ·pF |

| Ron × QGD | - | 266 | 2341.4 | mΩ·nC |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Li, P.; Guo, J.; Hu, S.; Lin, Z. A SiC Planar MOSFET with an Embedded MOS-Channel Diode to Improve Reverse Conduction and Switching. Micromachines 2023, 14, 1282. https://doi.org/10.3390/mi14071282

Li P, Guo J, Hu S, Lin Z. A SiC Planar MOSFET with an Embedded MOS-Channel Diode to Improve Reverse Conduction and Switching. Micromachines. 2023; 14(7):1282. https://doi.org/10.3390/mi14071282

Chicago/Turabian StyleLi, Ping, Jingwei Guo, Shengdong Hu, and Zhi Lin. 2023. "A SiC Planar MOSFET with an Embedded MOS-Channel Diode to Improve Reverse Conduction and Switching" Micromachines 14, no. 7: 1282. https://doi.org/10.3390/mi14071282

APA StyleLi, P., Guo, J., Hu, S., & Lin, Z. (2023). A SiC Planar MOSFET with an Embedded MOS-Channel Diode to Improve Reverse Conduction and Switching. Micromachines, 14(7), 1282. https://doi.org/10.3390/mi14071282