Abstract

Three-input logic primitives show high efficiency in logic synthesis compared to traditional two-input logic, which encourages researchers to implement three-input logic gates with emerging nanotechnologies. This paper demonstrates a compact implementation of three-input monotone logic gates based on the inverted T-shaped TFET. Firstly, based on the gate coupling mechanism in the novel inverted T channel, the BTBT current can be suppressed in the vertical or horizontal region to achieve the channel strobe. Therefore, the typical three-input monotone logic functions, Majority, OrAnd, and AndOr, are successfully implemented on a single transistor. Then, a simplified potential model describing gate coupling is established to describe the impact of key device parameters on the logic behavior. Combined with TCAD simulation, the design rules of devices with different logic functions are given. Finally, a series of three-input monotonic logic gates are designed and verified. The results show that the use of the proposed TFETs can effectively save the number of transistors in the three-input logic gate, which indicates that the three-input TFET is a compact and flexible candidate for three-input logic gates.

1. Introduction

The beyond CMOS transistors with sub-60 mV/dec subthreshold swing SS for ultralow power applications are exploring alternatives, such as tunneling FET, negative capacitance FET and impact ionization FET [1,2,3,4]. Tunneling field-effect transistors (TFETs) with band-to-band tunneling (BTBT) as the main transmission mechanism can achieve a steeper SS. Because its manufacturing process is compatible with standard CMOS process platforms, it is considered one of the best candidates for next-generation logic devices [3,4]. Although silicon-based TFETs are confronted with problems such as weak driving capability and the parasitic bipolar effects, it is also actively studied and used to implement the logic gate with interesting characteristics [5,6,7,8,9,10,11,12,13,14]. Referring to [5,6], a set of hybrid TFET/CMOS logic families and topologies can achieve lower hardware costs and intrinsic delays than CMOS. A single double-gate TFET mentioned in [10,11,12,13,14] can exhibit two-input Boolean logic behaviors, such as Or, And, Or-not, and And-not, so it can achieve two-input logic gates compactly by reducing the number of transistors. For example, the NAND2 and NOR2 logic gates in [10,13] only consist of two TFETs, while four transistors are required for the conventional CMOS. A novel split-gate FET has been used as a single transistor AND gate with a lesser area and power dissipation for two-input logic implementation [15]. In contrast to two-input logic primitives, some three-input logic gates exhibit higher efficiency in logic network simplification due to their high expressive power, such as typical three-input monotonic logic, Majority (MAJ) gate, AndOr gate, OrAnd gate, et al. [16,17,18]. Researchers are using emerging nanotechnology to implement three-input logic gates, such as Mach-Zehnder interferometers (MZI), quantum cellular automata (QCA), single electron transistor (SET), and naphthalene-based single-molecule transistor (NST) [19,20,21,22,23]. Among them, the MZI can implement three-input logic gates in optical but it needs a complex photoelectric conversion. The QCA is limited by the high fault rate in IC fabrication. The NST and SET use a resistor instead of pull-up networks, resulting in a larger area and static power consumption. As for the TFET, there is still room for improvement and optimization to construct the above three-input logic gate circuit by using the double-gate TFET technology mentioned in [10,13] to save at least half of the number of transistors. Consequently, this paper will explore the use of fewer transistors to implement a series of three-input monotone logic gates. Therefore, the three-input TFETs for realizing the MAJ, AndOr, and OrAnd logic functions are proposed. Due to the interesting characteristics of the proposed transistor, we also demonstrate a flexible and compact physical implementation of the three-input logic gate by using proposed TFETs.

This paper is organized as follows. In the second part, the device structure and simulation method are described, and the manufacturing process for the proposed device is clarified theoretically. The third section investigates the coupling effect and establishes a simplified potential model. A method for realizing a three-input logic function by a single three-input TFET device is described in the fourth section. In the fifth section, the compact implementation of MAJ, AndOr, and OrAnd gates using the proposed TFET is demonstrated. Finally, a summary and expectation are given.

2. Device Structure and Simulation Configuration

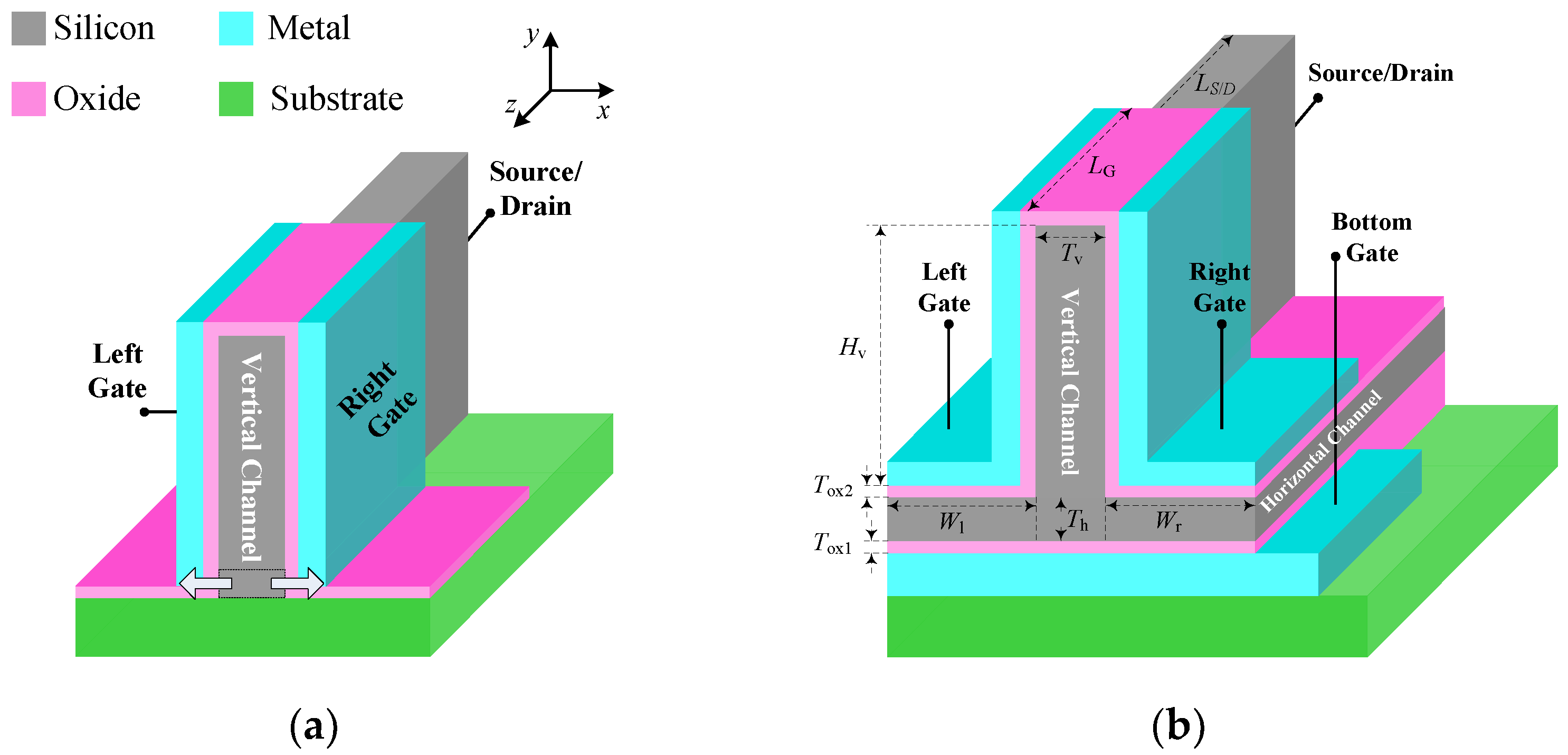

The three-dimensional structure of the proposed three-input TFET device is illustrated in Figure 1b, where the channel is shaped like an inverted letter “T”. Unlike the two-input TFET shown in Figure 1a, in the region where the horizontal channel is formed, the etch does not extend down to the oxide, and thus the Fin can be integrated into both the horizontal and vertical directions of a novel inverted T-shaped channel. Two independently biased gates are located on both sides of vertical channel, and the bottom gate is buried under the horizontal channel.

Figure 1.

The three-dimensional structure diagram of the proposed three-input TFET. (a) DG-TFET. (b) Inverted T-shaped TFET.

The proposed TFET utilizes three independently biased gates in order to provide unconventional control of the channel electrostatic. Three independent gate terminals accept the logical input signal of “ABC”, “A” for the left gate, “B” for the right gate, and “C” for the bottom gate. By choosing the appropriate body thickness (Th, Tv), gate work function ϕ (ϕL, ϕR, and ϕB are for left, right, and bottom gate), and the source doping level (NS_h, NS_v) of the horizontal and vertical regions, the BTBT in different biasing conditions can be suppressed. The remaining device parameters are listed in Table 1.

Table 1.

The parameters of the proposed TFET.

In this paper, we have employed Sentaurus TCAD software to predict the device properties. The dynamic nonlocal BTBT model is used in a 3D simulation environment to accurately describe the quantum tunneling current in a nonuniform electric field, where three important parameters in Nonlocal BTBT model, p = 2.5 for phonon-assisted tunneling, ASi = 1.64 × 1015 cm−3·s−1, and BSi = 23.8 × 106 V/cm referred from [24]. Considering that the energy band distribution in the diffusion region is affected by the heavy doping, the band gap narrow model is activated to describe the change in the band gap. We also utilize the Shockley–Read–Hall recombination model to simulate the leakage currents due to thermal injection. In addition, a modified local density approximation model is used to estimate the confined carrier distribution in the thin-body channel. Furthermore, the effective electron mass and hole mass are 0.26 m0 and 0.36 m0 for Si semiconductor, respectively. The carrier transport directions are aligned to the <1 0 0> crystallographic directions in simulations.

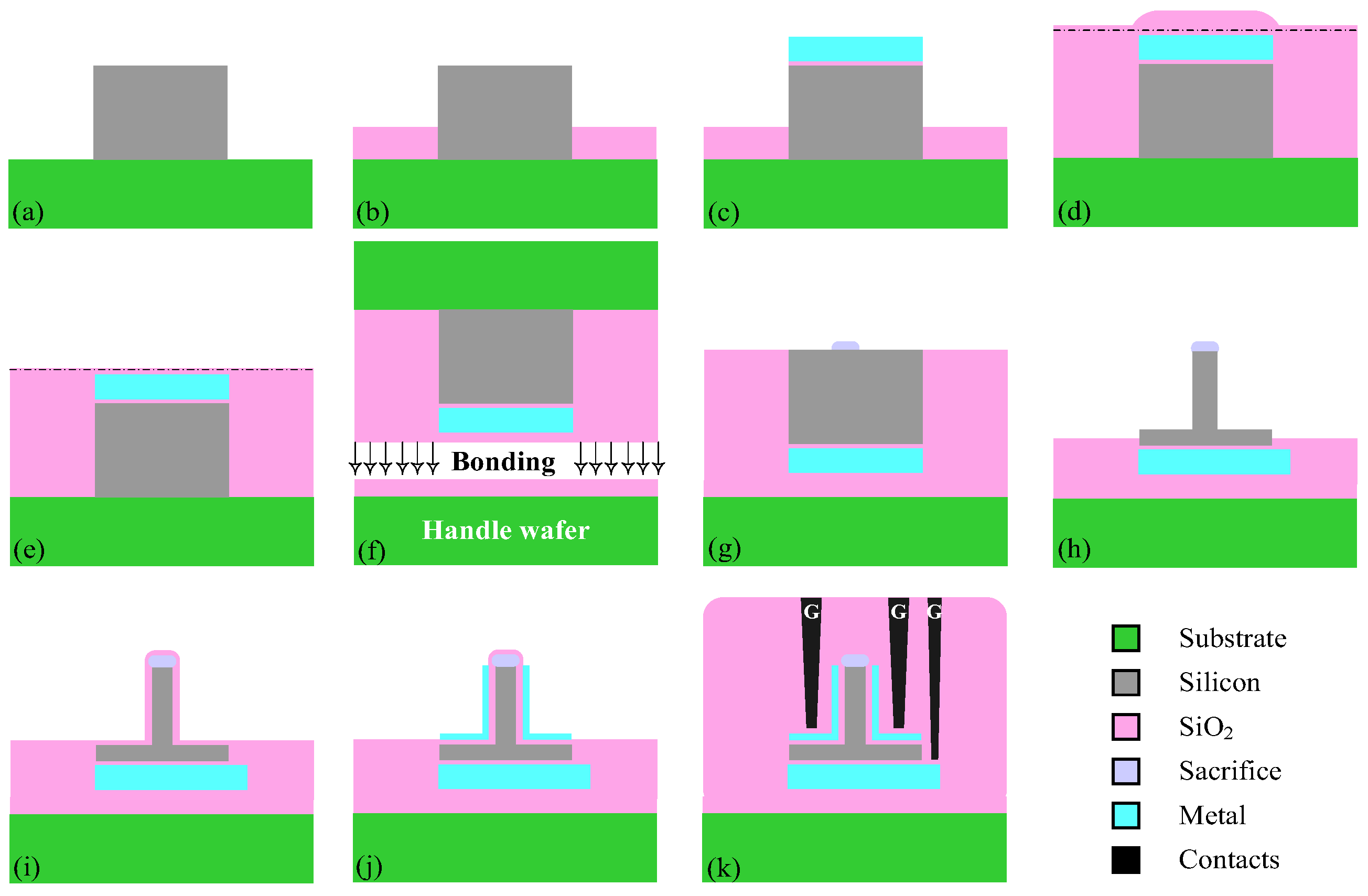

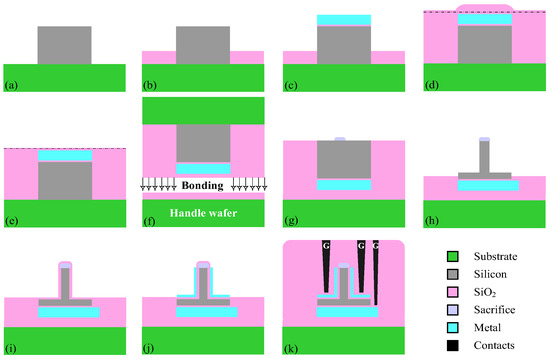

The basic process flow of the three-input TFET is shown in Figure 2. The key fabrication process of the proposed device is compatible with the SOI platform, except that the same e-beam marks are employed before and after the molecular bonding to align the three independently biased gates [25]. It started with the growth of epitaxial silicon on the substrate, followed by selective etching of the epitaxial silicon. Subsequently, the oxide isolation, the gate oxide, and the metal are deposited sequentially, and then, the bottom gate is patterned. After that, the oxide is deposited on the substrate, flattened using CMP technology, and an oxide cladding layer is formed. Next, the wafer is bonded on a handle wafer so that the bottom gate is buried below the channel, and as the next step, the inverted T-shape silicon is formed where the selective etch does not extend to the oxide. Finally, after the deposition of the SiO2, the left/right gate, the source, gate, and drain contacts are connected.

Figure 2.

The manufacturing process flow of an inverted T-shape structure. (a–c) Fin process. (d) oxide deposition, (e) CMP, (d) Bonding, (g–j) selective etch and metal gate deposition, and (k) contacts connection.

3. Gate Coupling in the Three-Input TFET

For a single device to exhibit MAJ (F = AB + BC + CA), OrAnd (F= AC + BC), and AndOr (F = AB + C) logic behavior, the challenge is to inhibit the on-state current when only one logic “1” is input (e.g., the N-type device should be in the cut-off state, where ABC = “100”, and the drain current is expressed as I001), which is diametrically opposed to the characteristics of a conventional MOSFET. The on-state current of TFET is mainly contributed by BTBT, and the BTBT current is most sensitive to the potential variation. Unlike the conventional TFET, the potential distribution in the inverted T-shaped channel is jointly modulated by the three gates, so the study of the coupling effect between the gates will help to find the appropriate device parameters to design a three-input TFET.

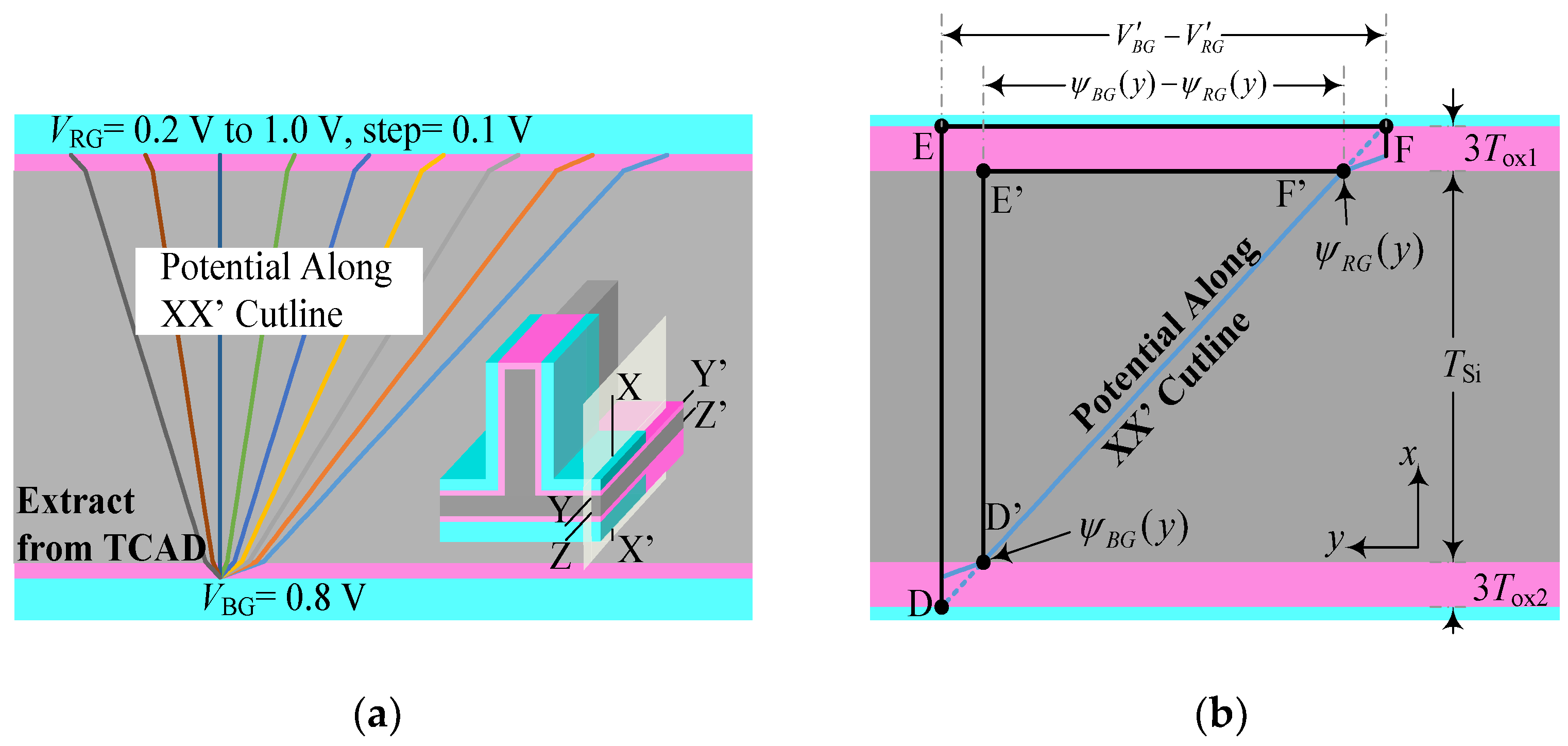

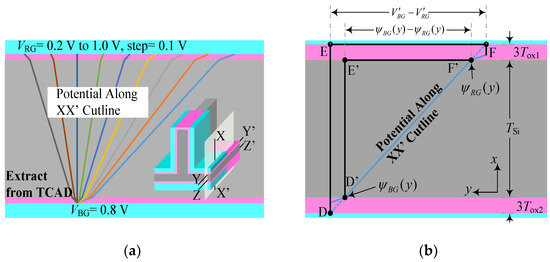

The potential distribution of the inverted T-shape channel for increasing VRG from 0.2 V to 1.0 V in steps of 0.1 V, where VBG is fixed at 0.8 V, is shown in Figure 3a. The important properties are visible: (1) The electrostatic potential in the right region of the horizontal channel is modulated by VRG and VBG. (2) The potential along XX’ cutline is weakly affected by VDS and presents a straight distribution.

Figure 3.

(a) Potential distribution (extracted by TCAD) along the XX’ cutline for increasing VRG from 0.2 V to 1.0 V in steps of 0.1 V, where VBG is fixed at 0.8 V. (b) Simplified model of the potential along the XX’ cutline. All cutlines lie in the YZ plane, and the YY’ and ZZ’ cutlines indicate the surface potential near the right and bottom gates, respectively.

To investigate the coupling effect on the conductive characteristics, a surface potential can be derived as a compact function of the body thickness TSi and the oxide thickness Tox. If εSi = εSiO2, the potential along the XX’ cutline will not bend at the Si-SiO2 interface. In order to obtain the same equivalent thickness of oxide, the Tox can be increased by εSi/εSiO2 = 11.9/3.9 ≈ 3 times [26]. Since the device is a long channel device, the potential distribution along the XX’ line is not affected by the source/drain potential. Therefore, the potential distribution shown in Figure 3b is linear, which is more convenient for intuitive analysis.

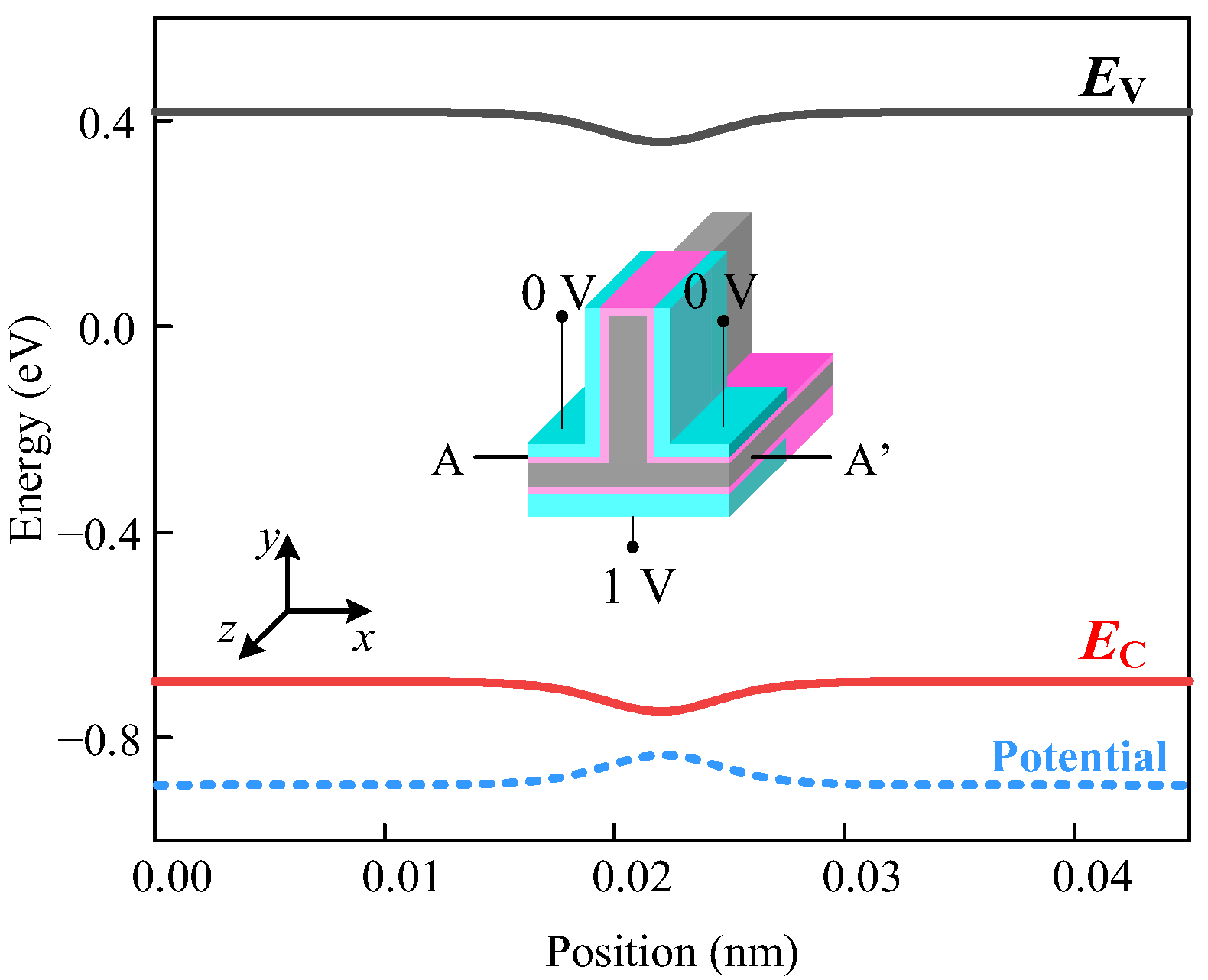

The potential distribution and energy band distributions along the x-axis are obtained by TCAD tools shown in Figure 4, where the input logic of ABC equals “001”. As we can see, the potential and energy band along the x-axis changes smoothly, and the current flow direction is perpendicular to the x-axis (in the yz-plane). Therefore, it is worth mentioning that we assumed that the carriers only flowed perpendicular to the x-axis, and thus only analyzes the potential distribution in the yz-plane.

Figure 4.

The potential and energy band distributions along cutline AA’ in x-axis.

Using the above simplified approach, the potential distribution (VRG = 1 V, VBG = 0 V) can be depicted as a straight line DF as shown in Figure 3b, where two similar triangles DEF and D’E’F’ can be obtained. Therefore, the simplified analytical model can be expressed as:

According to (1), ψRG(x) and ψRG(x) represent the surface potential near the right gate and the bottom gate, respectively. and are the difference between the gate voltage and the flat-band voltage, as given by and . Equation (1) can be rewritten as:

where Δϕ is the difference between the work functions of the right gate and bottom gates. To simplify the analysis, take Tox1 and Tox2 as 1 nm, and Δϕ = 0 eV. Equation (2) can be rewritten as:

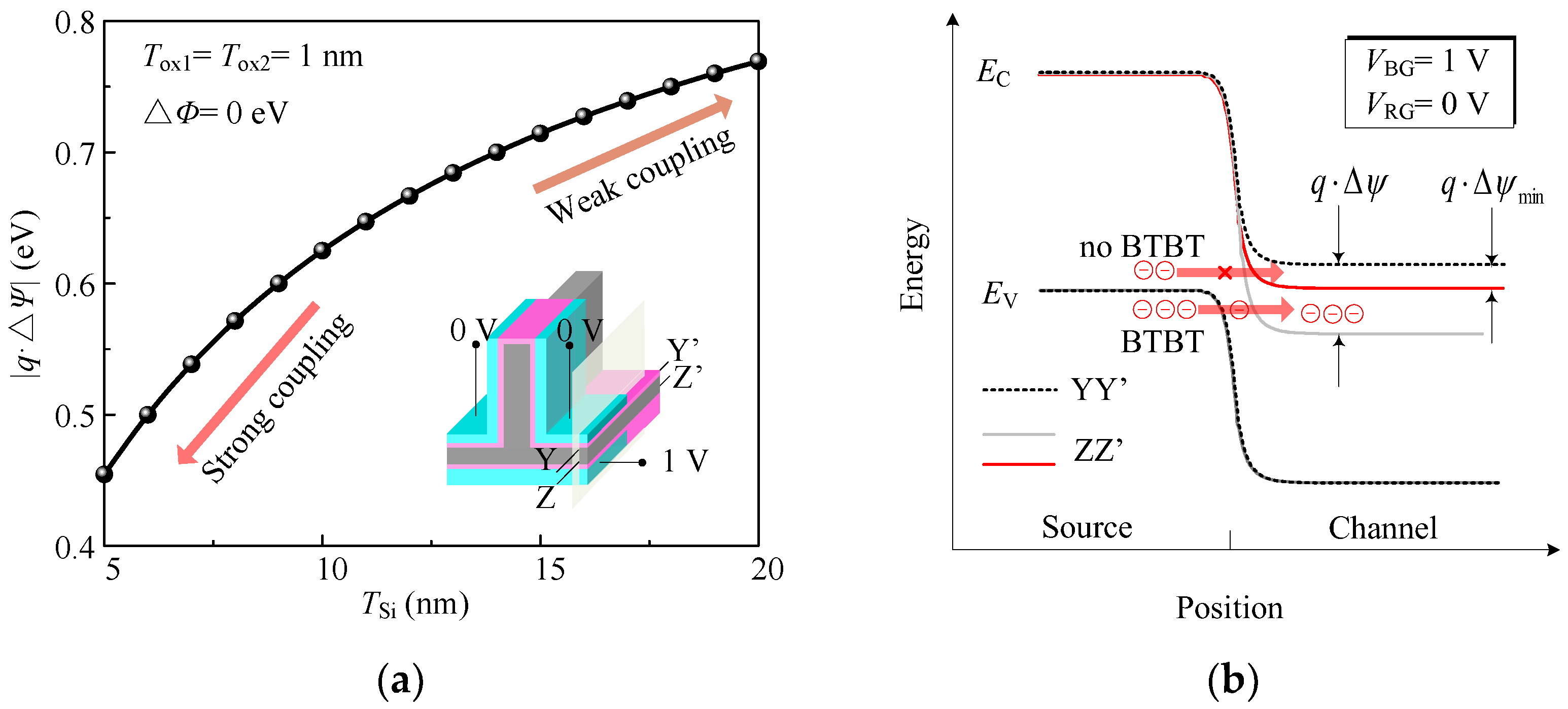

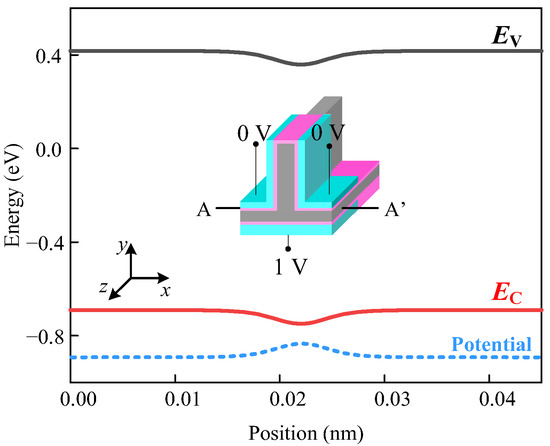

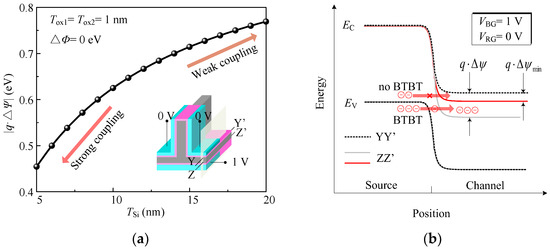

The relationship between the body thickness and the surface potential difference Δψ is plotted in Figure 4a, where VLG = VRG = 0 V, VBG = 1 V. We observed that the |q·Δψ| increases as body thickness increases and converges to the difference between VRG and VBG (VBG − VRG = 1 V). The surface potential on each side is modulated by the two gate voltages simultaneously. If the coupling is weaker, the |q·Δψ| is closer to VBG − VRG. Conversely, the potential difference is much smaller than VBG − VRG.

Taking inhibition of I001 as an example, where VLG = VRG = 0 V and VBG = 1 V. We assume that the ϕ of the right gate is large, which causes no BTBT occurring near the right gate, and the energy band distribution along the YY’ cutline is shown as the dashed line in Figure 5b. We find that the |q·Δψ| is too large, and the BTBT will occur along the ZZ’ cutline resulting in high I001 in this condition, as shown by gray solid lines in Figure 5b. Referring to (3), it can be seen that reducing the TSi can reduce the |q·Δψ|. If the coupling is small enough to make |q·Δψ|<|q·Δψmin|, the conduction band energy in the channel will be higher than the valence band in the source region, as shown by red solid line in Figure 5b. Therefore, the BTBT will not occur, and the purpose of suppressing the I001 is achieved.

Figure 5.

(a) The variation of the |q·Δψ| with the various body thickness at input logic of ABC = “001”. (b) Energy band distribution along YY’ and ZZ’ cutline.

This section may be divided by subheadings. It should provide a concise and precise description of the experimental results, their interpretation, as well as the experimental conclusions that can be drawn.

4. Extending the Logic Behavior of a Single TFET Device

4.1. Majority Behavior

An N-type device exhibiting MAJ logic behavior is turned on in which at least two of gate biases of 1 V. Therefore, the drain current, such as I100, I010, and I001, is needed to be suppressed in order to obtain a high Ion/Ioff ratio. From the analysis in the previous section, two important device parameters should be concerned: (1) A large work function ϕ (ϕL, ϕR, ϕB). (2) A thin channel (Th, Tv) to obtain a stronger coupling. The device parameters for the other devices are also given in Table 2.

Table 2.

Key parameter configuration of three-input TFETs with different logic behaviors.

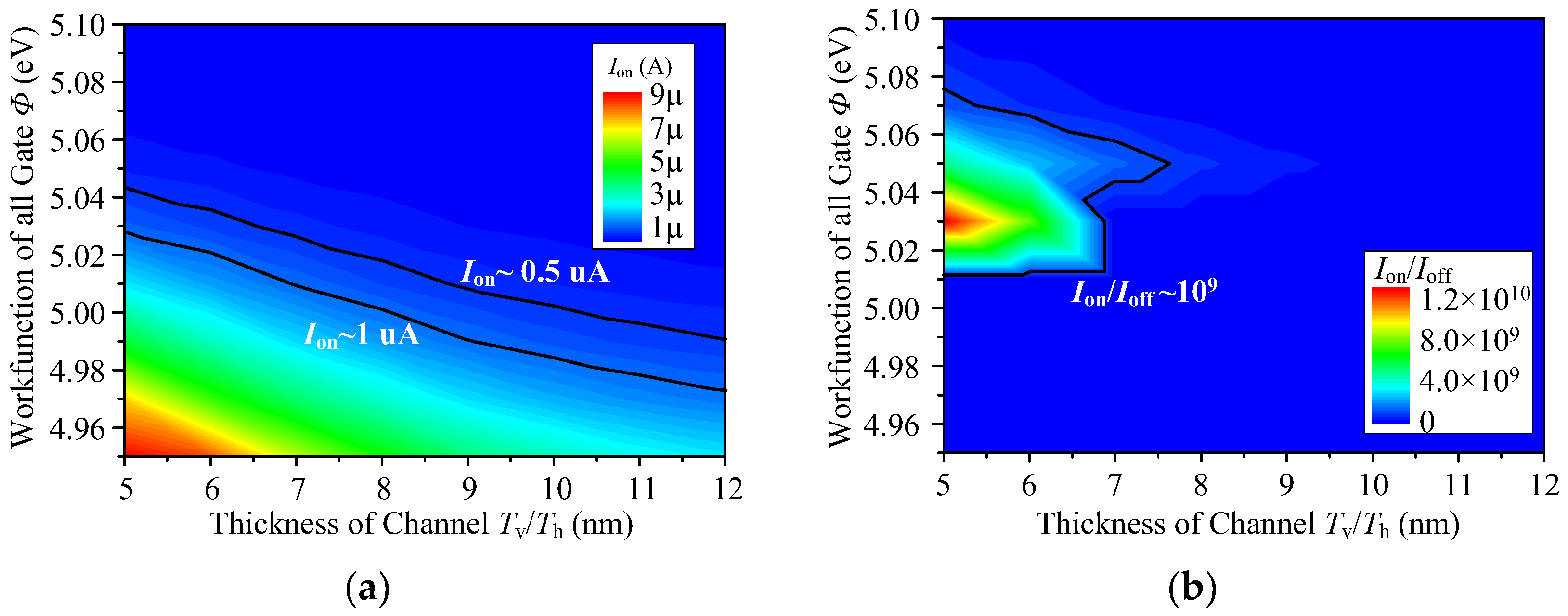

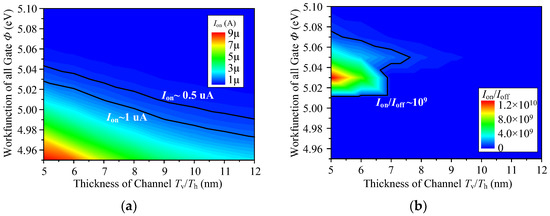

As verified by TCAD, the best device performance is achieved with the ϕ set to 5.03 eV for three gates and the Th/Tv set to 5–7 nm, as shown in Figure 6. It is worth noting that the proposed device is sensitive to the fluctuation of the ϕ; thus, requires a strict process control for the gate.

Figure 6.

(a) The on-state current Ion versus work function ϕ and body thickness Th/Tv. (b) The Ion/Ioff ratio versus ϕ and Th/Tv.

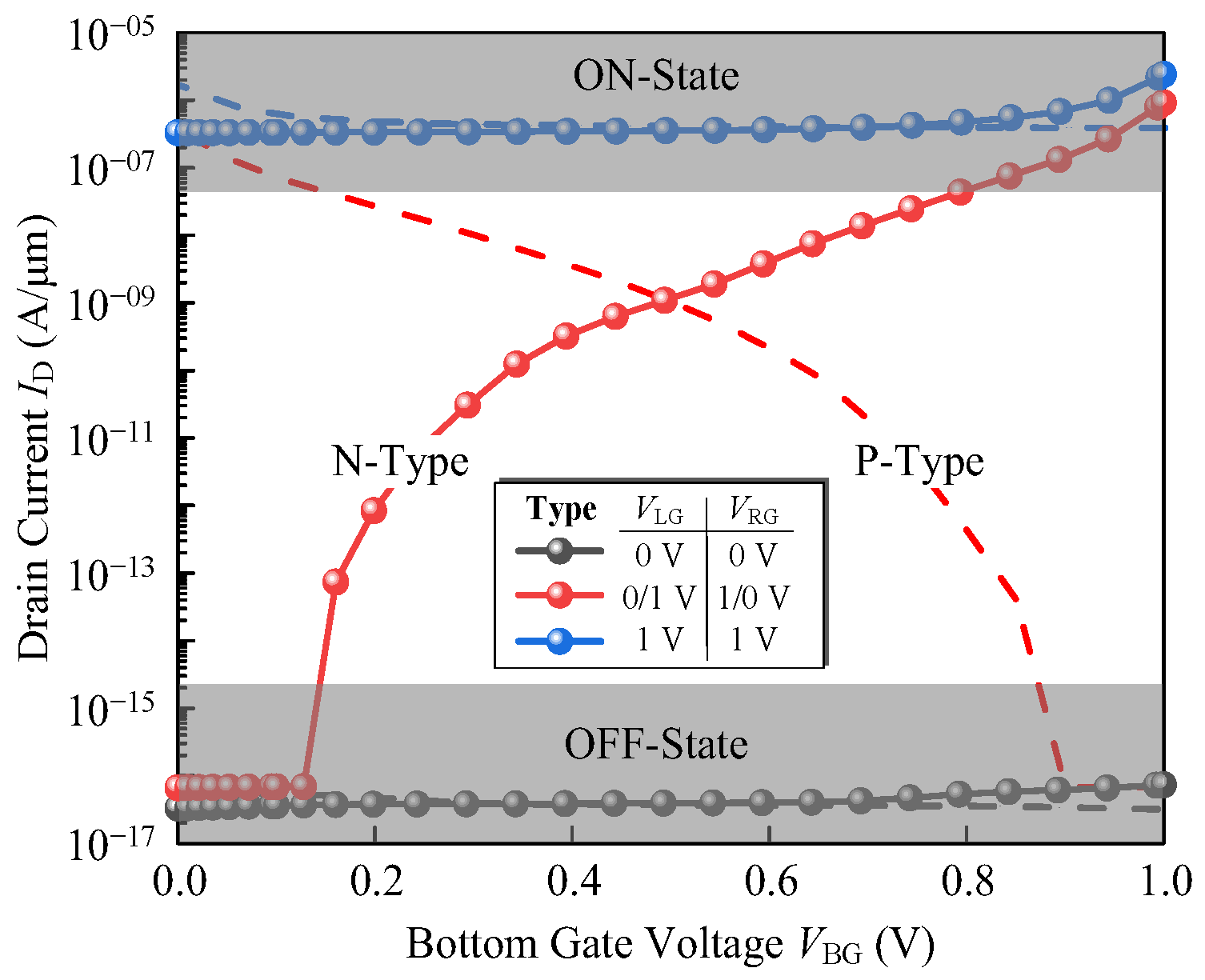

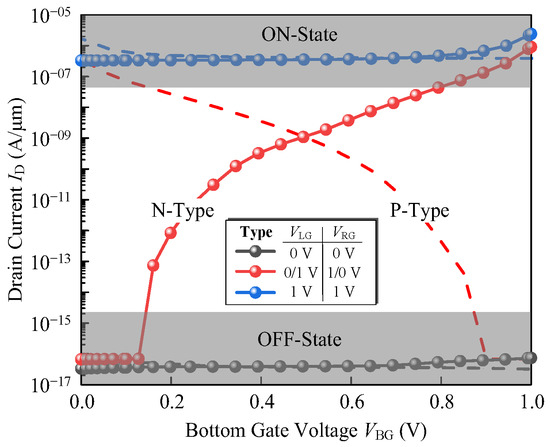

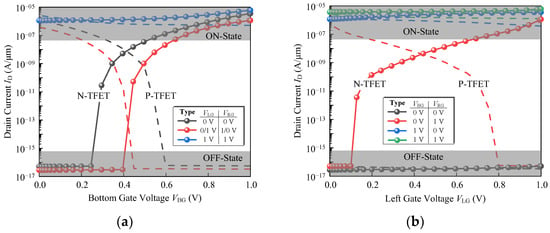

The transfer characteristics of the three-input TFET are obtained by scanning the bottom gate, where the VLG and VRG are fixed at logic “00”, “01”, “10” or “11”, as shown by the dotted lines in Figure 7. As can be seen, a single transistor exhibits MAJ logic behavior. When the VLG and VRG are both fixed at 0 V, the device is always turned off regardless of the variation of VBG. In contrast, the device is in on-state at VLG = VRG = 1 V. The Ion/Ioff ratio above ~109 are obtained, as well as the low turn-off current Ioff. However, the on-state current is still small, which is a common disadvantage for silicon-based TFETs but meets the requirement of the minimum current of 1 µA for low-power transistors as indicated by IRDS2020 [27].

Figure 7.

I-V characteristics of the N-type and P-type MAJ logic transistor at VDS = 1 V.

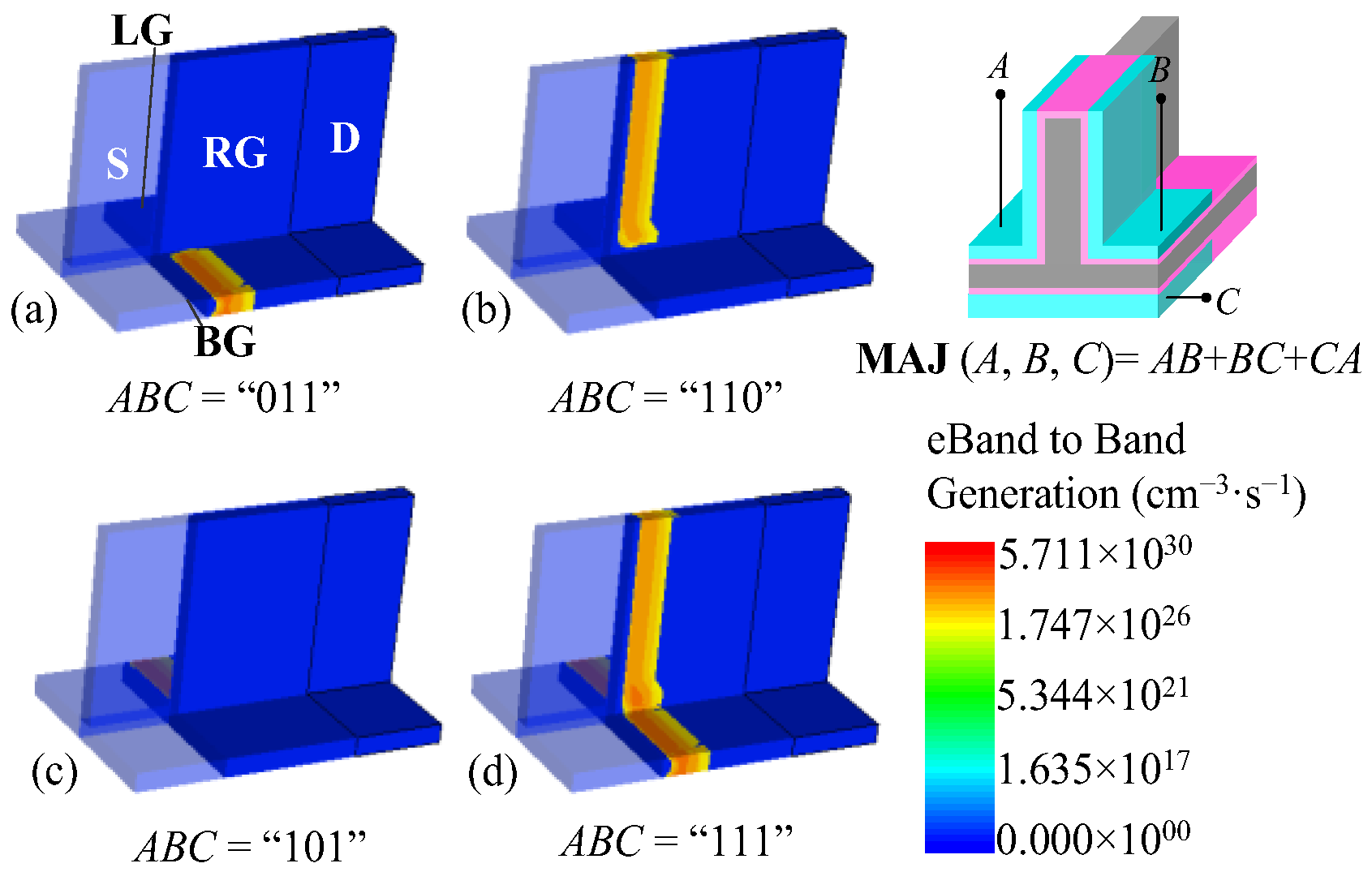

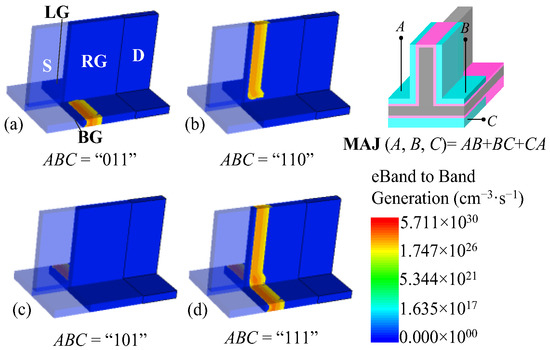

The BTBT generation distribution in the inverted T channel at different gate inputs reveals different on-state mechanisms, as shown in Figure 8. Taking the condition of ABC = “110” as an example (Figure 8b), the BTBT only occurs in the vertical channel, and thus the drain current flows through the vertical region. Due to the strong coupling, the BTBT in the horizontal channel is suppressed, resulting in an almost zero BTBT generation rate in this region. The different gate inputs lead to distribution differences of the BTBT, which shows the channel strobe mechanisms of the proposed device.

Figure 8.

Schematic diagram of BTBT generation with different gate inputs in MAJ logic device. (a) ABC = “011”, (b) ABC = “110”, (c) ABC = “101”, and (d) ABC = “111”.

To build a static complementary MAJ logic gate, a P-type TFET with MAJ behavior is also indispensable. The design of a P-type TFET is similar to an N-type TFET with reversed doping type. The doping concentrations of the N-doped source and P-doped drain are 1 × 1020 cm−3 and 4 × 1018 cm−3. The I-V characteristics of the P-type device of ϕ = 4.22 eV are shown as dashed lines in Figure 7, which shows a good symmetry.

4.2. OrAnd Behavior

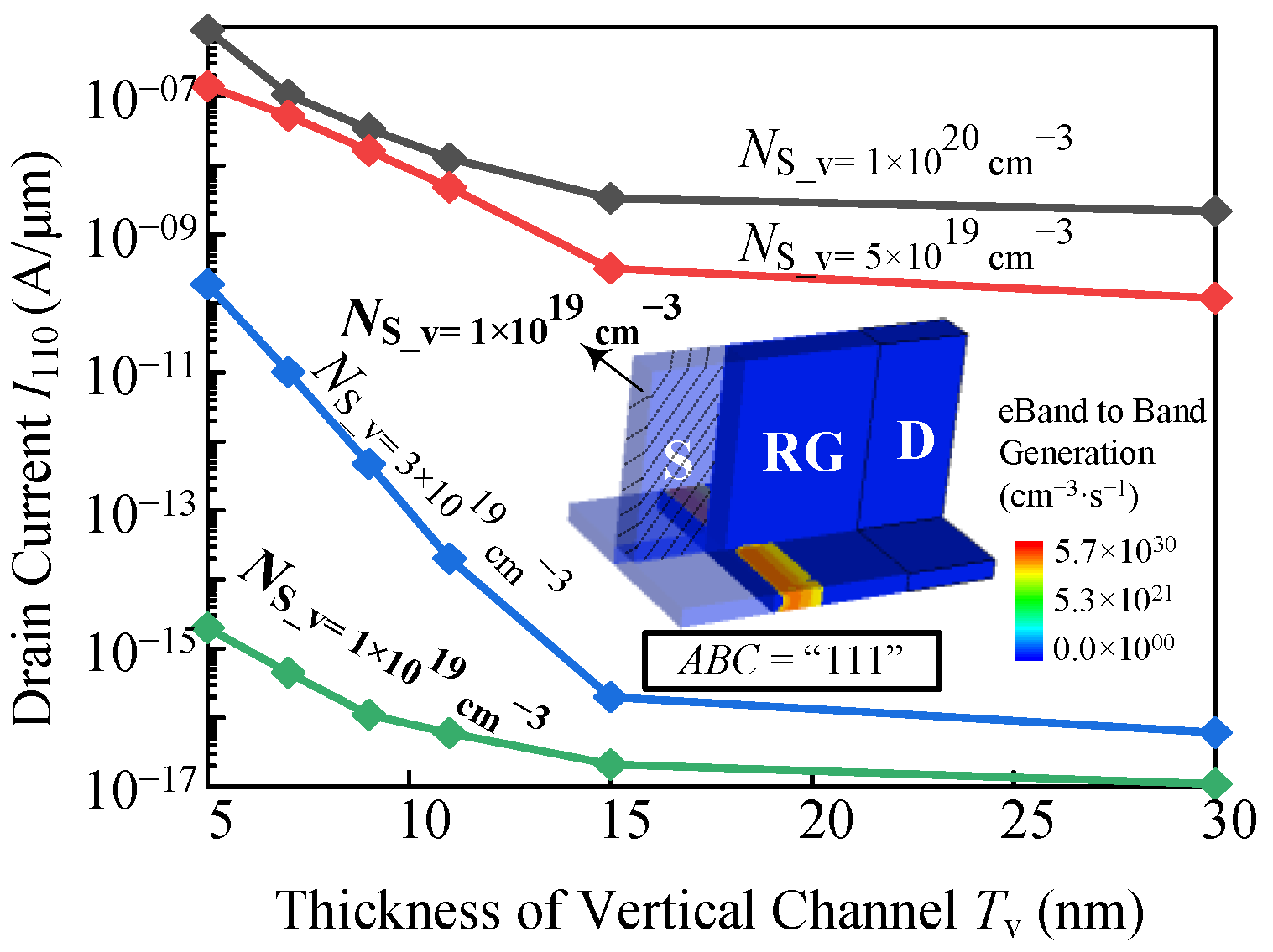

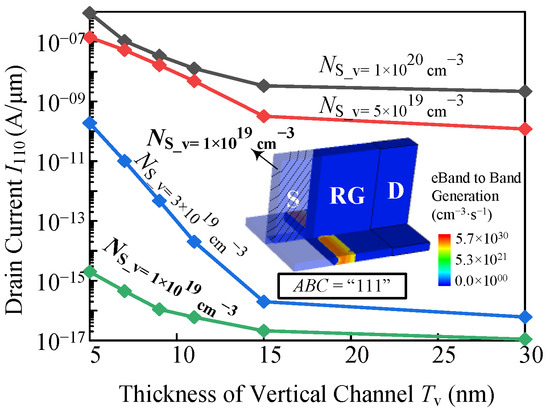

Comparing the MAJ (F = AB + AC + BC) and OrAnd (F = AC + BC) functions, the OrAnd logic function lacks the AB term. Therefore, suppressing the drain current I110 in the vertical channel at the gate inputs of AB = “11” is also one of the keys in an OrAnd logic device. According to the analysis in Section 3, this can be achieved by appropriately increasing the Tv to reduce the coupling. The other device parameters for the OrAnd device are shown in Table 2.

The black curve in Figure 9 indicates the I110 with various Tv. As Tv increases from 5 nm to 30 nm, the I110 decreases from 1.02 × 10−6 A/μm to 2.18 × 10−9 A/μm. The decreasing trend of the I110 slows down when the Tv is above 15 nm, which is highly consistent with the tendency in Figure 5a. However, the I110 is still high, which will lead to the large leakage power. Considering the low leakage and the simple process, the doping concentration of the vertical source region is chosen to be optimized. Therefore, we explored the device performance with different NS_v and found the appropriate value. As shown in Figure 9, for a device with NS_v = 1 × 1019 cm−3 and Tv = 9 nm, the I110 is suppressed to less than 10−16 A/μm. The inset of Figure 9 shows the contour plot of the BTBT generation rate at ABC = “111”, from which we observe that no BTBT occurs in the vertical channel and the drain current only flows through the horizontal region, even for VLG = VRG = 1 V.

Figure 9.

The Tv varied with I110 at NS_v = 1 × 1020 cm−3, 5 × 1019 cm−3, 3 × 1019 cm−3, and 1 × 1019 cm−3 in the OrAnd logic device.

Considering the current characteristics in all on-state of OrAnd devices (no BTBT current in vertical channel), complete removal of the vertical fin would be a better option. In order to obtain the same structure of all logic transistors, the doping concentration of the vertical source region is chosen to be optimized. However, ion implantation with different implantation dose and ionic energy is required for vertical and horizontal channels, resulting in additional shading layers over vertical and horizontal channels and extra process steps.

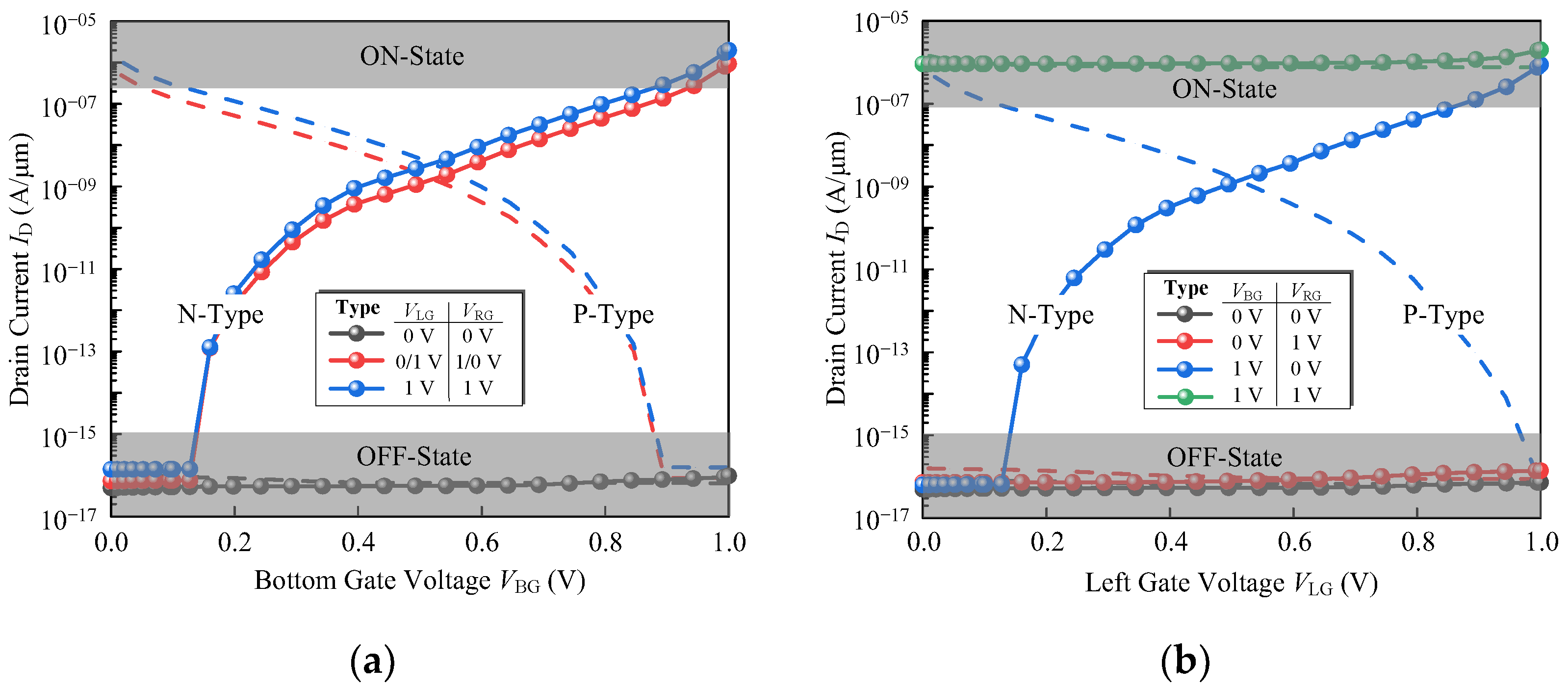

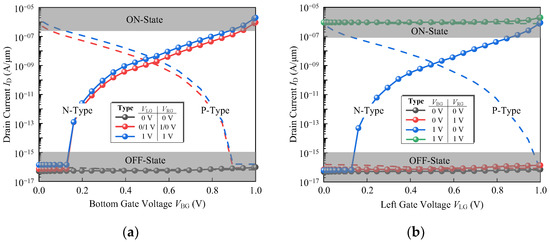

Without increasing the device width (Wl + Wr + Tv), the smaller the Tv the larger the effective area of the horizontal channel is obtained. Therefore, the Tv is taken as 9 nm, and the ID-VBG and ID-VLG characteristics of the N-type device are shown in Figure 10 (dotted lines). For a P-type TFET, the vertical source is 1 × 1019 cm−3 N-doped, the horizontal source is 1 × 1020 cm−3 N-doped, and the drain is 1 × 1018 cm−3 P-doped. The transfer characteristics of the P-type OrAnd logic device at ϕ = 4.22 eV are shown in Figure 10 (dashed lines).

Figure 10.

(a) ID-VBG and (b) ID-VLG curve of the proposed device exhibiting OrAnd behavior. The dotted lines are for N-type device and dashed lines for P-type.

4.3. AndOr Behavior

The pull-up network of an OrAnd logic gate needs to exhibit AndOr logic behavior, so a three-input TFET with the AndOr logic behavior is needed to be realized. For an AndOr logic device, only the BTBT current in the vertical channel at gate inputs of AB = “10” or AB = “01” needs to be suppressed. Consequently, the device parameters related to the vertical channel can remain unchanged, such as the ϕ of the left and right gate and Tv. It is worth noting that the device is turned on at ABC = “001”, so the coupling in the horizontal should not be enhanced.

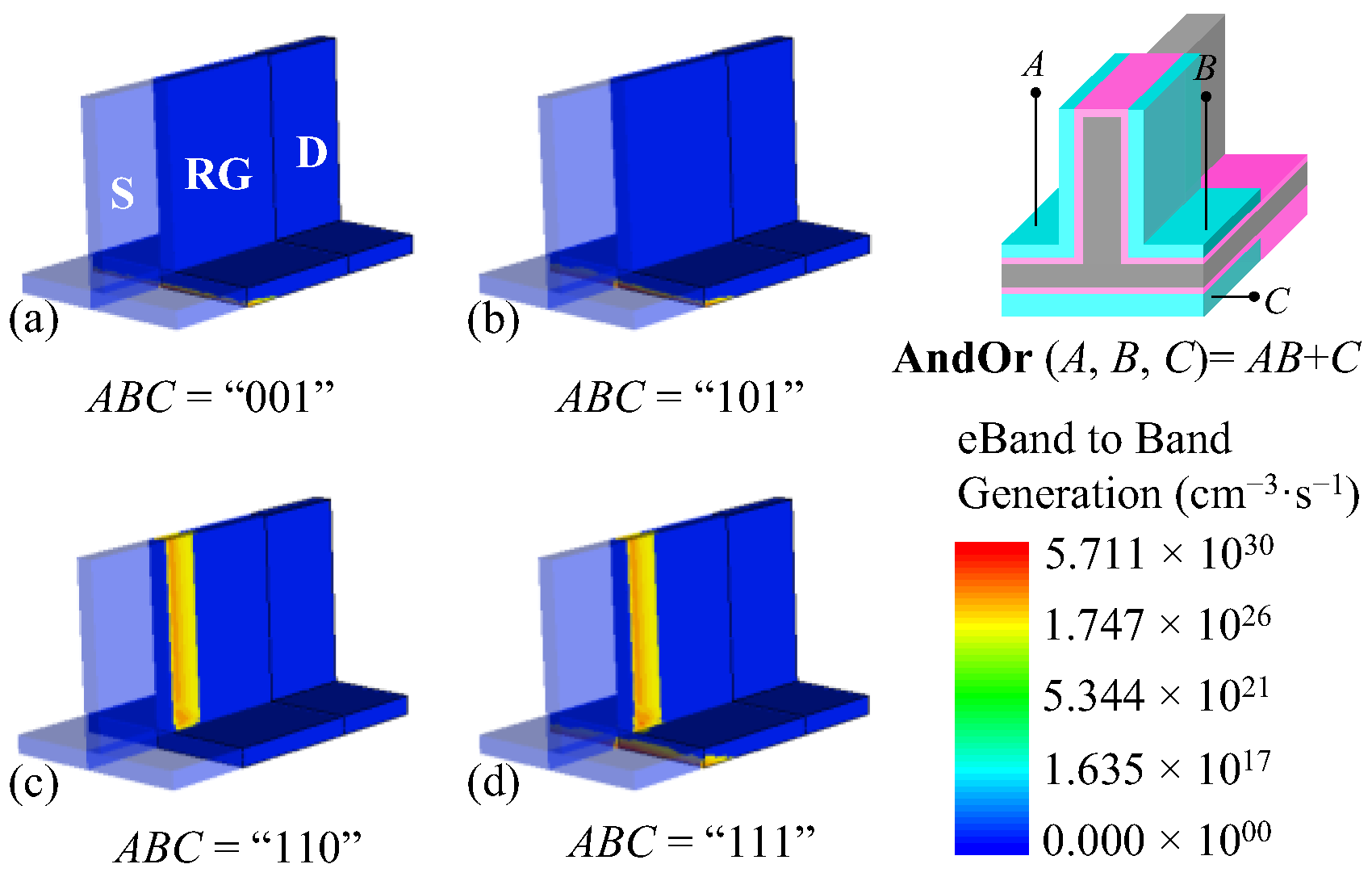

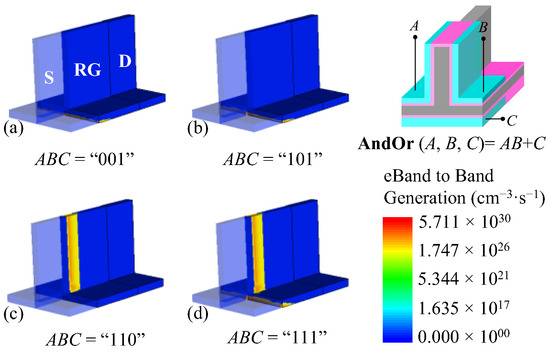

On the basis of the MAJ logic device, the ϕ of the bottom gate is reduced to 4.2 eV, and the NS_v is set to N-doped 5 × 1019 cm−3. The BTBT generation rate distribution under different biasing condition is obtained, as shown in Figure 11. As we can see, the BTBT in the horizontal channel is modulated by the VBG only, and the BTBT only occurs near the bottom region in the horizontal channel due to the small threshold voltage of the bottom gate.

Figure 11.

Contour plot of the BTBT generation rate for different gate inputs in AndOr logic device. (a) ABC = “001”, (b) ABC = “101”, (c) ABC = “110”, and (d) ABC = “111”.

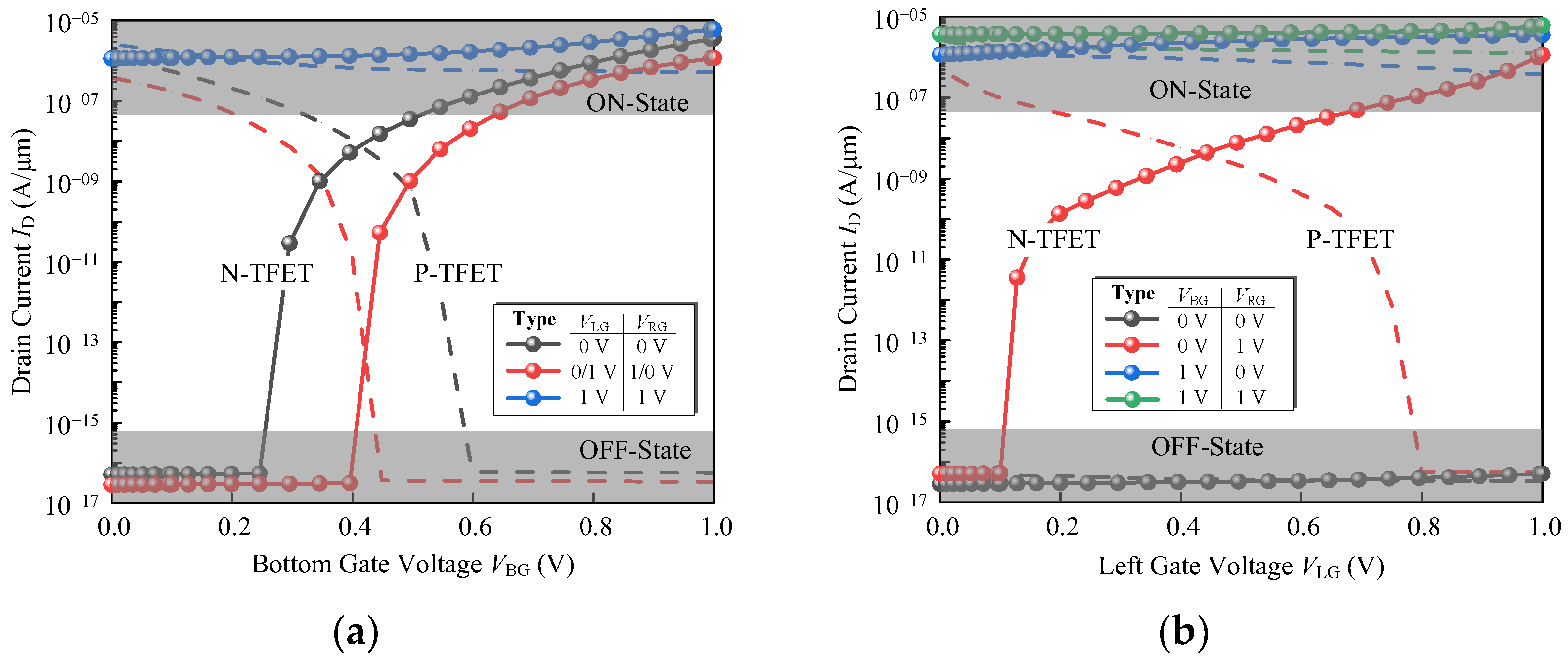

The ID-VBG and ID-VLG characteristics of the N-type (dotted lines) and P-type (dashed lines) device are shown in Figure 12. For the P-type AndOr device, the ϕ of the left and right gates are both set to 4.22 eV and 5.1 eV for the bottom gate.

Figure 12.

(a) ID-VBG and (b) ID-VLG curve of the proposed device exhibiting AndOr behavior. The dotted lines are for N-type device and dashed lines for P-type.

5. Discussion

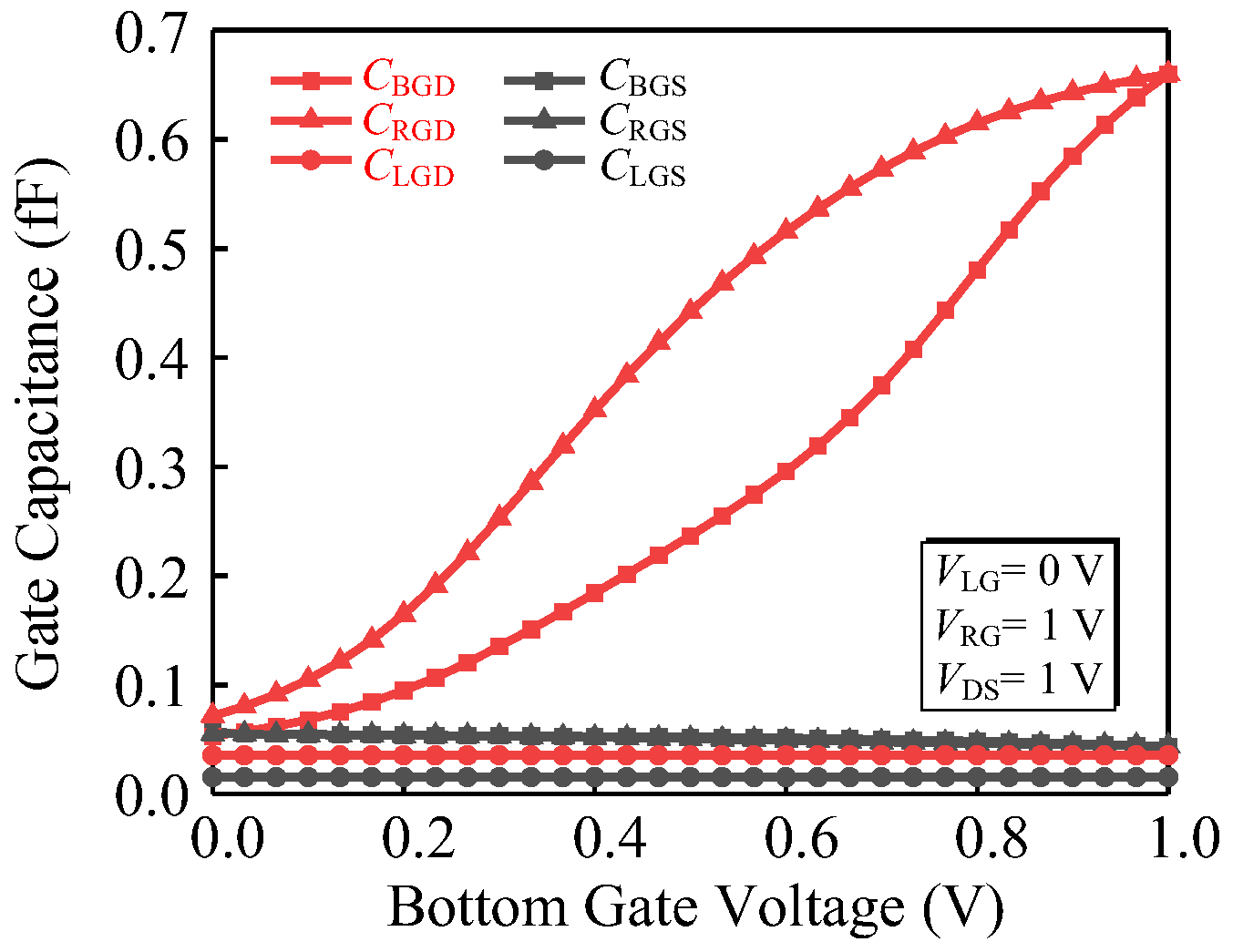

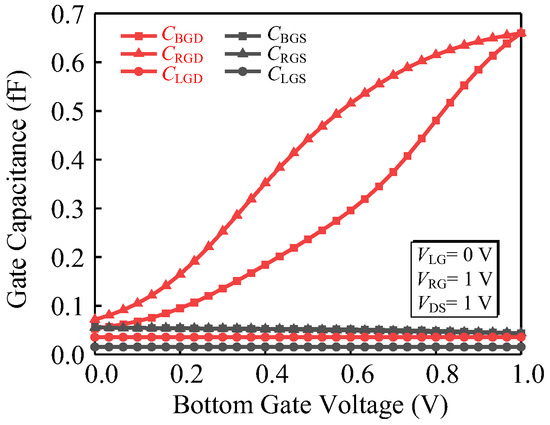

After optimizing the device parameters, critical electrical performances are summarized in Table 3, demonstrating correct logic behavior with Ion/Ioff ratio of more than 10−9. We also applied a small signal voltage of 1 MHz to the proposed device and extracted the parasitic capacitance curve, as shown in Figure 13. For the three-input TFET, the inversion layer is only connected to the drain, resulting in the gate–drain capacitance constituting a higher fraction of gate–gate capacitance Cgg [28]. Since the VRG is fixed at 1 V, the inversion first occurs in the horizontal channel near the right gate, with the right gate–drain capacitance CRGD accounting for a large proportion of Cgg. When the VBG is scanned to 1 V, the bottom gate–drain capacitance CBGD and CRGD are equal. The TFETs have a large Miller capacitance (CGD) compared to MOSFET; thus, obtain the larger overshoot resulting in a degradation of switching characteristics. Referring to [28], the CGD can be reduced through design improvements made to the drain dopant profile or through Lg scaling.

Table 3.

Important electrical performances of the proposed devices and logic gates.

Figure 13.

Capacitance characteristics of the proposed device. CBGS, CRGS, and CLGS indicate the gate-source capacitance, and CBGD, CRGD, and CLGD indicate the gate–drain capacitance.

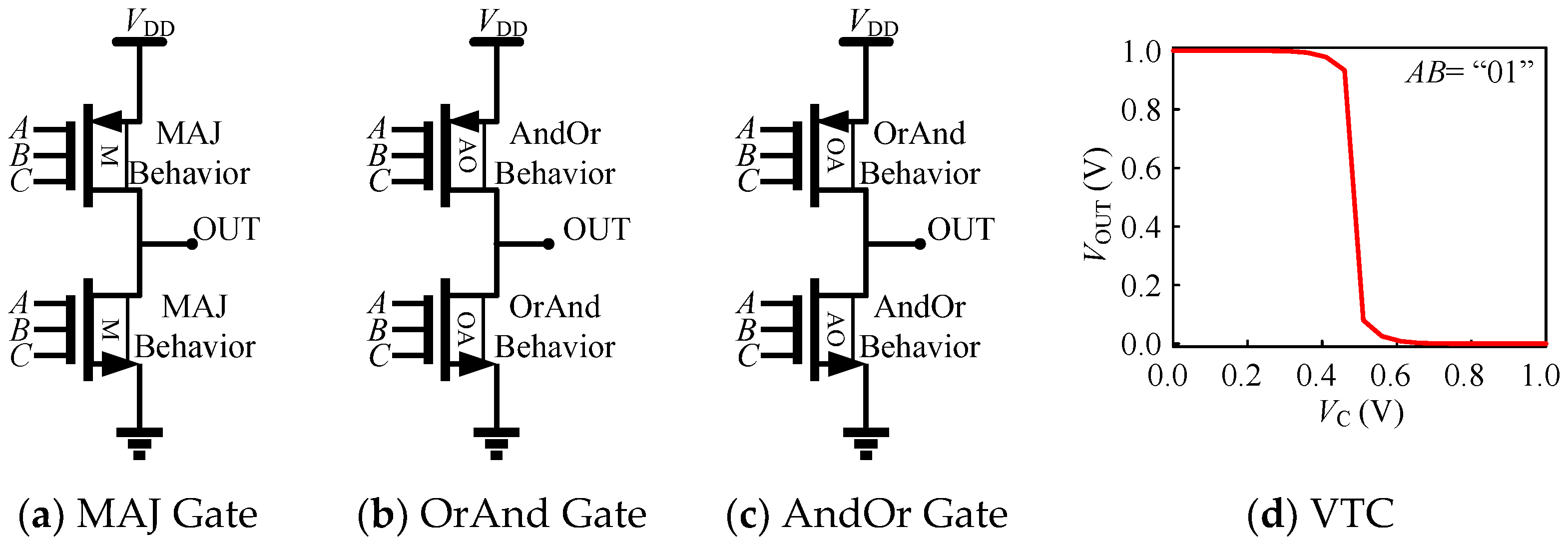

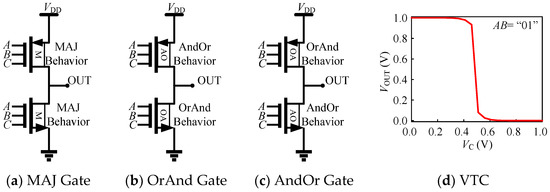

To implement static complementary three-input logic gates, we divide the six logic devices into three complementary pull-up and pull-down transistor pairs, such as the pair of P-type MAJ and N-type MAJ logic TFETs, the pair of P-type OrAnd and N-type AndOr logic TFETs, and the pair of P-type AndOr and N-type OrAnd logic TFETs. Figure 14a–c illustrates the compact implementation of the three logic gates, as we can see, using the proposed transistors to realize three-input logic gates, which can greatly save the number of transistors. The voltage transfer characteristics of the MAJ gate are shown in Figure 14d, which shows good static performance.

Figure 14.

(a–c) Construction of compact MAJ gate, OrAnd gate, and AndOr gate based on three-input TFETs. (d) VTC characteristic curve of MAJ gate, where AB = “01”.

Using the delay estimation method of logic gates mentioned in [29] reveals that the three-input TFET logic gate still has a high delay compared to the conventional CMOS gates. It is due to the low on-state current and high gate-drain capacitance in silicon-based TFETs. However, it is worth mentioning that implementing three-input logic gates by using the proposed devices can significantly reduce the number of transistors. In addition, the use of proposed devices could reduce the load capacitance and stack height, which results in an improvement of high delay in TFET-based circuits.

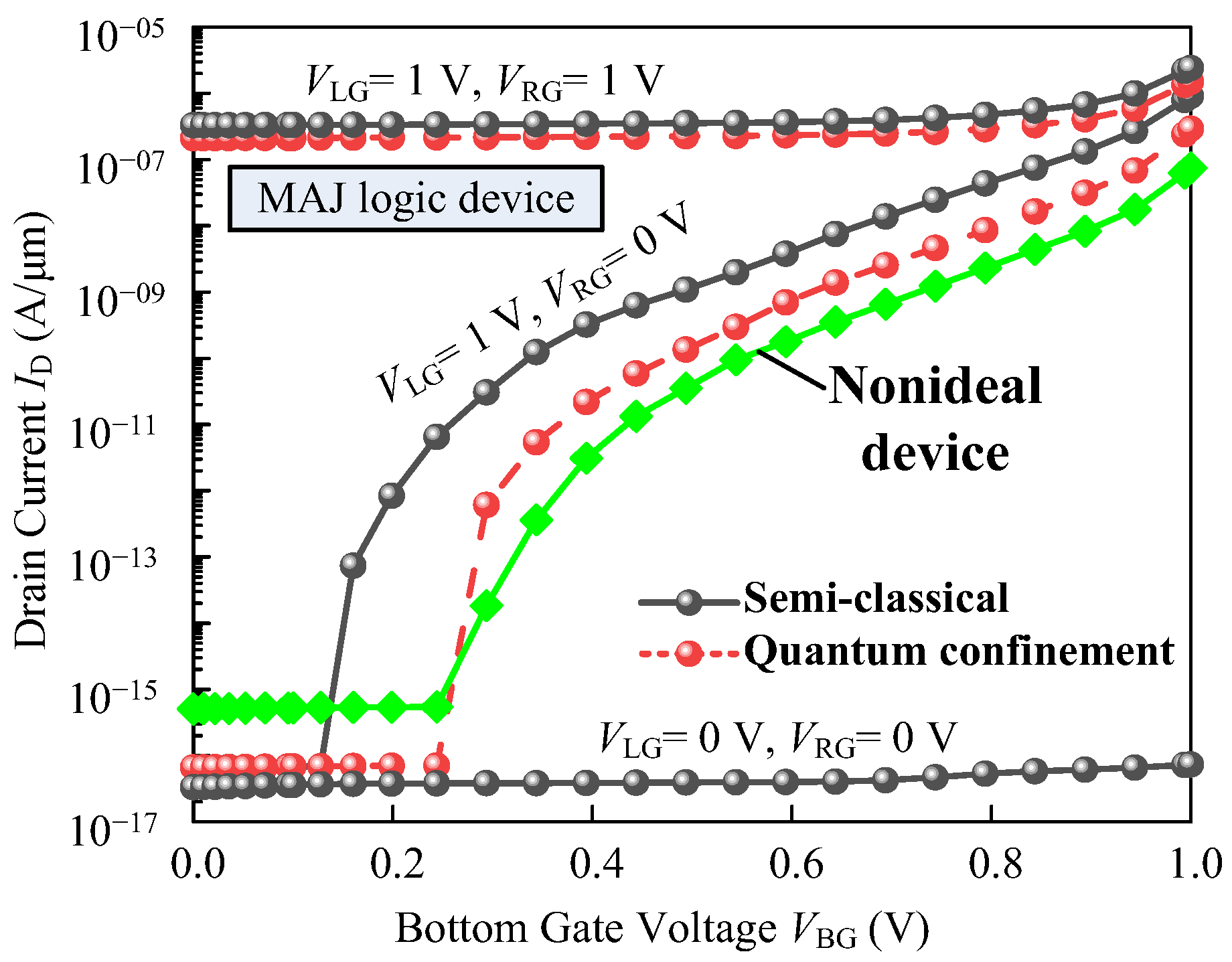

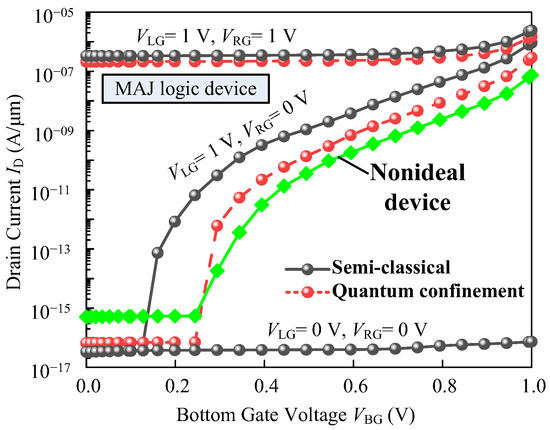

If carriers are confined in the thin body, geometric quantization leads to an energy shift of EC and EV leading to a larger band gap and effective mass in proposed devices. Therefore, we plot the transfer characteristics for the MAJ logic device obtained by the semi-classical model and quantum confinement model. Compared to the semi-classical models, the quantum mechanical treatment reveals a shift of the onset of 130 mV and degradation of subthreshold swing.

Furthermore, the second-order effects such as trap-assisted tunneling and non-homogenous doping are also taken into account. The nonideal transfer curve is shown in Figure 15, where the SS and Ion/Ioff ratio degradation is predicted but does not affect the logic behavior of the device. In general, degradation of device performance will cause degradation of proposed logic gate performance, such as increased static power consumption, increased delay, and low drive current.

Figure 15.

The transfer curves of the MAJ logic device extracted by TCAD simulation: (i) semi-classical, (ii) considering quantum confinement effect, and (iii) considering nonideal effects.

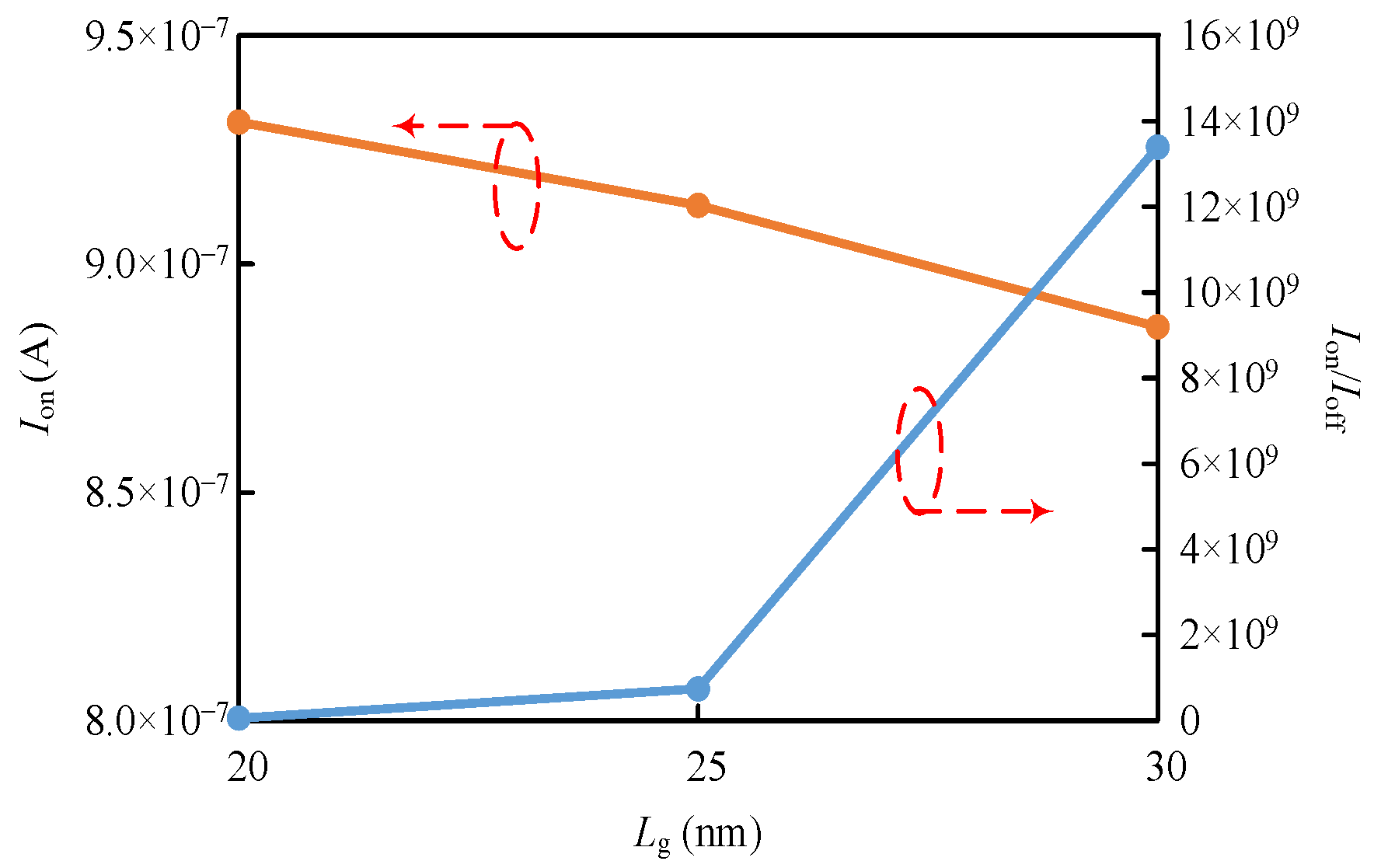

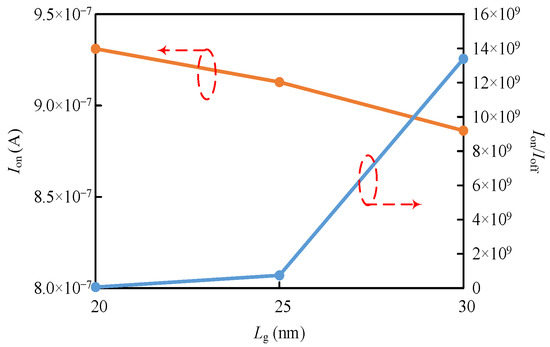

Scaling of LG from 30 nm to 20 nm is investigated, as shown in Figure 16. As LG is scaled with the same body thickness and oxide thickness, Ion and Ion/Ioff degrades. To achieve the proposed MAJ/AndOr/OrAnd gate, a design with a thin channel and a small Tox is required. This would be problematic for scaling. The tunneling current and Ion/Ioff of TFETs are very sensitive to body thickness, as shown in Figure 6. The sensitivity of TFET characteristics to oxide thickness is not significant [30]. Therefore, the main goal to recover degraded characteristics due to scaled-LG is using a thinner body, which will have negative effects on the MAJ device process and device variability.

Figure 16.

The Ion and Ion/Ioff of the MAJ logic device with same body thickness and oxide thickness.

6. Conclusions

This paper presents a novel TFET with an inverted T channel structure that can compactly implement MAJ, OrAnd, and AndOr logic gates. Under the different biasing conditions, the channel strobe mechanism is achieved through suppressing the coupling in the horizontal or vertical channel. The impact of the body thickness, work function and doping concentration on logic behavior and device performance are studied in detail with the help of the proposed simplified model and TCAD. The results show that realize three-input logic gates by using the proposed devices can save the number of transistors, and has low load capacitance and leakage current. Compared to the traditional CMOS logic gates, silicon-based TFET gates still have the problem of high delay, and extending the logic behavior in the three-input TFET also has negative effects on the device process and device variability. However, the use of three-input TFETs will provide a flexible and compact candidate for physical implementation of three-input logic functions.

The main objective of this paper is to propose techniques for extending the three-input logic behavior in a single silicon-based TFET, rather than enhancing device performance. In the future, the use of narrow energy gap materials or heterojunction technology on the silicon-based three-input TFETs will lead to improved device performance.

Author Contributions

Methodology, H.Y.; software, Y.S. and B.C.; validation, X.L. and J.H.; data curation, G.L.; writing—review and editing, H.Y. and P.W. All authors have read and agreed to the published version of the manuscript.

Funding

This research was funded by the National Natural Science Foundation of China (No. 62001257), in part by the Zhejiang Provincial Natural Science Foundation (No. LQ20F010004 and No. LY20F040007), in part by the Natural Science Foundation of Ningbo (2021S066), and in part by the Scientific Research Fund of Zhejiang Provincial Education Department (Y202248761).

Data Availability Statement

The data presented in this study are available on request from the corresponding author.

Conflicts of Interest

The authors declare no conflict of interest.

References

- Zhou, J.R.; Han, G.Q.; Li, J.; Liu, Y.; Peng, Y.; Zhang, J.C.; Sun, Q.Q.; Zhang, D.W.; Hao, Y. Negative Differential Resistance in Negative Capacitance EFTs. IEEE Electron Device Lett. 2018, 39, 622–625. [Google Scholar] [CrossRef]

- Zhou, J.R.; Han, G.Q.; Li, Q.L.; Peng, Y.; Lu, X.L.; Zhang, C.F.; Sun, Q.Q.; Zhang, D.W.; Hao, Y. Ferroelectric HfZrOx Ge and GeSn PMOSFETs with Sub-60 mV/decade Subthreshold Swing, Negligible Hysteresis, and Improved Ids. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016. [Google Scholar] [CrossRef]

- Han, K.; Long, S.; Deng, Z.; Zhang, Y.; Li, J. A Novel Germanium-Around-Source Gate-All-Around Tunnelling Field-Effect Transistor for Low-Power Applications. Micromachines 2020, 11, 164. [Google Scholar] [CrossRef] [PubMed]

- Ma, B.; Chen, S.; Wang, S.; Han, T.; Zhang, H.; Yin, C.; Chen, Y.; Liu, H. A Novel L-Gate InGaAs/GaAsSb TFET with Improved Performance and Suppressed Ambipolar Effect. Micromachines 2022, 13, 1474. [Google Scholar] [CrossRef] [PubMed]

- Nirschl, T.; Wang, P.F.; Weber, C.; Sedlmeir, J.; Heinrich, R.; Kakoschke, R.; Schrufer, K.; Holz, J.; Pacha, C.; Schulz, T.; et al. The Tunneling Field Effect Transistor (TFET) as An Add-on for Ultra-Low-Voltage Analog and Digital Processes. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 13–15 December 2004. [Google Scholar] [CrossRef]

- Wang, Z.X.; Zhong, Y.; Chen, C.; Ye, L.; Huang, Q.Q.; Yang, L.B.; Wang, Y.Y.; Huang, R. Ultra-Low Power Hybrid TFET-MOSFET Topologies for Standard Logic Cells with Improved Comprehensive Performance. In Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS), Sapporo, Japan, 26–29 May 2019. [Google Scholar] [CrossRef]

- Thapliyal, H.; Varun, T.S.S.; Kumar, S.D. Low-Power and Secure Lightweight Cryptography Via TFET-Based Energy Recovery Circuits. In Proceedings of the IEEE International Conference on Rebooting Computing (ICRC), Washington, DC, USA, 1–4 November 2017. [Google Scholar] [CrossRef]

- Alper, C.; Padilla, J.L.; Palestri, P.; Ionescu, A.M. A Novel Reconfigurable Sub-0.25-V Digital Logic Family Using the Electron-Hole Bilayer TFET. IEEE J. Electron Devices Soc. 2018, 6, 2–7. [Google Scholar] [CrossRef]

- Wang, Z.X.; Ye, L.; Huang, Q.Q.; Du, K.X.; Tan, Z.C.; Wang, Y.Y.; Huang, R. Ultra-Low-Power and Performance-Improved Logic Circuit Using Hybrid TFET-MOSFET Standard Cells Topologies and Optimized Digital Front-End Process. IEEE Trans. Circuits Syst. I Reg. Papers 2021, 68, 1160–1170. [Google Scholar] [CrossRef]

- Wang, J.; Hu, J.; Bai, W. Dual-threshold Independent-gate N-type TFETs. In Proceedings of the International Conference on Nanotechnology (IEEE-NANO), Cork, Ireland, 1–4 July 2018. [Google Scholar] [CrossRef]

- Garg, S.; Saurabh, S. Implementation of Boolean Functions Using Tunnel Field-Effect Transistors. IEEE J. Explor. Solid-State Computat. 2020, 6, 146–154. [Google Scholar] [CrossRef]

- Garg, S.; Saurabh, S. Implementing Logic Functions Using Independently-Controlled Gate in Double-Gate Tunnel FETs: Investigation and Analysis. IEEE Access 2019, 7, 117591–117599. [Google Scholar] [CrossRef]

- Banerjee, S.; Garg, S.; Saurabh, S. Realizing Logic Functions Using Single Double-Gate Tunnel FETs: A Simulation Study. IEEE Electron Device Lett. 2018, 39, 773–776. [Google Scholar] [CrossRef]

- Garg, S.; Saurabh, S. Realizing XOR and XNOR Functions Using Tunnel Field-Effect Transistors. IEEE J. Electron Devices Soc. 2020, 8, 1001–1009. [Google Scholar] [CrossRef]

- Kumar, P.; Gupta, M.; Singh, K.; Kumar, N. Design and Investigation of Split-Gate MoTe2-based FET as Single Transistor and Gate Using Nonequilibrium Green’s Function. IEEE Trans. Electron Devices 2020, 67, 5221–5228. [Google Scholar] [CrossRef]

- Chu, Z.F.; Soeken, M.; Xia, Y.S.; Wang, L.Y.; Micheli, G.D. Advanced Functional Decomposition Using Majority and Its Applications. IEEE Trans. Comput.-Aided Design Integr. Circuits Syst. 2020, 39, 1621–1634. [Google Scholar] [CrossRef]

- Reuben, J. Rediscovering Majority Logic in the Post-CMOS Era: A Perspective from In-Memory Computing. J. Low Power Electron. Appl. 2020, 10, 28. [Google Scholar] [CrossRef]

- Marakkalage, D.S.; Testa, E.; Riener, H.; Mishchenko, A.; Soeken, M.; Micheli, G.D. Three-Input Gates for Logic Synthesis. IEEE Trans. Comput.-Aided Design Integr. Circuits Syst. 2021, 40, 2184–2188. [Google Scholar] [CrossRef]

- Rehan, S.E. A 3-input Universal Logic Gate (ULG) using a Single Electron Linear Threshold Gate (LTG). In Proceedings of the IEEE Mediterranean Electrotechnical Conference (IEEE MELECON), Yasmine Hammamet, Tunisia, 25–28 March 2012. [Google Scholar] [CrossRef]

- Foroutan, S.A.; Sabbaghi-Nadooshan, R.; Mohammadi, M.; Tavakoli, M.B. Investigating Multiple Defects on A New Fault-tolerant Three-input QCA Majority Gate. J. Supercomput. 2021, 77, 8305–8325. [Google Scholar] [CrossRef]

- Karbasian, G.; McConnell, M.S.; George, H.; Schneider, L.C.; Filmer, M.J.; Orlov, A.O.; Nazarov, A.N.; Snider, G.L. Metal-Insulator-Metal Single Electron Transistors with Tunnel Barriers Prepared by Atomic Layer Deposition. Appl. Sci. 2017, 7, 246. [Google Scholar] [CrossRef]

- Kumar, S.; Singh, G.; Amphawan, A. Reversible Ripple Carry Adder using the Electro-optic Effect of Lithium-niobate Based Mach-Zehnder Interferometer. In Proceedings of the Workshop on Recent Advances in Photonics (WRAP), Bangalore, India, 1–4 December 2015. [Google Scholar] [CrossRef]

- Fakheri, M.T.; Navi, K.; Tehrani, M. A Novel Device to Implement Full Set of Three-Input Logic Gates Using a Naphthalene-Based Single-Molecule Field-Effect Transistor. IEEE Trans. Electron Devices 2021, 68, 733–738. [Google Scholar] [CrossRef]

- Kao, K.H.; Verhulst, A.S.; Vandenberghe, W.G.; Soree, B.; Groeseneken, G.; Meyer, K.D. Direct and Indirect Band-to-Band Tunneling in Germanium-based TFETs. IEEE Trans. Electron Devices 2012, 59, 292–301. [Google Scholar] [CrossRef]

- Vinet, M.; Poiroux, T.; Licitra, C.; Widiez, J.; Bhandari, J.; Previtali, B.; Vizioz, C.; Lafond, D.; Arvet, C.; Besson, P.; et al. Self-Aligned Planar Double-Gate MOSFETs by Bonding for 22-nm Node, with Metal Gates, High-k Dielectrics, and Metallic Source/Drain. IEEE Electron Device Lett. 2009, 30, 748–750. [Google Scholar] [CrossRef]

- Masahara, M.; Surdeanu, R.; Witters, L.; Doornbos, G.; Nguyen, V.H.; Bosch, G.V.; Vrancken, C.; Jurczak, M.; Biesemans, S. Experimental Investigation of Optimum Gate Workfunction for CMOS Four-termihal Multigate MOSFETs (MUGFETs). IEEE Trans. Electron Devices 2007, 54, 1431–1437. [Google Scholar] [CrossRef]

- Executive Summary, International Roadmap for Device and Systems (IRDS). 2020. Available online: https://irds.ieee.org/editions/2020/ (accessed on 30 January 2023).

- Yang, Y.; Tong, X.; Yang, L.T.; Guo, P.F.; Fan, L.; Yeo, Y.C. Tunneling Field-Effect Transistor: Capacitance Components and Modeling. IEEE Electron Device Lett. 2010, 31, 752–754. [Google Scholar] [CrossRef]

- Na, M.H.; Nowak, E.J.; Haensch, W.; Cai, J. The Effective Drive Current in CMOS Inverters. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 8–11 December 2002. [Google Scholar] [CrossRef]

- Avci, U.E.; Young, I.A. Heterojunction TFET Scaling and Resonant-TFET for Steep Subthreshold Slope at Sub-9nm Gate-length. In Proceedings of the 2013 IEEE International Electron Devices Meeting, Washington, DC, USA, 9–11 December 2013. [Google Scholar]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).