An Accurate Electro-Thermal Coupling Model of a GaAs HBT Device under Floating Heat Source Disturbances

Abstract

:1. Introduction

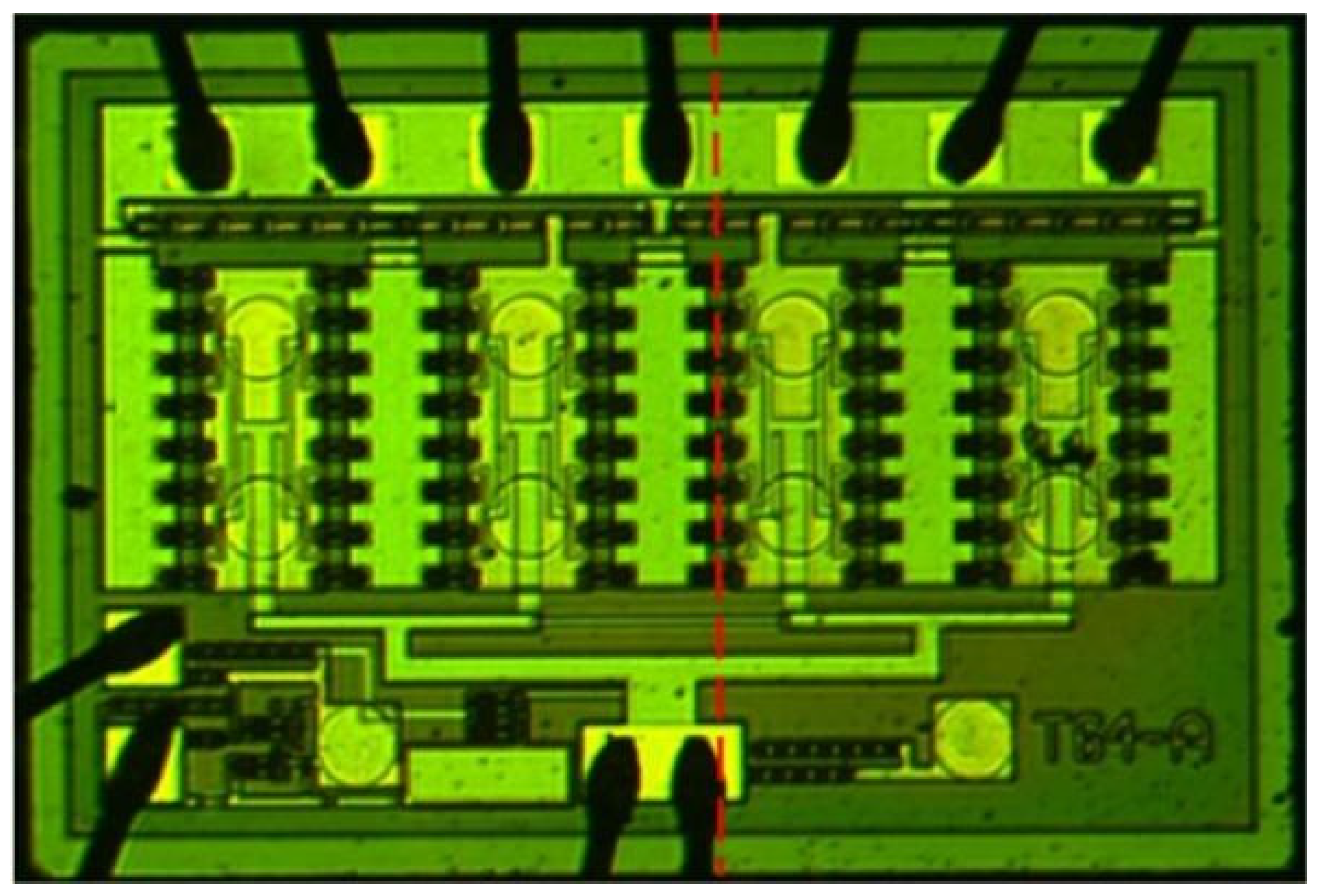

2. Establishment of Theoretical Models

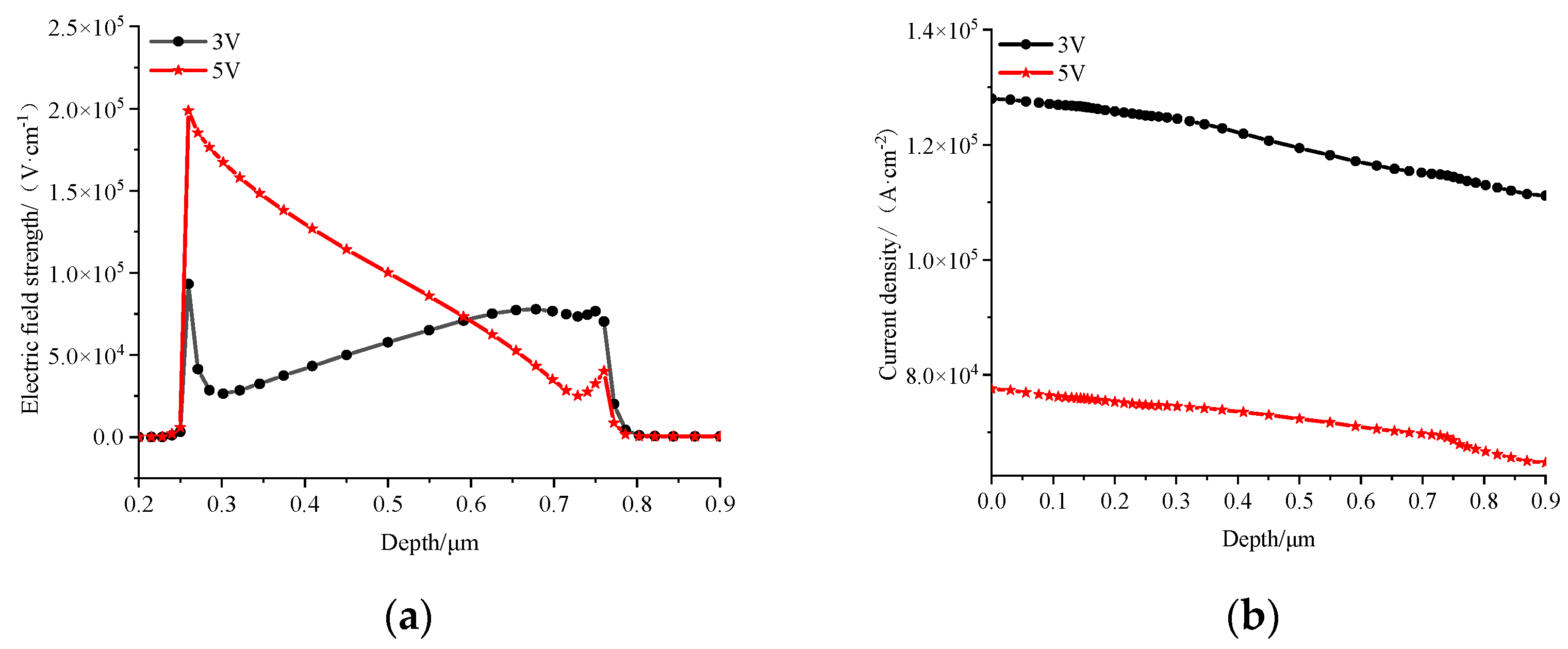

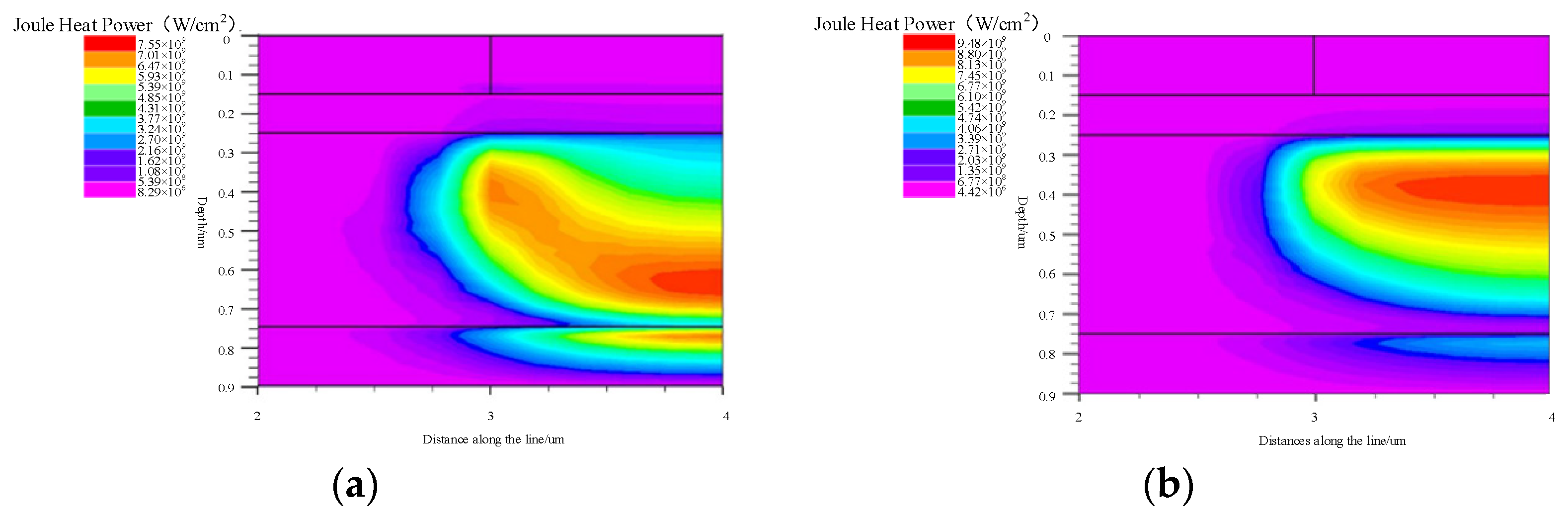

2.1. Single-Transistor Electro-Thermal Phenomenon

2.2. Physical Analysis

2.3. Nonlinear Temperature Model Based on Current Correction

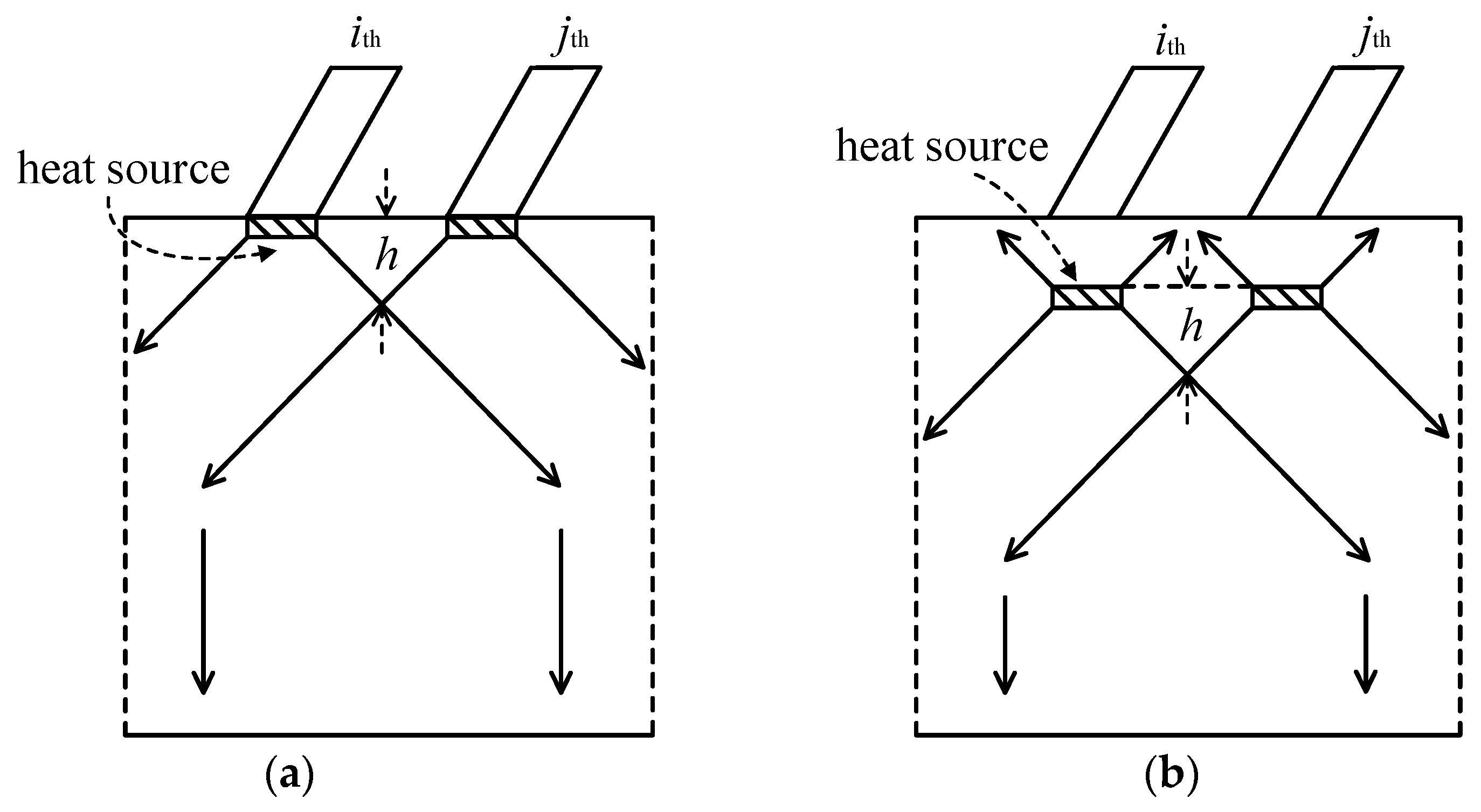

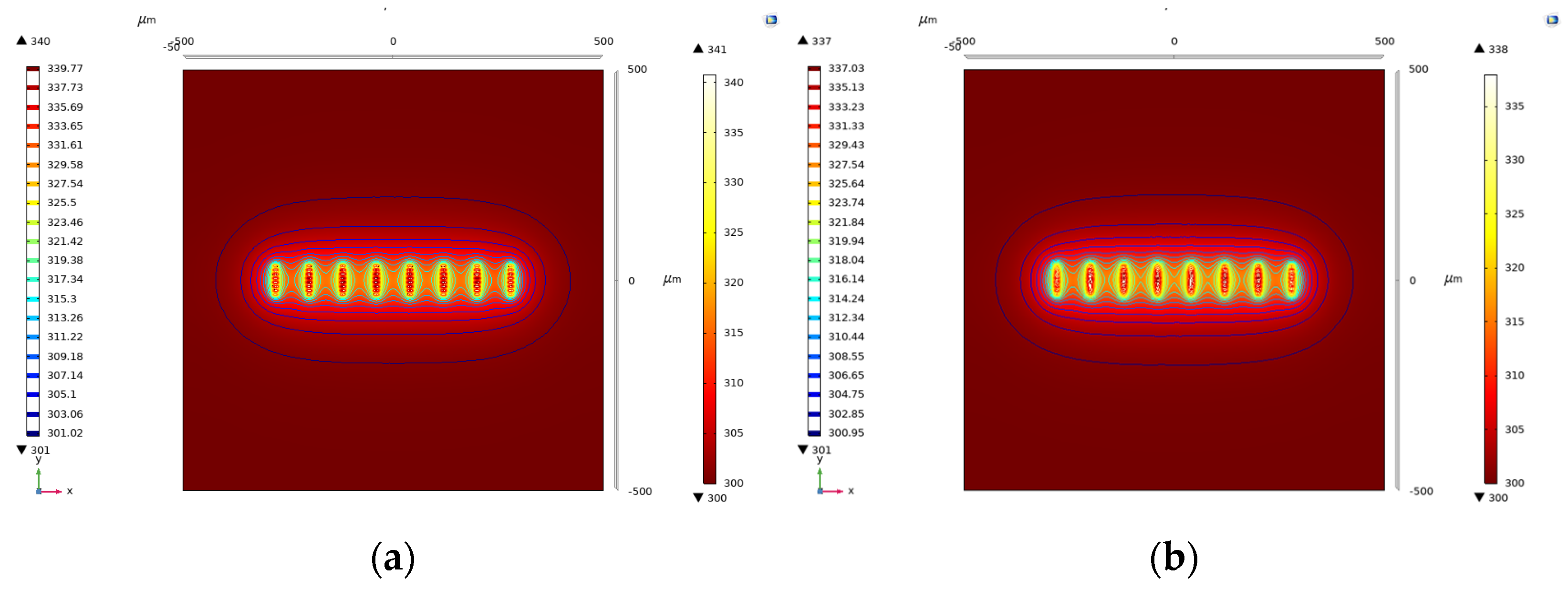

2.4. Temperature Distribution of Multi-Tube Parallel Units

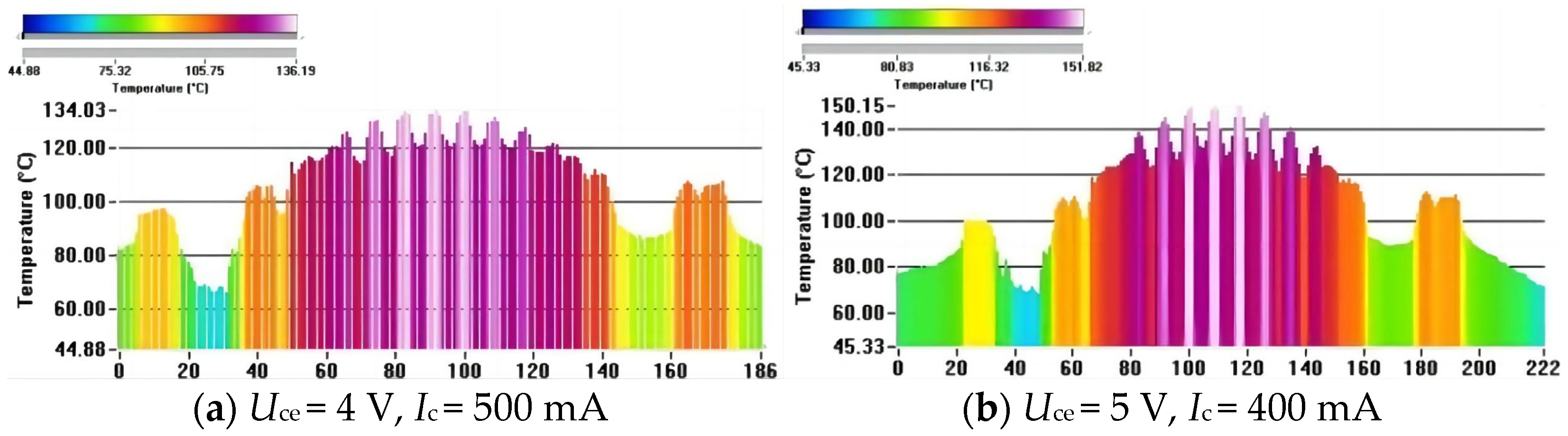

3. Experiment and Results Analysis

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Darwish, A.; Bayba, A.J.; Hung, H.A. Channel temperature analysis of GaN HEMTs with nonlinear thermal conductivity. IEEE Trans. Electron Devices 2015, 62, 840–846. [Google Scholar] [CrossRef]

- Gao, G.B.; Li, X.X. Reliability Physics; Science Press: Beijing, China, 1987; pp. 126–138. [Google Scholar]

- Barradas, F.M.; Tome, P.M.; Gomes, J.M.; Cunha, T.R.; Cabral, P.M.; Pedro, J.C. Power, linearity, and efficiency prediction for MIMO arrays with antenna coupling. IEEE Trans. Microw. Theory Tech. 2017, 65, 5284–5297. [Google Scholar] [CrossRef]

- Boulgheb, A.; Lakhdara, M.; Latreche, S. Improvement of the self-heating performance of an advanced SiGe HBT transistor through the Peltier effect. IEEE Trans. Electron Devices 2021, 68, 479–484. [Google Scholar] [CrossRef]

- Ju, I.; Gong, Y.; Cressler, J.D. Highly linear high-power 802.11 ac/ax WLAN SiGe HBT power amplifiers with a compact 2nd-harmonic-shorted four-way transformer and a thermally compensating dynamic bias circuit. IEEE J. Solid-State Circuits 2020, 55, 2356–2370. [Google Scholar] [CrossRef]

- D’Esposito, R.; Balanethiram, S.; Battaglia, J.L.; Frégonèse, S.; Zimmer, T. Thermal penetration depth analysis and impact of the BEOL metals on the thermal impedance of SiGe HBTs. IEEE Electron Device Lett. 2017, 38, 1457–1460. [Google Scholar] [CrossRef]

- Darwish, A.M.; Hung, H.A.; Bayba, A.J.; El-Kinawi, K. Accurate calculation of junction temperature of HBTs. IEEE Trans. Microw. Theory Tech. 2011, 59, 652–659. [Google Scholar] [CrossRef]

- Goh, G.; Kim, U.; Jeon, M.S.; Kim, J. A simple extraction method of thermal resistance in multifinger GaAs HBT. IEEE Trans. Electron Devices 2016, 63, 2620–2624. [Google Scholar] [CrossRef]

- Muscato, O.; Di Stefano, V. Local equilibrium and off-equilibrium thermoelectric effects in silicon semiconductors. J. Appl. Phys. 2011, 110, 093706. [Google Scholar] [CrossRef]

- Vitusevich, S.A.; Danylyuk, S.V.; Klein, N.; Petrychuk, M.V.; Avksentyev, A.Y.; Sokolov, V.N.; Kochelap, V.A.; Belyaev, A.E.; Tilak, V.; Smart, J.; et al. Separation of hot-electron and self-heating effects in two-dimensional AlGaN/GaN-based conducting channels. Appl. Phys. Lett. 2003, 82, 748–750. [Google Scholar] [CrossRef]

- Liu, W.; Asheghi, M. Thermal conduction in ultrathin pure and doped single-crystal silicon layers at high temperatures. J. Appl. Phys. 2005, 98, 123523. [Google Scholar] [CrossRef]

- Meneghesso, G.; Meneghini, M.; Zanoni, E. Breakdown mechanisms in AlGaN/GaN HEMTs: An overview. Jpn. J. Appl. Phys. 2014, 53, 100211. [Google Scholar] [CrossRef]

- Sun, X.; Zhang, X.; Sun, Y. Thermal characterization and design of GaAs HBT with heat source drifting effects under large current operating condition. Microelectron. J. 2020, 100, 104779. [Google Scholar] [CrossRef]

- Shi, M. Semiconductor Devices Physics and Technology; Zhao, H.M.; Qian, M.; Huang, Q.P., Translators; Suzhou University Press: Suzhou, China, 2003. [Google Scholar]

- Liu, E.K.; Luo, J.S. Semiconductor Physics; National Defence Industrial Press: Beijing, China, 2007. [Google Scholar]

| Ic/mA | Pdiss/W | Actual Temperature Rise/°C | Power Consumption Polynomial (First Order)/°C | Power Consumption Polynomial (Second Order)/°C | Current-Corrected Model/°C |

|---|---|---|---|---|---|

| 300 | 1.5 | 120.47 | 130.52 | 123.33 | 119.28 |

| 400 | 2.0 | 151.82 | 158.76 | 154.78 | 149.58 |

| 500 | 2.5 | 181.02 | 187.20 | 188.90 | 182.65 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Sun, X.; Yang, Y.; Zhang, C.; Zhang, X.; Tian, T. An Accurate Electro-Thermal Coupling Model of a GaAs HBT Device under Floating Heat Source Disturbances. Micromachines 2023, 14, 2236. https://doi.org/10.3390/mi14122236

Sun X, Yang Y, Zhang C, Zhang X, Tian T. An Accurate Electro-Thermal Coupling Model of a GaAs HBT Device under Floating Heat Source Disturbances. Micromachines. 2023; 14(12):2236. https://doi.org/10.3390/mi14122236

Chicago/Turabian StyleSun, Xiaohong, Yijun Yang, Chaoran Zhang, Xiaodong Zhang, and Ting Tian. 2023. "An Accurate Electro-Thermal Coupling Model of a GaAs HBT Device under Floating Heat Source Disturbances" Micromachines 14, no. 12: 2236. https://doi.org/10.3390/mi14122236

APA StyleSun, X., Yang, Y., Zhang, C., Zhang, X., & Tian, T. (2023). An Accurate Electro-Thermal Coupling Model of a GaAs HBT Device under Floating Heat Source Disturbances. Micromachines, 14(12), 2236. https://doi.org/10.3390/mi14122236