A High-Performance InGaAs Vertical Electron–Hole Bilayer Tunnel Field Effect Transistor with P+-Pocket and InAlAs-Block

Abstract

:1. Introduction

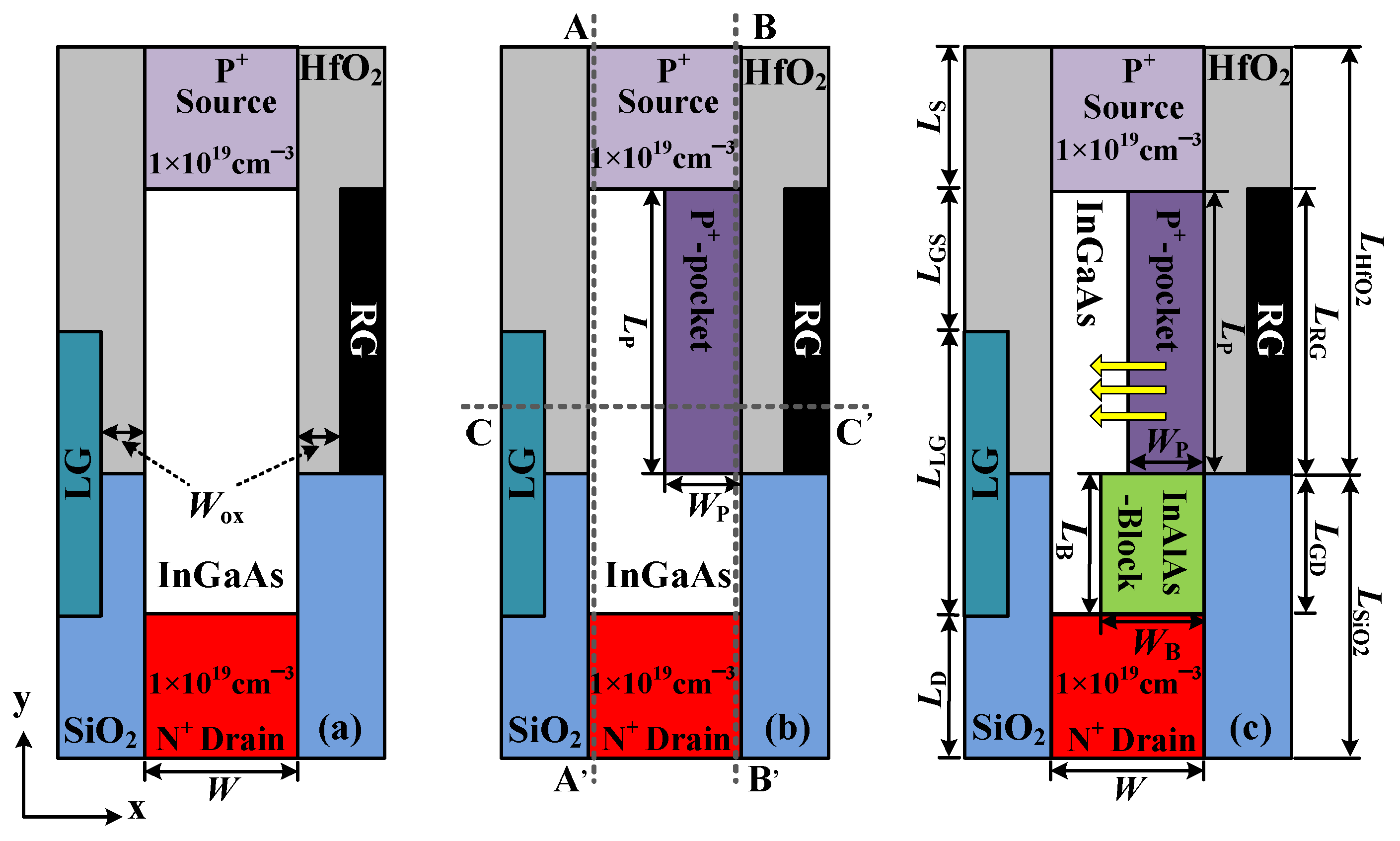

2. Device Structures and Simulation Methods

3. Results and Discussion

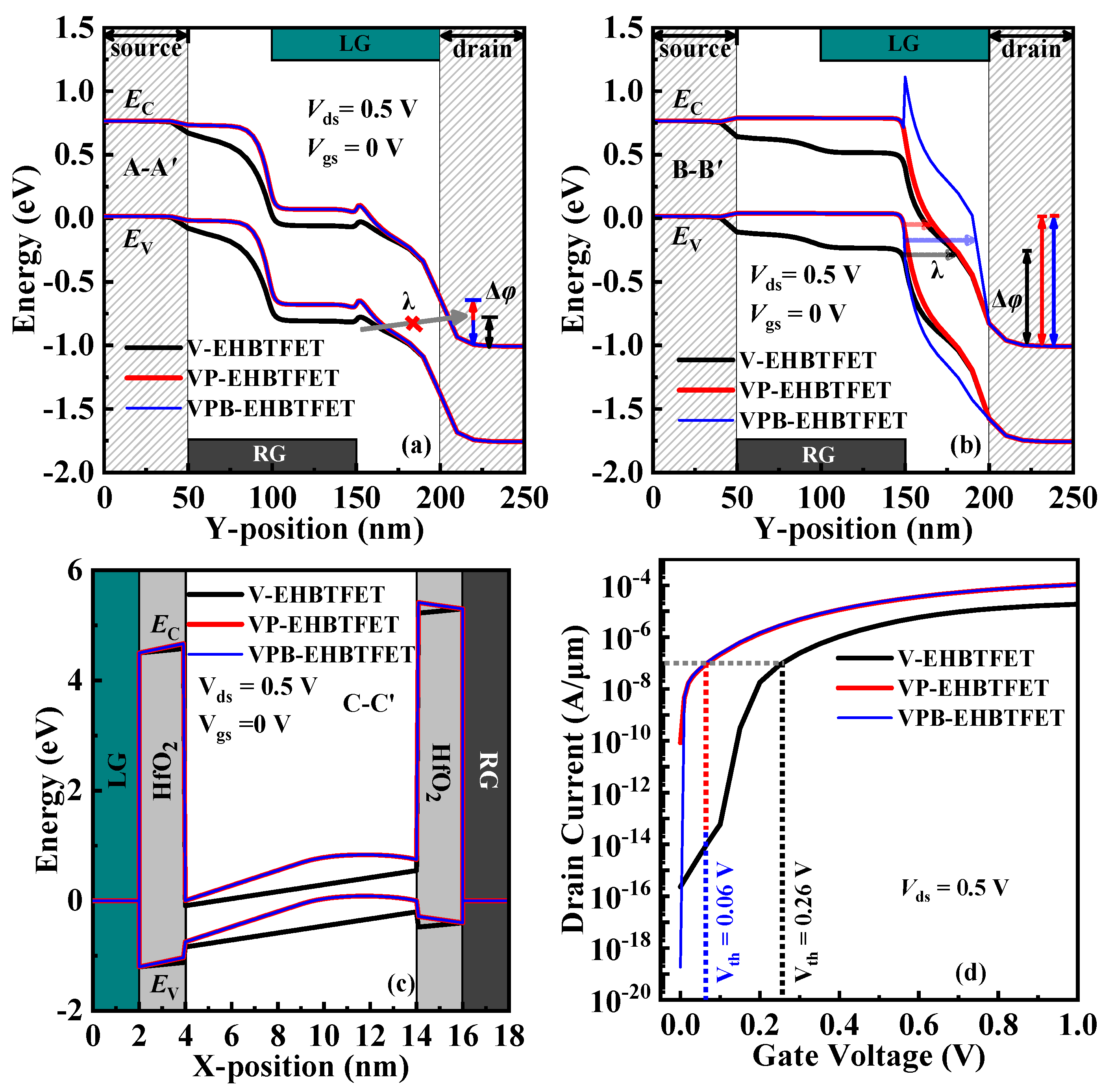

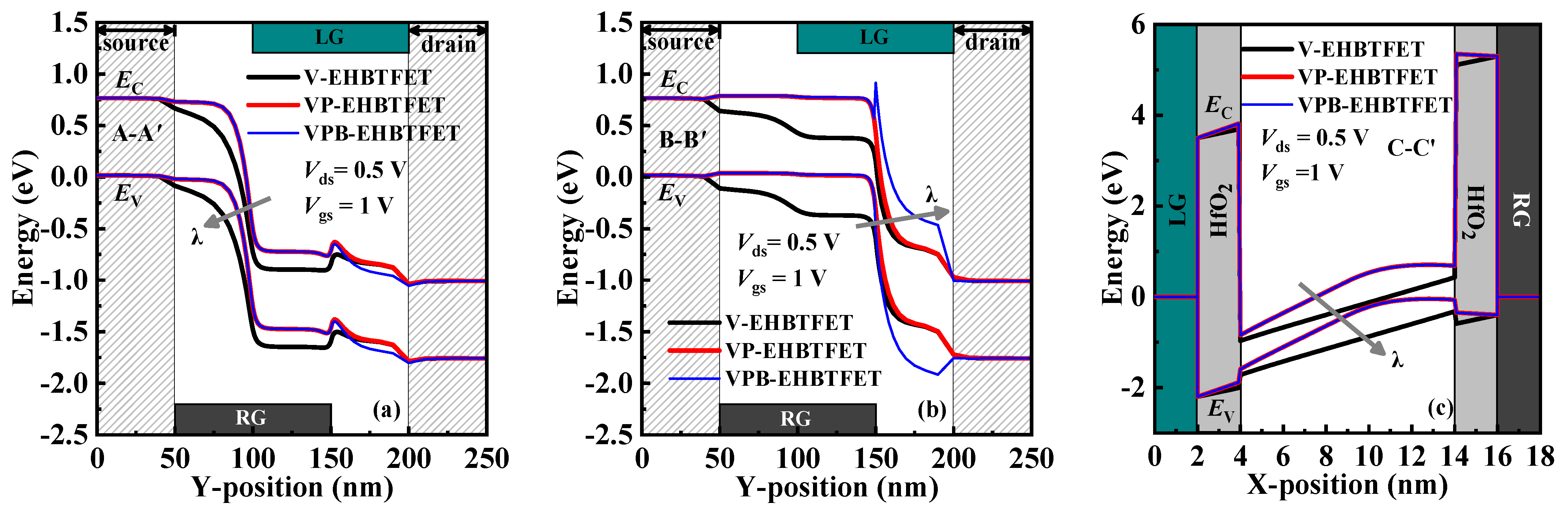

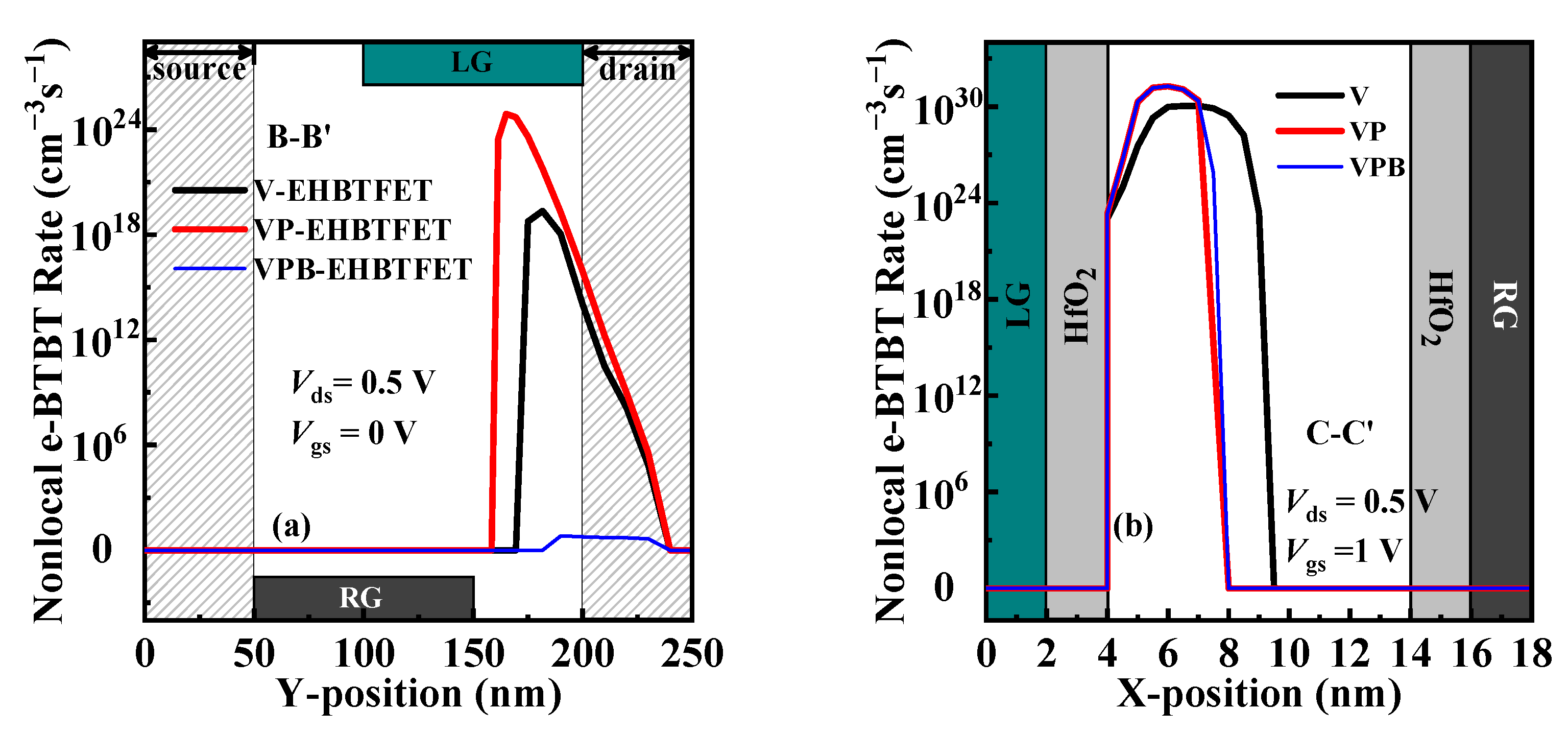

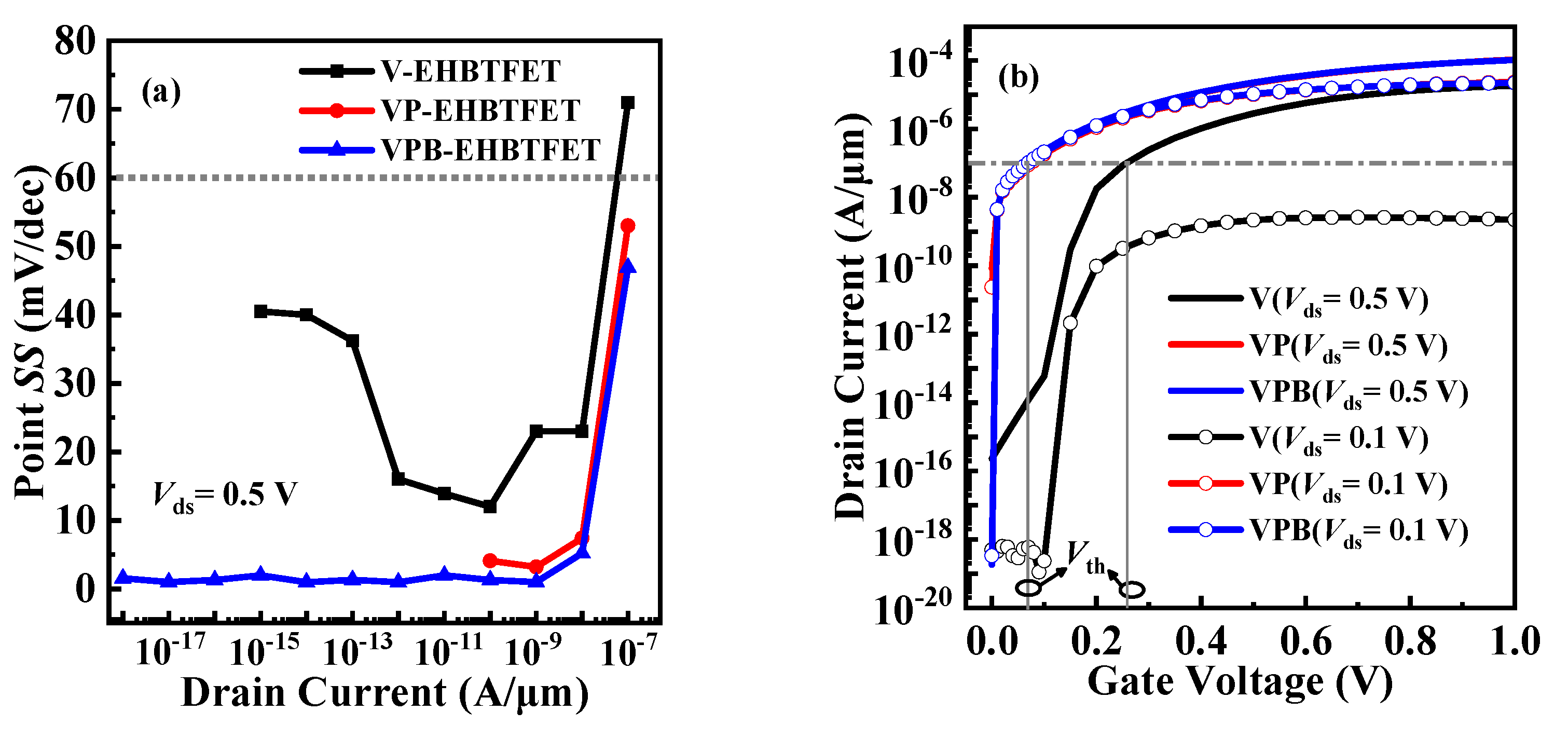

3.1. Performance Comparison between V-EHBTFET, VP-EHBTFET, and VPB-EHBTFET

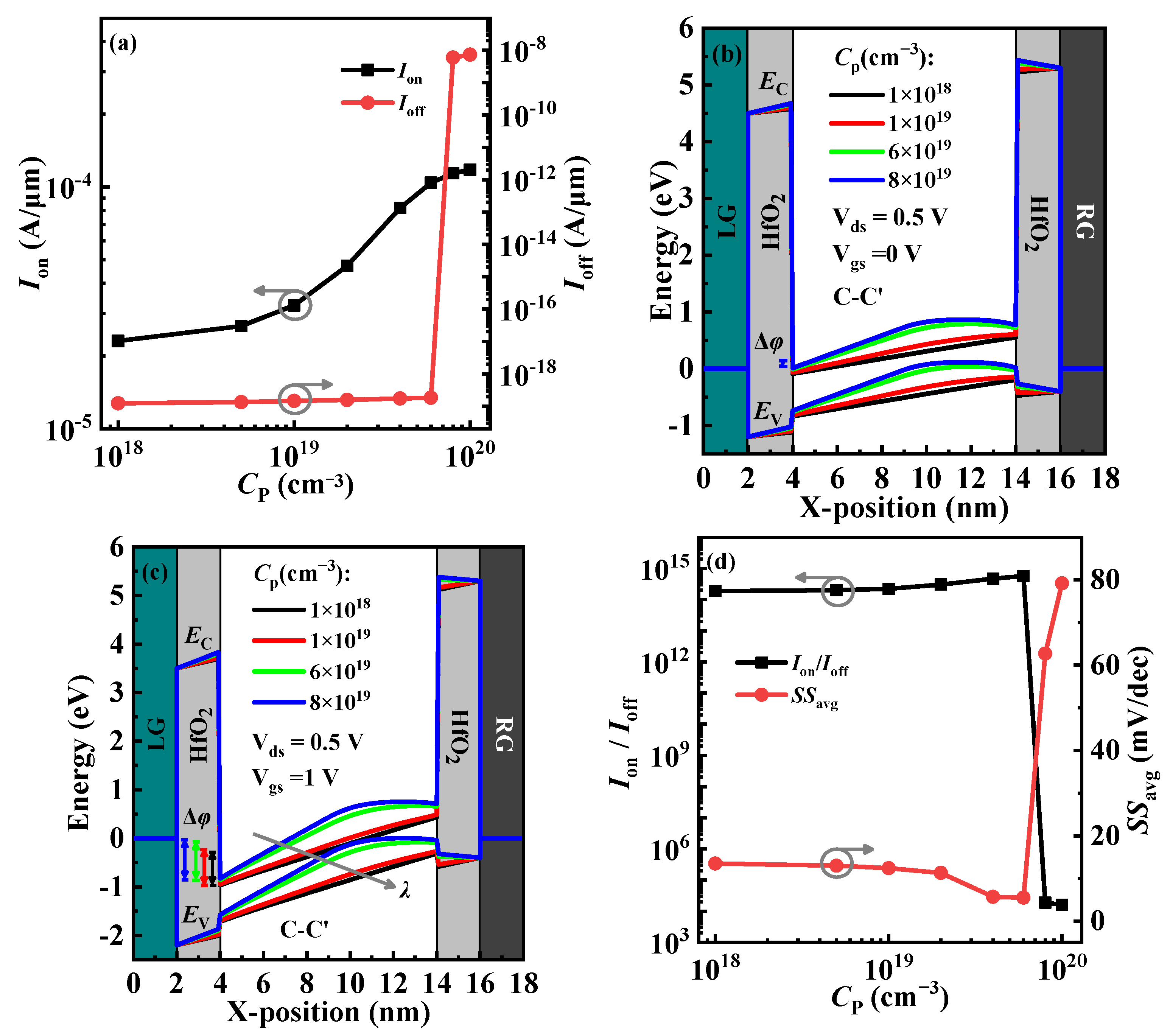

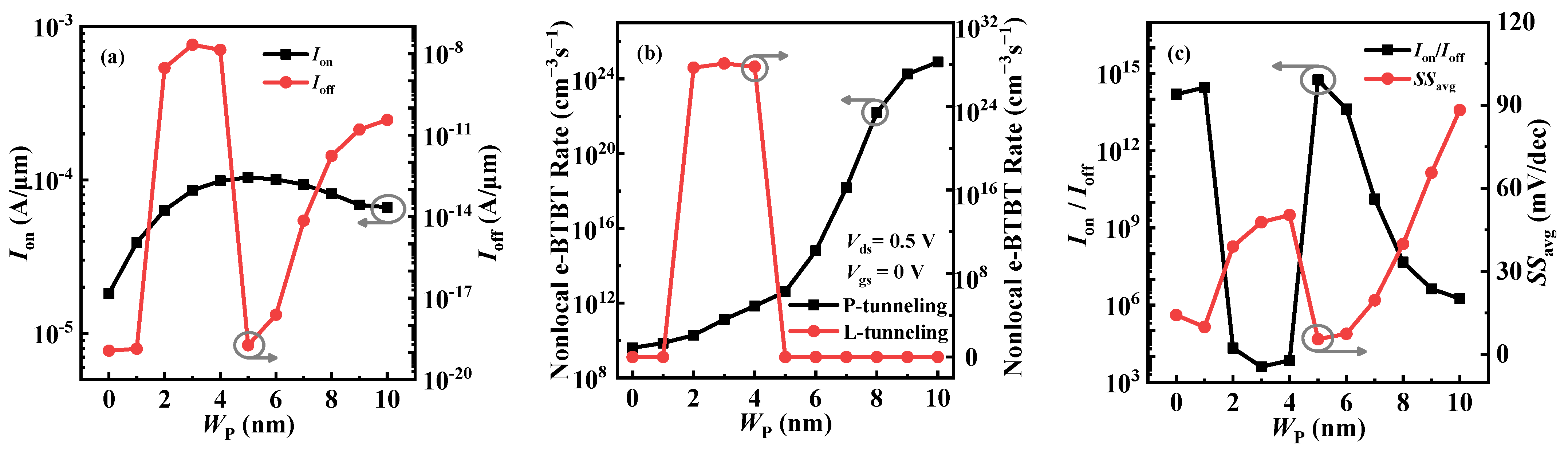

3.2. Effect of P+-Pocket on VPB-EHBTFET

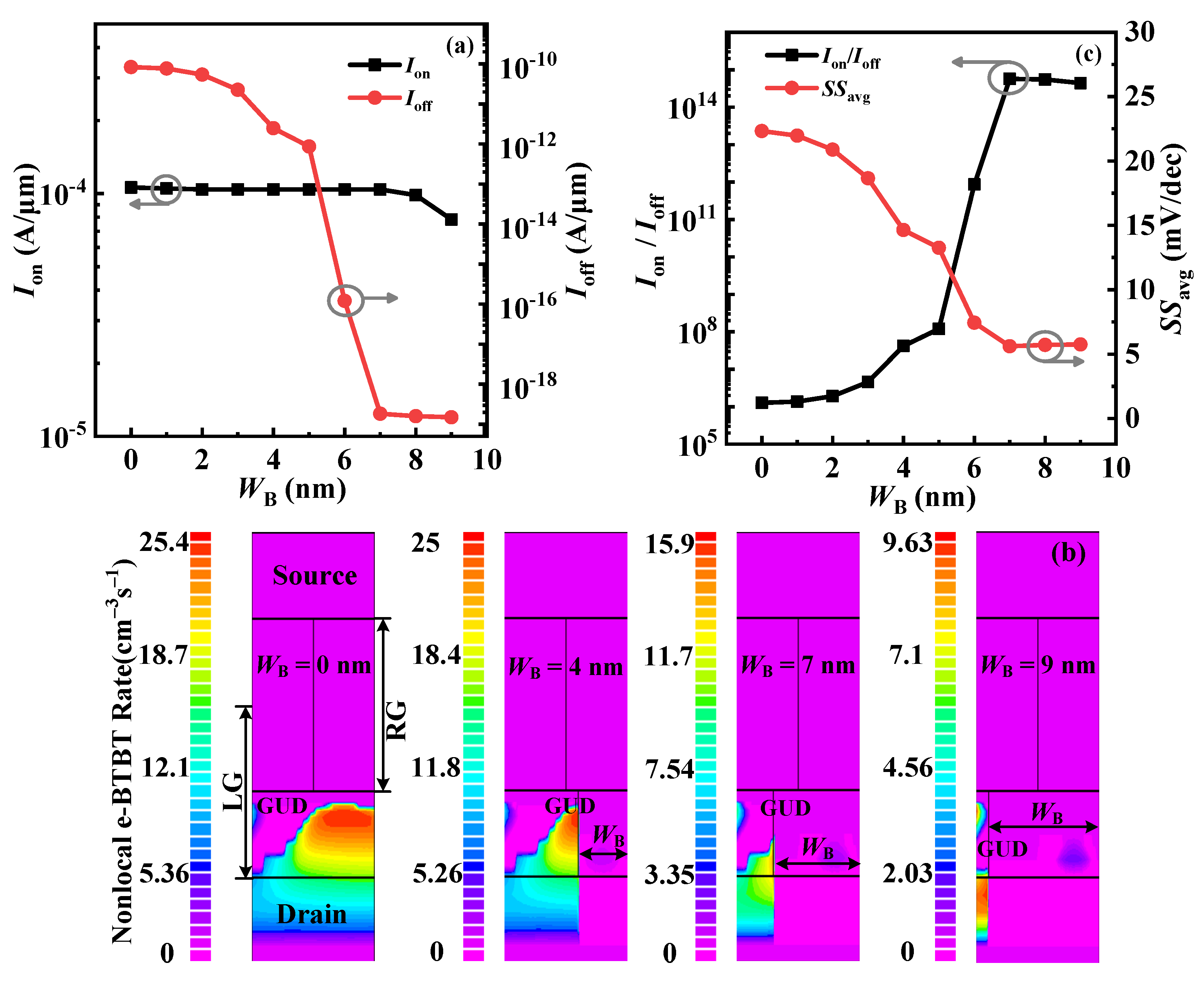

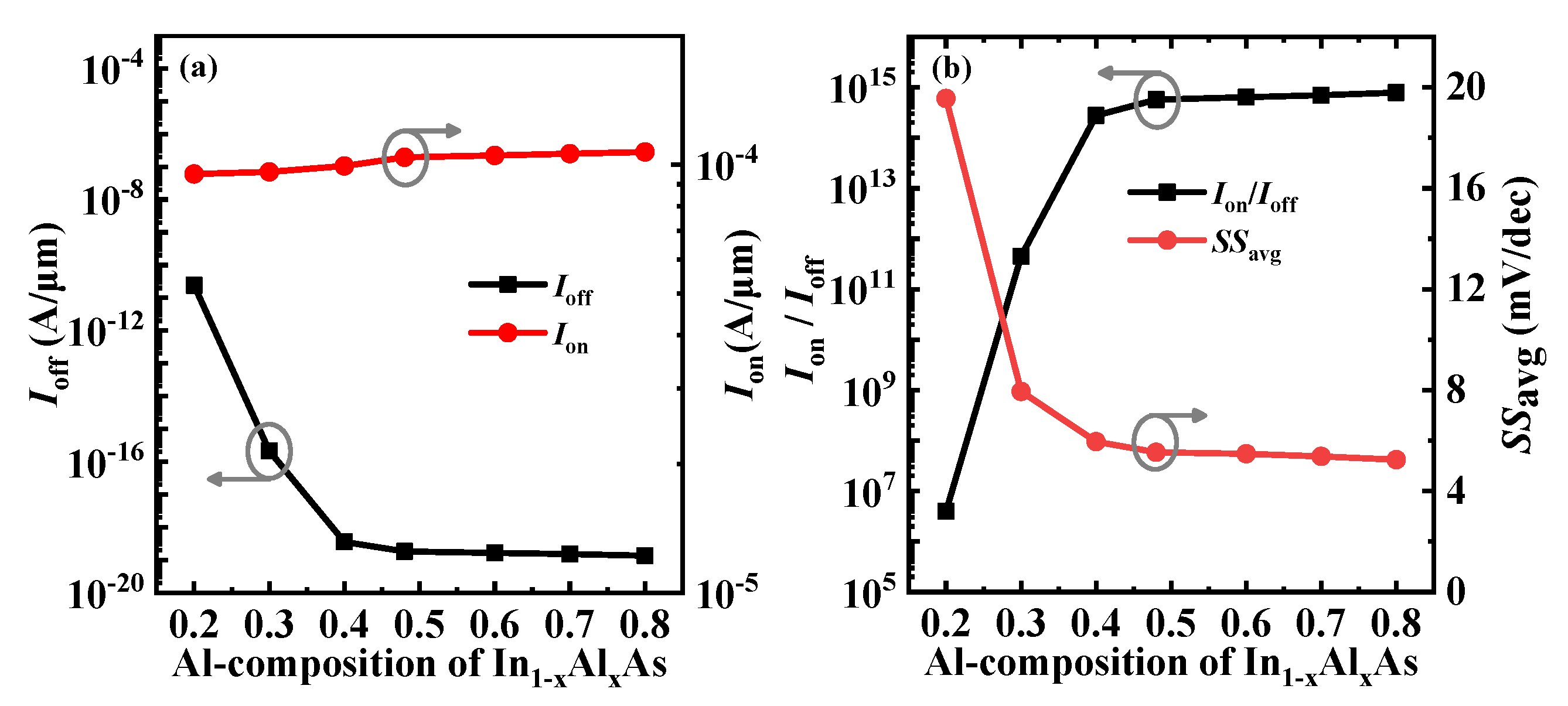

3.3. Effect of InAlAs-Block on VPB-EHBTFET

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Sarkar, D.; Xie, X.J.; Liu, W.; Cao, W.; Kang, J.H.; Gong, Y.J.; Kraemer, S.; Ajayan, P.M.; Banerjee, K. A subthermionic tunnel field-effect transistor with an atomically thin channel. Nature 2015, 526, 91–95. [Google Scholar] [CrossRef] [PubMed]

- Kumar, M.J.; Janardhanan, S. Doping-less tunnel field effect transistor: Design and investigation. IEEE Trans. Electron Devices 2013, 60, 3285–3290. [Google Scholar] [CrossRef]

- Yang, Z.N. Tunnel field-effect transistor with an L-shaped gate. IEEE Electron Device Lett. 2016, 37, 839–842. [Google Scholar] [CrossRef]

- Jiang, X.X.; Shi, X.Y.; Zhang, M.; Wang, Y.R.; Gu, Z.H.; Chen, L.; Zhu, H.; Zhang, K.; Sun, Q.Q.; Zhang, D.W. A symmetric tunnel field-effect transistor based on mos2/black phosphorus/mos2 nanolayered heterostructures. ACS Appl. Nano Mater. 2019, 2, 5674–5680. [Google Scholar] [CrossRef]

- Xu, J.; Jia, J.Y.; Lai, S.; Ju, J.; Lee, S.J. Tunneling field effect transistor integrated with black phosphorus-MoS2 junction and ion gel dielectric. Appl. Phys. Lett. 2017, 110, 033103. [Google Scholar] [CrossRef]

- Chava, P.; Fekri, Z.; Vekariya, Y.; Mikolajick, T.; Erbe, A. Band-to-band tunneling switches based on two-dimensional van der Waals heterojunctions. Appl. Phys. Rev. 2023, 10, 011318. [Google Scholar] [CrossRef]

- Guha, S.; Pachal, P. Heterojunction negative-capacitance tunnel-FET as a promising candidate for sub-0.4 V VDD digital logic circuits. IEEE Trans. Nanotechnol. 2021, 20, 576–583. [Google Scholar] [CrossRef]

- Hu, V.P.H.; Lin, H.H.; Lin, Y.K.; Hu, C.M. Optimization of negative-capacitance vertical-tunnel FET (NCVT-FET). IEEE Trans. Electron Devices 2020, 67, 2593–2599. [Google Scholar] [CrossRef]

- Li, H.; Xu, P.P.; Xu, L.; Zhang, Z.Y.; Lu, J. Negative capacitance tunneling field effect transistors based on monolayer arsenene, antimonene, and bismuthene. Semicond. Sci. Technol. 2019, 34, 085006. [Google Scholar] [CrossRef]

- Liu, H.; Yang, L.A.; Jin, Z.; Hao, Y. An In0.53Ga0.47As/In0.52Al0.48As Heterojunction Dopingless Tunnel FET with a Heterogate Dielectric for High Performance. IEEE Trans. Electron Devices 2019, 66, 3229–3235. [Google Scholar] [CrossRef]

- Tripathy, M.R.; Singh, A.K.; Baral, K.; Singh, P.K.; Jit, S. III-V/Si staggered heterojunction based source-pocket engineered vertical TFETs for low power applications. Superlattices Microstruct. 2020, 142, 106494. [Google Scholar] [CrossRef]

- Ameen, T.A.; Ilatikhameneh, H.; Fay, P.; Seabaugh, A.; Rahman, R.; Klimeck, G. Alloy engineered nitride tunneling field-effect transistor: A solution for the challenge of heterojunction tfets. IEEE Trans. Electron Devices 2019, 66, 736–742. [Google Scholar] [CrossRef]

- Memisevic, E.; Svensson, J.; Lind, E.; Wernersson, L.E. Vertical nanowire TFETs with channel diameter down to 10 nm and point S MIN of 35 mV/decade. IEEE Electron Device Lett. 2018, 39, 1089–1091. [Google Scholar] [CrossRef]

- Kumar, N.; Raman, A. Performance Assessment of the Charge-Plasma-Based Cylindrical GAA Vertical Nanowire TFET With Impact of Interface Trap Charges. IEEE Trans. Electron Devices 2019, 66, 4453–4460. [Google Scholar] [CrossRef]

- Kumar, N.; Raman, A. Prospective sensing applications of novel heteromaterial based dopingless nanowire-TFET at low operating voltage. IEEE Trans. Nanotechnol. 2020, 19, 527–534. [Google Scholar] [CrossRef]

- Cherik, I.C.; Mohammadi, S. Germanium-source L-shaped TFET with dual in-line tunneling junction. Appl. Phys. A 2021, 127, 525. [Google Scholar] [CrossRef]

- Xie, H.W.; Liu, H.X. Design and investigation of a dual source and U-shaped gate TFET with n buffer and SiGe pocket. AIP Adv. 2020, 10, 055125. [Google Scholar] [CrossRef]

- Li, W.; Jia, Q.R.; Pan, Y.M.; Chen, X.A.; Yin, Y.; Wu, Y.P.; Wang, Y.C.; Wen, Y.; Wang, C.; Wang, S.X. A T-shaped gate tunneling field effect transistor with negative capacitance, super-steep subthreshold swing. Nanotechnology 2021, 32, 395202. [Google Scholar] [CrossRef] [PubMed]

- LattanzioL, L.; Michielis, D.; Ionescu, A.M. The electron–hole bilayer tunnel FET. Solid-State Electron. 2012, 74, 85–90. [Google Scholar] [CrossRef]

- Padilla, J.L.; Medina-Bailon, C.; Alper, C.; Gamiz, F.; Ionescuet, A.M. Confinement-induced InAs/GaSb heterojunction electron–hole bilayer tunneling field-effect transistor. Appl. Phys. Lett. 2018, 112, 182101. [Google Scholar] [CrossRef]

- Anam, A.; Kumar, N.; Amin, S.I.; Prasad, D.; Anand, S. Charge-plasma based symmetrical-gate complementary electron–hole bilayer TFET with improved performance for sub-0.5 V operation. Semicond. Sci. Technol. 2023, 38, 015012. [Google Scholar] [CrossRef]

- Ahangari, Z. Design and performance optimization of thin film tin monoxide (SnO)/silicon electron–hole bilayer tunnel field-effect transistor. J. Comput. Electron. 2020, 19, 1485–1493. [Google Scholar] [CrossRef]

- Alper, C.; Palestri, P.; Padilla, J.L.; Ionescu, A.M. Underlap counterdoping as an efficient means to suppress lateral leakage in the electron–hole bilayer tunnel FET. Semicond. Sci. Technol. 2016, 31, 045001. [Google Scholar] [CrossRef]

- Jeong, W.J.; Kim, T.K.; Moon, J.M.; Park, M.G.; Yoon, Y.G.; Hwang, B.W.; Choi, W.Y.; Shin, M.; Lee, S.H. Germanium electron–hole bilayer tunnel field-effect transistors with a symmetrically arranged double gate. Semicond. Sci. Technol. 2015, 30, 035021. [Google Scholar] [CrossRef]

- Padilla, J.L.; Medina-Bailon, C.; Navarro, C.; Alper, C.; Gamiz, F.; Ionescu, A.M. Analysis of the heterogate electron–hole bilayer tunneling field-effect transistor with partially doped channels: Effects on tunneling distance modulation and occupancy probabilities. IEEE Trans. Electron Devices 2018, 65, 339–346. [Google Scholar] [CrossRef]

- Ashita; Loan, S.A.; Alharbi, A.G.; Rafat, M. Ambipolar leakage suppression in electron–hole bilayer TFET: Investigation and analysi. J. Comput. Electron. 2018, 17, 977–985. [Google Scholar] [CrossRef]

- Ahangari, Z. Performance investigation of steep-slope core–shell nanotube indium nitride electron–hole bilayer tunnel field effect transistor. Appl. Phys. A Mater. Sci. Process. 2019, 125, 405. [Google Scholar] [CrossRef]

- Kim, S.; Choi, W.Y.; Park, B.G. Vertical-Structured Electron-Hole Bilayer Tunnel Field-Effect Transistor for Extremely Low-Power Operation with High Scalability. IEEE Trans. Electron Devices 2018, 65, 2010–2015. [Google Scholar] [CrossRef]

- Liu, H.; Zhang, W.T.; Wang, Z.X.; Li, Y.; Zhang, H.W. OFF-State Leakage Suppression in Vertical Electron–Hole Bilayer TFET Using Dual-Metal Left-Gate and N+-Pocket. Materials 2022, 15, 6924. [Google Scholar] [CrossRef]

- Iida, R.; Kim, S.H.; Yokoyama, M.; Taoka, N.; Lee, S.H.; Takenaka, M.; Takagi, S. Planar-type In0.53Ga0.47As channel band-to-band tunneling metal-oxide-semiconductor field-effect transistors. J. Appl. Phys. 2011, 100, 124505. [Google Scholar] [CrossRef]

- Suzuki, R.; Taoka, N.; Yokoyama, M.; Lee, S.; Kim, S.H.; Hoshii, T.; Yasuda, T.; Jevasuwan, W.; Maeda, T.; Ichikawa, O.; et al. 1-nm-capacitance-equivalent-thickness HfO2/Al2O3/InGaAs metal-oxide-semiconductor structure with low interface trap density and low gate leakage current density. Appl. Phys. Lett. 2012, 100, 132906. [Google Scholar] [CrossRef]

- Zhou, G.L.; Lu, Y.Q.; Li, R.; Zhang, Q.; Hwang, W.S.; Liu, Q.M.; Vasen, T.; Chen, C.; Zhu, H.J.; Kuo, J.M.; et al. Vertical InGaAs/InP Tunnel FETs with Tunneling Normal to the Gate. IEEE Electron Device Lett. 2011, 32, 1516–1518. [Google Scholar] [CrossRef]

- Zhao, H.; Huang, J.; Chen, Y.T.; Yum, J.H.; Wang, Y.Z.; Zhou, F.; Xue, F.; Lee, J.C. Effects of gate-first and gate-last process on interface quality of In0.53Ga0.47As metal-oxide-semiconductor capacitors using atomic-layer-deposited Al2O3 and HfO2 oxides. Appl. Phys. Lett. 2009, 95, 253501. [Google Scholar] [CrossRef]

- Hueting, R.J.E.; Rajasekharan, B.; Salm, C.; Schmitz, J. The Charge Plasma P-N Diode. IEEE Electron Device Lett. 2008, 29, 1367–1369. [Google Scholar] [CrossRef]

- Lide, D.R. CRC Handbook of Chemistry and Physics, 89th ed.; Taylor and Francis: New York, NY, USA, 2008; p. 12. [Google Scholar]

| Parameters | Value |

|---|---|

| Source length (LS) | 50 nm |

| Gate/source space (LGS) | 50 nm |

| Left gate length (LLG) | 100 nm |

| Drain length (LD) | 50 nm |

| Right gate length (LRG) | 100 nm |

| HfO2 length (LHfO2) | 150 nm |

| P+-pocket length (Lp) | 100 nm |

| P+-pocket width (Wp) | 5 nm |

| InAlAs-block length (LB) | 50 nm |

| InAlAs-block width (WB) | 7 nm |

| SiO2 length (LSiO2) | 100 nm |

| Gate/drain space (LGD) | 50 nm |

| Bulk material width (W) | 10 nm |

| Dielectric width (Wox) | 2 nm |

| Left gate work-function | 4.5 eV |

| Right gate work-function | 5.3 eV |

| Device | IOFF (A/μm) | ION (A/μm) | ION/IOFF | Vth (V) | SSavg (mV/dec) | DIBL (mV/V) |

|---|---|---|---|---|---|---|

| V-EHBTFET | 2.29 × 10−16 | 1.84 × 10−5 | 8.0 × 1010 | 0.26 | 30.2 | N/A |

| VP-EHBTFET | 8.37 × 10−11 | 1.04 × 10−4 | 1.2 × 106 | 0.06 | 22.1 | 7.5 |

| VPB-EHBTFET | 1.83 × 10−19 | 1.04 × 10−4 | 5.7 × 1014 | 0.06 | 5.5 | 7.5 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Liu, H.; Li, P.; Zhou, X.; Wang, P.; Li, Y.; Pan, L.; Zhang, W.; Li, Y. A High-Performance InGaAs Vertical Electron–Hole Bilayer Tunnel Field Effect Transistor with P+-Pocket and InAlAs-Block. Micromachines 2023, 14, 2049. https://doi.org/10.3390/mi14112049

Liu H, Li P, Zhou X, Wang P, Li Y, Pan L, Zhang W, Li Y. A High-Performance InGaAs Vertical Electron–Hole Bilayer Tunnel Field Effect Transistor with P+-Pocket and InAlAs-Block. Micromachines. 2023; 14(11):2049. https://doi.org/10.3390/mi14112049

Chicago/Turabian StyleLiu, Hu, Peifeng Li, Xiaoyu Zhou, Pengyu Wang, Yubin Li, Lei Pan, Wenting Zhang, and Yao Li. 2023. "A High-Performance InGaAs Vertical Electron–Hole Bilayer Tunnel Field Effect Transistor with P+-Pocket and InAlAs-Block" Micromachines 14, no. 11: 2049. https://doi.org/10.3390/mi14112049

APA StyleLiu, H., Li, P., Zhou, X., Wang, P., Li, Y., Pan, L., Zhang, W., & Li, Y. (2023). A High-Performance InGaAs Vertical Electron–Hole Bilayer Tunnel Field Effect Transistor with P+-Pocket and InAlAs-Block. Micromachines, 14(11), 2049. https://doi.org/10.3390/mi14112049