Analysis of SiC/Si Heterojunction Band Energy and Interface State Characteristics for SiC/Si VDMOS

Abstract

:1. Introduction

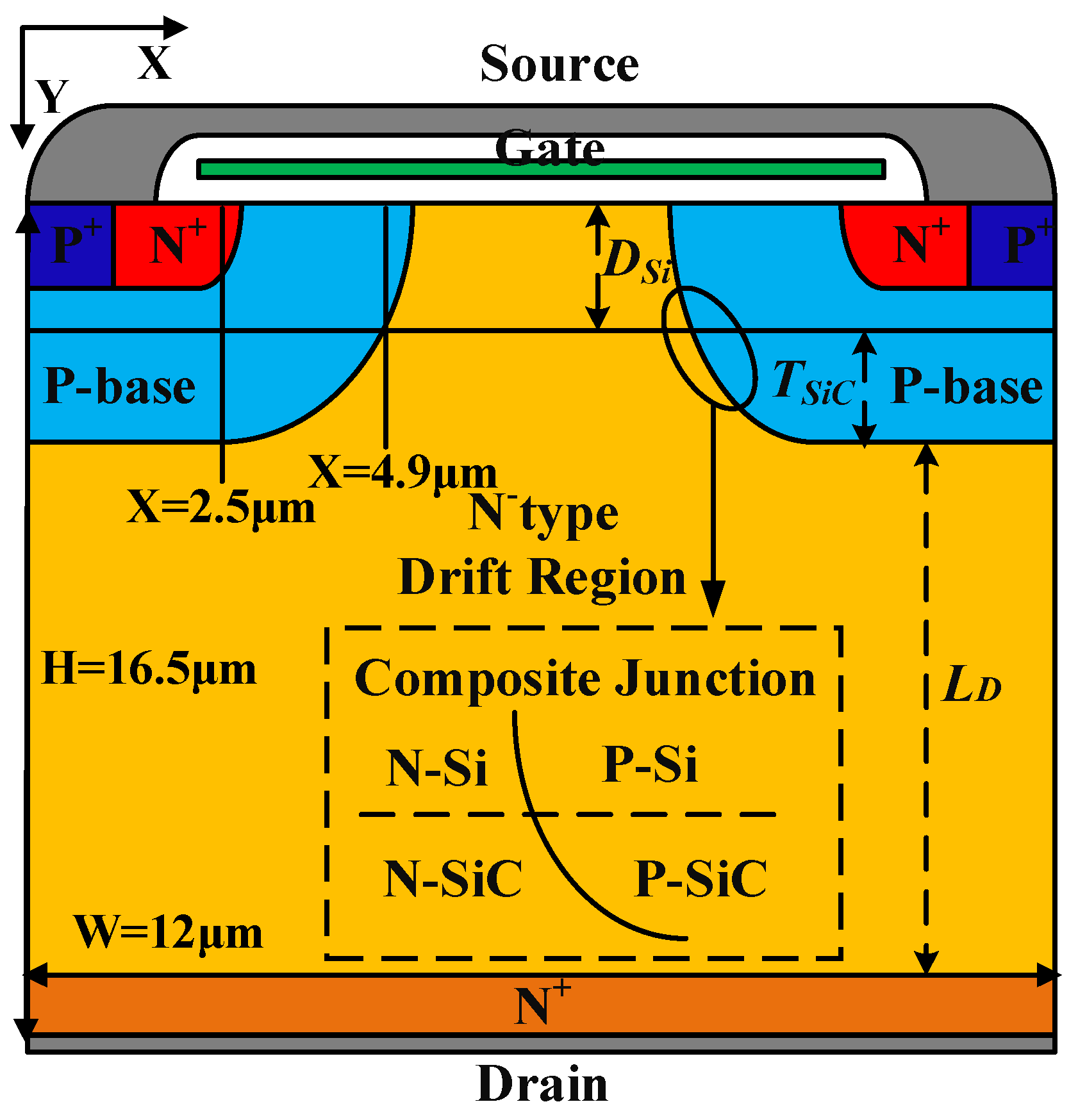

2. Materials and Methods

3. Results and Discussion

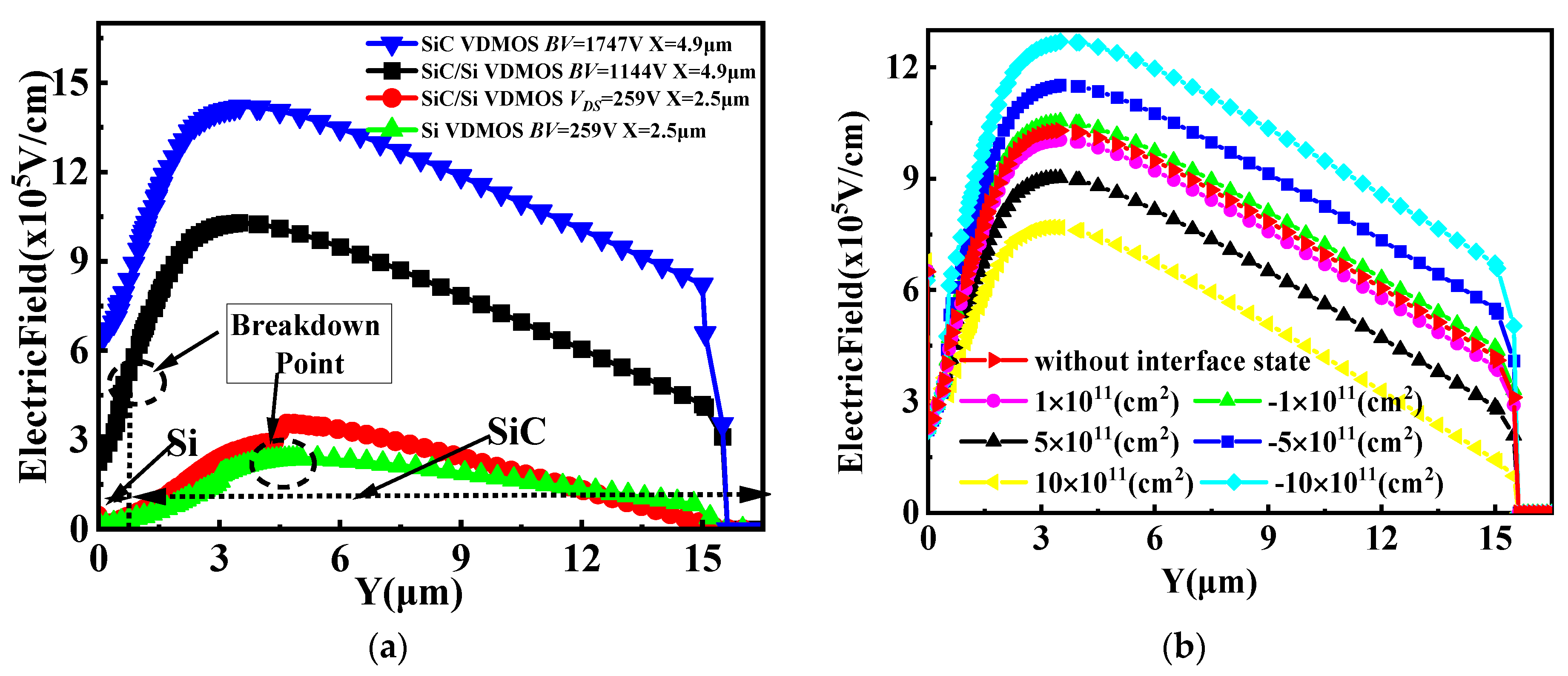

3.1. The Influence of Interface State on Electrical Parameters

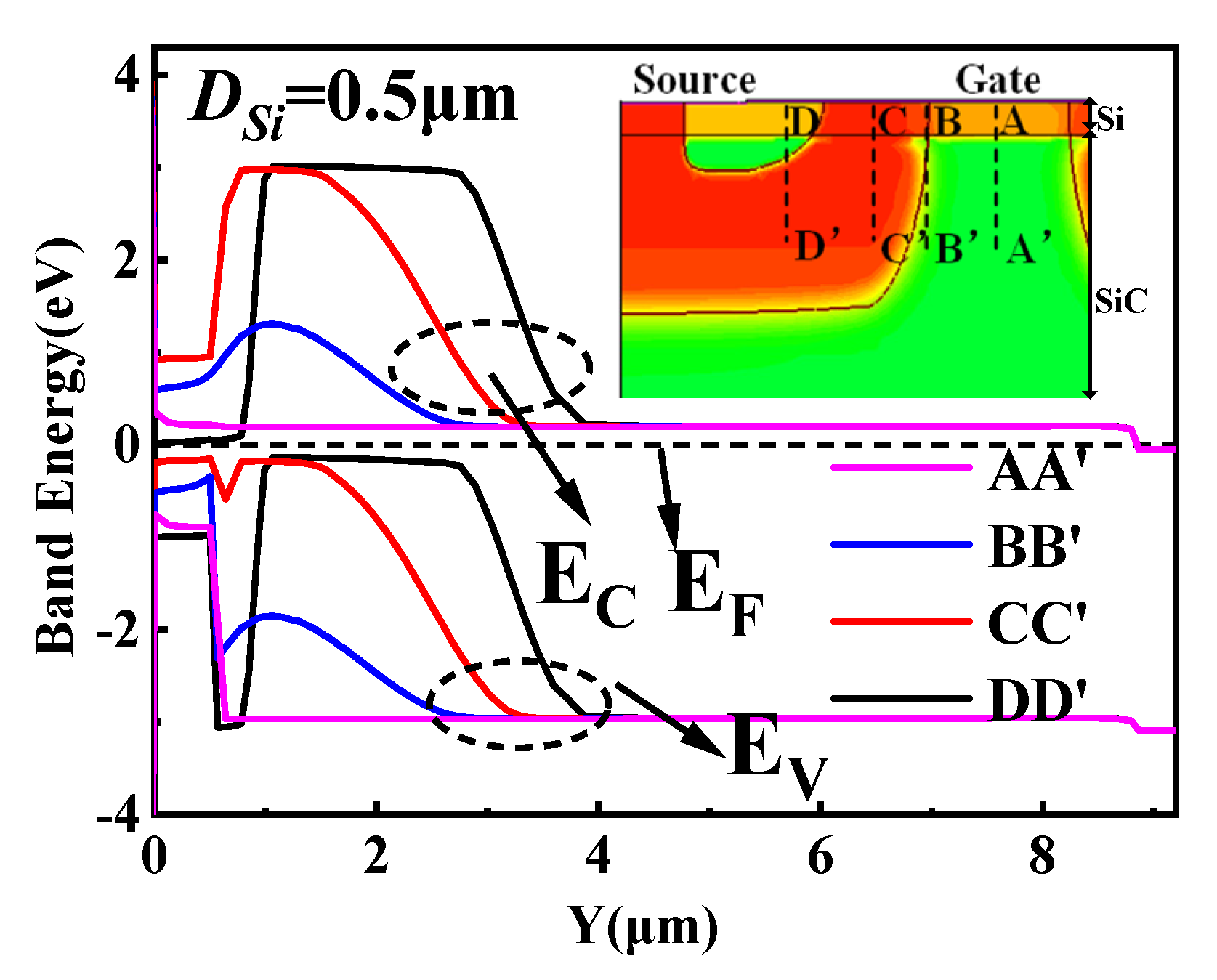

3.2. The Influence of Interface State on Band Energy Distributions

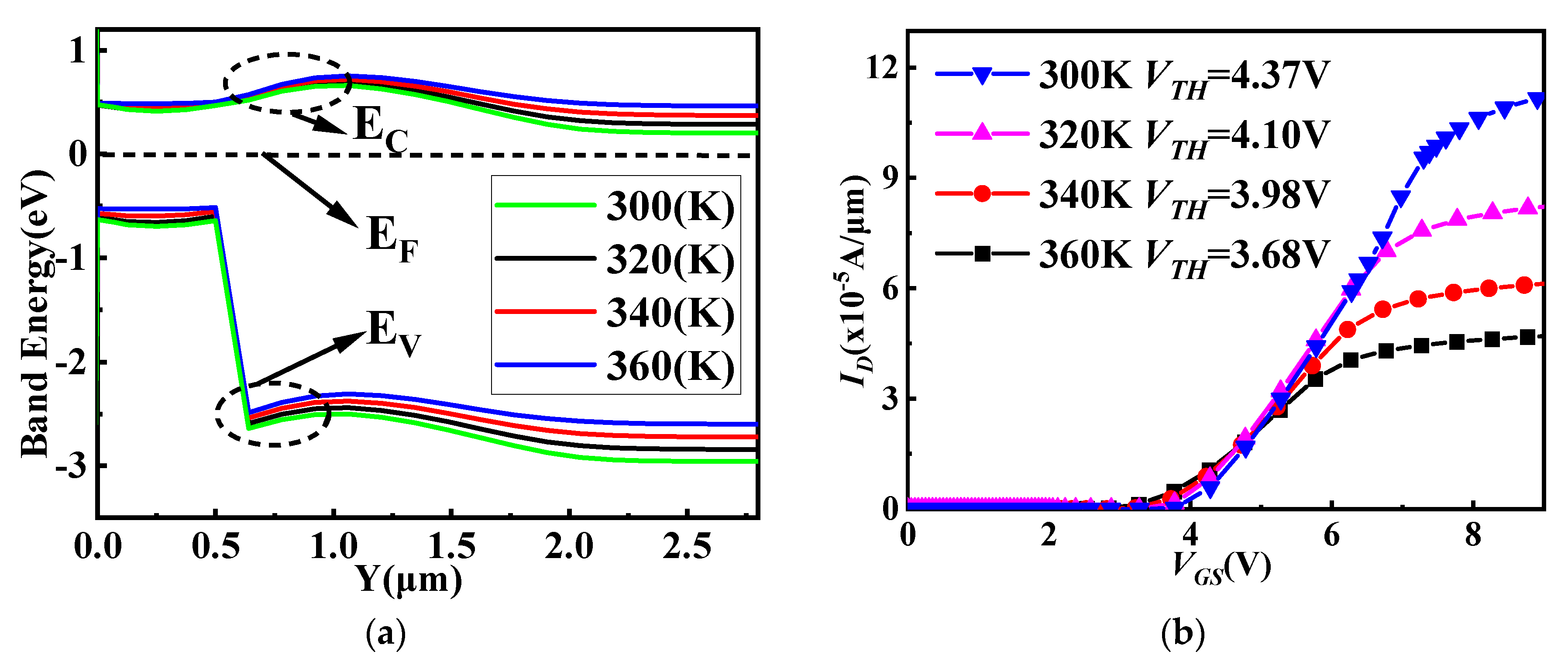

3.3. The Influence of Interface State on Temperature Effects

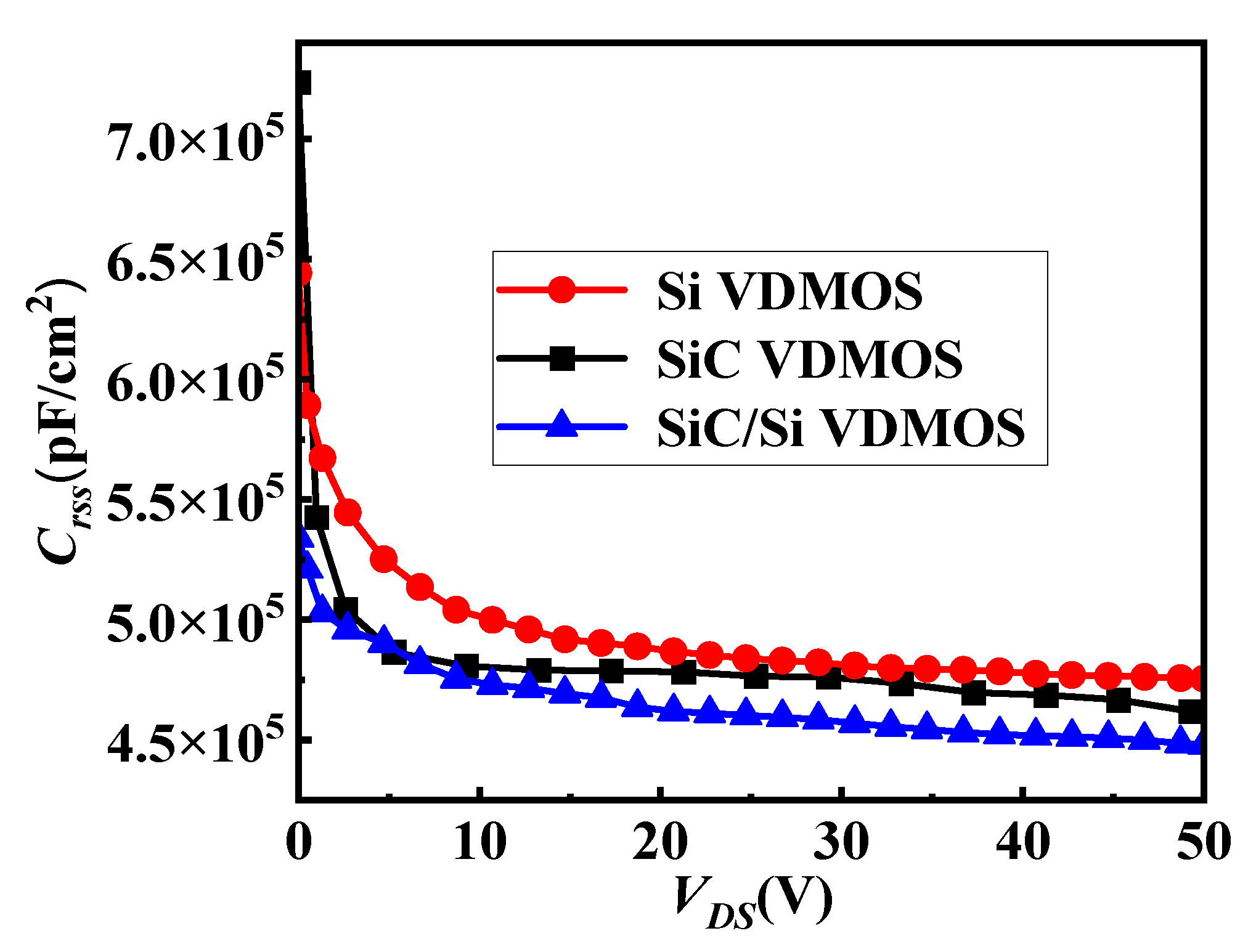

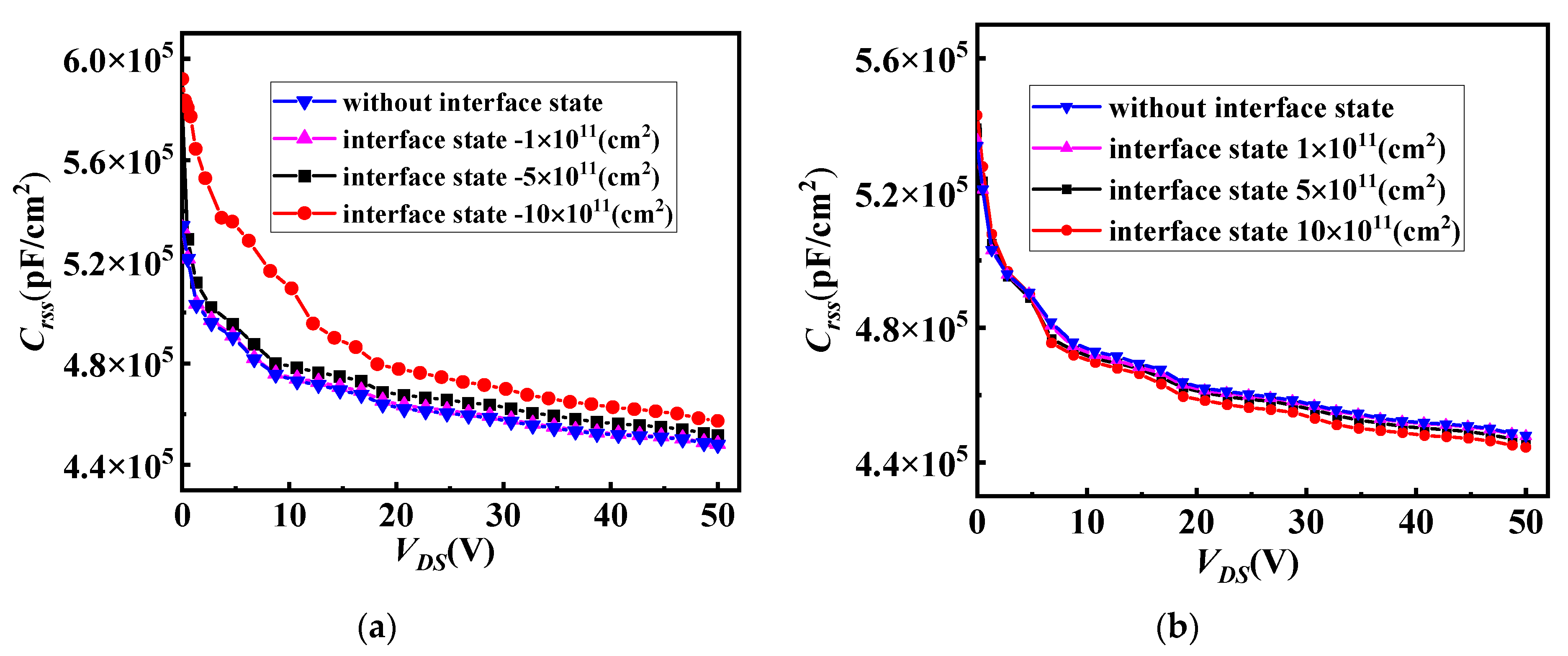

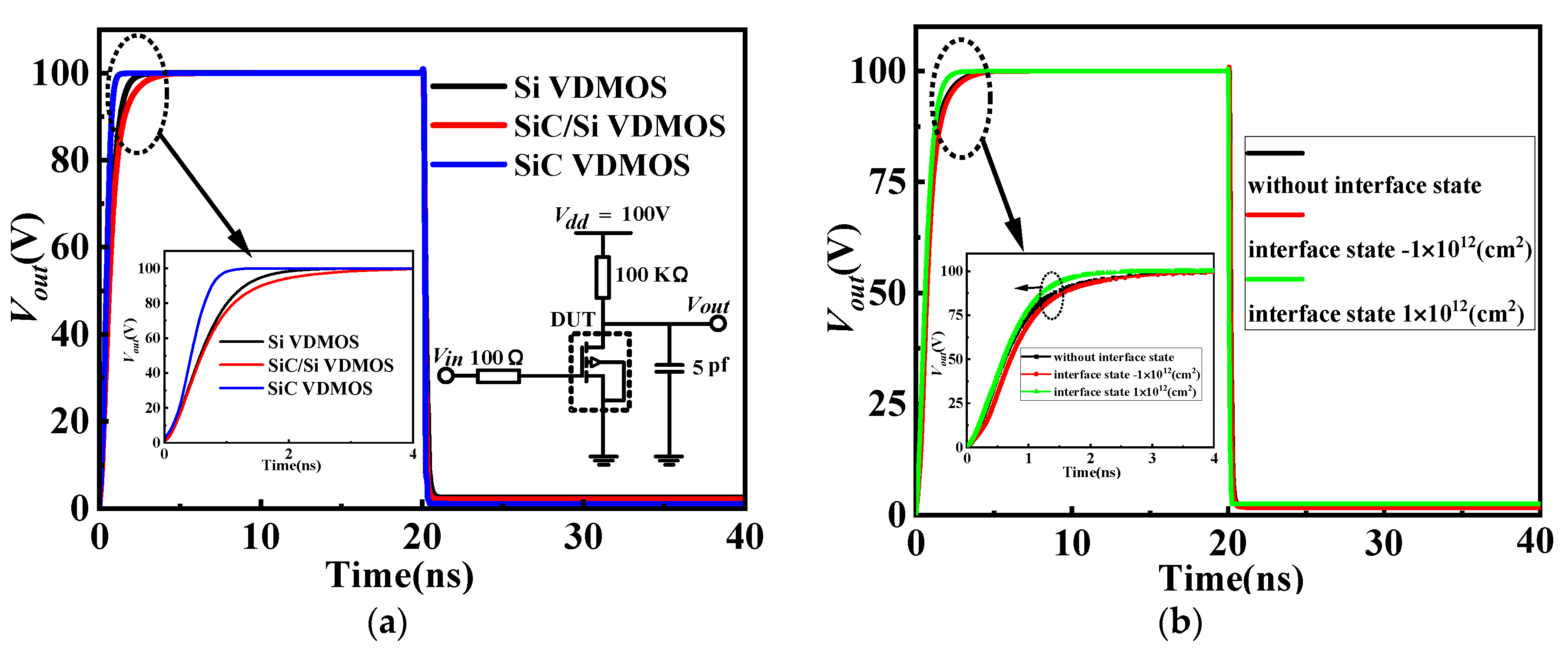

3.4. The Influence of Interface State on Interface Capacitances and Switching Performances

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Baliga, B.J. Fundamentals of Power Semiconductor Devices; Springer-Science: New York, NY, USA, 2008. [Google Scholar]

- Thapar, N.; Baliga, B. Influence of the Trench Corner Design on Edge Termination of UMOS Power Devices. Solid-State Electron. 1997, 41, 1929–1936. [Google Scholar] [CrossRef]

- Chen, X.-B.; Sin, J. Optimization of the specific on-resistance of the COOLMOS. IEEE Trans. Electron Devices 2001, 48, 344–348. [Google Scholar] [CrossRef]

- Lidow, A.; Herman, T.; Collins, H.W. Power MOSFET technology. In Proceedings of the International Electron Devices Meeting, Washington, DC, USA, 3–5 December 1979; Volume 25, pp. 79–85. [Google Scholar] [CrossRef]

- Baliga, B.J. The future of power semiconductor device technology. Proc. IEEE 2001, 89, 822–832. [Google Scholar] [CrossRef]

- Huang, H.M.; Chen, X.-B. Optimization of Specific On-Resistance of Balanced Symmetric Super junction MOSFETs Based on a Better Approximation of Ionization Integral. IEEE Trans. Electron Devices 2012, 59, 2742–2747. [Google Scholar] [CrossRef]

- Udrea, F.; Deboy, G.; Fujihira, T. Superjunction Power Devices, History, Development, and Future Prospects. IEEE Trans. Electron Devices 2017, 64, 713–727. [Google Scholar] [CrossRef]

- Luo, X.; Jiang, Y.H.; Zhou, K.; Wang, P.; Wang, X.W.; Wang, Q.; Yao, G.L.; Zhang, B.; Li, Z.J. Ultralow Specific On-Resistance Superjunction Vertical DMOS With High-K Dielectric Pillar. IEEE Electron Device Lett. 2012, 33, 1042–1044. [Google Scholar] [CrossRef]

- Luo, X.; Tan, Q.; Wei, J.; Zhou, K.; Deng, G.; Li, Z.; Zhang, B. Ultralow ON-Resistance High-Voltage p-Channel LDMOS With an Accumulation-Effect Extended Gate. IEEE Trans. Electron Devices 2016, 63, 2614–2619. [Google Scholar] [CrossRef]

- Ohta, K.; Morimoto, M.; Saitoh, M.; Fukuda, T.; Morino, A.; Shimizu, K.; Hayashi, Y.; Tarui, Y. A high-speed logic LSI using diffusion self-aligned enhancement depletion MOS IC. IEEE J. Solid-State Circuits 1975, 10, 314–321. [Google Scholar] [CrossRef]

- Chen, X.; Huang, M. A Vertical Power MOSFET With an Interdigitated Drift Region Using High-k Insulator. IEEE Trans. Electron Devices 2012, 59, 2430–2437. [Google Scholar] [CrossRef]

- Cao, Z.; Duan, B.X.; Cai, H.; Yuan, S.; Yang, Y.T. Theoretical Analyses of Complete 3-D Reduced Surface Field LDMOS With Folded-Substrate Breaking Limit of Superjunction LDMOS. IEEE Trans. Electron Devices 2016, 63, 4865–4872. [Google Scholar] [CrossRef]

- Duan, B.; Cao, Z.; Yuan, X.; Yuan, S.; Yang, Y. New Superjunction LDMOS Breaking Silicon Limit by Electric Field Modulation of Buffered Step Doping. IEEE Electron Device Lett. 2014, 36, 47–49. [Google Scholar] [CrossRef]

- Duan, B.; Cao, Z.; Yuan, S.; Yang, Y. Complete 3D-Reduced Surface Field Superjunction Lateral Double-Diffused MOSFET Breaking Silicon Limit. IEEE Electron Device Lett. 2015, 36, 1348–1350. [Google Scholar] [CrossRef]

- Duan, B.; Yang, Y. REBULF super junction MOSFET with N+ buried layer. Micro Nano Lett. 2011, 6, 881–883. [Google Scholar] [CrossRef]

- Duan, B.; Yang, X.; Lv, J.; Yang, Y. Novel SiC/Si Heterojunction Power MOSFET With Breakdown Point Transfer Terminal Technology by TCAD Simulation Study. IEEE Trans. Electron Devices 2018, 65, 3388–3393. [Google Scholar] [CrossRef]

- Duan, B.; Lv, J.; Zhao, Y.; Yang, Y. SiC/Si heterojunction VDMOS breaking silicon limit by breakdown point transfer technology. Micro Nano Lett. 2018, 13, 96–99. [Google Scholar] [CrossRef]

- Yang, X.; Duan, B.; Yang, Y. GaN/Si Heterojunction VDMOS with High Breakdown Voltage and Low Specific On-Resistance. Micromachines 2023, 14, 1166. [Google Scholar] [CrossRef]

- Zhao, D.; Wang, Y.; Chen, Y.; Shao, J.; Fu, Z.; Duan, B.; Liu, F.; Li, X.; Li, T.; Yang, X.; et al. Novel Step Floating Islands VDMOS with Low Specific on-Resistance by TCAD Simulation. Micromachines 2022, 13, 573. [Google Scholar] [CrossRef]

- Saddow, S.E.; Frewin, C.L.; Nezafati, M.; Oliveros, A.; Afroz, S.; Register, J.; Reyes, M.; Thomas, S. 3C-SiC on Si: A bio- and hemo-compatible material for advanced nano-bio devices. In Proceedings of the 2014 IEEE 9th Nanotechnology Materials and Devices Conference (NMDC), Aci Castello, Italy, 12–15 October 2014; pp. 49–53. [Google Scholar]

- Kukushkin, S.A.; Osipov, A.V. Theory and practice of SiC growth on Si and its applications to wide-gap semiconductor films. J. Phys. D. Appl. Phys. 2014, 47, 313001. [Google Scholar] [CrossRef]

- Jennings, M.R.; Pérez-Tomás, A.; Guy, O.J.; Hammond, R.; Burrows, S.E.; Gammon, P.M.; Lodzinski, M.; Covington, J.A.; Mawby, P.A. Si/SiC Heterojunctions Fabricated by Direct Wafer Bonding. Electrochem. Solid-State Lett. 2008, 11, H306–H308. [Google Scholar] [CrossRef]

- Gammon, P.M.; Chan, C.W.; Li, F.; Gity, F.; Trajkovic, T.; Pathirana, V.; Flandre, D.; Kilchytska, V. Development, characterisation and simulation of wafer bonded Si-on-SiC substrates. Mater. Sci. Semicond. Process. 2018, 78, 69–74. [Google Scholar] [CrossRef]

- Sasada, Y.; Kurumi, T.; Shimizu, H.; Kinoshita, H.; Yoshimoto, M. Junction Formation via Direct Bonding of Si and 6H-SiC. Mater. Sci. Forum 2014, 778–780, 714–717. [Google Scholar] [CrossRef]

- Hayashi, T.; Tanaka, H.; Shimoida, Y.; Tanimoto, S.; Hoshi, M. New High-Voltage Unipolar Mode p+ Si/n− 4H-SiC Heterojunction Diode. Mater. Sci. Form 2005, 483–485, 953–956. [Google Scholar] [CrossRef]

- Chen, L.; Guy, O.; Jennings, M.; Igic, P.; Wilks, S.; Mawby, P. Study of a novel Si/SiC hetero-junction MOSFET. Solid-State Electron. 2007, 51, 662–666. [Google Scholar] [CrossRef]

- Liang, J.; Nishida, S.; Hayashi, T.; Arai, M.; Shigekawa, N. Effects of interface state charges on the electrical properties of Si/SiC heterojunctions. Appl. Phys. Lett. 2014, 105, 151607. [Google Scholar] [CrossRef]

- Williams, R.K.; Darwish, M.N.; Blanchard, R.A.; Siemieniec, R.; Rutter, P.; Kawaguchi, Y. The Trench Power MOSFET: Part I—History, Technology, and Prospects. IEEE Trans. Electron Devices 2017, 64, 674–691. [Google Scholar] [CrossRef]

- Williams, R.K.; Darwish, M.N.; Blanchard, R.A.; Siemieniec, R.; Rutter, P.; Kawaguchi, Y. The Trench Power MOSFET—Part II: Application Specific VDMOS, LDMOS, Packaging, and Reliability. IEEE Trans. Electron Devices 2017, 64, 692–712. [Google Scholar] [CrossRef]

- Sung, W.; Baliga, B.J. Monolithically Integrated 4H-SiC MOSFET and JBS Diode (JBSFET) Using a Single Ohmic/Schottky Process Scheme. IEEE Electron Device Lett. 2016, 37, 1605–1608. [Google Scholar] [CrossRef]

- Sung, W.; Baliga, B.J. A Near Ideal Edge Termination Technique for 4500V 4H-SiC Devices: The Hybrid Junction Termination Extension. IEEE Electron Device Lett. 2016, 37, 1609–1612. [Google Scholar] [CrossRef]

- Tega, N.; Hisamoto, D.; Shima, A.; Shimamoto, Y. Channel Properties of SiC Trench-Etched Double-Implanted MOS (TED MOS). IEEE Trans. Electron Devices 2016, 63, 3439–3444. [Google Scholar] [CrossRef]

- Ni, W.; Emori, K.; Marui, T.; Saito, Y.; Yamagami, S.; Hayashi, T.; Hoshi, M. SiC Trench MOSFET with an Integrated Low Von Unipolar Heterojunction Diode. Mater. Sci. Forum 2014, 778–780, 923–926. [Google Scholar] [CrossRef]

- Nazarov, A.N.; Vovk, Y.N.; Lysenko, V.S.; Turchanikov, V.I.; Scryshevskii, V.A.; Ashok, S. Carrier transport in amorphous SiC/crystalline silicon heterojunctions. J. Appl. Phys. 2001, 89, 4422–4428. [Google Scholar] [CrossRef]

- Gammon, P.M.; Pérez-Tomás, A.; Jennings, M.R.; Sanchez, A.M.; Fisher, C.A.; Thomas, S.M.; Donnellan, B.T.; Mawby, P.A. Bipolar Conduction across a Wafer Bonded p-n Si/SiC Heterojunction. Mater. Sci. Forum 2013, 740–742, 1006–1009. [Google Scholar] [CrossRef]

- Su, J.; Niu, Q.; Zhang, D.; Zhang, Y.; Fu, Z. Carrier transport mechanisms of p-SiC/n-Si hetero-junctions. Solid State Sci. 2011, 13, 434–437. [Google Scholar] [CrossRef]

- Nishida, S.; Liang, J.; Hayashi, T.; Arai, M.; Shigekawa, A. Correlation between the electrical properties of p-Si/n-4H-SiC junctions and concentrations of acceptors in Si. Jpn. J. Appl. Phys. 2015, 54, 030210. [Google Scholar] [CrossRef]

- Raghunathan, R.; Alok, D.; Baliga, B. High voltage 4H-SiC Schottky barrier diodes. IEEE Electron Device Lett. 1995, 16, 226–227. [Google Scholar] [CrossRef]

- Raghunathan, R.; Baliga, B.J. Role of defects in producing negative temperature dependence of breakdown voltage in SiC. Appl. Phys. Lett. 1998, 72, 3196–3198. [Google Scholar] [CrossRef]

- Kimoto, T.; Urushidani, T.; Kobayashi, S.; Matsunami, H. High-voltage (>1 kV) SiC Schottky barrier diodes with low on-resistances. IEEE Electron Device Lett. 1993, 14, 548–550. [Google Scholar] [CrossRef]

- Licciardo, G.D.; Di Benedetto, L.; Bellone, S. Modeling of the SiO2/SiC Interface-Trapped Charge as a Function of the Surface Potential in 4H-SiC Vertical-DMOSFET. IEEE Trans. Electron Devices 2016, 63, 1783–1787. [Google Scholar] [CrossRef]

- Wang, Y.; Ma, Y.-C.; Hao, Y.; Hu, Y.; Wang, G.; Cao, F. Simulation Study of 4H-SiC UMOSFET Structure With p+-polySi/SiC Shielded Region. IEEE Trans. Electron Devices 2017, 64, 3719–3724. [Google Scholar] [CrossRef]

- Wang, Y.; Wang, H.-Y.; Cao, F.; Wang, H.-Y. High Performance of Polysilicon/4H-SiC Dual-Heterojunction Trench Diode. IEEE Trans. Electron Devices 2017, 64, 1653–1659. [Google Scholar] [CrossRef]

- Chan, C.; Mawby, P.A.; Gammon, P.M. Analysis of Linear-Doped Si/SiC Power LDMOSFETs Based on Device Simulation. IEEE Trans. Electron Devices 2016, 63, 2442–2448. [Google Scholar] [CrossRef]

- Chan, C.W.; Li, F.; Sanchez, A.; Mawby, P.A.; Gammon, P.M. Comparative study of RESURF Si/SiC LDMOSFETs for high-temperature applications using TCAD modeling. IEEE Trans. Electron Devices 2017, 64, 3713–3718. [Google Scholar] [CrossRef]

- Araki, R.; Shimizu, H.; Kurumi, T.; Kinoshita, H.; Yoshimoto, M. Drain current -gate voltage characteristics of Si MOSFETs fabricated on Si-on-SiC wafers. In Proceedings of the 2011 International Meeting for Future of Electron Devices, Osaka, Japan, 19–20 May 2011; pp. 68–69. [Google Scholar]

- Tanaka, H.; Hayashi, T.; Shimoida, Y.; Yamagami, S.; Tanimoto, S.; Hoshi, M. Ultra-low von and high voltage 4H-SiC heterojunction diode. In Proceedings of the 17th International Symposium on Power Semiconductor Devices and ICs, Santa Barbara, CA, USA, 23–26 May 2005; pp. 287–290. [Google Scholar] [CrossRef]

| Device | Si VDMOS | SiC/Si VDMOS | SiC VDMOS |

|---|---|---|---|

| Dsi (μm) | / | 0.5 | / |

| TSiC (μm) | / | 3 | / |

| LD (μm) | 12 | 12 | 12 |

| ND (cm−3) | 6 × 1014 | 3.3 × 1015 | 5 × 1015 |

| Np (cm−3) | 5 × 1017 | 5 × 1017 | 5 × 1017 |

| NSUB (cm−3) | 1 × 1014 | 1 × 1014 | 1 × 1014 |

| Device | Si VDMOS (LD = 12 μm) | SiC/Si VDMOS (LD = 12 μm) | SiC VDMOS (LD = 12 μm) | GaN/Si VDMOS (LD = 20 μm) |

|---|---|---|---|---|

| BV(V) | 259 | 1144 | 1747 | 2029 |

| Ron,sp (mΩ·cm2) | 18.2 | 6.03 | 5.03 | 17.2 |

| FOM (MW/cm2) | 3.68 | >217 | 607 | 2939.4 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Yang, X.; Duan, B.; Yang, Y. Analysis of SiC/Si Heterojunction Band Energy and Interface State Characteristics for SiC/Si VDMOS. Micromachines 2023, 14, 1890. https://doi.org/10.3390/mi14101890

Yang X, Duan B, Yang Y. Analysis of SiC/Si Heterojunction Band Energy and Interface State Characteristics for SiC/Si VDMOS. Micromachines. 2023; 14(10):1890. https://doi.org/10.3390/mi14101890

Chicago/Turabian StyleYang, Xin, Baoxing Duan, and Yintang Yang. 2023. "Analysis of SiC/Si Heterojunction Band Energy and Interface State Characteristics for SiC/Si VDMOS" Micromachines 14, no. 10: 1890. https://doi.org/10.3390/mi14101890

APA StyleYang, X., Duan, B., & Yang, Y. (2023). Analysis of SiC/Si Heterojunction Band Energy and Interface State Characteristics for SiC/Si VDMOS. Micromachines, 14(10), 1890. https://doi.org/10.3390/mi14101890