Abstract

Ultra-wideband (UWB) technology has been applied in many fields, such as radar and indoor positioning, because of its advantages of having a high transmission rate, anti-multipath interference, and good concealment. In the UWB physical layer, the transmitting link, including an encoder and a pulse generator, is used to improve the anti-interference ability of the signal, while the receiving link, including a receiver and a decoder, can correct the error signal. Therefore, the performance of the UWB physical layer can obviously affect the speed and quality of UWB signal transmission. In this paper, the structure and performance of the codec and transceiver of the UWB physical layer are introduced and compared. In addition, some typical architectures and features are summarized and discussed, which provides a valuable reference and suggestions for the design of the UWB physical layer. Finally, the outlook of the UWB physical layer is presented: its development direction mainly includes high speed, low power consumption, and fewer hardware resources.

1. Introduction

Ultra-wideband (UWB) technology has attracted attention for its advantages such as its high transmission rate, anti-multipath interference, and good robustness [1,2,3]. Due to the advantages of requiring low power, having a small size, and strong penetration, the UWB system has been widely applied in many fields such as indoor positioning [4,5,6,7,8], wireless body area network [9,10,11,12], and radar [13,14,15]. It has become one of the most important technologies in wireless communication research. Specifically, the UWB physical layer can achieve data transmitting, which is an important part of the UWB system. Therefore, the investigation of the UWB physical layer is essential.

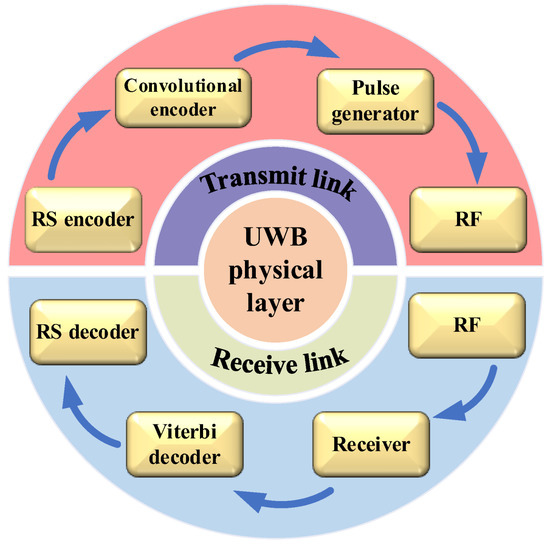

The UWB physical layer transceiver link structure is shown in Figure 1 [16]. Reed Solomon (RS) encoders are used for payload bits from the physical layer to increase its antijamming ability [17]. Then, a convolutional encoder is used to sort the RS encoded data. A scrambler is inserted into the transmitting link to increase the antijamming capability [18]. The encoded data are emitted by a pulse generator [19,20]. After receiving the information, the receiver demodulates the data, and then decodes the data through a Viterbi decoder and an RS decoder, respectively, to obtain the information [21,22,23,24].

Figure 1.

Structure of UWB physical layer.

The performance of the UWB physical layer determines the speed and accuracy of data transmission, so its investigation is essential to improve the transmitting performance [25]. However, the traditional UWB physical layer cannot satisfy the high requirements of speed and accuracy. Firstly, the coding speed of traditional encoders is slow when large amounts of data are encoded. Secondly, a pulse generator can interfere with the narrow band systems. Additionally, the receiver can be interfered with in a multipath environment. In addition, the complex algorithm can increase hardware resources and power consumption when decoding data. Therefore, the UWB physical layer transceiver link faces the following challenges:

- (1)

- High-speed encoders are required to deal with large amounts of encoded data;

- (2)

- Interference between UWB and other narrowband systems should be reduced;

- (3)

- The anti-multipath capability of the receiver should be improved;

- (4)

- A low-complexity algorithm is needed for the decoder to reduce hardware resources.

In this paper, the development and prospects of the UWB physical layer transceiver are reviewed to provide valuable references for designing a high-performance UWB physical layer. Section 2 introduces the encoder module of the UWB transmitting link. The UWB pulse generator module is introduced in Section 3. Section 4 introduces the receiver module. In Section 5, the decoder module of the UWB receiver link is presented. Finally, a summary and outlook of the UWB physical layer are presented.

2. Encoder

The encoder is used to add a check bit for data, which can improve its anti-interference ability in channel transmission. In a UWB transmitting link, the encoder module is composed of an RS encoder, a convolution encoder, and a scrambler.

2.1. RS Encoder

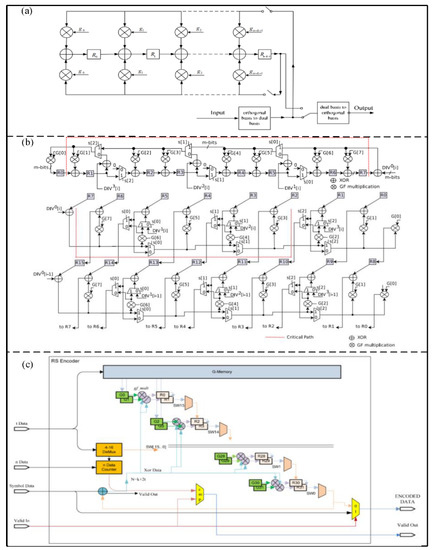

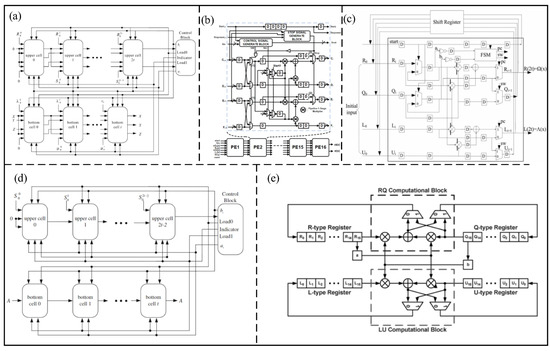

An RS encoder is widely used in wireless communication, digital broadcasting, television, and deep space exploration. The speed of a traditional RS encoder is slow, and it can be blocked when encoding a large amount of data, which can reduce the encoding efficiency. In order to deal with this problem, Ren et al. [26] proposed a bit-parallel multiplication RS encoder based on a dual basis, as shown in Figure 2a. All multiplication and addition operations are applied to the dual-basis encoder, and a pipeline structure is adopted in the proposed algorithm, which can greatly increase the encoder efficiency. In addition, Mohamed et al. [27] proposed a linear feedback shift register (LFSR) RS encoder based on a vector string/parallel divider, as shown in Figure 2b. Multiple division operations can be performed in parallel in the proposed architecture. Compared with a traditional RS encoder with a polynomial length of 17, the proposed structure can improve throughput by about 83.3%.

Generally, traditional RS encoders occupy a large area and heavy hardware resources. Jitawutipoka et al. [28] proposed a Galois domain multiplier based on subexpression sharing to reduce hardware resources, which can reduce the number of exclusive OR (XOR) gates. Moreover, Wu et al. [29] optimized the multiplication algorithm by logical algebra to further decrease the number of XOR gates in the adder. For an RS (255,239) encoder, the number of total XOR gates without the optimization algorithm is 366. However, those in [28,29] are 276 and 246, respectively.

In order to solve the problem of different encoder rates in different channels, Lee et al. [30] proposed an RS encoder with extra memory, as shown in Figure 2c. The proposed architecture can provide adaptive bit rates according to the characteristics of irregular channels, which can be implemented in an upstream modulation Gbps cable transmission system.

Figure 2.

(a) Architecture of dual basis RS encoder. (Reprinted from [26], Copyright 2009, with permission from IEEE). (b) Circuit implementation of the vector string/parallel divider RS encoder. (Reprinted from [27], Copyright 2019, with permission from Elsevier). (c) Architecture of variable-rate RS encoder. (Reprinted from [30], Copyright 2011, with permission from Springer).

2.2. Convolutional Encoder

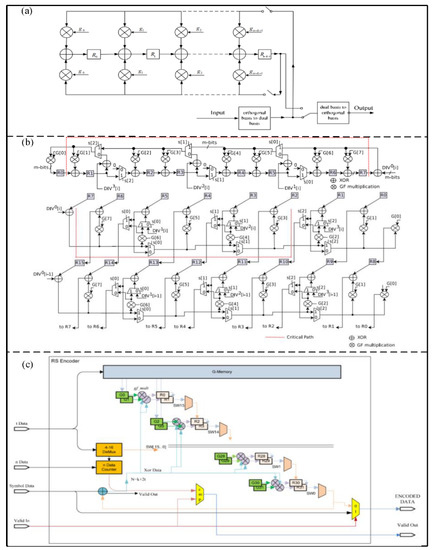

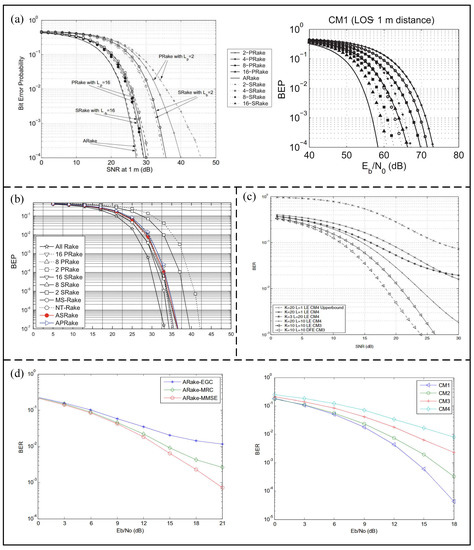

A convolutional encoder is used to sort the RS encoded data and suppress the spectrum [31]. In recent years, the pseudo-chaotic time hopping (PCTH) technique has been used in convolutional coders to suppress spectral lines and reduce the bit error rate (BER). Villarreal-Reyes et al. [32] proposed a new binary to m-base maximum free distance convolution code for time-hopping (TH) impulse radio (IR) UWB systems. Compared with the PCTH algorithm, the proposed algorithm has better hard and soft decision bit error rates, as shown in Figure 3a. However, the proposed algorithm cannot suppress the spectral lines in power spectral density (PSD), and the input of the encoder cannot be completely uniform binary numbers. In order to mitigate the above disadvantages, Villarreal-Reyes et al. [33] improved the algorithm again, and proposed a convolution encoder suitable for binary phase shift keying (BPSK) and quaternary bi-orthogonal pulse position modulated (Q-BOPPM) TH-IR UWB systems. In this encoder, the power spectral density cannot exceed the spectral limit; even the input of the encoder consists of nonuniformly distributed binary numbers, with the result shown in Figure 3b. In addition, Aldo et al. [34] proposed a spectral line free (SLF) convolution encoded IR-UWB over a fiber system with higher transmission power to increase the transmission distance and reduce the BER.

Figure 3.

(a) BER performance for several of the rate 1 binary to 32−ary encoders and 32−ary PCH. (Reprinted from [32], Copyright 2007, with permission from IEEE). (b) BER performance in IEEE 802.15.4a CM1. (Reprinted from [33], Copyright 2011, with permission from IEEE).

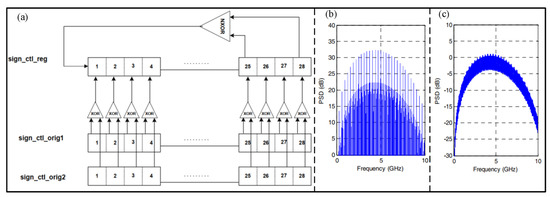

2.3. Scrambler

The anti-interference capability of transmitting data is an important research direction in wireless communication. Scramblers are used to whiten baseband data to reduce error and bit error rates during transmission. In order to reduce the PSD of UWB, Mo et al. [35] proposed a scrambler with a two-layer LFSR to increase the randomness of the scrambler. As shown in Figure 4, the proposed scrambler can increase its randomness in the Y direction. Compared with LFSR-15 with four seeds, the proposed structure can reduce by about 32 dB the UWB physical layer PSD. In addition, Kouassi et al. [36] proposed a UWB transmitter with a random pulse-width scrambling method. After analyzing and optimizing with a genetic algorithm, the result shows that the informationless scrambler can improve spectrum utilization and antijamming ability.

Figure 4.

(a) Architecture of the two−layer LFSR. (b) PSD of original scrambler. (c) PSD of proposed scrambler. (Reprinted from [35], Copyright 2004, with permission from IEEE).

2.4. Comparison and Discussion

The encoder style, scope, and effect of three different encoders are presented in Table 1. These three encoders are used to increase the anti-interference to reduce the bit error rate. The coding manners of RS and convolutional encoders are both forward error correction codes. The application ranges of these three codes are different. An RS encoder is used to encode the PSDU, the convolution encoder is used to sort the PSDU, and scramblers act on preamble codes.

Table 1.

Comparison between different encoders.

3. Pulse Generator

3.1. Low Spectral Interference Generator

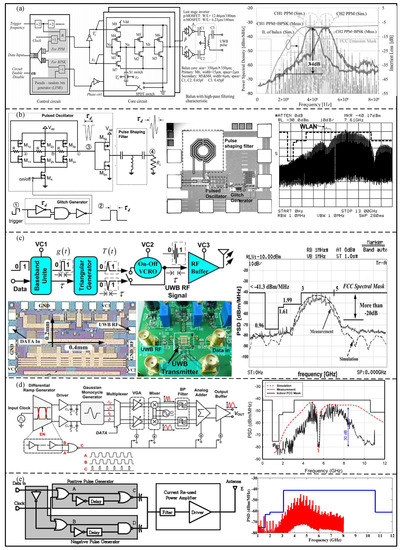

A pulse generator is used to load the encoded data onto the carrier, which is essential in the UWB physical layer. The UWB system may conflict with other narrowband systems, so many circuits have been proposed to reduce PSD [37,38]. Dong et al. [39] proposed a 0.18 μm UWB pulse generator with a pulse oscillator structure and two optional channels for 3–5 GHz, which includes a control circuit, a pulse generation core, an inverter, and a balun, as shown in Figure 5a. The on-chip balun with high-pass characteristics shows high suppression towards PSD in the Global Positioning System (GPS) band. The measurement results showed that the PSD suppression was about 19 dB. Additionally, Sim et al. [37] proposed a low-power, high-peak-value UWB pulse generator based on the 0.18 μm process for 6–10 GHz, which consisted of a pulse generator, a pulse-shaping filter, and a pulse oscillator, as shown in Figure 5b. The pulse-shaping filter was used to make the spectrum comply with Federal Communications Commission (FCC) regulations. For the GPS band at 0.96–1.61 GHz, the proposed pulse-shaping filter can suppress the spectral component by more than 34 dB. As shown in Figure 5c, Zhao et al. [38] proposed a CMOS UWB pulse generator for 3–5 GHz with on–off keying (OOK) modulation, in which a new push-and-pull-integrating narrow triangular pulse generator was designed to reduce the common mode interference and static current. In addition, a new on–off voltage-controlled ring oscillator (VCRO) with a complementary switch mode was proposed, which can reduce power consumption by avoiding generating base-band energy. The results show that the proposed structure can suppress the sidelobes by more than 20 dB. Based on the 90 nm CMOS process, Hedayati et al. [40] proposed a fully integrated analog UWB pulse transmitter with a BPSK modulation, as shown in Figure 5d, which can co-exist with the IEEE 802.11a system. The measurement results show that the generator can produce a tunable notch with a 30 dB attenuation in the narrowband system. Based on the 0.18 um CMOS process, Gunturi et al. [41] proposed a 250 Mb/s data rate IR-UWB transmitter, composed of a pulse generator and a current-reused power amplifier, as shown in Figure 5e. The experimental result shows that the peak PSD power is −42 dBm.

Figure 5.

(a) Block diagram and output PSD of proposed UWB pulse generator. (Reprinted from [39], Copyright 2017, with permission from IEEE). (b) Schematic, die photograph of the proposed UWB pulse generator. (Reprinted from [37], Copyright 2009, with permission from IEEE). (c) Block diagram, die photograph, and test board of the OOK pulse generator, and output PSD in compliance with FCC mask. (Reprinted from [38], Copyright 2013, with permission from IEEE). (d) Block diagram of UWB pulse generator, simulated and measured spectrum of UWB pulse. (Reprinted from [40], Copyright 2013, with permission from IEEE). (e) Block diagram and Measured PSD of the IR−UWB BPSK transmitter. (Reprinted from [41], Copyright 2017, with permission from IEEE).

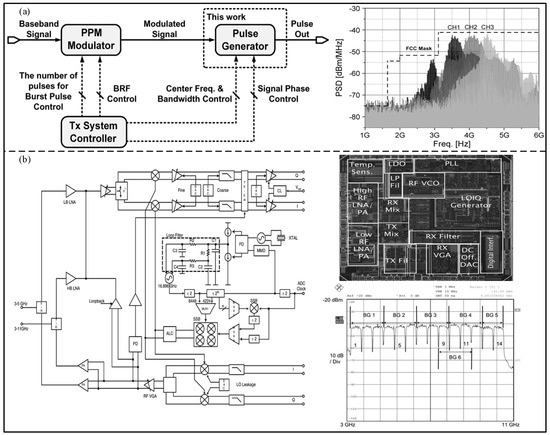

3.2. Optional Channel Generator

Due to the different UWB frequency bands of different countries, many pulse generators are only suitable for a specific frequency band. In order to solve this problem, Choi et al. [42] proposed an all-digital pulse generator based on the 0.13 μm CMOS technology, consisting of a delay line structure, as shown in Figure 6a. The center frequency and the bandwidth of the proposed generator are digitally controlled to cover three channels at 3.1–4.8 GHz. Based on the 65 nm CMOS process, Na et al. [43] proposed an all-digital UWB pulse generator with three optional channels. An all-digital oscillator (ADO) containing a delay line and an edge synthesizer was used to generate a UWB baseband signal. Compared to the architecture proposed by Choi, the architecture proposed by Na can achieve lower power consumption. In addition, Oliver et al. [44] proposed a UWB pulse generator with 14 frequency bands covering the whole UWB bandwidth. As shown in Figure 6b, the proposed pulse generator includes a wideband T/R switch, radio frequency balun, and a full phase-locked loop (PLL) filter assembly, and was fabricated via the 0.13 μm SiGe BiCMOS process.

Figure 6.

(a) System configuration for UWB transmission and measured output for each channel. (Reprinted from [42], Copyright 2012, with permission from IEEE). (b) Block diagram and chip microphotograph of the UWB transceiver, and the measured spectrum of all 14 channels. (Reprinted from [44], Copyright 2007, with permission from IEEE).

3.3. Low Power Consumption Generator

Low power consumption is also an important area of the UWB physical layer [45]. Based on the 0.18 um CMOS process, Zheng et al. [46] proposed a burst mode super-regenerative low-power UWB generator with an OOK modulation, which can be applied in a wireless body area network, as shown in Figure 7a. The proposed generator can restore the received signal and reduce the post-stage amplifier, and its power consumption is 671 pJ/pause. In order to achieve low power consumption, Mercier et al. [47] proposed a low-power all-digital UWB pulse generator with a BPSK + PPM modulation based on the 90 nm CMOS process, as shown in Figure 7b. The proposed generator uses a simple single-ended ring oscillator and a digital output buffer to synthesize the pulse, and the measured energy consumption is 17.5 pJ/pause. As shown in Figure 7c, Bourdel et al. [48] proposed a low-power pulse response filter OOK-modulated UWB pulse generator, fabricated by the 0.13 um CMOS process. The edge synthesizer is used to excite an integrated bandpass filter, and the proposed generator energy consumption is 9 pJ/pause. In addition, Shen et al. [49] proposed a UWB pulse generator based on the 0.18 μm CMOS process with low peak power consumption, as shown in Figure 7d. In order to decrease the peak current and maintain the waveform of the generated UWB pulse signal, a slow-charging and fast-discharging method was adopted in the proposed generator to increase the duration of the pulse peak current. The measurement results show that the minimum power consumption is 5 pJ/pause. Based on the 0.18 um CMOS process, Radic et al. [50] proposed a low-power IR-UWB transmitter, consisting of a controllable pulse generator, a switchable tunable oscillator, a driver, and a pulse-shaping filter, as shown in Figure 7e. The experimental results show that the minimum power consumption is only 3 pJ/pulse.

Figure 7.

(a) Block diagram and die photograph of the super−regenerative UWB transceiver. (Reprinted from [46], Copyright 2014, with permission from IEEE). (b) Block diagram and die photograph of the proposed generator. (Reprinted from [47], Copyright 2009, with permission from IEEE). (c) Architecture of the proposed pulse generator and current consumption simulation. (Reprinted from [48], Copyright 2010, with permission from IEEE). (d) CMOS implementation of the pro-posed pulse generator and measured current at a PRR of 10 Mpps. (Reprinted from [49], Copyright 2014, with permission from IEEE). (e) Detailed schema and measured output waveform of the proposed transmitter. (Reprinted from [50], Copyright 2020, with permission from IEEE).

3.4. Comparison and Discussion

The summary of the UWB pulse generator is shown in Table 2. The process, bandwidth, power consumption, modulation mode, circuit area, etc., are systematically compared and discussed. Obviously, the 0.18 μm CMOS process is the most mainstream process at present. Meanwhile, some more advanced processes, such as 90 nm CMOS and 65 nm CMOS, have also been used in the fabrication of a pulse generator, which can reduce the power consumption and die photograph area. As shown in Table 2, the pulse oscillator, delay lines, and analog circuits are major architectures in a pulse generator. BPSK modulation can suppress spectral line problems and has a low bit error rate. Additionally, OOK modulation shows low bit error rate characteristics with a simple structure. Therefore, most pulse generators adopt the BPSK and OOK modulation. The pulse generators in [43,44,45] provide optional channels, but their −10 dB bandwidth is only 0.5 GHz, which is less than other architectures. Compared with other pulse generators, the tunable pulse in [51] leads to significantly low power consumption, 3 pJ/pause. The generator proposed by Shen et al. [50] can operate at a high pulse repetition rate (PRR) of 1 Gpps, which is the highest.

Table 2.

Summary of UWB pulse generators in different architectures.

4. Receiver

The pulse signal is transmitted through an environmental channel, which is demodulated and filtered for noise by the receiver. Rake and analog front-end receivers applied in the UWB physical layer are introduced.

4.1. Rake Receiver

A rake receiver is a key technology of a spread-spectrum communication system, and was proposed by Price and Green in 1958 [51]. The multipath signal energy is processed by the rake receiver to improve the signal-to-noise ratio (SNR) of the signal and reduce the fading probability [52]. Rake receivers are divided into multipath collection and combination. In order to implement a multipath collection strategy, the ideal rake receiver is used to analyze all multipath components which can be called all-rake (A-rake). The A-rake has the best BER performance; however, its architecture is not widely used because of the high complexity.

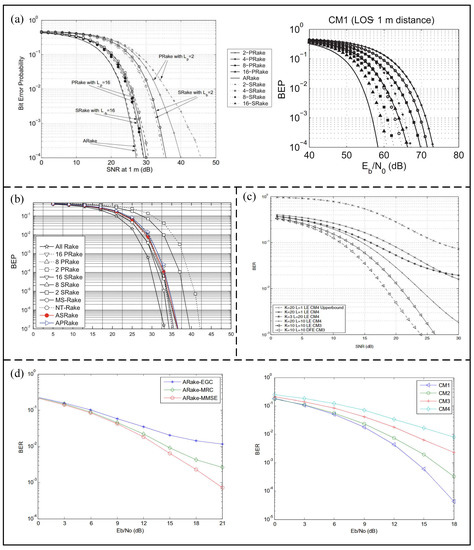

In order to balance complexity and performance, two UWB rake receivers with low complexity were proposed by Cassioli et al. [53], a partial rake (P-rake) and selective rake (S-rake). A P-rake has the lowest complexity because it only combines the multipath components that arrive to the receiver first, while the instantaneous strongest multipath component is received by the S-rake. As shown in Figure 8a, the performance of the S-rake and P-rake is similar at a high-frequency channel, while the S-rake significantly outperforms the P-rake at a low-frequency channel. In addition, adaptive P-rake and S-rake receivers were proposed by Doukeli [54], and can be applied in the UWB physical layer. In the proposed receivers, the number of combined paths can be reduced by comparing the SNR quality of each path. As shown in Figure 8b, the performance of these proposed rake structures is higher than that of S-rake and P-rake.

Different combination methods are used by the rake receivers in the multipath combination strategy. Maximum ratio combination (MRC) is known as an optimal linear combination technology, which combines all paths with different weights. The combination weights can be selected by a minimum mean square error (MMSE) equalizer for better performance. A receiver hardware architecture that combines a rake and MMSE equalizer was proposed by Eslami [55]. Rake and equalizer structures are used to combat intersymbol interference. The performance of the proposed receiver relationship with the number of equalizer taps and rake fingers is studied by a semi-analytical approach and Monte Carlo simulation. As shown in Figure 8c, the number of rake fingers is the main factor that improves the performance of the system at low SNR, while the number of equalizer taps is more important at high SNR. In addition, a new adaptive rake MMSE receiver architecture based on the recursive least squares algorithm was proposed by Kang et al. [56]. The MMSE method is used by the proposed architecture to combine multipath components for eliminating narrowband interference. As shown in Figure 8d, the MMSE can achieve better performance than the traditional MRC and equal-gain combining (EGC) receivers. The performance of the proposed receiver is the best in CM1 (line-of-sight channel), and the worst in CM4 (non-line-of-sight channel).

Figure 8.

(a) Functional between BEP and normalized SNR at rake output of A−rake, S−rake, and P−rake in LF channel. The BEP vs. Eb/N0 for P−Rake and S−Rake in the HF channel model with the full transmission bandwidth. (Reprinted from [53], Copyright 2007, with permission from IEEE). (b) BEP for the case of the LF channel model. (Reprinted from [54], Copyright 2012, with permission from Springer). (c) UWB rake−MMSE−equalizer structure and performance of UWB rake−MMSE−receiver for different number of equalizer taps and rake fingers. (Reprinted from [55], Copyright 2005, with permission from IEEE). (d) BER comparison of three combining methods for Rake in CM3 and the BER performance of the proposed Rake−MMSE receiver under CM1−CM4 channel models. (Reprinted from [56], Copyright 2016, IEEE).

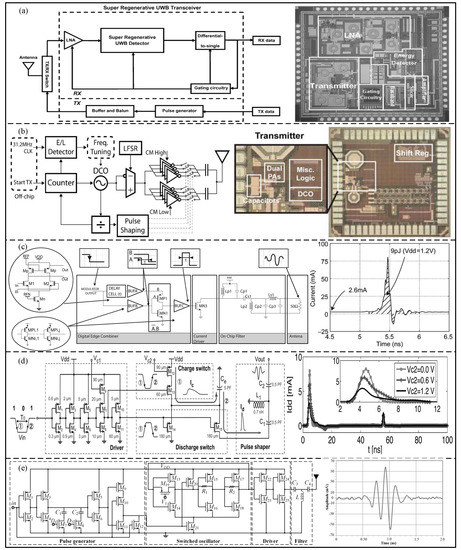

4.2. Analog Front-End Receiver

The received signal is amplified and digitized by the analog front-end receiver. Generally, the receiver consists of a low-noise amplifier, an analog-to-digital converter, and a digital signal processing unit.

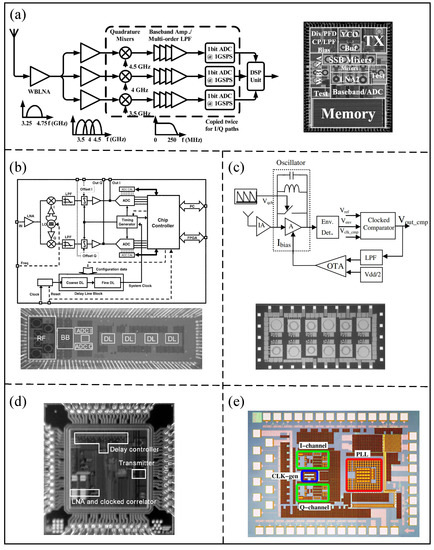

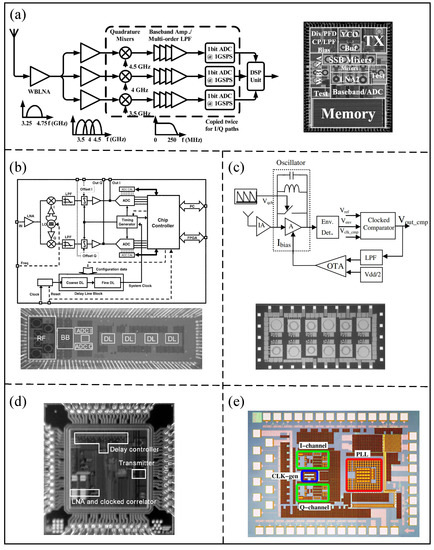

In order to achieve low power consumption and high-data-rate communication, Medi et al. [57] proposed an ultra-wide band receiver implemented in 0.18 μm CMOS technology operating at a 3.25–4.75 GHz band and pulse-based, as shown in Figure 9a. Using the proposed receiver, the UWB signal can be effectively digitized and its robustness can be increased. When running at a data rate of 1 Gbps, the proposed receiver consumes 98 pJ/b in the receive mode. In addition, Ryckaert et al. [58] proposed a low-power pulse radio UWB receiver that can be applied at a low data rate. As shown in Figure 9b, the quadrature analog correlation architecture is used in the proposed receiver, which has low energy consumption because of reducing the ADC sampling speed. At the 20 Mpulses/s pulse rate, a 16 mA power consumption can be achieved by the proposed receiver implemented in the 0.18 μm CMOS.

In a narrowband interference channel, Anis et al. [59] proposed a UWB receiver architecture, which can extract effective signals by narrow-band-pass filters. The narrow-band-pass filter consists of a super-regenerative receiver (SRR), as shown in Figure 9c. The receiver has been implemented in 0.18 μm CMOS with a power consumption of 2.6 mW.

In order to reduce the power consumption and layout area, Terada et al. [60] proposed a CMOS UWB-IR receiver architecture with 0.18 μm CMOS technology, as shown in Figure 9d. The intermittent operation in the proposed architecture can reduce the power consumption mainly caused by the clock correlator and differential low-noise amplifier. The power consumption of the proposed receiver is only 1 mW when the differential low-noise amplifier works intermittently through the bias switch. Based on the 0.13 μm CMOS process, Helleputte et al. [61] proposed an integrated ultra-low-power analog front-end architecture for UWB pulse radio receivers, as shown in Figure 9e. A local oscillator is adopted to reduce the power consumption of pulse correlation, and the proposed receiver has a power consumption of 2.7 mW at a 39.0625 Mpulses/s pulse rate.

Figure 9.

(a) Frequency channelized receive and chip micrograph. (Reprinted from [57], Copyright 2008, with permission from IEEE). (b) Quadrature analog correlating architecture and receiver chip mi-crophotograph. (Reprinted from [58], Copyright 2007, with permission from IEEE). (c) Block dia-gram of Super regenerative receiver and die photograph for UWB receiver. (Reprinted from [59], Copyright 2007, with permission from IEEE). (d) Chip microphotograph. (Reprinted from [60], Copyright 2006, with permission from IEEE). (e) Key performance of different modules and die photo. (Reprinted from [61], Copyright 2009, with permission from IEEE).

4.3. Comparison and Discussion

The parameters of UWB pulse radio receivers are compared in Table 3, including the fabrication process, bandwidth, maximum symbol rate, power consumption, and chip area. Obviously, the mainstream fabrication process of UWB pulse radio receivers is 0.18 μm CMOS technology. Compared with other receivers, the 0.13 μm process adopted by Hellepute [61] can improve the performance, and reduce power consumption and chip area. The architecture proposed by Anis [59] has a high bandwidth, which can transmit highspeed signals in an indoor situation. Due to the sub-1 GHz operating bandwidth, the signal transmitted by the architectures [60,61] is a low-speed signal with a strong penetrating ability and wide range. Compared with other receivers, the architecture proposed by Medi [57] achieves lower power consumption and a higher maximum bit rate, which makes it suitable for high-speed data communication.

Table 3.

Parameters of UWB pulse radio receiver.

5. Decoder

During the data transmission process, data can easily be disturbed by noise. The decoder corrects erroneous data by adding check bits during the encoding process. In the UWB transmitting link, the decoder module consists of a Viterbi decoder and an RS decoder.

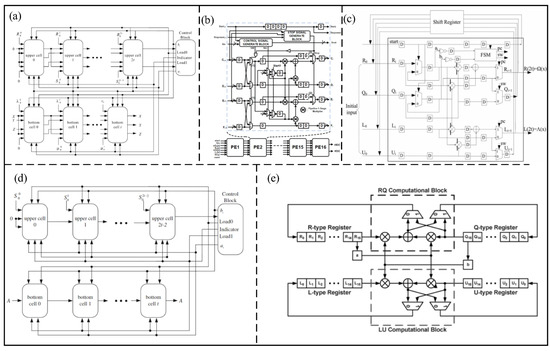

5.1. Viterbi Decoder

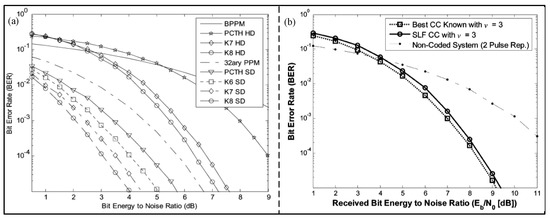

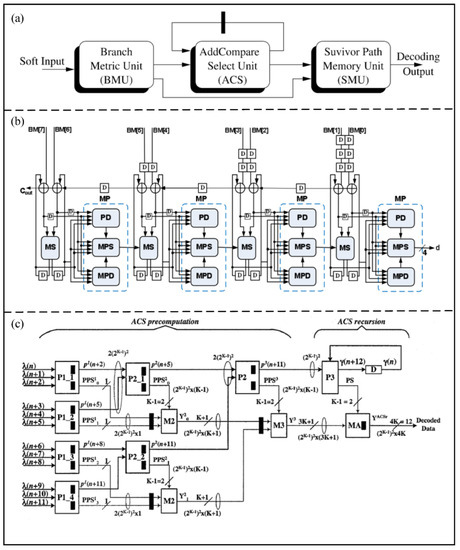

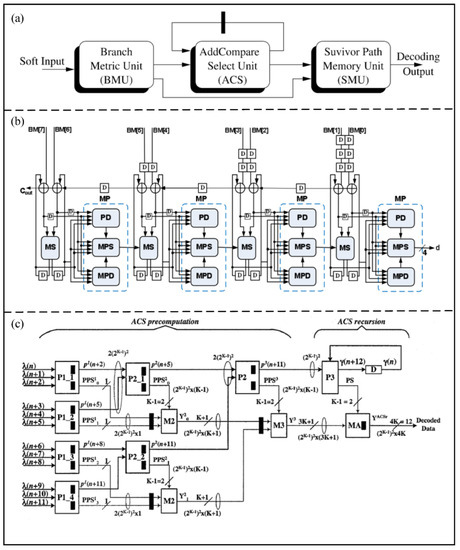

The Viterbi algorithm was proposed in 1967 [62], and is used to produce a sequence of observed events. As a convolutional decoding method, the Viterbi decoding has been widely used in digital circuits and communication decoding. The Viterbi decoder consists of a branch measurement unit (BMU), an add comparison selection unit (ACSU), and a surviving path memory unit (SMU), as shown in Figure 10a. Recursive operation is a nonlinear feedback loop in the ACSU, and is a key method for improving the speed of the decoder [63].

In order to simplify the nonlinear feedback loop, Fettweis [64] proposed a semicircular algebraic architecture technique consisting of two recursive ACSU operations. The architecture changes the nonlinear recursion in the Viterbi algorithm to achieve linear recursion, which breaks the iteration bounds of the Viterbi decoding algorithm.

In order to reduce the length of the critical path, Parhi et al. [65] proposed a pipelined most significant bit (MSB) ACSU architecture. The length of the critical path is reduced to the iteration limit in the ACSU by balancing the establishment time of different paths, which can reduce the parallelism and area of Viterbi decoder. Compared with the traditional architecture, the critical path of ACSU can be reduced by 15% via the proposed architecture.

In addition, Goo et al. [66] proposed a pipelined MSB ACSU architecture based on the two-step look-ahead technique, as shown in Figure 10b. The two-step look-ahead technique is used to eliminate the feedback operation for improving the proposed decoder speed. Compared with a traditional MSB ACSU, the proposed decoder saves 12% of area and increases speed by 9%.

Kong et al. [67] proposed a low-latency branch precomputation architecture for a high-throughput Viterbi decoder, as shown in Figure 10c. The look-ahead technique is improved by changing the calculation of ACSU latency to increase logarithmically. The proposed architecture is used to avoid the linear stepwise calculation process and shows great improvement in reducing latency.

In order to reduce the latency of the M-step look-ahead method, Cheng et al. [68] proposed a Viterbi decoding method with a K-nested layer that can efficiently reduce latency by parallel work. The results show improved hardware efficiency and that the latency of ACSU calculation is reduced.

In the M-step look-ahead method, one step of the complex trellis consists of multiple steps of the chronological binary trellis, which is called branch metric precomputation (BMP). In order to simplify the BMP, Liu et al. [69] proposed an overall low-complexity BMP architecture based on a balanced binary grouping (BBG) algorithm, which can be used to eliminate redundancy and achieve minimum complexity and latency. The complexity/delay of the proposed architecture is reduced by 45.65%/72.50%.

Figure 10.

(a) Basic computation units in a Viterbi decoder. (Reprinted from [65], Copyright 2004, with permission from IEEE). (b) Block diagram of the proposed two−bit level pipelined MSB−first ACSU. (Reprinted from [66], Copyright 2008, with permission from IEEE). (c) An architecture of the low−latency branch precomputation Viterbi decoder. (Reprinted from [67], Copyright 2004, with permission from IEEE).

5.2. Comparison and Discussion of Viterbi Decoder

The latency and complexity of the ACSU for the lookahead architecture are summarized in Table 4, which represent the number of clock cycles and adders, respectively. In the table, K is the constraint length of the decoder and M is the step size of the look-ahead method. Compared with the conventional method, these proposed architectures are greatly optimized for latency by increasing the complexity. In the architecture proposed by Kong et al. [67], the K-layer look-ahead method is applied to the conventional architecture, which reduces the latency. The architecture proposed by Cheng et al. [68] reduces the complexity by improving the look-ahead method. In addition, the BBG method is applied to the proposed architecture by Kong et al. [67], which can significantly optimize latency and complexity. The architecture proposed by Liu et al. [69] performs best in terms of latency, and its hardware resources are slightly more complicated than those of a conventional architecture.

Table 4.

Latency and complexity of the ACSU.

5.3. RS Decoder

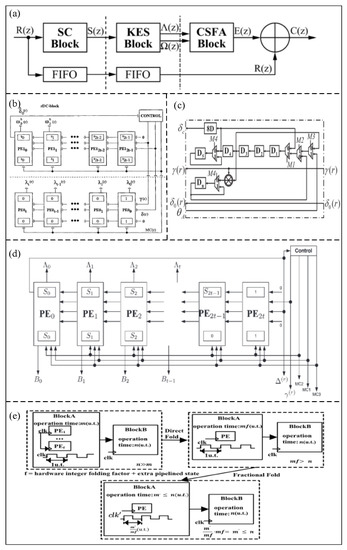

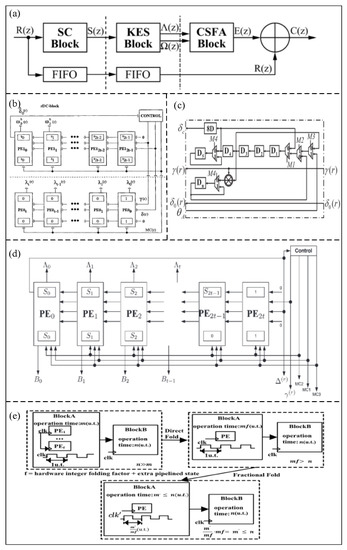

An RS decoder is widely used to decode and correct data that have been encoded in various digital communication systems [21]. An RS decoder is divided into three parts: the calculation of correction factors, the solution of the key equation, and the determination of error location and size [70], as shown in Figure 11a. The solution of the key equation is the most complex part of the decoder, and can be implemented by the Berlekamp–Massey (BM) algorithm or the Euclidean algorithm.

5.3.1. BM Algorithm

The BM algorithm was proposed by Berlekamp and Massey for solving the key equations in the decoder [71]. In the BM algorithm, the key equation is solved by decoding iteration, which leads to a complex operation.

In order to simplify the BM algorithm, Reed et al. [72] proposed an inverse-free decoding method, called iBM. The iBM algorithm eliminates the inversion operation of the BM algorithm in a nonbinary Galois domain. Therefore, a Very Large-Scale Integration (VLSI) of the RS code can be realized by the iBM algorithm. In addition, Sarwate et al. [73] proposed a new reconfigurable inverse-free decoding architecture called RiBM, as shown in Figure 11b. The critical path can be optimized by RiBM architecture, so the number of multipliers/adders is reduced from two/ (where t is the number of detection errors) to one. Based on an RiBM architecture, Liang et al. [74] developed a compensated, simplified, inverse-free BM called CS-RIBM architecture. The redundant calculation in RiBM architecture can be eliminated by the CS-RiBM architecture, so high throughput and low hardware complexity can be achieved by the proposed architecture. Compared with the RiBM architecture, the proposed architecture can reduce the area by 14% and improve the efficiency by 17%. In order to further reduce the hardware complexity, Liu et al. [75] proposed a simplified inverse-free BM architecture with recursive compensation called RCS-RiBM. The proposed architecture consists of a processing element and a compensation unit, which can effectively reduce the hardware complexity. Compared with the common RS decoder, the proposed architecture can reduce the area by 11%. Based on the CS-RiBM architecture, Lu et al. [76] proposed a modified, compensated, simplified, inverse-free BM (MCS-RiBM) architecture, which combines the folding technology to improve the hardware utilization and simplify the generated architecture. Figure 11c shows the folded compensated simplified circuit diagram. The proposed architecture has a total gate number of 255,400.

In order to simplify the iBM architecture, Wu et al. [77] proposed an enhanced parallel inverse-free BM (EPIBM) architecture, as shown in Figure 11d. The generalized Horiguchi–Koetter formula is used in the proposed architecture to increase its parallel calculation ability. Compared with the iBM architecture, which requires 3t systolic cells, the EPIBMA architecture only needs 2t + 1 systolic cells. In addition, Ji et al. [78] proposed the recursive enhanced parallel inverse-free BM (REPIBM) architecture based on the 0.18 um CMOS process, which can effectively reduce the hardware complexity by recursive operation. The experimental result shows the number of gates is 13,000.

Figure 11.

(a) Block diagram of RS decoder. (Reprinted from [75], Copyright 2017, with permission from IEEE). (b) The systolic RiBM architecture. (Reprinted from [73], Copyright 2001, with permission from IEEE). (c) The folded compensated simplified circuit diagram. (Reprinted from [76], Copyright 2019, with permission from IEEE). (d) EPIBM block diagram. (Reprinted from [77], Copyright 2015, with permission from IEEE). (e) The process of fractional folding. (Reprinted from [79], Copyright 2021, with permission from IEEE).

Liu et al. [79] proposed an enhanced parallel inverse-free BM RS decoder based on fractional folding (FF-EPIBM). The process of fractional folding is shown in Figure 11e. The number of processing units can be reduced to one, resulting in ultra-low hardware complexity. Compared with the fully extended parallel EPIBM architecture, the RS decoder based on the FF-EPIBM architecture can reduce the hardware complexity by about 60%.

5.3.2. Euclidean Algorithm

The Euclidean algorithm is also a common method used to solve the key equations in the RS decoder, which can be achieved by calculating the greatest common factor. The complexity of the Euclidean algorithm is high due to its inversion operation. To eliminate the inversion operation, Shao et al. [80] proposed a modified Euclidean (ME) architecture to calculate the error location polynomial. In the ME architecture, the degree calculation can increase the complexity of circuit. Bae et al. [81] proposed a modified Euclidean architecture to remove the degree calculation (DCME), as shown in Figure 12a. The proposed architecture has low hardware complexity because of completely removing the degree calculation. Compared with the conventional ME decoder, the proposed DCME architecture can reduce the total gate count and delay by 23% and 10%, respectively. In order to increase speed and reduce complexity, Lee et al. [82] proposed a pipelined DCME (PDCME) architecture for the RS decoder, as shown in Figure 12b. The proposed architecture can reduce the total gate count by 15% more than the ME architecture.

In the DCME architecture, the conventional systolic architecture needs many processing elements, which can increase the circuit complexity. Yuan et al. [83] proposed a high-speed and low-complexity Reed–Solomon (RS) decoder architecture based on a recursive DCME architecture, as shown in Figure 12c. The proposed architecture uses the recursive architecture of a single processing element instead of the conventional architecture of multiple processing elements, which has low hardware complexity. The proposed architecture can reduce the total gate count by 30% compared with the DCME architecture.

In order to replace the ME architecture, Baek et al. [84] proposed a simplified Euclidean (SE) decoder architecture, as shown in Figure 12d. In the proposed architecture, the new initial conditions and polynomials are used, which can significantly reduce the complexity. The total gate count of the proposed architecture is only 40,136 for the (255,239) RS code, and is reduced by 5% compared with the DCME architecture. In addition, Hsu et al. [85] proposed an RS decoder architecture based on the real-time folding modified Euclidean algorithm, as shown in Figure 12e. Compared with the parallel RS architecture, the proposed architecture can reduce the hardware complexity by about 50%.

Figure 12.

(a) Proposed DCME architecture. (Reprinted from [81], Copyright 2006, with permission from IEEE). (b) Block diagram of DCME algorithm. (Reprinted from [82], Copyright 2007, with permission from IEEE). (c) Block diagram of RDCME algorithm. (Reprinted from [83], Copyright 2009, with permission from IEEE). (d) New SE algorithm. (Reprinted from [84], Copyright 2013, with permission from IEEE). (e) Proposed Jit−FMEA algorithm. (Reprinted from [85], Copyright 2004, with permission from IEEE).

5.4. Comparison and Discussion for the RS Decoder

The performance parameters of different RS decoders are compared in Table 5, and mainly included technology, total gates, frequency, throughput, and technology-scaled normalized throughput (TSNT). Obviously, the mainstream fabrication process of the RS decoders is the 0.18 μm CMOS technology. However, advanced processes with smaller feature sizes, such as 0.13, 0.09, and 0.04 μm CMOS technologies, have been adopted since they can greatly increase the working frequency and throughput. The total number of gates of the RS decoder consists of the syndrome computation (SC), the Chien search and error evaluation (CSEE) and the key equation solver (KES) blocks. Compared with other architectures, only one processing unit is used in the folding architecture proposed by Liu et al. [79], which can effectively reduce the number of gates used in the KES. In addition, the throughput and TSNT of the proposed architecture are 24.8 Gb/s and 592 Mb/s/K·gate due to processing data in parallel and high frequency. The recursive method is used in the RCS-RiBM architecture [75] and RDCME [83] to reduce the total number of gates to fewer than 20,000. When the frequency is less than 700 MHz, the architecture proposed by Lu et al. [76] achieves the highest throughput, but the compensation unit used in the architecture leads to an increase in the number of selectors and path delay.

Table 5.

Performance summary of recently proposed RS decoders for the UWB physical layer.

6. Conclusions and Outlook

The development of the UWB physical layer, including the encoder, pulse generator, receiver, and decoder, is introduced in this paper. The encoder includes an RS encoder, a convolutional encoder, and a scrambler. In the RS encoder, methods to increase coding speed and reduce hardware resources are discussed. The PSD can be reduced by a convolutional encoder and scrambler. In the pulse generator, the low spectral interference generator can meet IEEE 802.15.4a, and the optional channel generator and low power consumption generator should meet the spectrum requirements. In the receiver, the rake receiver is a key technology of spread-spectrum communication systems, and the analog front-end receiver can amplify and digitize the received signal. In the decoder, the delay of the Viterbi decoder can be reduced by optimizing algorithms. The RS decoder is optimized by BM and Euclidean algorithms to achieve higher speed and lower hardware complexity. A detailed discussion of the UWB physical layer is presented to provide suggestions for the design of a high-performance UWB physical layer.

With the requirements of high speed, low power, and fewer hardware resources, the performance of a UWB system can be improved in several aspects:

- The encoder speed should be improved.

The encoder can be blocked when encoding large amounts of data, and the coding efficiency can be reduced. Besides the traditional bit-serial RS encoder, other architectures such as the bit-parallel and dual-based encoders can be adopted to improve the encoder speed. However, these architectures can influence the area and power consumption, so the power consumption and area should be balanced when the encoder speed is increased.

- The transmitting link should meet the low PSD requirement.

UWB signals easily interfere with narrowband signals because of their wide frequency spectrum. Therefore, the UWB frequency should meet the low PSD requirement. The MFD algorithm in a convolutional coder, two-layer LFSR of a scrambler, and on-chip balun in a pulse generator can effectively reduce the power spectral density.

- The pulse generator should maintain low power consumption.

UWB is widely used in wireless wearable devices, so low power consumption is required to support long-term usage. Existing methods include reducing the peak current of the pulse generator and maintaining the off state when the pulse generator is out of work. More methods are needed to maintain the low power consumption of the pulse generator.

- Multiple-user interference can be decreased in the receiver.

Multiple-user access and communication exist when UWB is used for indoor positioning, so the effect of multiple-user interference and environmental noise should be decreased by orthogonal frequency division multiplexing to improve the anti-multipath interference and robustness.

- The complexity and latency of decoders should be reduced.

Due to the large volume of resources used by the decoders, the BBG algorithm can be used in different Viterbi decoders to reduce the complexity and latency of BMP units. In order to reduce the complexity of the key equation in the RS decoder, the generalized fractional folding and pipeline structures can be used in different algorithms.

Author Contributions

Conceptualization, Z.L. and X.Z. (Xin Zhang 1); methodology, D.C.; software, D.C.; validation, Z.L., X.Z. (Xin Zhang 1) and D.C.; formal analysis, D.L.; investigation, D.C.; resources, D.L.; data curation, D.C.; writing—original draft preparation, D.L.; writing—review and editing, X.W.; visualization, Y.Z.; supervision, X.Z. (Xin Zhang 2); project administration, T.Z.; funding acquisition, Y.Y. All authors have read and agreed to the published version of the manuscript.

Funding

This research was funded by Youth Talent Fund of Joint Fund of the Ministry of Education for Equipment Pre-Research (No: 8091B032138), Wuhu and Xidian University special fund for industry-university-research cooperation (No: XWYCXY-012021008), the Cooperation Program of XDU-Chongqing IC Innovation Research Institute (No. CQIRI-2022CXY-Z01) and the Fundamental Research Funds for the Central Universities and the Innovation Fund of Xidian University.

Data Availability Statement

Not applicable.

Conflicts of Interest

The authors declare no conflict of interest.

References

- Qi, F.; Lv, H.; Wang, J.; Fathy, A.E. Quantitative Evaluation of Channel Micro-Doppler Capacity for MIMO UWB Radar Human Activity Signals Based on Time–Frequency Signatures. IEEE Trans. Geosci. Remote Sens. 2020, 58, 6138–6151. [Google Scholar] [CrossRef]

- Yektakhah, B.; Chiu, J.; Alsallum, F.; Sarabandi, K. Low-Profile, Low-Frequency, UWB Antenna for Imaging of Deeply Buried Targets. IEEE Geosci. Remote Sens. Lett. 2020, 17, 1168–1172. [Google Scholar] [CrossRef]

- Wymeersch, H.; Lien, J.; Win, M.Z. Cooperative Localization in Wireless Networks. Proc. IEEE 2009, 97, 427–450. [Google Scholar] [CrossRef]

- Zhang, Y.; Tan, X.; Zhao, C. UWB/INS Integrated Pedestrian Positioning for Robust Indoor Environments. IEEE Sensors J. 2020, 20, 14401–14409. [Google Scholar] [CrossRef]

- Wen, K.; Yu, K.; Li, Y.; Zhang, S.; Zhang, W. A New Quaternion Kalman Filter Based Foot-Mounted IMU and UWB Tightly-Coupled Method for Indoor Pedestrian Navigation. IEEE Trans. Veh. Technol. 2020, 69, 4340–4352. [Google Scholar] [CrossRef]

- Li, D.; Wang, X.; Chen, D.; Zhang, Q.; Yang, Y. A precise ultra-wideband ranging method using pre-corrected strategy and particle swarm optimization algorithm. Measurement 2022, 194, 110966. [Google Scholar] [CrossRef]

- Yang, Y.; Wang, X.; Li, D.; Chen, D.; Zhang, Q. An Improved Indoor 3D Ultra-Wideband Positioning Method by Particle Swarm Optimization Algorithm. IEEE Trans. Instrum. Meas. 2022, 71, 1005211. [Google Scholar] [CrossRef]

- Puschita, E.; Simedroni, R.; Palade, T.; Codau, C.; Vos, S.; Ratiu, V.; Ratiu, O. Performance Evaluation of the UWB-based CDS Indoor Positioning Solution. In Proceedings of the 2020 International Workshop on Antenna Technology (iWAT), Bucharest, Romania, 25–28 February 2020. [Google Scholar] [CrossRef]

- Ali, M.; Shawkey, H.; Zekry, A.; Sawan, M. One Mbps 1 nJ/b 3.5–4 GHz fully integrated FM-UWB transmitter for WBAN applications. IEEE Trans. Circuits Syst. I Reg. Pap. 2018, 65, 2005–2014. [Google Scholar] [CrossRef]

- Zhou, B.; Chiang, P. Short-Range Low-Data-Rate FM-UWB Transceivers: Overview, Analysis, and Design. IEEE Trans. Circuits Syst. I Regul. Pap. 2016, 63, 423–435. [Google Scholar] [CrossRef]

- Fort, A.; Desset, C.; De Doncker, P.; Wambacq, P.; Van Biesen, L. An ultra-wideband body area propagation channel Model-from statistics to implementation. IEEE Trans. Microw. Theory Technol. 2006, 54, 1820–1826. [Google Scholar] [CrossRef]

- Promsrisawat, P.; Promwong, S. A study of HB-UWB transfer function model for wireless body area network. In Proceedings of the 2018 International Conference on Digital Arts, Media and Technology (ICDAMT), Phayao, Thailand, 25–28 February 2018; pp. 225–228. [Google Scholar] [CrossRef]

- Li, J.; Zeng, Z.; Sun, J.; Liu, F. Through-wall detection of human being’s movement by UWB radar. IEEE Geosci. Remote Sens. Lett. 2012, 9, 1079–1083. [Google Scholar] [CrossRef]

- Salmi, J.; Molisch, A.F. Propagation Parameter Estimation, Modeling and Measurements for Ultrawideband MIMO Radar. IEEE Trans. Antennas Propag. 2011, 59, 4257–4267. [Google Scholar] [CrossRef]

- Chen, S.; Liu, H.H. UWB slot antenna on shielding can for high accuracy positioning application. In Proceedings of the 2020 Global Congress on Electrical Engineering (GC-ElecEng), Valencia, Spain, 4–6 September 2020. [Google Scholar] [CrossRef]

- IEEE Std 802.15.4-2011; IEEE Standard for Local and Metropolitan Area Networks—Part 15.4: Low-Rate Wireless Personal Area Networks (LR-WPANs). (Revision of IEEE Std 802.15.4-2006); IEEE: New York, NY, USA, 2011; pp. 1–314.

- Zhang, X. VLSI Architectures for Reed–Solomon Codes: Classic, Nested, Coupled, and Beyond. IEEE Open J. Circuits Syst. 2020, 1, 157–169. [Google Scholar] [CrossRef]

- Han, S.; Zhang, M. A Method for Blind Identification of a Scrambler Based on Matrix Analysis. IEEE Commun. Lett. 2018, 22, 2198–2201. [Google Scholar] [CrossRef]

- Cavallaro, M.; Sapone, G.; Giarrizzo, G.; Italia, A.; Palmisano, G. A 3–5-GHz UWB Front-End for Low-Data Rate WPANs in 90-nm CMOS. IEEE Trans. Microw. Theory Technol. 2010, 58, 854–865. [Google Scholar] [CrossRef]

- Mahmood, H.U.; Utomo, D.R.; Kim, J.; Lee, S.-G. A 27 dB Sidelobe Suppression, 1.12 GHz BW−10dB UWB Pulse Generator With Process Compensation. IEEE Trans. Circuits Syst. II Express Briefs 2021, 68, 2805–2809. [Google Scholar] [CrossRef]

- Choi, S.-W.; Choi, S.-S.; Lee, H.-h. RS decoder architecture for UWB. In Proceedings of the 2006 8th International Conference Advanced Communication Technology, Phoenix Park, Republic of Korea, 20–22 February 2006; pp. 4–808. [Google Scholar]

- Santhi, M.; Lakshminarayanan, G.; Sundaram, R.; Balachander, N. Synchronous pipelined two-stage radix-4 200Mbps MB-OFDM UWB Viterbi decoder on FPGA. In Proceedings of the 2009 International SoC Design Conference (ISOCC), Busan, Republic of Korea, 22–24 November 2009; pp. 468–471. [Google Scholar] [CrossRef]

- Zou, Z.; Mendoza, D.S.; Wang, P.; Zhou, Q.; Mao, J.; Jonsson, F.; Tenhunen, H.; Zheng, L.-R. A Low-Power and Flexible Energy Detection IR-UWB Receiver for RFID and Wireless Sensor Networks. IEEE Trans. Circuits Syst. I Regul. Pap. 2011, 58, 1470–1482. [Google Scholar] [CrossRef]

- Huang, S.; Yang, Y.; Sun, Z. Add-select-delay-compare Viterbi decoder for UWB communications in electronic power systems. In Proceedings of the 2014 IEEE International Conference on Communiction Problem-solving, Beijing, China, 5–7 December 2014; pp. 1–4. [Google Scholar] [CrossRef]

- Leenaerts, D.; van de Beek, R.; Bergervoet, J.; Kundur, H.; van der Weide, G.; Kapoor, A.; Pu, T.Y.; Fang, Y.; Wang, Y.J.; Mukkada, B.J.; et al. A 65 nm CMOS Inductorless Triple Band Group WiMedia UWB PHY. IEEE J. Solid-State Circuits 2009, 44, 3499–3510. [Google Scholar] [CrossRef]

- Ren, Z.; Yao, D. An improved high-speed RS encoding algorithm. In Proceedings of the 2009 3rd IEEE International Symposium on Microwave, Antenna, Propagation and EMC Technologies for Wireless Communications, Beijing, China, 27–29 October 2009. [Google Scholar]

- Mohamed, A.; Shukla, S.K. LFSR based versatile divider architectures for BCH and RS error correction encoders. Microprocess. Microsyst. 2019, 71, 102902. [Google Scholar]

- Jittawutipoka, J.; Ngarmnil, J. Low complexity Reed-Solomon encoder using globally optimized finite field multipliers. In Proceedings of the 2004 IEEE Region 10 Conference TENCON 2004, Chiang Mai, Thailand, 24 November 2004. [Google Scholar] [CrossRef]

- Wu, X.; Shen, X.; Zeng, Z. An improved RS encoding algorithm. In Proceedings of the 2012 2nd International Conference on Consumer Electronics, Communications and Networks (CECNet), Yichang, China, 21–23 April 2012; pp. 1648–1652. [Google Scholar]

- Lee, Y.S.; Yeo, S.-S. A novel design of variable-rate RS encoder for ubiquitous high performance multimedia service in Gbps transmission system. J. Supercomput. 2011, 55, 192–206. [Google Scholar] [CrossRef]

- Villarreal-Reyes, S.; Edwards, R.M. Analysis Techniques for the Power Spectral Density Estimation of Convolutionally Coded Impulse Radio UWB Signals Subject to Attenuation and Timing Jitter. IEEE Trans. Veh. Technol. 2009, 58, 1355–1374. [Google Scholar] [CrossRef]

- Villarreal-Reyes, S.; Edwards, R.M. Maximum Free Distance Binary to M-ary Convolutional Codes for Pseudo Chaotic Type Time Hopping PPM Impulse Radio UWB. IEEE Microw. Wirel. Compon. Lett. 2007, 17, 250–252. [Google Scholar] [CrossRef]

- Villarreal-Reyes, S.; Edwards, R.M.; Villaseñor-Gonzalez, L.; Conte-Galvan, R.; Aquino-Santos, R. Maximum Free Distance Rate 1/2 Spectral Line Free Convolutional Codes for BPSK/Q-BOPPM TH-IR UWB Systems. IEEE Microw. Wirel. Compon. Lett. 2011, 21, 166–168. [Google Scholar]

- Perez-Ramos, A.E.; Villarreal-Reyes, S.; Arvizu-Mondragón, A.; Lepers, C.; Santos-Aguilar, J. Spectral line suppression capabilities of spectral line free convolutional codes in UWB over fiber systems. Microw. Opt. Technol. Lett. 2014, 56, 1712–1715. [Google Scholar] [CrossRef]

- Mo, S.; Gelman, A. Scrambler design to reduce power spectral density of UWB signals in IEEE 802.15.3a. In Proceedings of the 2004 IEEE International Conference on Communications (IEEE Cat. No.04CH37577), Paris, France, 20–24 June 2004; Volume 6, pp. 3586–3590. [Google Scholar] [CrossRef]

- Kouassi, K.; Clavier, L.; Doumbia, I.; Rolland, P.-A. Optimal PWR Codes for TH-PPM UWB Multiple-Access Interference Mitigation. IEEE Commun. Lett. 2013, 17, 103–106. [Google Scholar] [CrossRef]

- Sim, S.; Kim, D.-W.; Hong, S. A CMOS UWB Pulse Generator for 6–10 GHz Applications. IEEE Microw. Wirel. Compon. Lett. 2009, 19, 83–85. [Google Scholar] [CrossRef]

- Zhao, M.J.; Li, B.; Wu, Z.H. 20-pJ/Pulse 250 Mbps Low-Complexity CMOS UWB Transmitter for 3–5 GHz Applications. IEEE Microw. Wirel. Compon. Lett. 2013, 23, 158–160. [Google Scholar] [CrossRef]

- Dong, R.; Kanaya, H.; Pokharel, R.K. A CMOS Ultrawideband Pulse Generator for 3–5 GHz Applications. IEEE Microw. Wirel. Compon. Lett. 2017, 27, 584–586. [Google Scholar] [CrossRef]

- Hedayati, H.; Entesari, K. A 90-nm CMOS UWB Impulse Radio Transmitter with 30-dB In-Band Notch at IEEE 802.11a System. IEEE Trans. Microw. Theory Technol. 2013, 61, 4220–4232. [Google Scholar] [CrossRef]

- Gunturi, P.; Emanetoglu, N.W.; Kotecki, D.E. A 250-Mb/s Data Rate IR-UWB Transmitter Using Current-Reused Technique. IEEE Trans. Microw. Theory Technol. 2017, 65, 4255–4265. [Google Scholar] [CrossRef]

- Choi, Y.; Kim, Y.; Hoang, H.; Bien, F. A 3.1–4.8-GHz IR-UWB All-Digital Pulse Generator with Variable Channel Selection in 0.13-μm CMOS Technology. IEEE Trans. Circuits Syst. II Express Briefs 2012, 59, 282–286. [Google Scholar] [CrossRef]

- Na, K.; Jang, H.; Ma, H.; Choi, Y.; Bien, F. A 200-Mb/s Data Rate 3.1–4.8-GHz IR-UWB All-Digital Pulse Generator with DB-BPSK Modulation. IEEE Trans. Circuits Syst. II Express Briefs 2015, 62, 1184–1188. [Google Scholar] [CrossRef]

- Werther, O.; Cavin, M.; Schneider, A.; Renninger, R.; Liang, B.; Bu, L.; Jin, Y.; Rogers, J.; Marcincavage, J. A Fully Integrated 14 Band, 3.1 to 10.6 GHz 0.13 μm SiGe BiCMOS UWB RF Transceiver. IEEE J. Solid-State Circuits 2008, 43, 2829–2843. [Google Scholar] [CrossRef]

- Phan, T.-A.; Lee, J.; Krizhanovskii, V.; Han, S.-K.; Lee, S.-G. A 18-pJ/Pulse OOK CMOS Transmitter for Multiband UWB Impulse Radio. IEEE Microw. Wirel. Compon. Lett. 2007, 17, 688–690. [Google Scholar] [CrossRef]

- Zheng, Y.; Zhu, Y.; Ang, C.-W.; Gao, Y.; Heng, C.-H. A 3.54 nJ/bit-RX, 0.671 nJ/bit-TX Burst Mode Super-Regenerative UWB Transceiver in 0.18-μm CMOS. IEEE Trans. Circuits Syst. I Regul. Pap. 2014, 61, 2473–2481. [Google Scholar] [CrossRef]

- Mercier, P.P.; Daly, D.C.; Chandrakasan, A.P. An Energy-Efficient All-Digital UWB Transmitter Employing Dual Capacitively-Coupled Pulse-Shaping Drivers. IEEE J. Solid-State Circuits 2009, 44, 1679–1688. [Google Scholar] [CrossRef]

- Bourdel, S.; Bachelet, Y.; Gaubert, J.; Vauche, R.; Fourquin, O.; Dehaese, N.; Barthelemy, H. A 9-pJ/Pulse 1.42-Vpp OOK CMOS UWB Pulse Generator for the 3.1–10.6-GHz FCC Band. IEEE Trans. Microw. Theory Technol. 2010, 58, 65–73. [Google Scholar] [CrossRef]

- Shen, M.; Yin, Y.-Z.; Jiang, H.; Tian, T.; Mikkelsen, J.H. A 3–10 GHz IR-UWB CMOS Pulse Generator With 6 mW Peak Power Dissipation Using A Slow-Charge Fast-Discharge Technique. IEEE Microw. Wirel. Compon. Lett. 2014, 24, 634–636. [Google Scholar] [CrossRef][Green Version]

- Radic, J.; Brkic, M.; Djugova, A.; Videnovic-Misic, M.; Goll, B.; Zimmermann, H. Area and Power Efficient 3–8.8-GHz IR-UWB Transmitter with Spectrum Tunability. IEEE Microw. Wirel. Compon. Lett. 2020, 30, 39–42. [Google Scholar] [CrossRef]

- Price, R.; Green, P.E. A Communication Technique for Multipath Channels. Proc. IRE 1958, 46, 555–570. [Google Scholar] [CrossRef]

- Wang, M.; Han, Y.; Sheng, W. A Bayesian Approach to Adaptive RAKE Receiver. IEEE Access 2018, 6, 3648–3654. [Google Scholar] [CrossRef]

- Cassioli, D.; Win, M.Z.; Vatalaro, F.; Molisch, A.F. Low Complexity Rake Receivers in Ultra-Wideband Channels. IEEE Trans. Wirel. Commun. 2007, 6, 1265–1275. [Google Scholar] [CrossRef]

- Doukeli, A.P.; Lioumpas, A.S.; Karagiannidis, G.K.; Frangos, P.V. Increasing the Efficiency of Rake Receivers for Ultra-Wideband Applications. Wirel. Pers. Commun. 2012, 62, 715–728. [Google Scholar] [CrossRef]

- Eslami, M.; Dong, X. Performance of rake-MMSE-equalizer for UWB communications. In Proceedings of the IEEE Wireless Communications and Networking Conference, New Orleans, LA, USA, 13–17 March 2005. [Google Scholar] [CrossRef]

- Xiao-Fei, K.; Bai-Ping, L.; Qi-Chang, S. A Rake-MMSE Receiver Based on RLS Algorithm for UWB Systems. In Proceedings of the 2016 International Symposium on Computer, Consumer and Control (IS3C), Xi’an, China, 4–6 July 2016; pp. 136–139. [Google Scholar] [CrossRef]

- Medi, A.; Namgoong, W. A High Data-Rate Energy-Efficient Interference-Tolerant Fully Integrated CMOS Frequency Channelized UWB Transceiver for Impulse Radio. IEEE J. Solid-State Circuits 2008, 43, 974–980. [Google Scholar] [CrossRef]

- Ryckaert, J.; Verhelst, M.; Badaroglu, M.; D’Amico, S.; De Heyn, V.; Desset, C.; Nuzzo, P.; Van Poucke, B.; Wambacq, P.; Baschirotto, A.; et al. A CMOS Ultra-Wideband Receiver for Low Data-Rate Communication. IEEE J. Solid-State Circuits 2007, 42, 2515–2527. [Google Scholar] [CrossRef]

- Anis, M.; Tielert, R. Low power UWB pulse radio transceiver front-end. In Proceedings of the ESSCIRC 2007—33rd European Solid-State Circuits Conference, Munich, Germany, 11–13 September 2007; pp. 131–134. [Google Scholar] [CrossRef]

- Terada, T.; Yoshizumi, S.; Muqsith, M.; Sanada, Y.; Kuroda, T. A CMOS ultra-wideband impulse radio transceiver for 1-mb/s data communications and /spl plusmn/2.5-cm range finding. IEEE J. Solid-State Circuits 2006, 41, 891–898. [Google Scholar] [CrossRef]

- Van Helleputte, N.; Gielen, G. A 70 pJ/Pulse Analog Front-End in 130 nm CMOS for UWB Impulse Radio Receivers. IEEE J. Solid-State Circuits 2009, 44, 1862–1871. [Google Scholar] [CrossRef]

- Viterbi, A.J. Error Bounds for Convolutional Codes and an Asymptotically Optimum Decoding Algorithm. IEEE Trans. Inform. Theory 1967, 13, 260–269. [Google Scholar] [CrossRef]

- Liu, R.; Parhi, K.K. Minimal complexity low-latency architectures for Viterbi decoders. In Proceedings of the 2008 IEEE Workshop on Signal Processing Systems, Washington, DC, USA, 8–10 October 2008; pp. 140–145. [Google Scholar] [CrossRef]

- Fettweis, G.; Meyr, H. High-rate Viterbi processor: A systolic array solution. IEEE J. Sel. Areas Commun. 1990, 8, 1520–1534. [Google Scholar] [CrossRef]

- Parhi, K.K. An Improved Pipelined MSB-First Add-Compare Select Unit Structure for Viterbi Decoders. IEEE Trans. Circuits Syst. I Regul. Pap. 2004, 51, 504–511. [Google Scholar] [CrossRef]

- Goo, Y.-J.; Lee, H. Two bit-level pipelined viterbi decoder for high-performance UWB applications. In Proceedings of the 2008 IEEE International Symposium on Circuits and Systems (ISCAS), Seattle, WA, USA, 18–21 May 2008; pp. 1012–1015. [Google Scholar] [CrossRef]

- Kong, J.J.; Parhi, K. Low-latency architectures for high-throughput rate Viterbi decoders. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2004, 12, 642–651. [Google Scholar] [CrossRef]

- Cheng, C.; Parhi, K.K. Hardware Efficient Low-Latency Architecture for High Throughput Rate Viterbi Decoders. IEEE Trans. Circuits Syst. II Express Briefs 2008, 55, 1254–1258. [Google Scholar] [CrossRef][Green Version]

- Liu, R.; Parhi, K.K. Low-Latency Low-Complexity Architectures for Viterbi Decoders. IEEE Trans. Circuits Syst. I Regul. Pap. 2009, 56, 2315–2324. [Google Scholar] [CrossRef]

- Srivastava, S.; McSweeney, R.; Spagnol, C.; Popovici, E. Efficient Berlekamp-Massey based recursive decoder for Reed-Solomon codes. In Proceedings of the 2012 28th International Conference on Microelectronics Proceedings, Nis, Serbia, 13–16 May 2012; pp. 379–382. [Google Scholar] [CrossRef]

- Berlekamp, E.R. Algebraic Coding Theory; McGraw-Hill: New York, NY, USA, 1968. [Google Scholar]

- Reed, I.; Shih, M.; Truong, T. VLSI design of inverse-free Berlekamp—Massey algorithm. IEE Proc. E Comput. Digit. Technol. 1991, 138, 295–298. [Google Scholar] [CrossRef]

- Sarwate, D.V.; Shanbhag, N.R. High-speed architectures for Reed-Solomon decoders. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2001, 9, 641–655. [Google Scholar] [CrossRef]

- Liang, Z.; Zhang, W. Efficient Berlekamp-Massey Algorithm and Architecture for Reed-Solomon Decoder. J. Signal Process. Syst. 2017, 86, 51–65. [Google Scholar] [CrossRef]

- Liu, Y.; Liang, Z.; Wang, Y.; Lu, W.; Zhang, W. Area-Efficient Reed–Solomon Decoder Using Recursive Berlekamp–Massey Architecture for Optical Communication Systems. IEEE Commun. Lett. 2017, 21, 2348–2351. [Google Scholar] [CrossRef]

- Lu, W.; Liang, Y.; Liu, Y.; Liang, Z.; Zhang, W. The Design of an RS Decoder Based on the mCS-RiBM Algorithm for 100 Gb/s Optical Communication Systems. IEEE Trans. Circuits Syst. II Express Briefs 2019, 66, 76–80. [Google Scholar] [CrossRef]

- Wu, Y. New Scalable Decoder Architectures for Reed–Solomon Codes. IEEE Trans. Commun. 2015, 63, 2741–2761. [Google Scholar] [CrossRef]

- Ji, W.; Zhang, W.; Peng, X.; Liu, Y. High-efficient Reed Solomon decoder design using recursive Berlekamp-Massey architecture. IET Commun. 2016, 10, 381–386. [Google Scholar] [CrossRef]

- Liu, W.W.; Lin, M.; Shi, J.W.; Lin, Q.H.; Wang, G.; Wang, P.; Liu, H.B. High Throughput Low Complexity and Low Power ePiBM RS Decoder Using Fractional Folding. IEEE Trans. Circuits Syst. II Express Briefs 2021, 68, 2830–2834. [Google Scholar] [CrossRef]

- Shao, H.; Truong, T.; Deutsch, L.; Yuen, J.; Reed, I. A VLSI Design of a Pipeline Reed-Solomon Decoder. IEEE Trans. Comput. 1985, C-34, 393–403. [Google Scholar] [CrossRef] [PubMed]

- Baek, J.; Sunwoo, M. New degree computationless modified euclid algorithm and architecture for Reed-Solomon decoder. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2006, 14, 915–920. [Google Scholar] [CrossRef]

- Lee, S.; Lee, H.; Shin, J.; Ko, J.-S. A High-Speed Pipelined Degree-Computationless Modified Euclidean Algorithm Architecture for Reed-Solomon Decoders. In Proceedings of the 2007 IEEE International Symposium on Circuits and Systems, New Orleans, LA, USA, 27–30 May 2007; pp. 901–904. [Google Scholar] [CrossRef]

- Yuan, B.; Wang, Z.; Li, L.; Gao, M.; Sha, J.; Zhang, C. Area-efficient reed-solomon decoder design for optical communications. IEEE Trans. Circuits Syst. II Express Briefs 2009, 56, 469–473. [Google Scholar] [CrossRef]

- Baek, J.; Ieee, F.M.; Sunwoo, M.H. New Cost-Effective Simplified Euclid’s Algorithm for Reed-Solomon Decoders. J. Signal Process. Syst. 2013, 71, 159–168. [Google Scholar] [CrossRef]

- Hsu, H.-Y.; Yeo, J.-C.; Wu, A.-Y. Area-efficient VLSI design of Reed-Solomon decoder for 10GBase-LX4 optical communication systems. In Proceedings of the 2004 IEEE Asia-Pacific Conference on Advanced System Integrated Circuits, Fukuoka, Japan, 5 August 2004. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).