A Snapback-Free and Low Turn-Off Loss 15 kV 4H–SiC IGBT with Multifunctional P-Floating Layer

Abstract

:1. Introduction

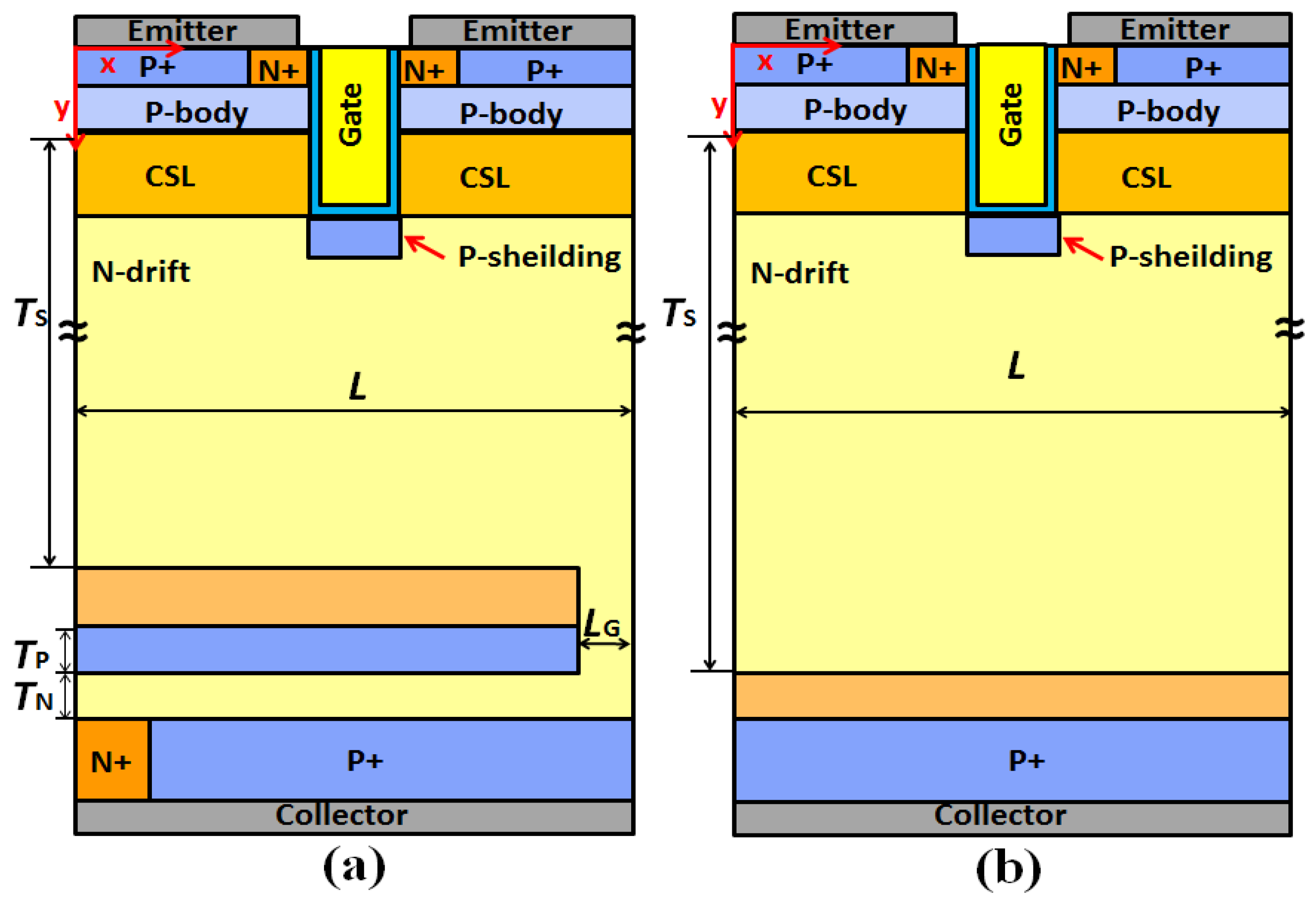

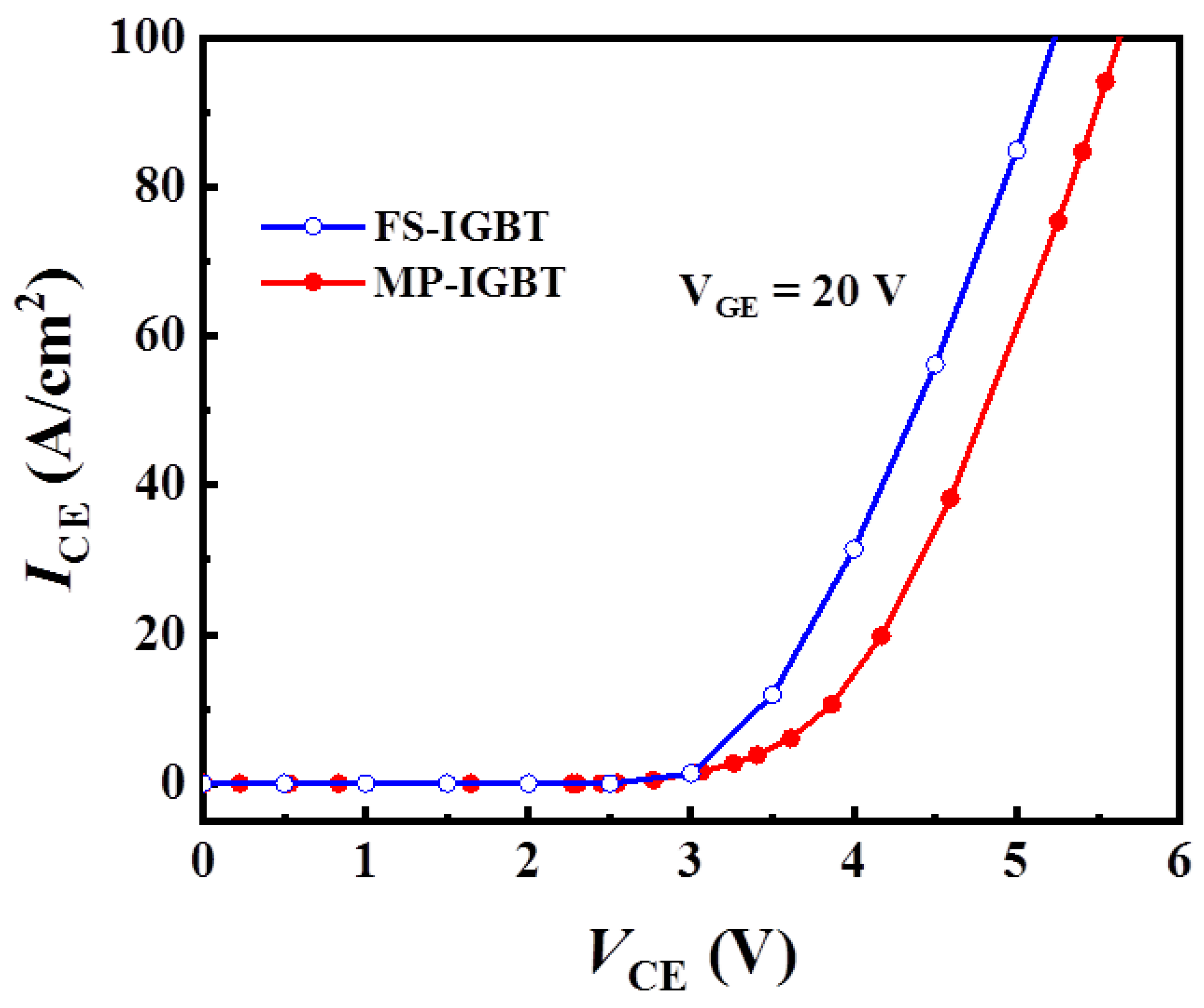

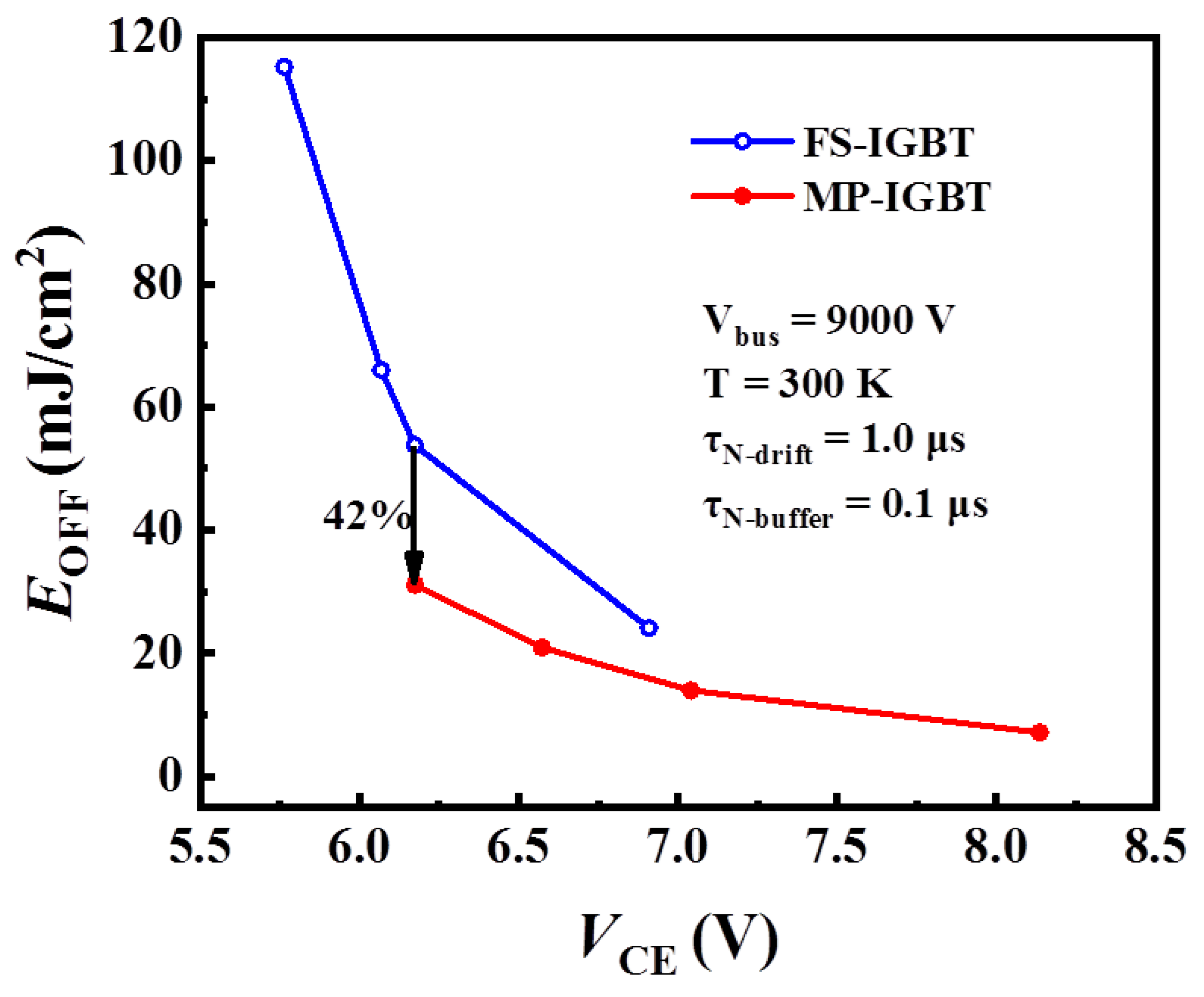

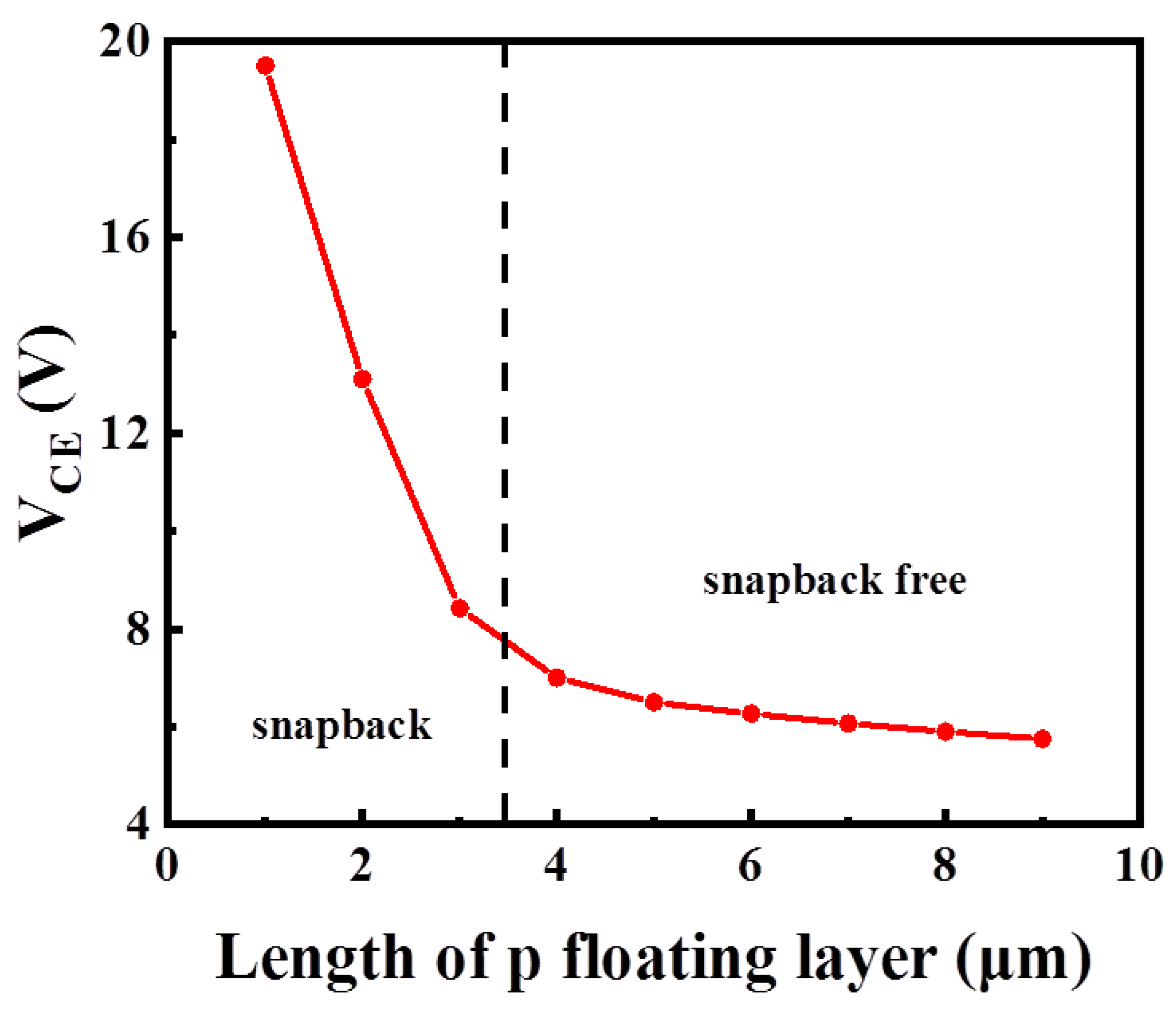

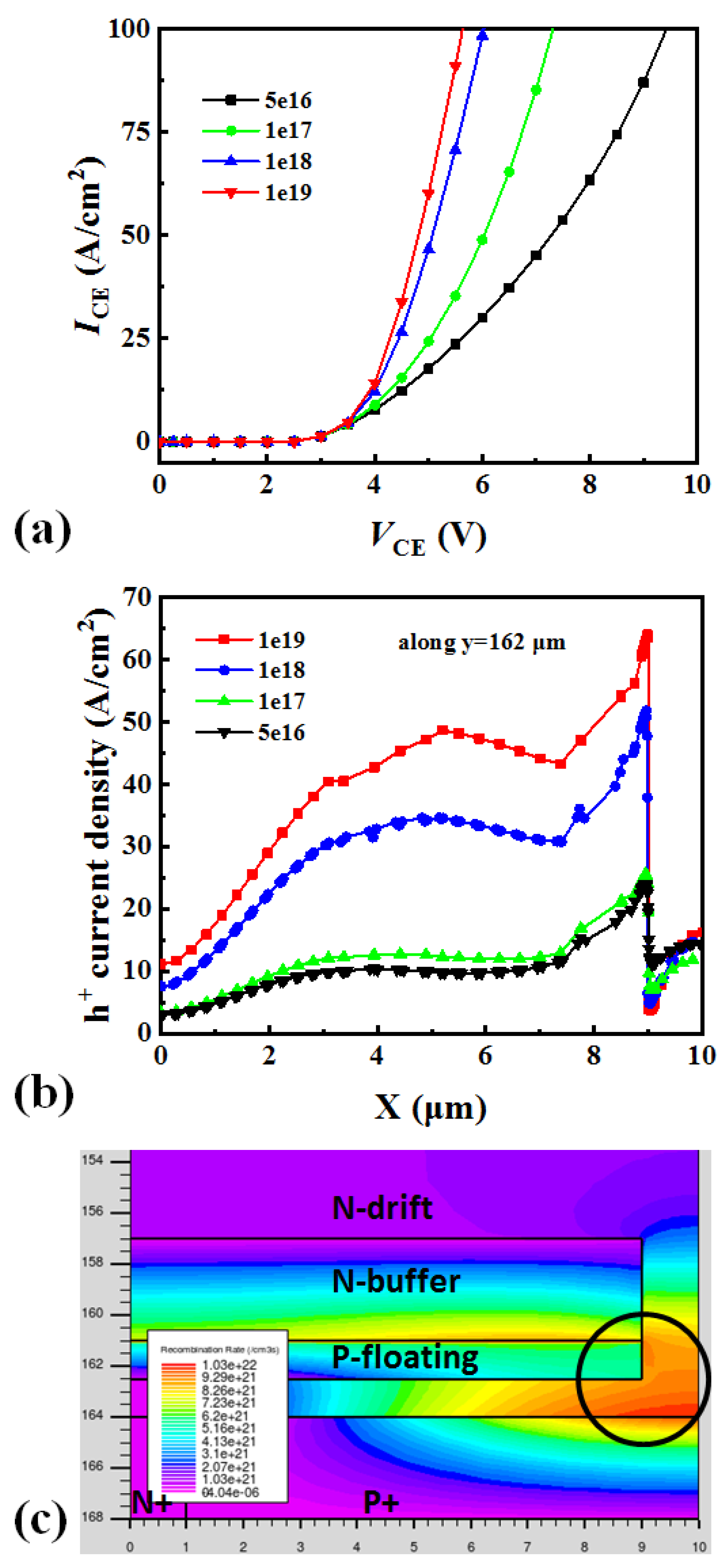

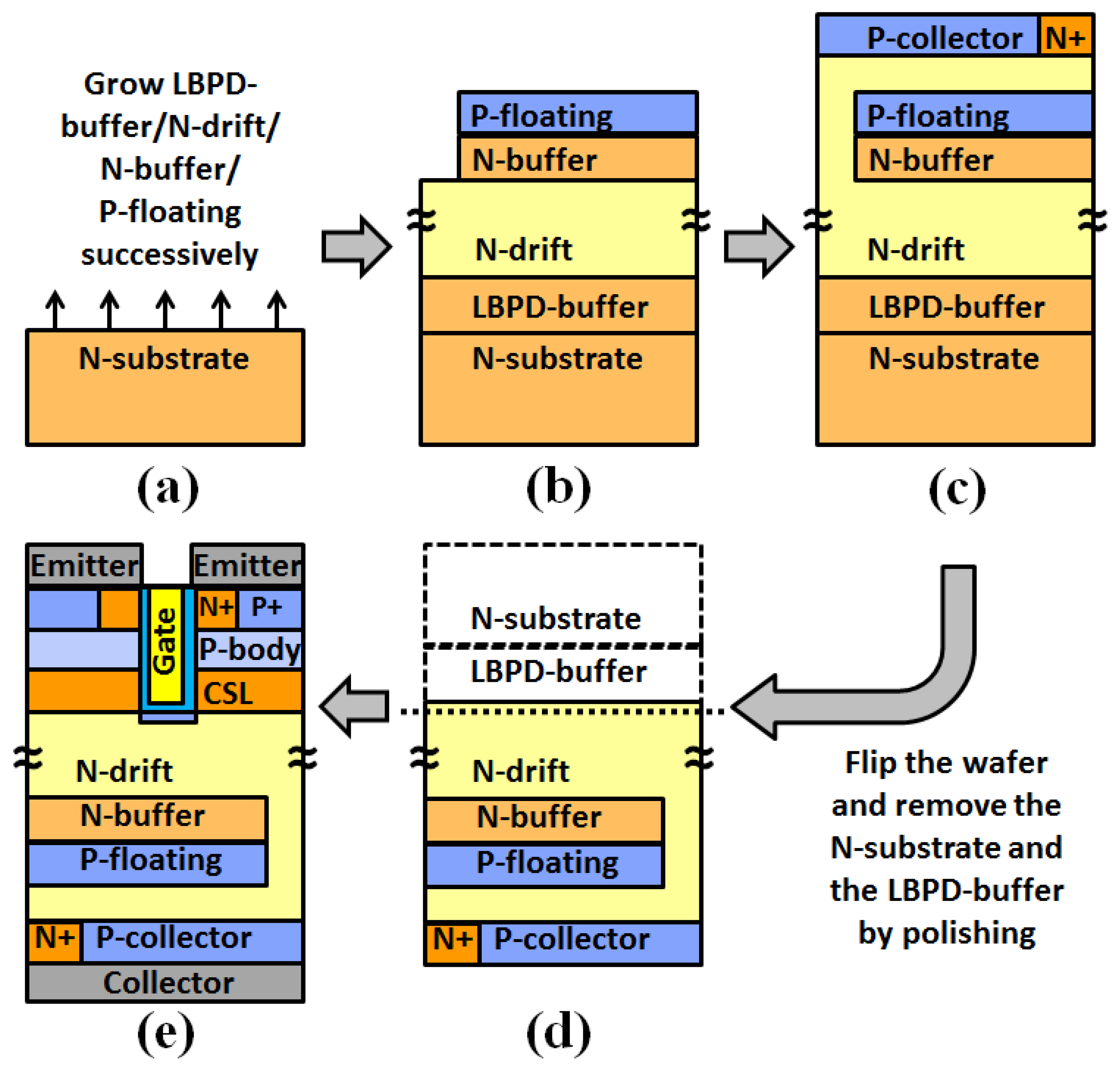

2. Devices Structure and Mechanism

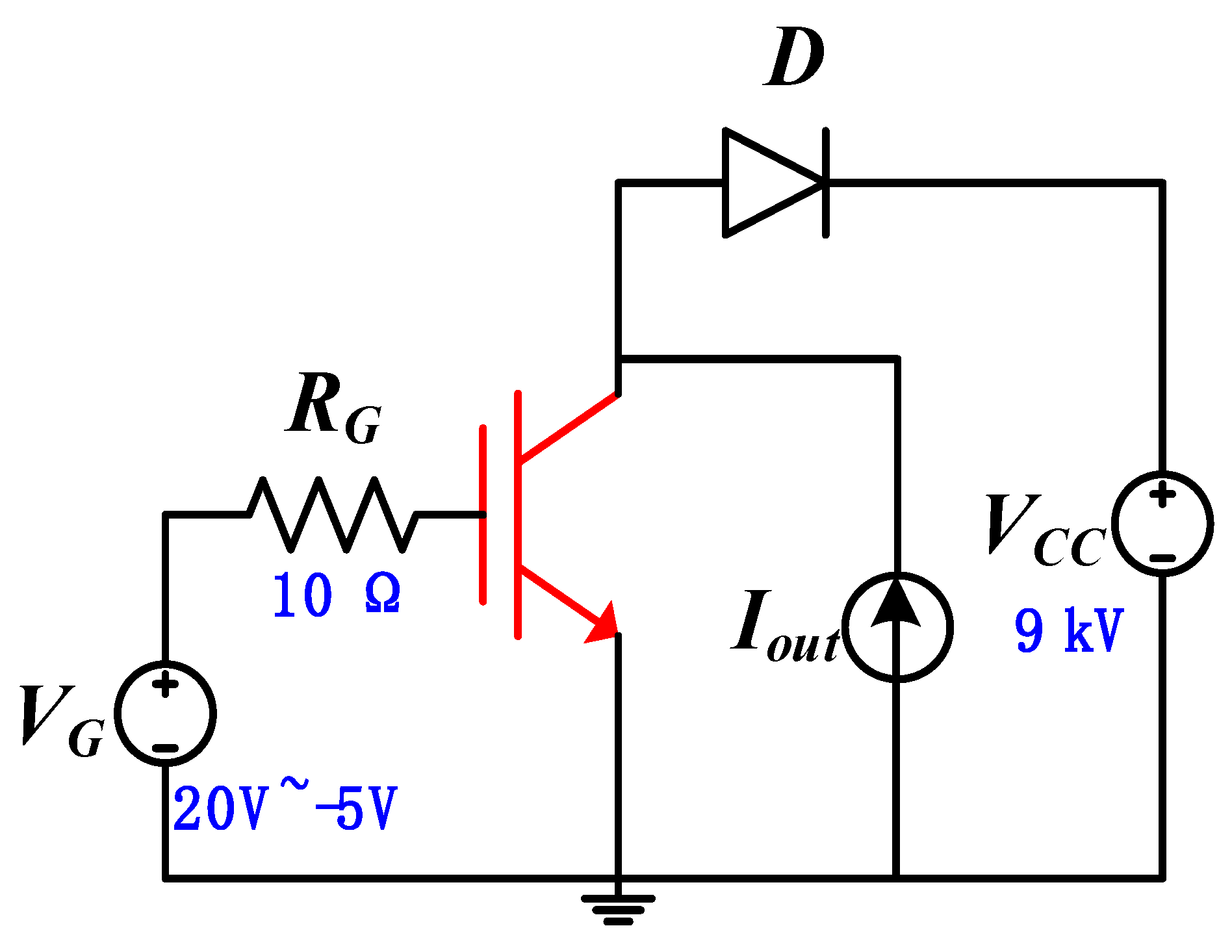

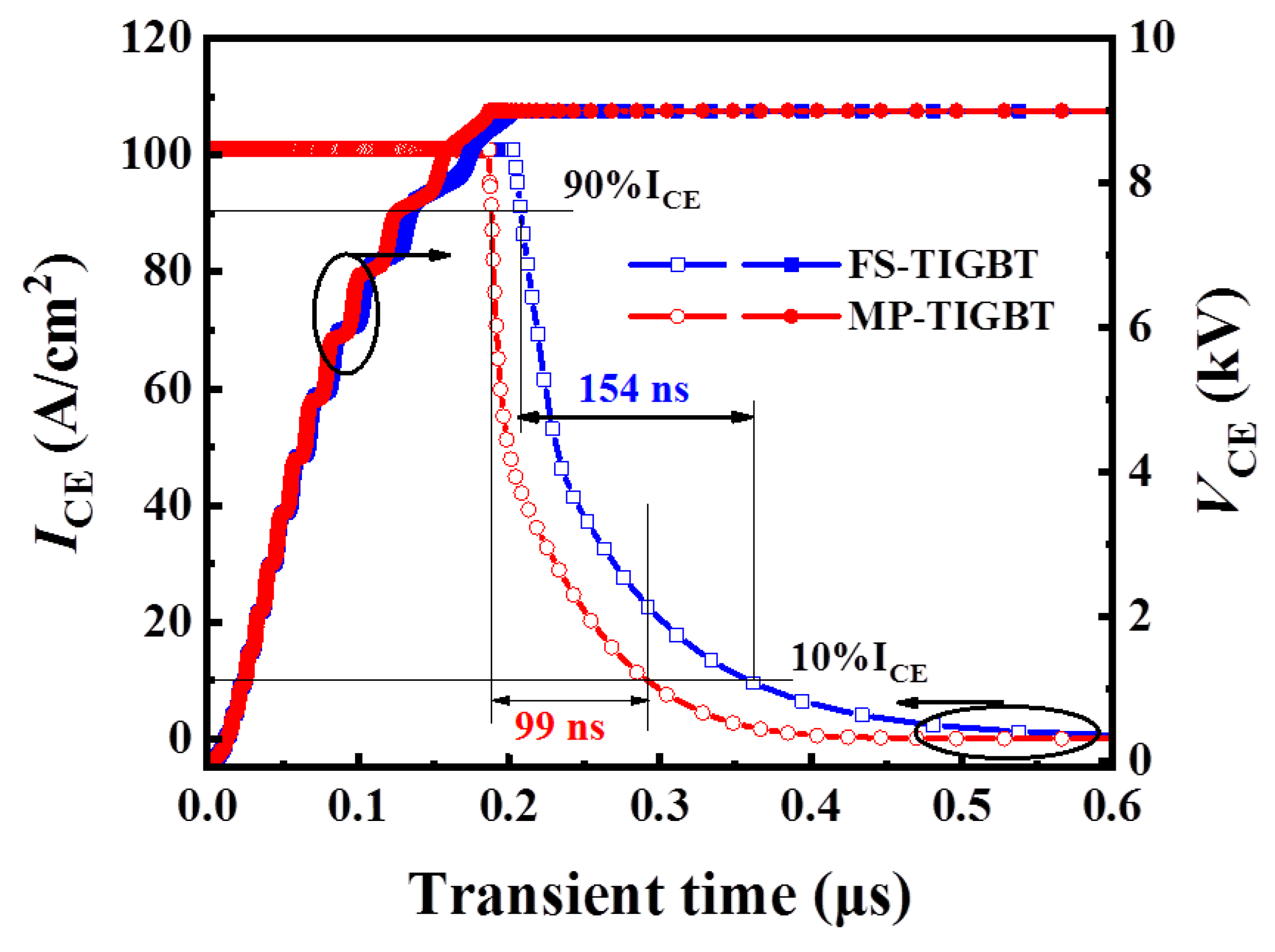

3. Simulation and Discussion

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Han, L.; Liang, L.; Kang, Y.; Qiu, Y. A Review of SiC IGBT: Models, Fabrications, Characteristics, and Applications. IEEE Trans. Power Electron. 2021, 36, 2080–2093. [Google Scholar] [CrossRef]

- Chowdhury, S.; Hitchcock, C.; Stum, Z.; Dahal, R.; Bhat, I.B.; Chow, T.P. 4H-SiC n-Channel Insulated Gate Bipolar Transistors on (0001) and (000-1) Oriented Free-Standing n(-) Substrates. IEEE Electron. Device Lett. 2016, 37, 317–320. [Google Scholar] [CrossRef]

- Sung, W.; Wang, J.; Huang, A.Q.; Baliga, B.J. Design and investigation of frequency capability of 15kV 4H-SiC IGBT. In Proceedings of the IEEE 21st International Symposium on Power Semiconductor Devices & IC’s (ISPSD), Barcelona, Spain, 14–18 June 2009; pp. 271–274. [Google Scholar]

- Zhang, Q.; Jonas, C.; Ryu, S.-H.; Agarwal, A.; Palmour, J. Design and fabrications of high voltage IGBTs on 4H-SiC. In Proceedings of the IEEE 18th International Symposium on Power Semiconductor Devices IC’s (ISPSD), Naples, Italy, 4–8 June 2006; pp. 1–4. [Google Scholar]

- Brunt, E.V.; Cheng, L.; O’Loughlin, M.; Capell, C.; Jonas, C.; Lam, K.; Richmond, J.; Pala, V.; Ryu, S.; Allen, S.T.; et al. 22 kV, 1 cm(2), 4H-SiC n-IGBTs with Improved Conductivity Modulation. In Proceedings of the IEEE 26th International Symposium on Power Semicond. Devices IC’s (ISPSD), Waikoloa, HI, USA, 15–19 June 2014; pp. 358–361. [Google Scholar]

- Sui, Y.; Cooper, J.A.; Wang, X.; Walden, G.G. Design, Simulation, and Characterization of High-Voltage SiC p-IGBTs. Mater. Sci. Forum 2009, 600–603, 1191–1194. [Google Scholar] [CrossRef]

- Sui, Y.; Wang, X.; Cooper, J.A. High-voltage self-aligned p-channel DMOS-IGBTs in 4H-SiC. IEEE Electron Device Lett. 2007, 28, 728–730. [Google Scholar] [CrossRef]

- Sui, Y.; Walden, G.G.; Wang, X.; Cooper, J. A, Device options and design considerations for high-voltage (10–20 kV) SiC power switching devices. Mater. Sci. Forum 2006, 527–529, 1449–1452. [Google Scholar] [CrossRef]

- Liu, Y.-J.; Wang, Y.; Hao, Y.; Fang, J.-P.; Shan, C.; Cao, F. A Low Turn-Off Loss 4H-SiC Trench IGBT With Schottky Contact in the Collector Side. IEEE Trans. Electron Devices 2017, 64, 4575–4580. [Google Scholar] [CrossRef]

- Liu, Y.-J.; Wang, Y.; Hao, Y.; Yu, C.-H.; Cao, F. 4H-SiC Trench IGBT With Back-Side n-p-n Collector for Low Turn-OFF Loss. IEEE Trans. Electron Devices 2017, 64, 488–493. [Google Scholar] [CrossRef]

- Tang, G.; Tang, X.; Song, Q.; Yang, S.; Zhang, Y.; Zhang, Y.; Zhang, Y. Frequency-Improved 4H-SiC IGBT With Multizone Collector Design. IEEE Trans. Electron Devices 2020, 67, 198–203. [Google Scholar] [CrossRef]

- Wei, J.; Luo, X.; Huang, L.; Zhang, B. Simulation Study of a Novel Snapback-Free and Low Turn-Off Loss Reverse-Conducting IGBT with Controllable Trench Gate. IEEE Electron Device Lett. 2018, 39, 252–255. [Google Scholar] [CrossRef]

- Jiang, H.; Zhang, B.; Chen, W.; Li, Z.; Liu, C.; Rao, Z.; Dong, B. A Snapback Suppressed Reverse-Conducting IGBT with a Floating p-Region in Trench Collector. IEEE Electron Device Lett. 2012, 33, 417–419. [Google Scholar] [CrossRef]

- Luther-King, N.; Sweet, M.; Spulber, O.; Vershinin, K.; Souza, M.M.D.; Narayanan, E.M.S. Striped anode engineering: A concept for fast switching power devices. Solid-State Electron. 2002, 46, 903–909. [Google Scholar] [CrossRef]

- Green, D.W.; Vershinin, K.V.; Sweet, M.; Narayanan, E.M.S. Anode engineering for the insulated gate bipolar transistor—A comparative review. IEEE Trans. Power Electron. 2007, 22, 1857–1866. [Google Scholar] [CrossRef]

- Sun, L.; Duan, B.; Yang, Y. High Novel Snapback-Free SOI LIGBT with Shorted Anode and Trench Barriers. IEEE Trans. Electron Devices 2021, 68, 2408–2413. [Google Scholar] [CrossRef]

- Luo, X.; Yang, Y.; Sun, T.; Wei, J.; Fan, D.; Ouyang, D.; Deng, G.; Yang, Y.; Zhang, B.; Li, Z. A Snapback-Free and Low-Loss Shorted-Anode SOI LIGBT with Self-Adaptive Resistance. IEEE Trans. Electron Devices 2019, 66, 1390–1395. [Google Scholar] [CrossRef]

- Vemulapati, U.; Kaminski, N.; Silber, D.; Storasta, L.; Rahimo, M. Reverse conducting-IGBTs initial snapback phenomenon and its analytical modeling. IET Circuits Devices Syst. 2014, 8, 168–175. [Google Scholar] [CrossRef]

- Tamaki, T.; Walden, G.G.; Sui, Y.; Cooper, J.A. Numerical study of the turnoff behavior of high-voltage 4H-SiC IGBTs. IEEE Trans. Electron Devices 2008, 55, 1928–1933. [Google Scholar] [CrossRef]

- Usman, M.; Nawaz, M. Device design assessment of 4H-SiC n-IGBT—A simulation study. Solid-State Electron. 2014, 92, 5–11. [Google Scholar] [CrossRef]

- Nawaz, M.; Chimento, F. On The TCAD Based Design Diagnostic Study of 4H-SiC Based IGBTs. Mater. Sci. Forum 2014, 778–780, 1034–1037. [Google Scholar] [CrossRef]

- Wang, X.; Cooper, J.A. High-Voltage n-Channel IGBTs on Free-Standing 4H-SiC Epilayers. IEEE Trans. Electron Devices 2010, 57, 511–515. [Google Scholar] [CrossRef]

- Chowdhury, S.; Hitchcock, C.; Dahal, R.; Bhat, I.B.; Chow, T.P. High Voltage 4H-SiC Bi-Directional IGBTs. In Proceedings of the IEEE 28th International Symposium on Power Semiconductor Devices IC’s (ISPSD), Prague, Czech Republic, 12–16 June 2016; pp. 463–466. [Google Scholar]

- Mizushima, T.; Takenaka, K.; Fujisawa, H.; Kato, T.; Harada, S.; Tanaka, Y.; Okamoto, M.; Sometani, M.; Okamoto, D.; Kumagai, N.; et al. Dynamic Characteristics of Large Current Capacity Module using 16-kV Ultrahigh Voltage SiC Flip-Type n-channel IE-IGBT. In Proceedings of the IEEE 26th International Symposium on Power Semiconductor Devices & ICs (ISPSD), Waikoloa, HI, USA, 15–19 June 2014; pp. 277–280. [Google Scholar]

- Yonezawa, Y.; Mizushima, T.; Takenaka, K.; Fujisawa, H.; Kato, T.; Harada, S.; Tanaka, Y.; Okamoto, M.; Sometani, M.; Okamoto, D.; et al. Low V-f and Highly Reliable 16 kV Ultrahigh Voltage SiC Flip-Type n-channel Implantation and Epitaxial IGBT. In Proceedings of the 2013 IEEE International Electron Devices Meeting, Washington, DC, USA, 9–11 December 2013; pp. 661–664. [Google Scholar]

| Parameters | MP-IGBT | FS-IGBT |

|---|---|---|

| MOS cell pitch (μm), LM | 10 | 10 |

| Gate oxide thickness (nm), Tox | 50 | 50 |

| Gate trench depth (μm), DG | 5 | 5 |

| Drift region doping (cm−3), Nd | 4.5 × 1014 | 4.5 × 1014 |

| N-buffer doping (cm−3), NNb | 1 × 1017 | 1 × 1017 |

| N-buffer thickness (μm), TNb | 4 | 4 |

| P-collector doping (cm−3), NPb | 1 × 1019 | 1 × 1019 |

| P-collector thickness (μm), TPb | 4 | 4 |

| N-collector length (μm), LN | 1 | - |

| Half collector length (μm), L | 10 | 10 |

| N-drift thickness (μm), TS | 155 | 155 |

| CSL doping (cm−3), NCSL | 1 × 1015 | 1 × 1015 |

| P-base doping (cm−3), Nbase | 4 × 1017 | 4 × 1017 |

| P-floating layer thickness (μm), Tpf | 1.5 | - |

| Length of P-floating layer (μm), Lpf | 1~9 | - |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhang, X.; Shen, P.; Zou, Z.; Song, M.; Zhang, L. A Snapback-Free and Low Turn-Off Loss 15 kV 4H–SiC IGBT with Multifunctional P-Floating Layer. Micromachines 2022, 13, 734. https://doi.org/10.3390/mi13050734

Zhang X, Shen P, Zou Z, Song M, Zhang L. A Snapback-Free and Low Turn-Off Loss 15 kV 4H–SiC IGBT with Multifunctional P-Floating Layer. Micromachines. 2022; 13(5):734. https://doi.org/10.3390/mi13050734

Chicago/Turabian StyleZhang, Xiaodong, Pei Shen, Zhijie Zou, Mingxin Song, and Linlin Zhang. 2022. "A Snapback-Free and Low Turn-Off Loss 15 kV 4H–SiC IGBT with Multifunctional P-Floating Layer" Micromachines 13, no. 5: 734. https://doi.org/10.3390/mi13050734

APA StyleZhang, X., Shen, P., Zou, Z., Song, M., & Zhang, L. (2022). A Snapback-Free and Low Turn-Off Loss 15 kV 4H–SiC IGBT with Multifunctional P-Floating Layer. Micromachines, 13(5), 734. https://doi.org/10.3390/mi13050734