Abstract

This paper proposes a simplified fabrication processing for nanosheet Field-Effect Transistors (FETs) part of beyond-3-nm node technology. Formation of the ground plane (GP) region can be replaced by an epitaxial grown doped ultra-thin (DUT) layer on the starting wafer prior to Six/SiGe1−x stack formation. The proposed process flow can be performed in-situ, and does not require changing chambers or a high temperature annealing process. In short, conventional processes such as ion implantation and subsequent thermal annealing, which have been utilized for the GP region, can be replaced without degrading device performance.

1. Introduction

To suppress short-channel effects (SCEs), which are an important concern with aggressive device scaling, semiconductor devices have evolved from 2-dimensional (2-D) structures to 3-dimensional (3-D) architectures. This has further benefits. For example, due to their superior gate controllability, FinFETs have lower subthreshold swing (SS) and off-state leakage (IOFF) than planar devices [1,2,3]. However, as device scaling approaches extreme levels, it is becoming difficult to control SCEs using FinFETs. As a solution, nanosheet FETs (NS FETs), which have multiple channels with a gate-all-around (GAA) backbone structure, have been introduced as beyond-FinFETs [4,5,6]. However, even though NS FETs have shown better suppression of SCEs than FinFETs, as well as better output performance, there are still many difficulties related to mass production. Producers such as Samsung Electronics Inc. and TSMC Inc. are planning the mass production of NS FETs in 2022 and 2023, respectively. However, it is unknown whether the yield will be sufficient. The reason for this lies in difficulties in the fabrication processing of the NS FETs. For example, surface roughness scattering stemming from germanium diffusion among the nanosheets, striction stemming from adhesion between nanosheets [6], residue formation (e.g., TiN or Si3N4) due to uncontrollable wet etching, unwanted void formation during metal gate filling [7], etc., are very challenging problems in current fabrication processing.

In addition, with respect to source/drain (S/D) modules, the contact depth as well as inner spacer thickness needs to be optimized [8,9]. It should be noted in particular that, unlike bulk FinFETs, which have already been mass produced, NS FETs have a parasitic channel underneath the first floor nanosheet [10,11,12,13]. Hence, even though NS FETs have multiple channels that are completely surrounded by metal gates (i.e., GAA), increased IOFF stemming from the parasitic channel is inevitable. V. Jegadheesan et al., have suggested that applying a ground plane (GP) region can effectively minimize the IOFF in the parasitic channel [14]. However, as we have mentioned above, the fabrication process flow of NS FETs is very sensitive. For example, ion implantation and rapid thermal annealing (RTA) for GP region formation are associated with an unwanted non-uniform doping profile [15,16]. In this context, it would be better, in terms of device variability and yield, if the conventional processes could be replaced with an alternative process. However, recently, research papers covering the fabrication process of NS FETs have been modest in number.

In this letter, we propose a fabrication process flow for NS FETs. The proposed process flow does not require ion implantation or additional thermal treatment, which are conventionally performed to form the GP region. Alternatively, a doped ultra-thin (DUT) layer is epitaxially grown on the starting wafer in-situ before Six/SiGe1−x stack formation. This achieves process simplification, improved variability, and improved yield during the fabrication of NS FETs.

2. Materials and Method

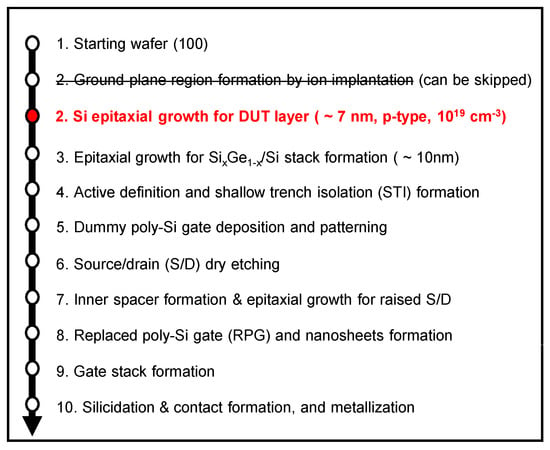

The proposed fabrication process flow is summarized in Figure 1. In the conventional NS FETs fabrication process, ion implantation and thermal annealing are performed in dashed step two for GP region formation. However, the process can be replaced by Si epitaxial growth for DUT layer formation, as described in the bolded step two. The DUT layer is doped with a p–type dopant (i.e., boron) to minimize the parasitic channel and punch-through underneath the first floor nanosheet. The thickness of the DUT is similar to the thickness of silicon and SixGe1−x layers, which are epitaxially grown as nanosheets and sacrificial layers, respectively. Hence, the formation of the DUT layer is not problematic under current processing technology. Above all, it should be noted that the processing from steps one to three in Figure 1 can be performed in-situ without changing chambers.

Figure 1.

Fabrication process flow of proposed NS FETs including epitaxially grown DUT layer prior to formation of the SixGe1−x/Si stack. The bolded step two can be alternatively added instead of the under-lined ion implantation and annealing process.

A 3-D simulator (Synopsys Sentaurus, Mountain View, CA, USA) was utilized to simulate fabrication processing and device characteristics. The drift-diffusion carrier transport equation was combined with the Poisson equation, and the density-gradient model was considered to reflect the quantum confinement effect of the nanosheet channels [17,18,19,20]. The Slotboom model was included for doping-dependent bandgap narrowing in the overall region [21]. Thin layer models such as inversion and accumulation layer mobility model (IALMob) were included to reflect impurity and phonon scattering [22]. In addition, the Shockley-Read-Hall (SRH) and non-local band-to-band tunneling (BTBT) recombination models were included to reflect gate-induced drain leakage (GIDL) during the simulations [22].

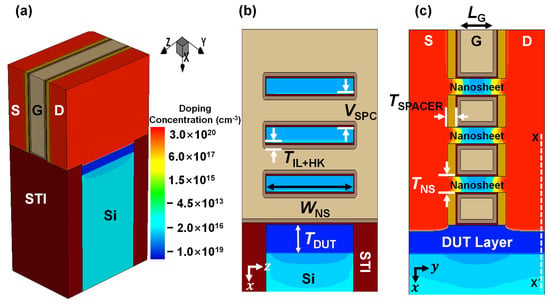

Figure 2 shows the backbone structure of the NS FETs used in the process simulation. Channel thickness (TCH) and width (WNS) were 5 nm and 45 nm, respectively. To elaborate, the dielectric constant of the HfO2 gate dielectric and effective-oxide-thickness (EOT) were assumed to be 25 and 0.7 nm, respectively. In terms of doping concentration, epitaxially grown S/D regions were doped with arsenic at 3 × 1020 cm−3 [14,23]. The three nanosheet channels and silicon substrate (NSub) were lightly doped with boron at 1 × 1017 cm−3 and 1 × 1016 cm−3, respectively. The doping concentration of the DUT layer was 1 × 1019 cm−3 of boron. The work-function of the titanium nitride for the metal gate was 4.5 eV. Detailed device parameters used for the simulations are summarized in Table 1.

Figure 2.

(a) Simulated NS FET device structure including the epitaxially–grown DUT layer on the starting wafer. Cross–sectional view of the proposed NS FET with a cut along the (b) gate and (c) channel directions, respectively.

Table 1.

Dimensions and parameters used for the TCAD simulations.

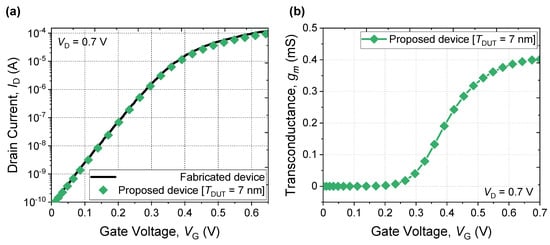

Then, the simulated ID-VG was carefully calibrated based on fabricated devices (i.e., such as doping concentration, structure, and gate work function) reported in [6], as shown in Figure 3a. Threshold voltage (VTH) was extracted using a constant current method at ID of 100 nA. Multiple VTH characteristic can be visible when series resistance of NS FET is high due to defect existence or low doping concentration of S/D regions, as well as excessively long VSPC. However, there was no observable multiple value of VTH observed in the subthreshold region. Hence such concerns were not problematic, as shown in Figure 3b.

Figure 3.

(a) Calibration of ID-VG curve with the fabricated device in Reference [6]. (b) Transconductance of (a).

3. Results and Discussion

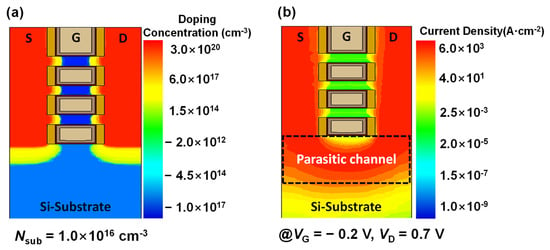

Figure 4a shows the simulated doping profile during the off-state when the GP region as well as the DUT layer were not included. An unwanted parasitic channel and punch-through were formed underneath the first floor nanosheet. These concerns led to increased IOFF during the off-state (Figure 4b).

Figure 4.

Simulated (a) doping profile distribution and (b) current density of a NS FET without a DUT layer during off–state.

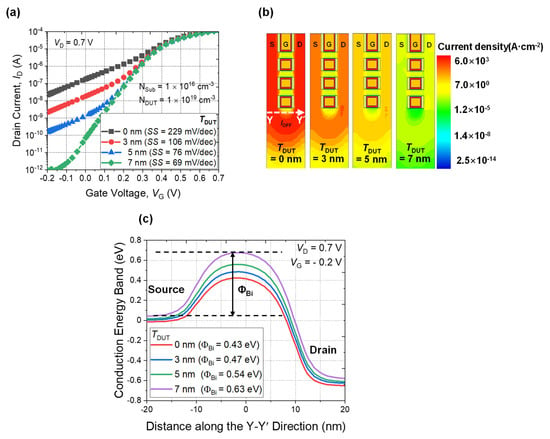

Figure 5a shows the simulated transfer characteristics of the NS FETs with various thicknesses of DUT layers (TDUT) from 0 nm to 7 nm. As the thickness of the DUT layer increases, IOFF, as well as SS, improve. The IOFF extracted at VG = −0.2 V was 21.8 nA with a 0 nm DUT layer but improved to 0.98 pA with a 7 nm DUT layer. Figure 5b shows the current density profile of the NS FETs in Figure 5a extracted at the off-state with VD = 0.7 V, VG = −0.2 V. As the TDUT increases, IOFF flowing through the parasitic channel (Y–Y′ direction) can be suppressed, aided by the increased energy barrier height (Φbi of the parasitic channel), as shown in Figure 5c. In addition, punch-through can be suppressed by applying a DUT layer.

Figure 5.

(a) Simulated ID-VG characteristic of NS FETs with various thicknesses of DUT layers without GP implantation and subsequent annealing. (b) Simulated parasitic current distribution profiles with various thicknesses of DUT layers. (c) Energy band diagram of parasitic channel along the Y–Y′ direction in (b). Conduction energy band height increases as TDUT increases.

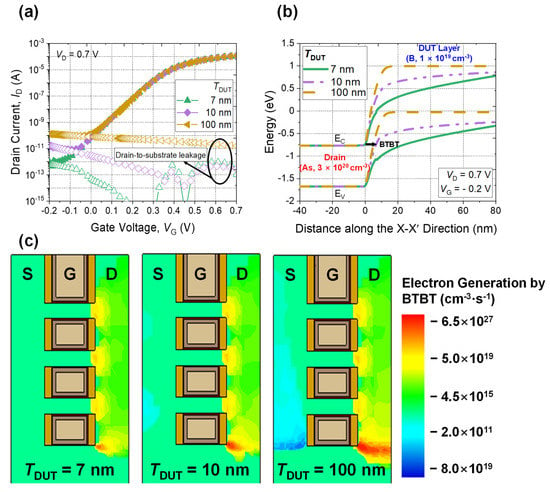

However, when TDUT is thicker than 7 nm, the IOFF increases (Figure 6a). Considering the IOFF value in the range of VG of –0.2 V to 0 V are identical to the drain–to–substrate leakage current, the source of the IOFF increase is not the parasitic channel, but rather the BTBT between the drain and the DUT layer. In other words, when TDUT is thicker than 7 nm, the DUT forms a p-n diode between the drain and the DUT layer, as shown in Figure 6b. During the off-state, the reverse biased p-n diode triggers BTBT of electrons, and increases the IOFF. Figure 6c shows the simulated rate of electron generation between the drain and the substrate by the BTBT. As the TDUT increases, there is a noticeable increase in electron generation by the BTBT. As a result, it can be concluded that a 7 nm thickness DUT layer is optimal to avoid unwanted increasing IOFF.

Figure 6.

(a) Simulated ID-VG characteristic and (b) extracted energy band diagram of NS FETs (X–X′ direction in Figure 2c) with various thicknesses of DUT layers greater than 7 nm. (c) Electron generation rates with various TDUT.

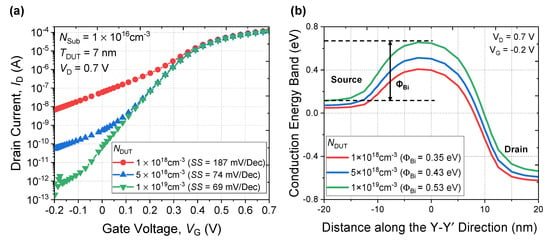

Figure 7a shows a simulated ID-VG curve for various doping concentrations (NDUT) of the DUT layer. When the NDUT is a low doping concentration of 1 × 1018 cm−3, the IOFF cannot be controlled due to increased SS. However, as the NDUT increases, leakage current through the parasitic channel can be suppressed by the increased built-in potential (Φbi) from 0.39 eV to 0.59 eV, as shown in Figure 7b. In addition, suppression of punch-through is possible with increased substrate doping concentration.

Figure 7.

(a) ID-VG characteristic with different NDUT layer. (b) Energy band diagram of the parasitic channel.

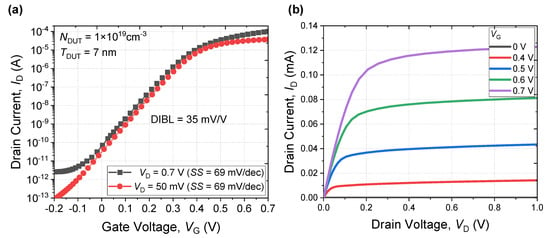

Figure 8 shows extracted ID-VG curve at VD = 50 mV and 0.7 V, as well as ID-VD curve. The drain-induced barrier lowering (DIBL) of the proposed NS FET is 35 mV, which a low value compared with the value of 33 nm of the planar FET [19] or 15 nm of FinFET [24], as summarized in Table 2. In other words, the superior gate controllability of the NS FET does not degrade even when a DUT layer is applied.

Figure 8.

(a) Extracted ID-VG and (b) ID–VD characteristics of NS FET with DUT layer.

Table 2.

Comparison of DIBL and SS characteristics with various devices.

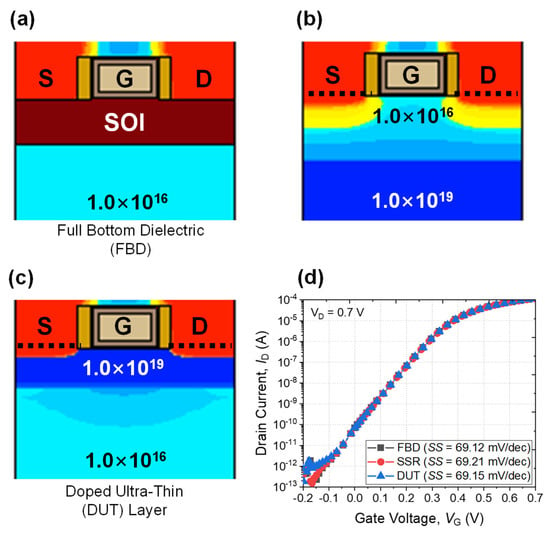

Figure 9 introduces various approaches to suppress the leakage current from the parasitic channel without the formation of a GP region [14,25]. A full bottom dielectric (FBD) can eliminate the parasitic channel perfectly (Figure 9a). However, fabrication of the FBD inevitably requires a starting wafer composed of silicon-on-insulator (SOI) which is vulnerable to self-heating as well as expensive wafer cost. In this context, a steep-retrograde (SSR) region which contains a deep and heavily doped layer is preferred. However, forming an abrupt doping profile for the SSR is impossible using ion implantation and spike annealing. Even though epitaxial growth can be utilized, at least one more epitaxial growth step is required compared to the DUT case. Figure 9d shows the simulated electrical characteristics of the FBD, SSR, and DUT structures, respectively. Even though the DUT layer has a simpler fabrication process than the others, device characteristics in terms of VTH, SS, and ION are not remarkable. Exact device parameters are summarized in Table 3.

Figure 9.

Various device structures without a GP region. NS FET with (a) full bottom dielectric (FBD) [25], (b) super steep-retrograde (SSR) region [14], and (c) the proposed DUT layer. (d) Simulated ID-VG characteristics of the respective device structures.

Table 3.

Comparison of NS FETs based on FBD, SSR, and DUT structures.

4. Conclusions

For better process simplification, the fabrication process for nanosheet FETs was newly suggested based on 3-D simulation. The doped ultra-thin (DUT) layer can be epitaxially grown in-situ on the starting wafer. Conventional ground plane (GP) doping implantation as well as annealing process can be excluded while forming the DUT layer. The thickness of the DUT layer has been optimized to suppress parasitic channel leakage, punch-through, and band-to-band tunneling (BTBT). The NS FET with the DUT layer showed comparable performance, but has a simpler fabrication process compared with other NS FETs, including full bottom dielectric (FBD) or steep-retrograde region (SSR).

Author Contributions

For J.-Y.P. conceived this project and designed all of the experiments. K.-S.L. conducted all of the simulations and wrote this paper. All authors have read and agreed to the published version of the manuscript.

Funding

This work was supported by the National Research Foundation of Korea (No. 2020M3H2A1076786 and 2021R1F1A1049456). The EDA tool was supported by the IDEC.

Data Availability Statement

Not applicable.

Conflicts of Interest

The authors declare no conflict of interest.

References

- Chang, L.; Choi, Y.-K.; Ha, D.; Ranade, P.; Xiong, S.; Bokor, J.; Hu, C.; King, T.-J. Extremely scaled silicon nano-CMOS device. Proc. IEEE 2003, 91, 1860–1873. [Google Scholar] [CrossRef] [Green Version]

- Razavieh, A.; Zeitzoff, P.; Nowak, E.J. Challenges and Limitations of CMOS Scaling for FinFET and beyond Architectures. IEEE Trans. Nanotechnol. 2019, 18, 999–1004. [Google Scholar] [CrossRef]

- Hisamoto, D.; Lee, W.; Kedzierski, J.; Takeuchi, H.; Asano, K.; Kuo, C.; Anderson, E.; King, T.J.; Bokor, J.; Hu, C. FinFET—A self-aligned double-gate MOSFET scalable to 20 nm. IEEE Trans. Electron Devices 2000, 12, 2320–2325. [Google Scholar]

- Lee, S.Y.; Kim, S.M.; Yoon, E.J.; Oh, C.W.; Chung, I.; Park, D.; Kim, K. A novel multi-bridge-channel MOSFET (MBCFET): Fabrication technologies and characteristics. IEEE Trans. Nanotechnol. 2004, 2, 253–257. [Google Scholar]

- Bae, G.; Bae, D.-I.; Kang, M.; Hwang, S.M.; Kim, S.S.; Seo, B.; Kwon, T.Y.; Lee, T.J.; Moon, C.; Choi, Y.M.; et al. 3nm GAA Technology featuring Multi-Bridge-Channel FET for Low Power and High Performance Applications. In Proceedings of the 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018; IEEE: San Francisco, CA, USA; pp. 28.7.1–28.7.4. [Google Scholar]

- Loubet, N.; Hook, T.; Montanini, P.; Yeung, C.; Kanakasabapathy, S.; Guillom, M.; Yamashita, T.; Zhang, J.; Miao, X.; Wang, J.; et al. Stacked nanosheet gate-all-around transistor to enable scaling beyond FinFET. In Proceedings of the 2017 IEEE Symposium on VLSI Technology, Kyoto, Japan, 5–8 June 2017; IEEE: Kyoto, Japan; pp. T230–T231. [Google Scholar]

- Witters, L.; Veloso, A.; Ferain, I.; Demand, M.; Collaert, N.; Son, N.J.; Adelmann, C.; Meersschaut, J.; Vos, R.; Rohr, E.; et al. Multiple-Vt FinFET devices through La2O3 dielectric capping. In Proceedings of the IEEE International SOI Conference, New Paltz, NY, USA, 6–9 October 2008; IEEE: New Paltz, NY, USA; pp. 121–122. [Google Scholar]

- Li, J.; Li, Y.; Zhou, N.; Xiong, W.; Wang, G. Study of Silicon Nitride Inner Spacer Formation in Process of Gate-all-around Nano-transistors. Nanomaterials 2020, 10, 793. [Google Scholar] [CrossRef] [PubMed]

- Lee, K.-S.; Park, J.-Y. Inner Spacer Engineering to Improve Mechanical Stability in Channel-Release Process of Nanosheet FETs. Electronics 2021, 10, 1395. [Google Scholar] [CrossRef]

- Ritzenthaler, R.; Mertens, H.; De Keersgieter, A.; Mitard, J.; Mocuta, D.; Horiguchi, N. Isolation of nanowires made on bulk wafers by ground plane doping. In Proceedings of the 2017 47th European Solid-State Device Research Conference (ESSDERC), Leuven, Belgium, 11–14 September 2017; IEEE: Leuven, Belgium; pp. 300–303. [Google Scholar]

- Choi, Y.; Lee, K.; Kim, K.Y.; Kim, S.; Lee, J.; Lee, R.; Kim, H.-M.; Song, Y.S.; Kim, S.; Lee, J.-H.; et al. Simulation of the effect of parasitic channel height on characteristics of stacked gate-all-around nanosheet FET. Solid State Electron. 2020, 164, 107686. [Google Scholar] [CrossRef]

- Hong, J.M.; Park, J.W.; Lee, J.W.; Ham, J.H.; Park, K.R.; Jeon, J.W. Alpha Particle Effect on Multi-Nanosheet Tunneling Field-Effect Transistor at 3-nm Technology Node. Micromachines 2019, 10, 847. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Seon, Y.; Chang, J.; Yoo, C.; Jeon, J. Device and Circuit Exploration of Multi-Nanosheet Transistor for Sub-3 nm Technology Node. Electronics 2021, 10, 180. [Google Scholar] [CrossRef]

- Jegadheesan, V.; Sivasankaran, K.; Konar, A. Optimized Substrate for Improved Performance of Stacked Nanosheet Field-Effect Transistor. IEEE Trans. Electron Devices 2020, 67, 4079–4084. [Google Scholar] [CrossRef]

- Ang, K.-W.; Barnett, J.; Loh, W.-Y.; Huang, J.; Min, B.-G.; Hung, P.Y.; Ok, I.; Yum, J.H.; Bersuker, G.; Rodgers, M.; et al. 300 mm FinFET results utilizing conformal, damage free, ultra shallow junctions (Xj∼5 nm) formed with molecular monolayer doping technique. In Proceedings of the 2011 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 5–7 December 2011; IEEE: Waschington, DC, USA; Volume 1–35, p. 35. [Google Scholar]

- Chen, W.C.; Lin, H.C.; Chang, Y.C.; Lin, C.D.; Huang, T.Y. In Situ Doped Source/Drain for Performance Enhancement of Double-Gated Poly-Si Nanowire Transistors. IEEE Trans. Electron Devices 2010, 57, 1608–1615. [Google Scholar] [CrossRef]

- Ancona, M.G.; Iafrate, G.J. Quantum correction to the equation of state of an electron gas in a semiconductor. Phys. Rev. B. 1989, 39, 9536–9540. [Google Scholar] [CrossRef] [PubMed]

- Huang, H.S.; Wang, W.L.; Wang, M.C.; Chao, Y.H.; Wang, S.J.; Chen, S.Y. I-V model of nano nMOSFETs incorporating drift and diffusion current. Vacuum 2018, 155, 76–82. [Google Scholar] [CrossRef]

- Chao, S.-Y.; Huang, H.-S.; Huang, P.-R.; Lin, C.-Y.; Wang, M.-C. Channel Mobility Model of Nano-Node MOSFETs Incorporating Drain-and-Gate Electric Fields. Crystals 2022, 12, 295. [Google Scholar] [CrossRef]

- Woltjer, R.; Tiemeijer, L.; Klaassen, D. An industrial view on compact modeling. Solid-State Electron. 2007, 51, 1572–1580. [Google Scholar] [CrossRef]

- Slotboom, J.W.; De Graaff, H.C. Bandgap Narrowing in Silicon Bipolar Transistors. IEEE Trans. Electron Devices 1977, 24, 1123–1125. [Google Scholar] [CrossRef]

- Sentaurus Device User Guide, Version L-2016.03; Synopsys Inc.: Mountain View, CA, USA, March 2016.

- Yoon, J.-S.; Jeong, J.S.; Lee, S.H.; Lee, J.J.; Lee, S.G.; Lim, J.W.; Baek, R.H. DC Performance Variations by Grain Boundary in Source/Drain Epitaxy of sub-3-nm Nanosheet Field-Effect Transistors. IEEE Access, 2022; in press. [Google Scholar] [CrossRef]

- Xie, R.; Montanini, P.; Akarvardar, K.; Tripathi, N.; Haran1, B.; Johnson, S.; Hook, T.; Hamieh, B.; Corliss, D.; Wang, J.; et al. A 7 nm FinFET technology featuring EUV patterning and dual strained high mobility channels. In Proceedings of the 2016 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016; IEEE: San Francisco, CA, USA; pp. 2–7. [Google Scholar]

- Zhang, J.; Frougier, J.; Greene, A. Full Bottom Dielectric Isolation to Enable Stacked Nanosheet Transistor for Low Power and High Performance Applications. In Proceedings of the IEEE 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; IEEE: San Francisco, CA, USA. [Google Scholar]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).