SiC Heterojunction Trench MOSFET with a Buried P-Type Pillar for the Low Gate-Drain Charge and Switching Loss

Abstract

:1. Introduction

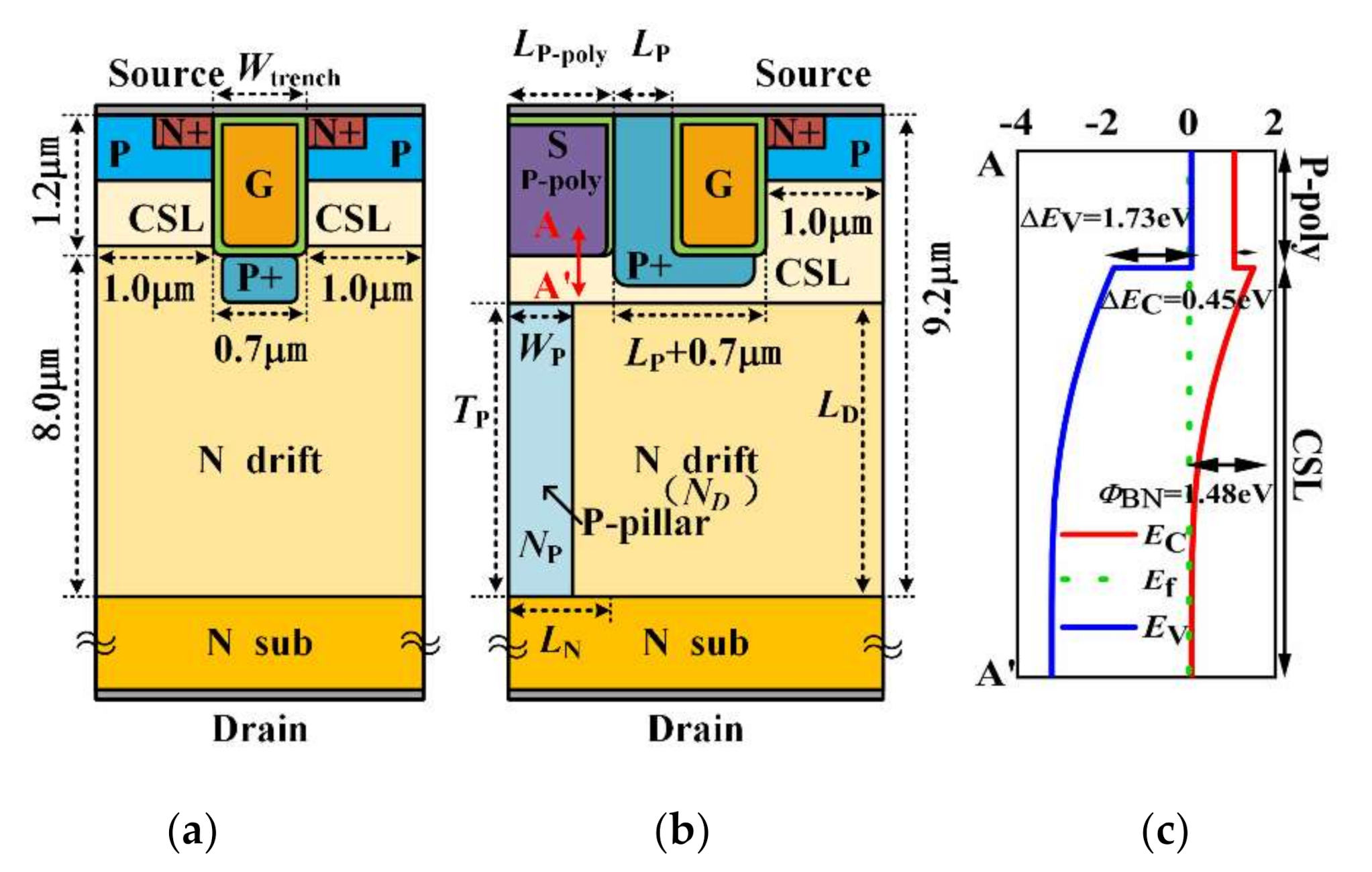

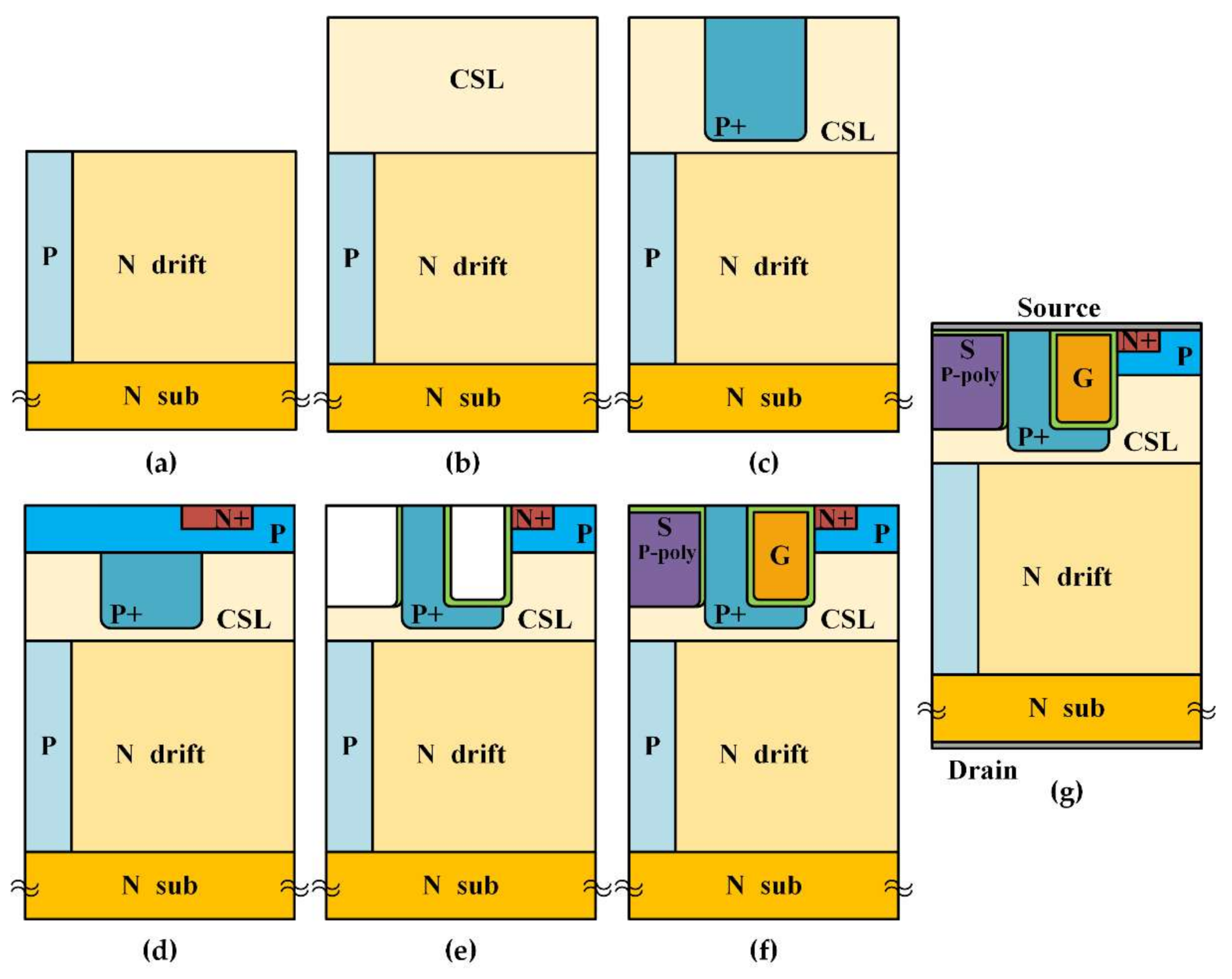

2. Device Structure and Mechanism

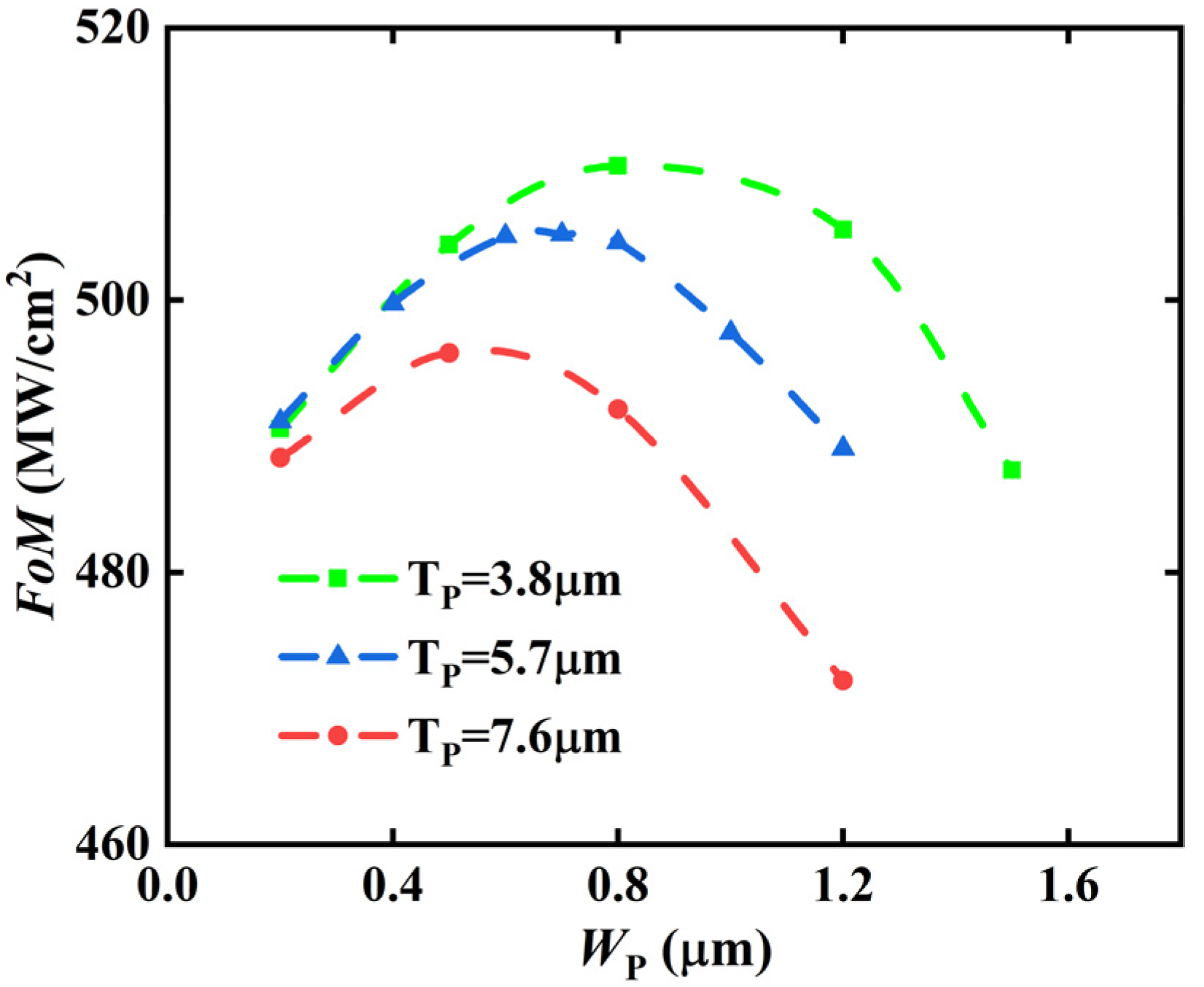

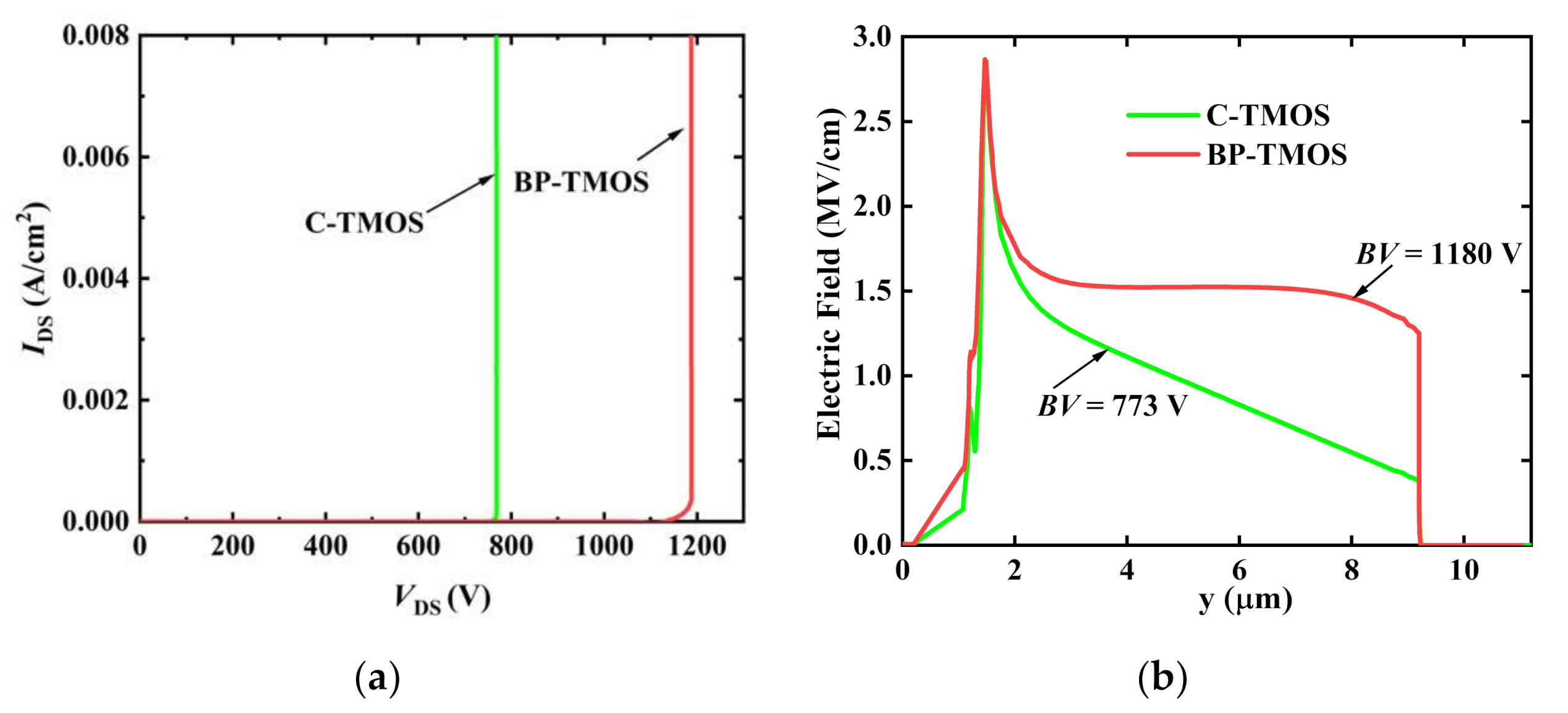

3. Results and Discussions

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Zhang, M.; Wei, J.; Jiang, H.-P. SiC trench MOSFET with self-biased p-shield for low RON-SP and low OFF-state oxide field. IET Power Electron. 2017, 10, 1208–1213. [Google Scholar] [CrossRef]

- Song, Q.-W.; Tang, X.-Y.; Zhang, Y.-M. Investigation of SiC trench MOSFET with floating islands. IET Power Electron. 2016, 9, 2492–2499. [Google Scholar] [CrossRef]

- Jia, H.; Dong, M.; Wang, X.; Zhu, S.; Yang, Y. A Novel 4H-SiC MESFET with a Heavily Doped Region, a Lightly Doped Region and an Insulated Region. Micromachines 2021, 12, 488. [Google Scholar] [CrossRef] [PubMed]

- Jiang, H.-P.; Wei, J.; Dai, X.-P.; Zheng, C.-W. SiC MOSFET with built-in SBD for reduction of reverse recovery charge and switching loss in 10-kV applications. In Proceedings of the 29th International Symposium on Power Semiconductor Devices and IC’s, Sapporo, Japan, 28 May–1 June 2017. [Google Scholar] [CrossRef]

- Conrad, M.; DeDoncker, R.W. Avoiding reverse recovery effects in super junction MOSFET based half-bridge. In Proceedings of the 6th International Symposium on Power Electronics for Distributed Generation Systems, Aachen, Germany, 22–25 June 2015. [Google Scholar] [CrossRef]

- Yamashita, N.; Murakami, N.; Yachi, T. Conduction power loss in MOSFET synchronous rectifier with parallel-connected Schottky barrier diode. IEEE Trans. Power Electron. 1998, 13, 667–673. [Google Scholar] [CrossRef]

- Kim, K.; Kim, J. 4H-SiC Double-Trench MOSFET with Side Wall Heterojunction Diode for Enhanced Reverse Recovery Performance. Energies 2018, 13, 4602. [Google Scholar] [CrossRef]

- Hsu, F.-J.; Yen, C.-T.; Hung, C.-C. High efficiency high reliability SiC MOSFET with monolithically integrated Schottky rectifier. In Proceedings of the 29th International Symposium on Power Semiconductor Devices and IC’s, Sapporo, Japan, 28 May–1 June 2017. [Google Scholar] [CrossRef]

- Chen, R.-X.; Hu, H.; Lin, Y.; Chen, X.-B. A Novel Shielded IGBT (SIGBT) With Integrated Diodes. IEEE J. Electron Devices Soc. 2020, 8, 594–599. [Google Scholar] [CrossRef]

- Jiang, H.-P.; Wei, J.; Dai, X.-P.; Zheng, C.-W. Silicon carbide split-gate MOSFET with merged Schottky barrier diode and reduced switching loss. In Proceedings of the 28th International Symposium on Power Semiconductor Devices and ICs, Prague, Czech Republic, 12–16 June 2016. [Google Scholar] [CrossRef]

- Kobayashi, Y.; Ohse, N.; Morimoto, T. Body PiN diode inactivation with low on-resistance achieved by a 1.2 kV-class 4H-SiC SWITCH-MOS. In Proceedings of the International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017. [Google Scholar] [CrossRef]

- Kobayashi, Y.; Ishimori, H.; Kinoshita, A. Evaluation of Schottky barrier height on 4H-SiC m-face for Schottky barrier diode wall integrated trench MOSFET. Jpn. J. Appl. Phys. 2017, 56, 04CR08. [Google Scholar] [CrossRef]

- Ni, W.; Emori, K.; Marui, T. SiC trench MOSFET with an integrated Low Von unipolar heterojunction diode. Mater. Sci. Forum 2014, 778–780, 923–926. [Google Scholar] [CrossRef]

- Kagawa, Y.; Fujiwara, N.; Sugawara, K. 4H-SiC Trench MOSFET with Bottom Oxide Protection. Mater. Sci. Forum 2014, 778–780, 919–922. [Google Scholar] [CrossRef]

- Kobayashi, Y.; Kinoshita, A.; Onishi, Y. Simulation Based Prediction of SiC Trench MOSFET Characteristics. FUJI Electr. Rev. 2016, 62, 12. [Google Scholar]

- Darwish, M.N.; Lentz, J.L.; Pinto, M.R. An improved electron and hole mobility model for general purpose device simulation. IEEE Trans. Electron. Devices 1997, 44, 1529–1538. [Google Scholar] [CrossRef]

| Parameter | C-TMOS | BP-TMOS | Unit |

|---|---|---|---|

| N drift doping, ND | 7.5 × 1015 | optimised | cm−3 |

| N drift thickness, LD | 8 | 7.6 | μm |

| P+ layer doping, NP+ | 1 × 1019 | 1 × 1019 | cm−3 |

| P well doping, Npwell | 3 × 1017 | 3 × 1017 | cm−3 |

| CSL layer thickness, TCSL | 0.4 | 0.8 | μm |

| CSL layer doping, NCSL | 2 × 1016 | 2 × 1016 | cm−3 |

| P well thickness, Tpwell | 0.8 | 0.8 | μm |

| Gate width, Wtrench | 0.7 | 0.7 | 0.7 |

| LP-poly | / | 1 | μm |

| LP | / | 0.4 | μm |

| P-pillar doping, NP | / | optimised | cm−3 |

| P-pillar width, WP | / | optimised | μm |

| P-pillar length, TP | / | optimised | μm |

| Parameter | C-TMOS | BP-TMOS |

|---|---|---|

| Ron,sp (mΩ·cm2) | 1.86 | 1.48 |

| BV (V) | 773 | 1180 |

| Qg (nC/cm2) | 775 | 525 |

| Qgd (nC/cm2) | 165 | 50 |

| FoM (MW/cm2) | 321 | 940 |

| VF (V) | 2.7 | 3.4 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ran, S.; Huang, Z.; Hu, S.; Yang, H. SiC Heterojunction Trench MOSFET with a Buried P-Type Pillar for the Low Gate-Drain Charge and Switching Loss. Micromachines 2022, 13, 248. https://doi.org/10.3390/mi13020248

Ran S, Huang Z, Hu S, Yang H. SiC Heterojunction Trench MOSFET with a Buried P-Type Pillar for the Low Gate-Drain Charge and Switching Loss. Micromachines. 2022; 13(2):248. https://doi.org/10.3390/mi13020248

Chicago/Turabian StyleRan, Shenglong, Zhiyong Huang, Shengdong Hu, and Han Yang. 2022. "SiC Heterojunction Trench MOSFET with a Buried P-Type Pillar for the Low Gate-Drain Charge and Switching Loss" Micromachines 13, no. 2: 248. https://doi.org/10.3390/mi13020248

APA StyleRan, S., Huang, Z., Hu, S., & Yang, H. (2022). SiC Heterojunction Trench MOSFET with a Buried P-Type Pillar for the Low Gate-Drain Charge and Switching Loss. Micromachines, 13(2), 248. https://doi.org/10.3390/mi13020248