A 100 KS/s 8–10-Bit Resolution-Reconfigurable SAR ADC for Biosensor Applications †

Abstract

1. Introduction

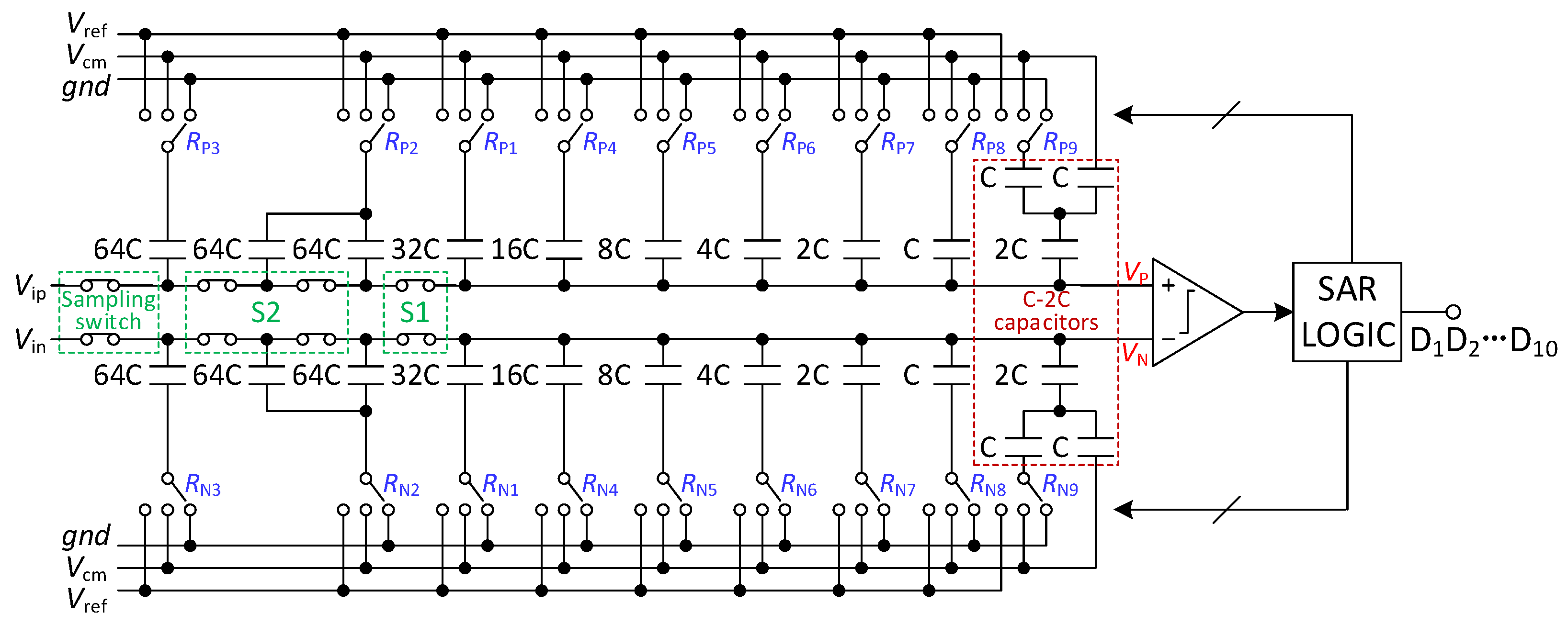

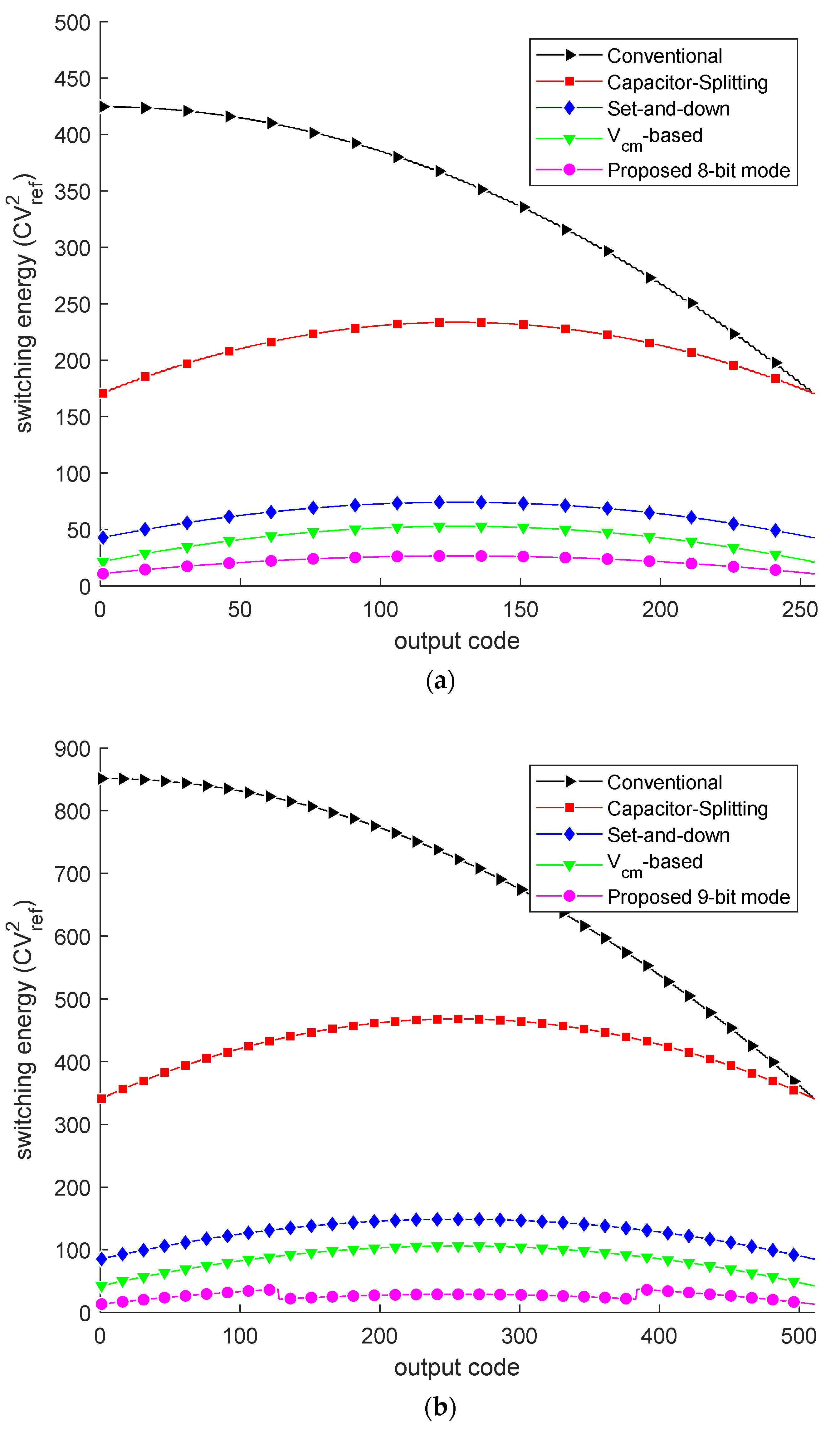

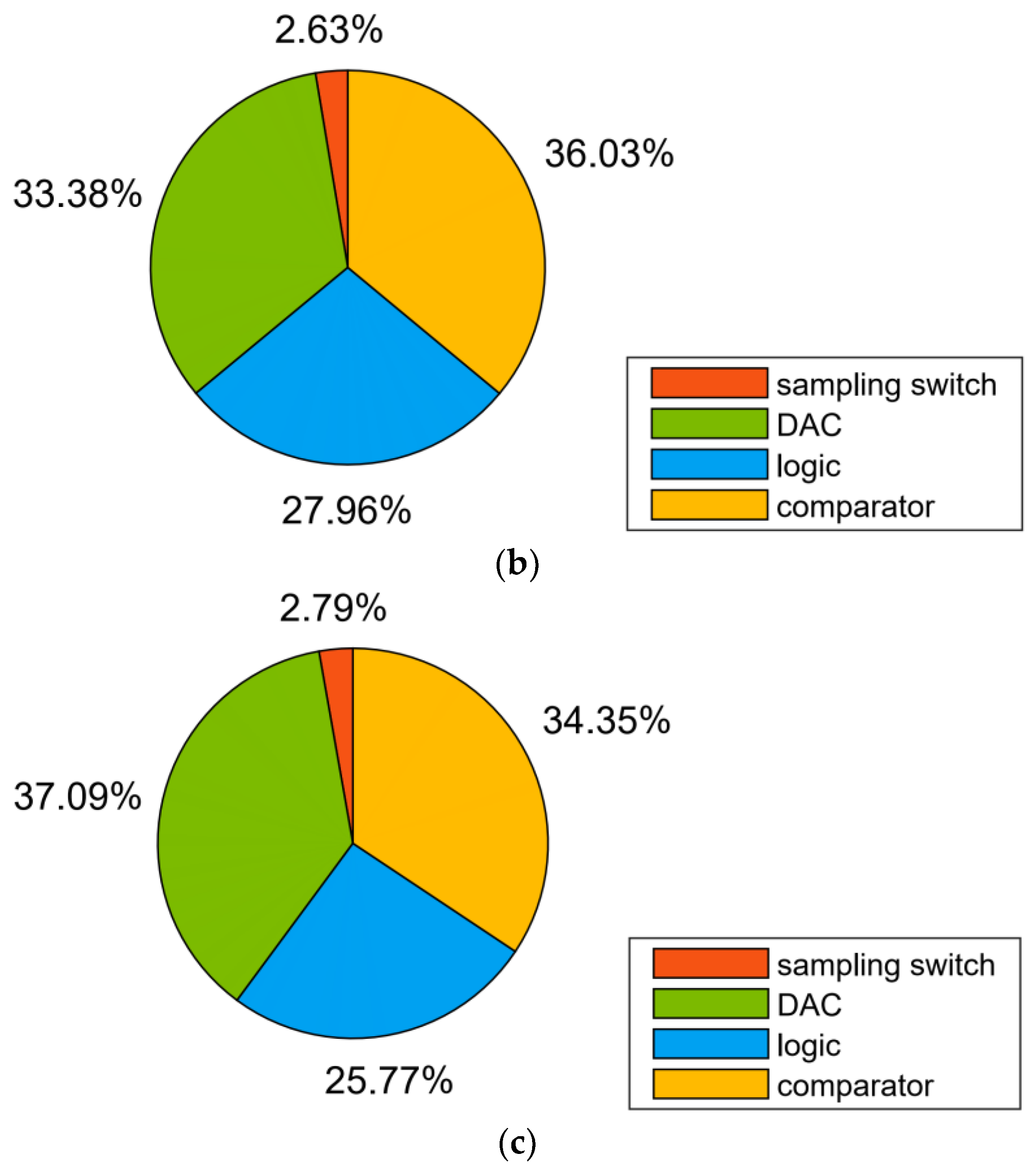

2. Proposed SAR ADC Architecture

2.1. Proposed DAC Switching Scheme

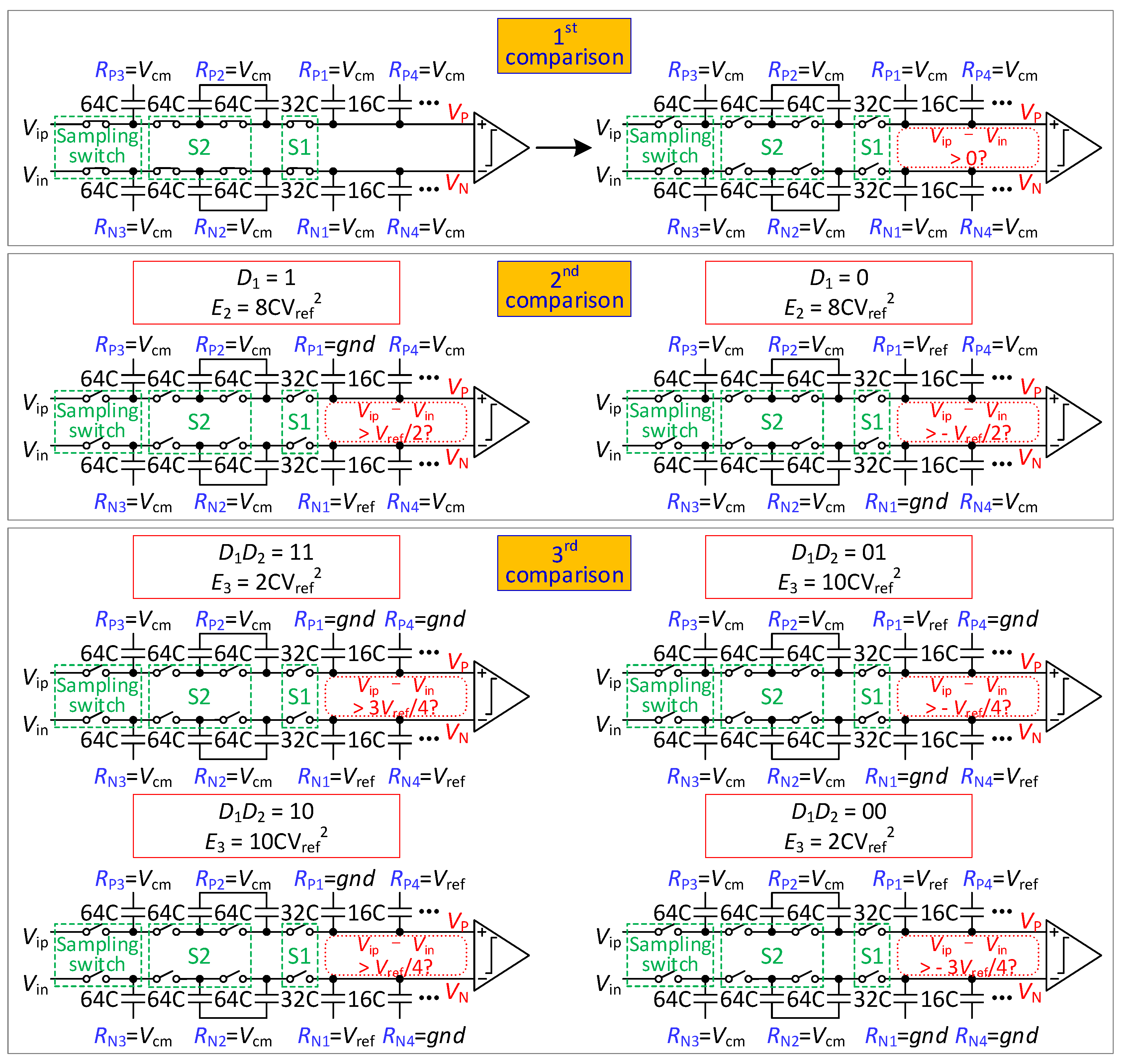

2.1.1. Proposed 8-Bit Mode Switching Scheme

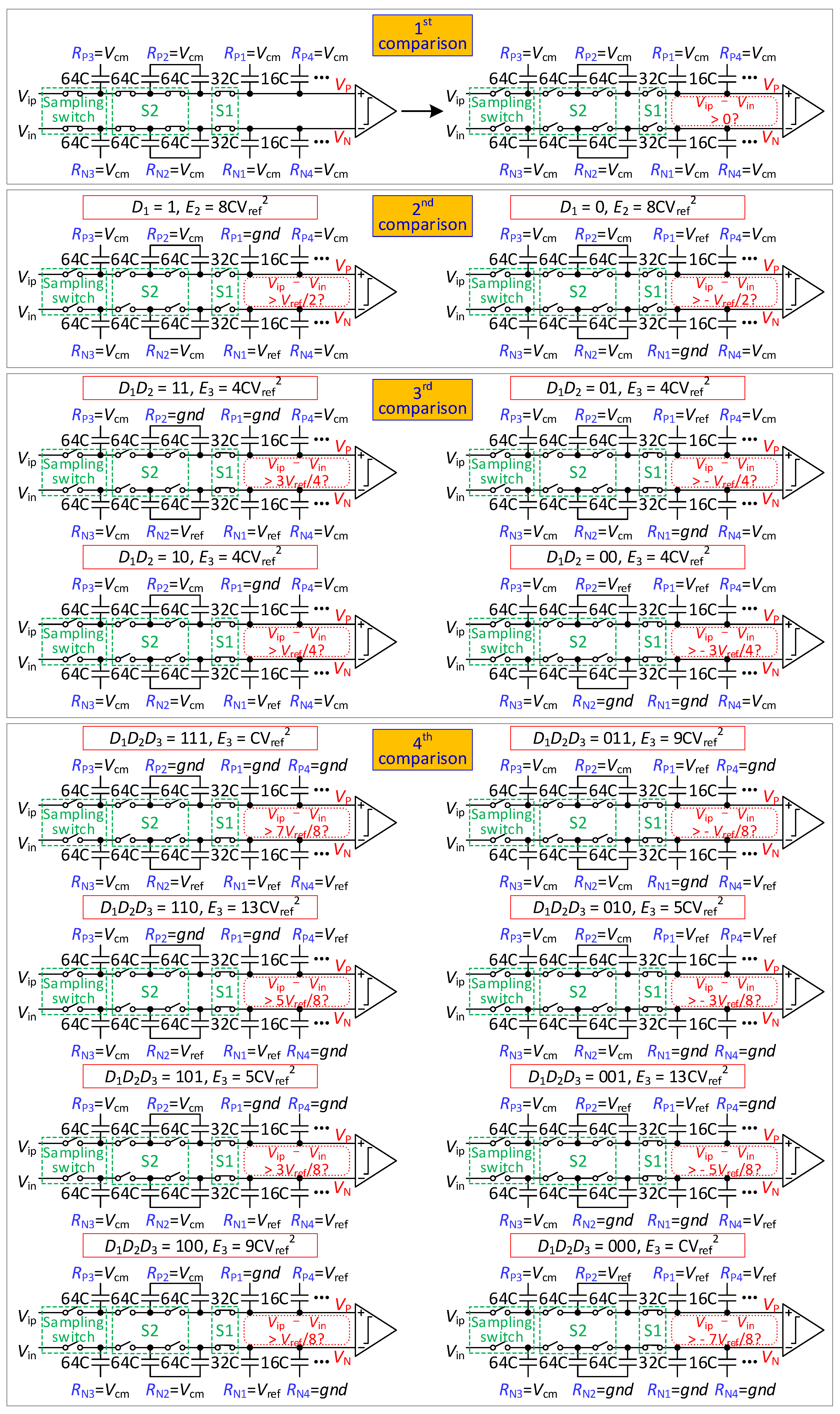

2.1.2. Proposed 9-Bit Mode Switching Scheme

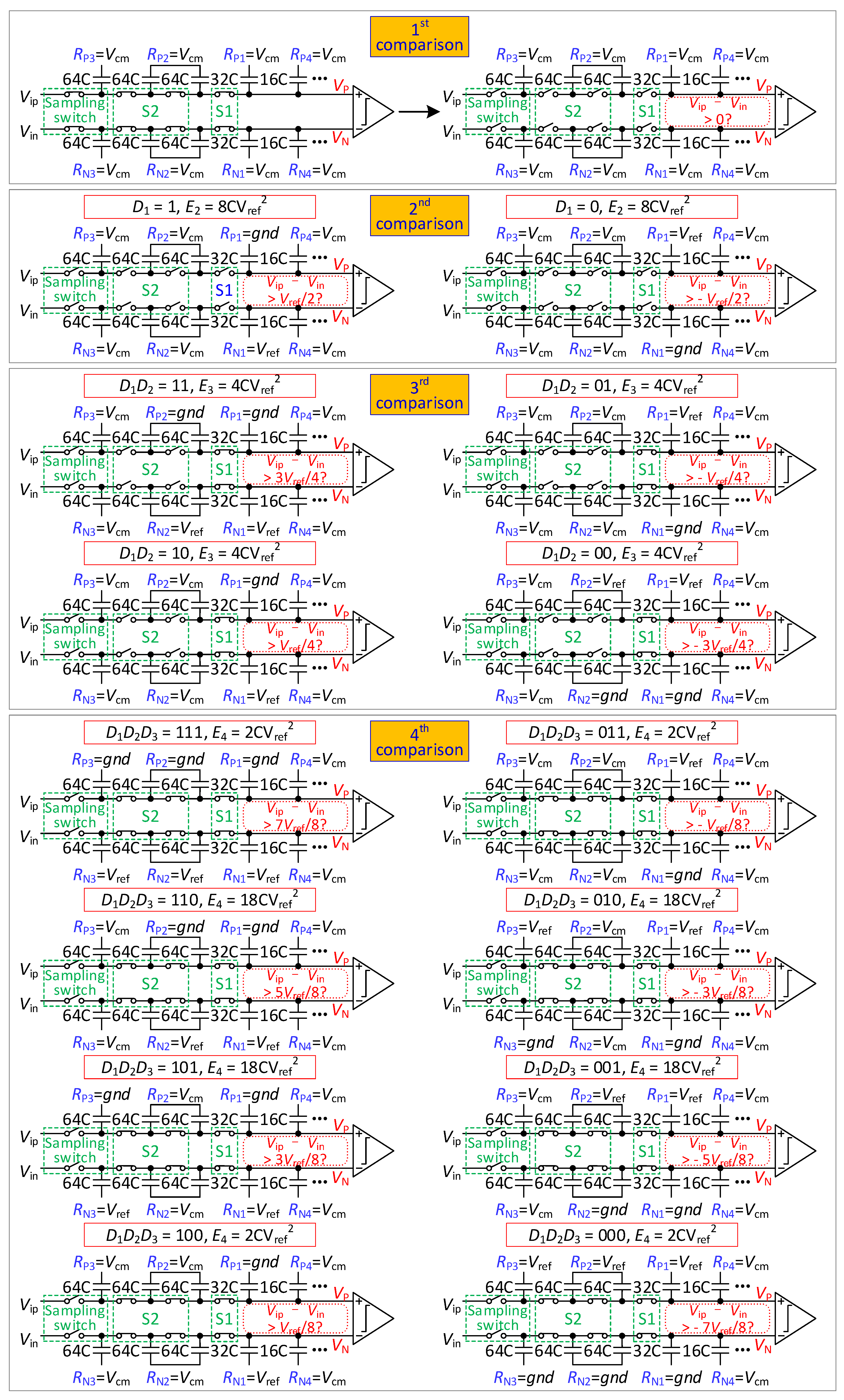

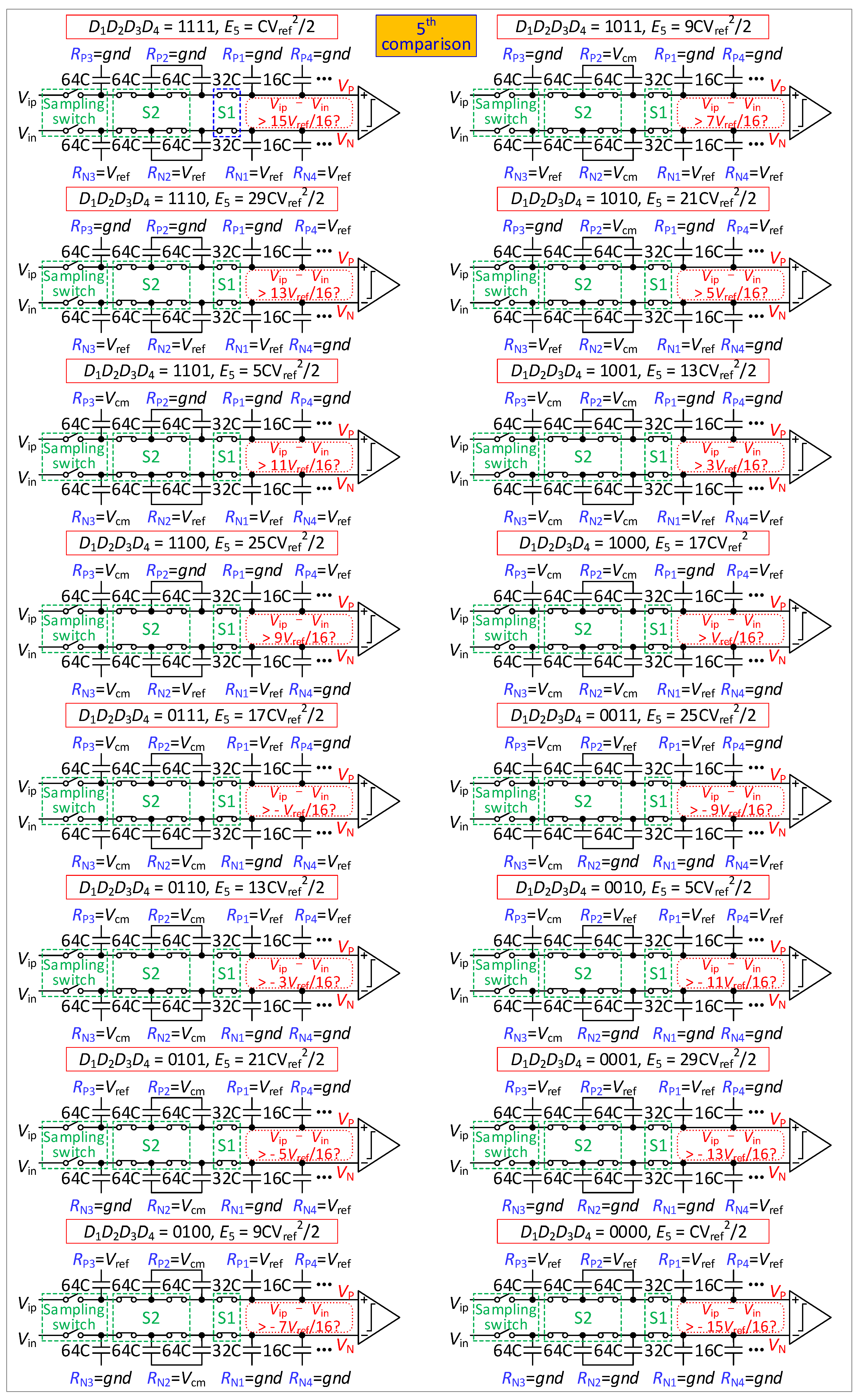

2.1.3. Proposed 10-Bit Mode Switching Scheme

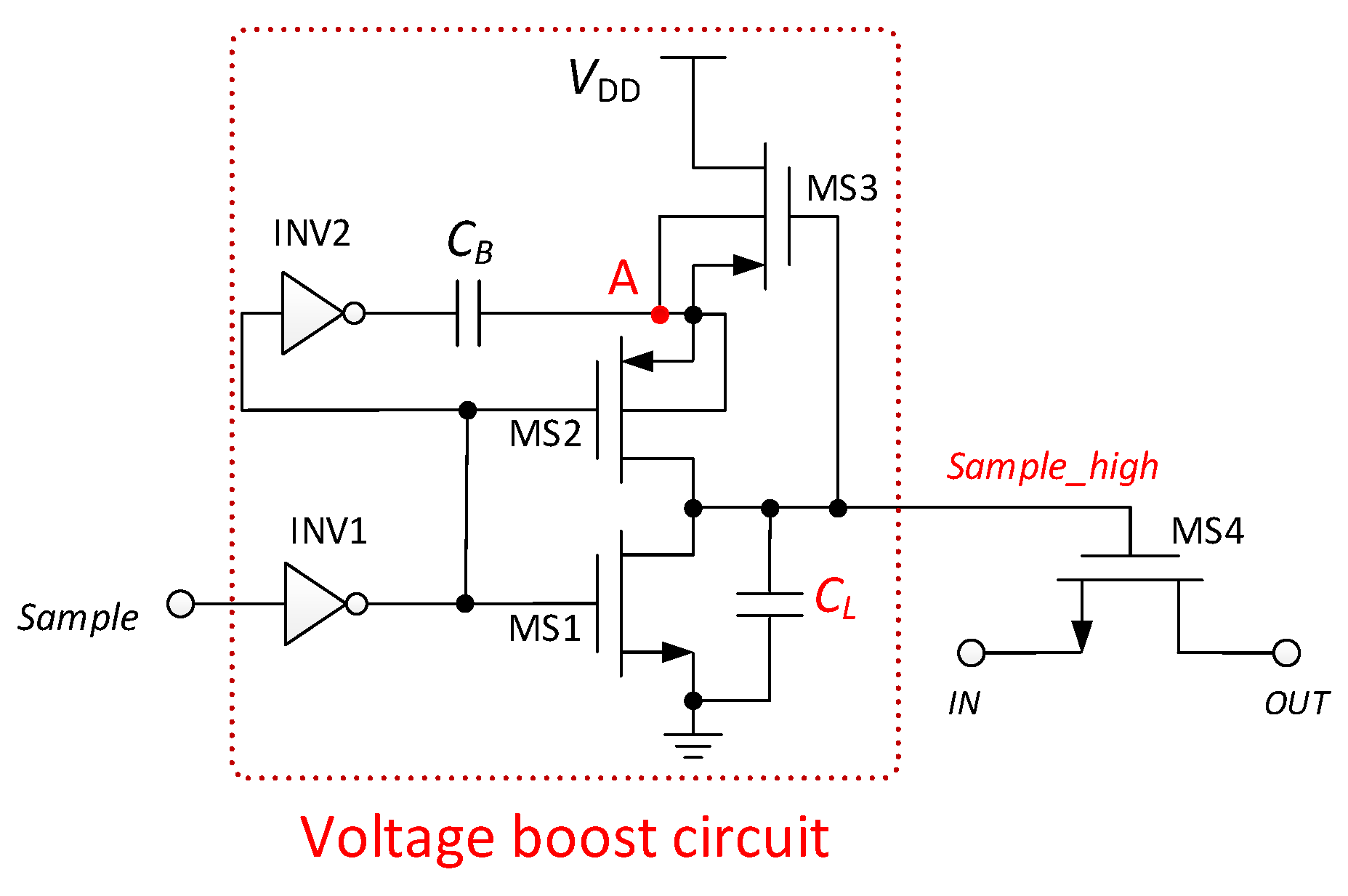

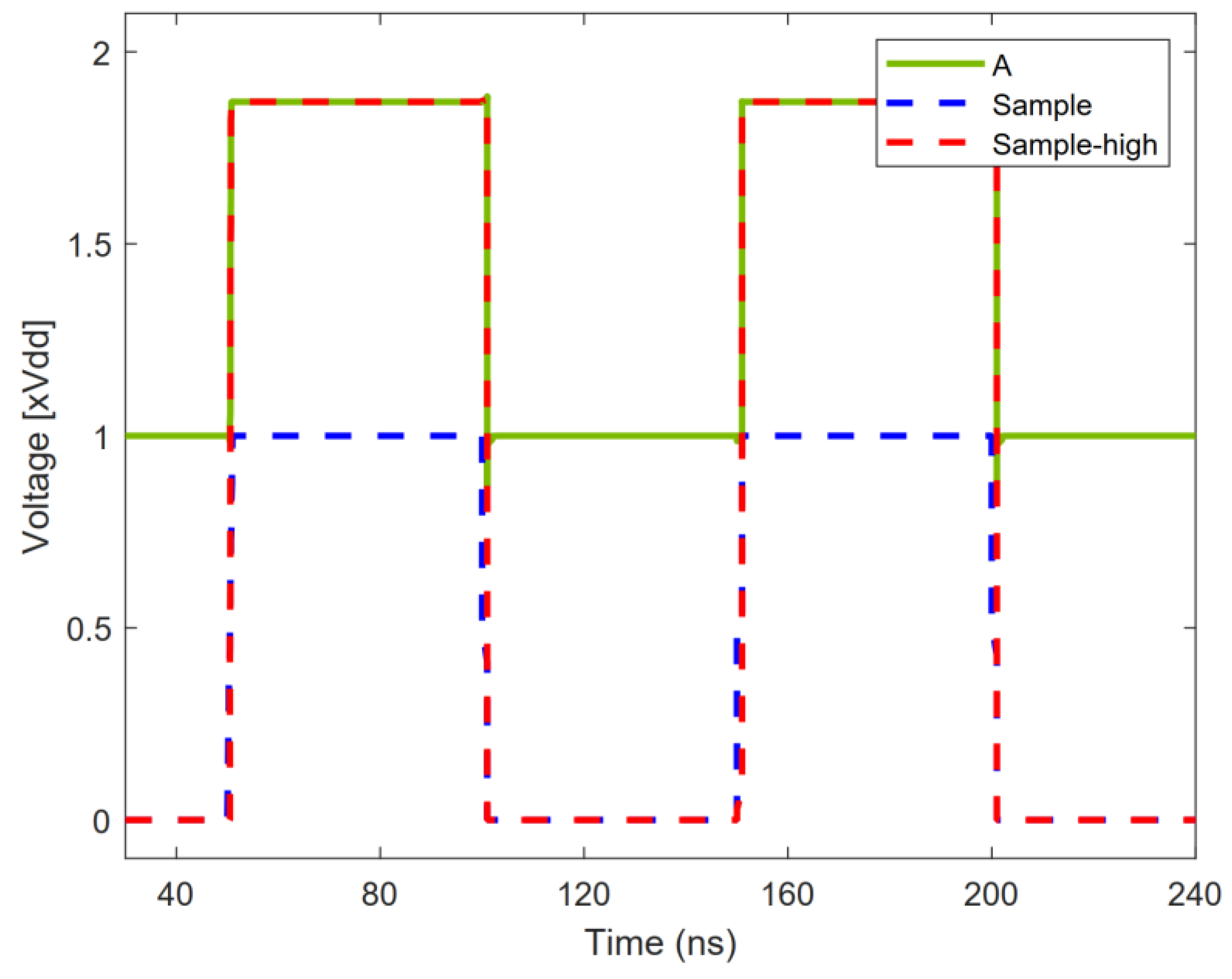

2.2. Sampling Switch

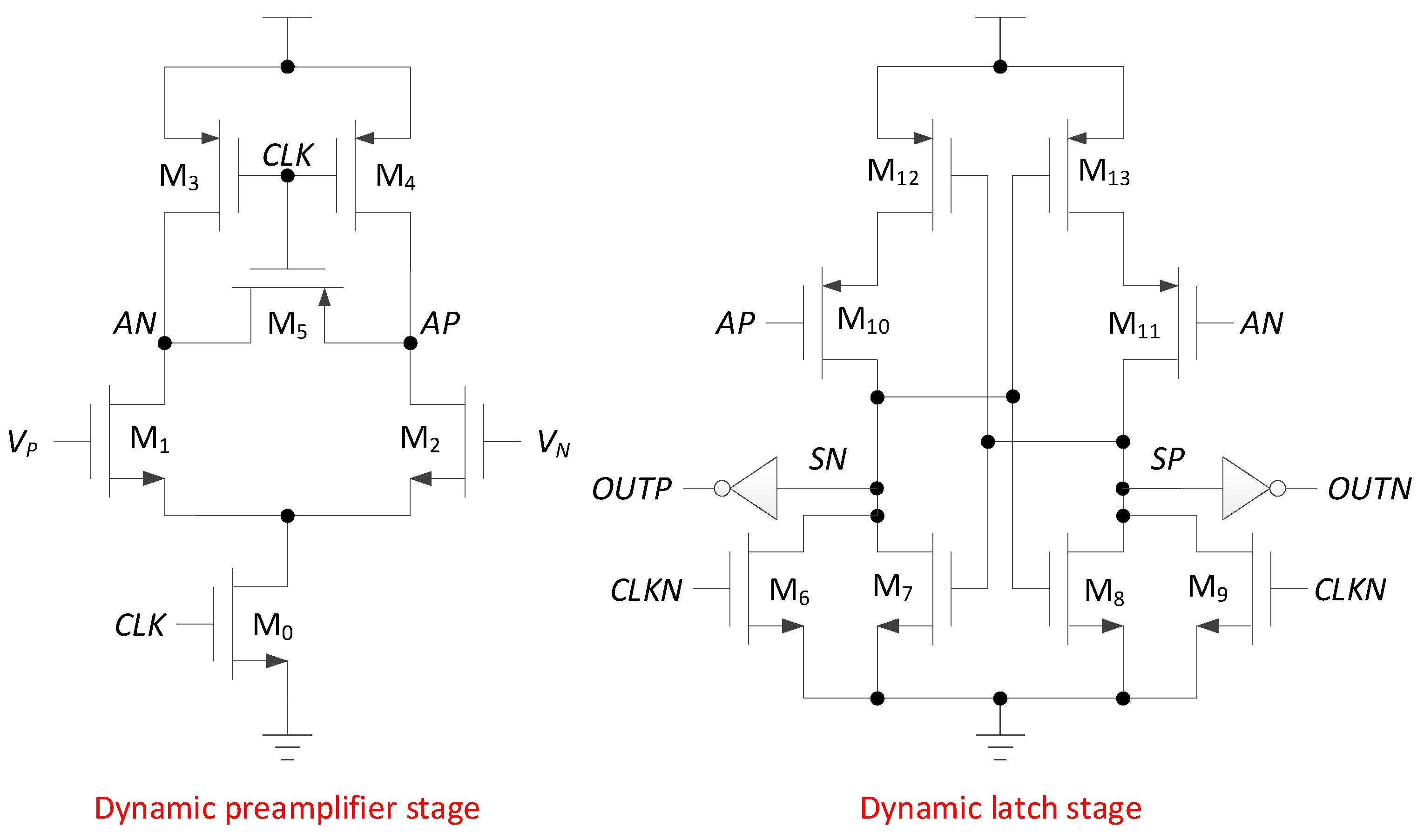

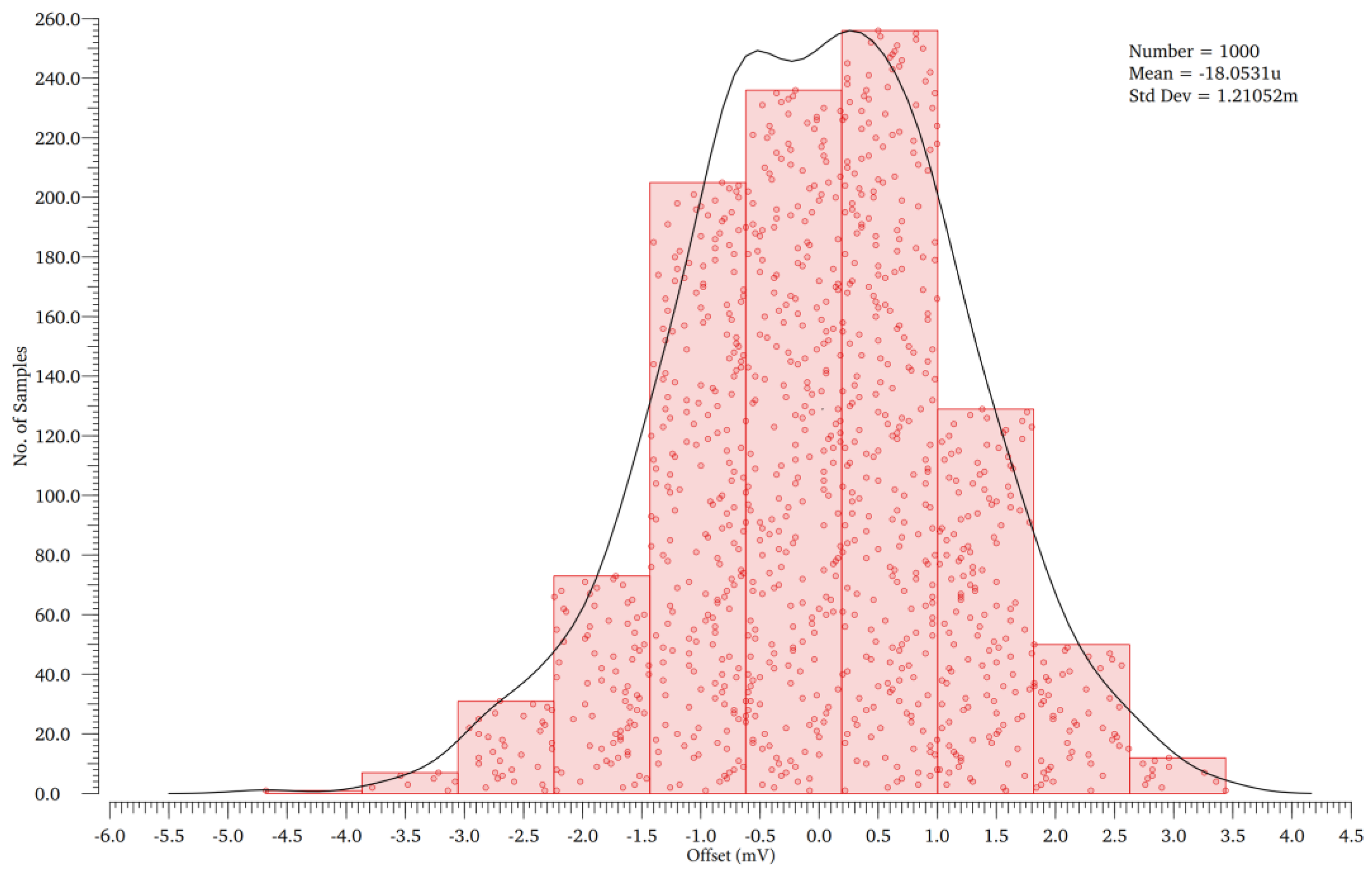

2.3. Comparator

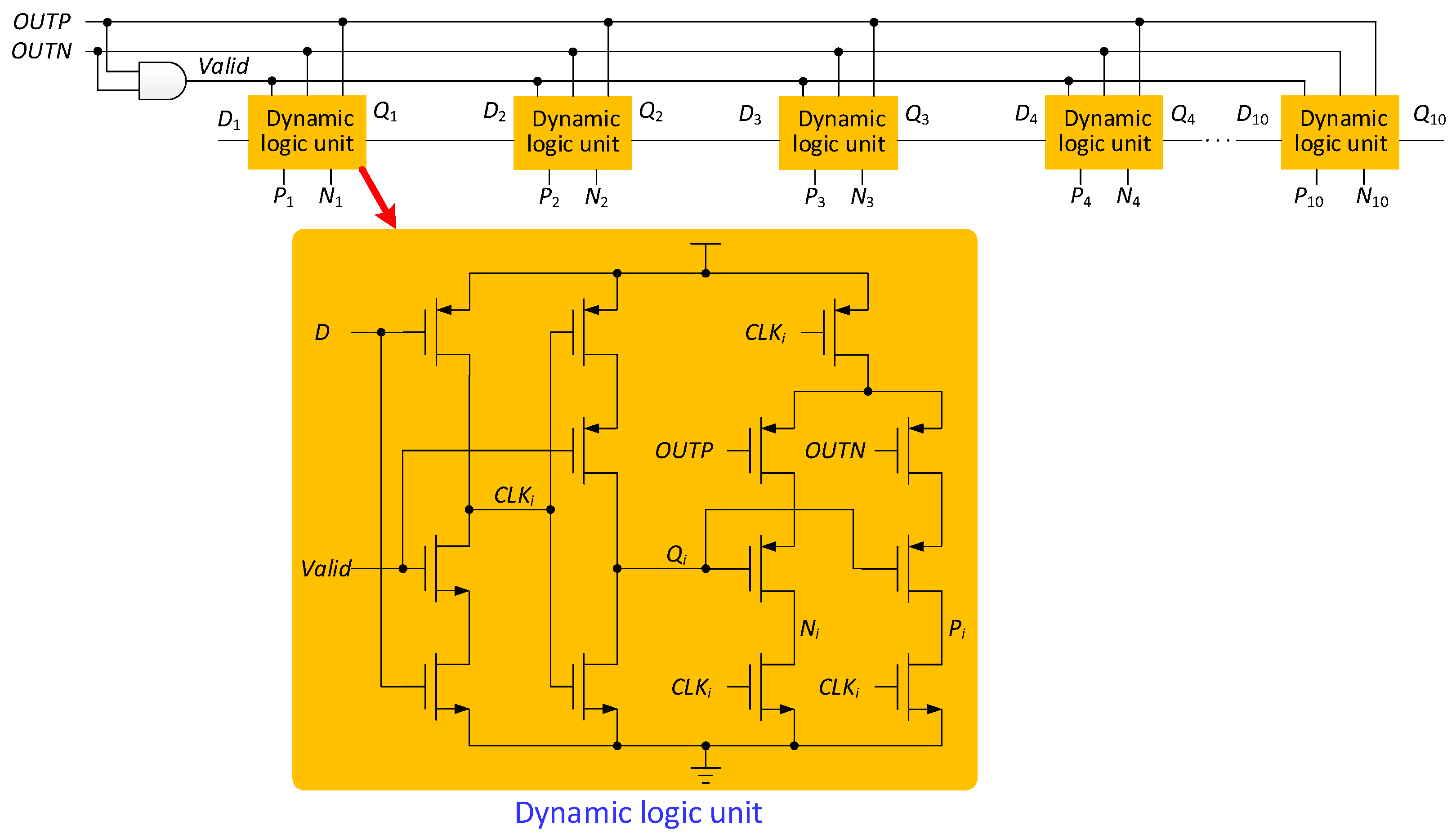

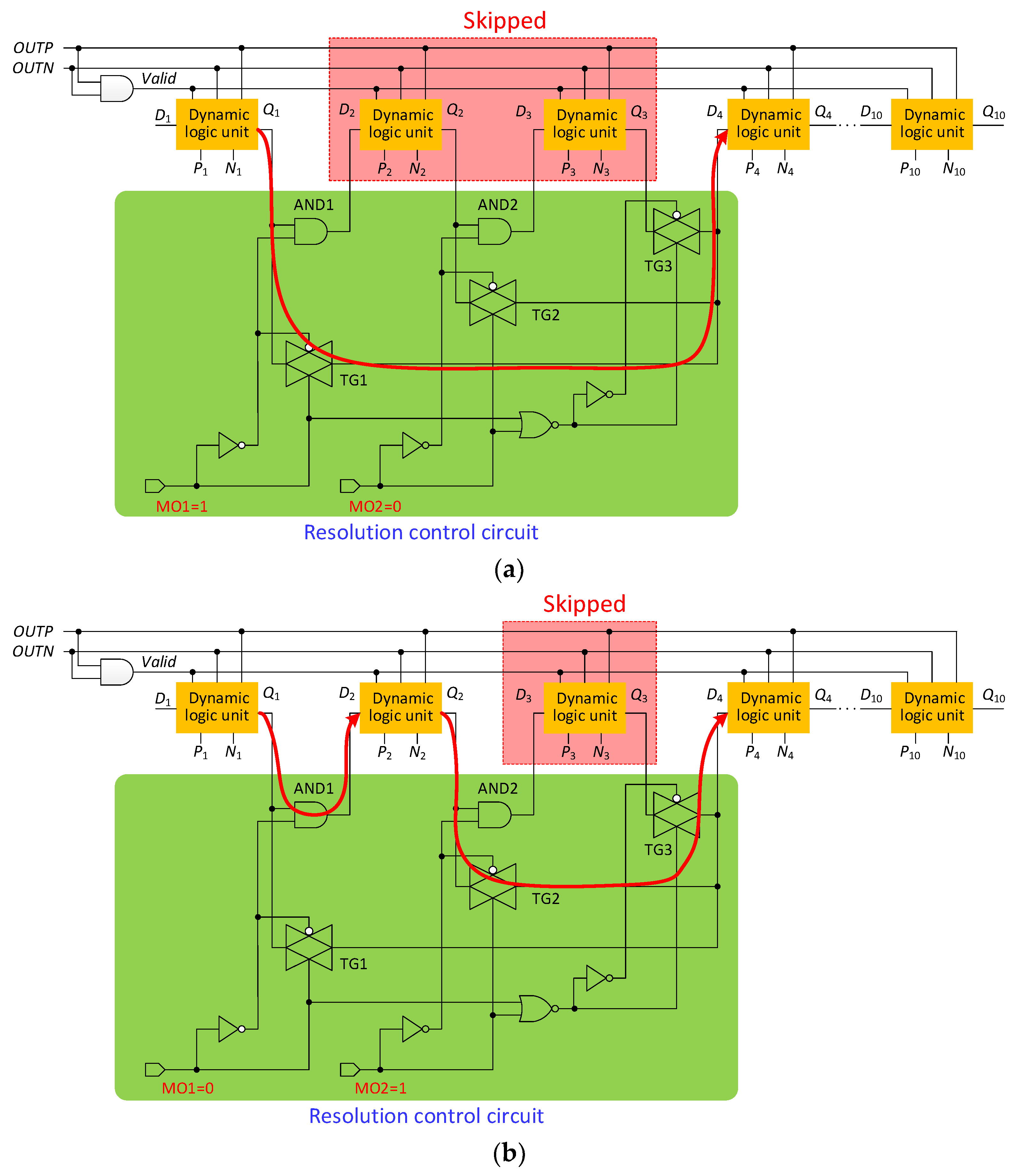

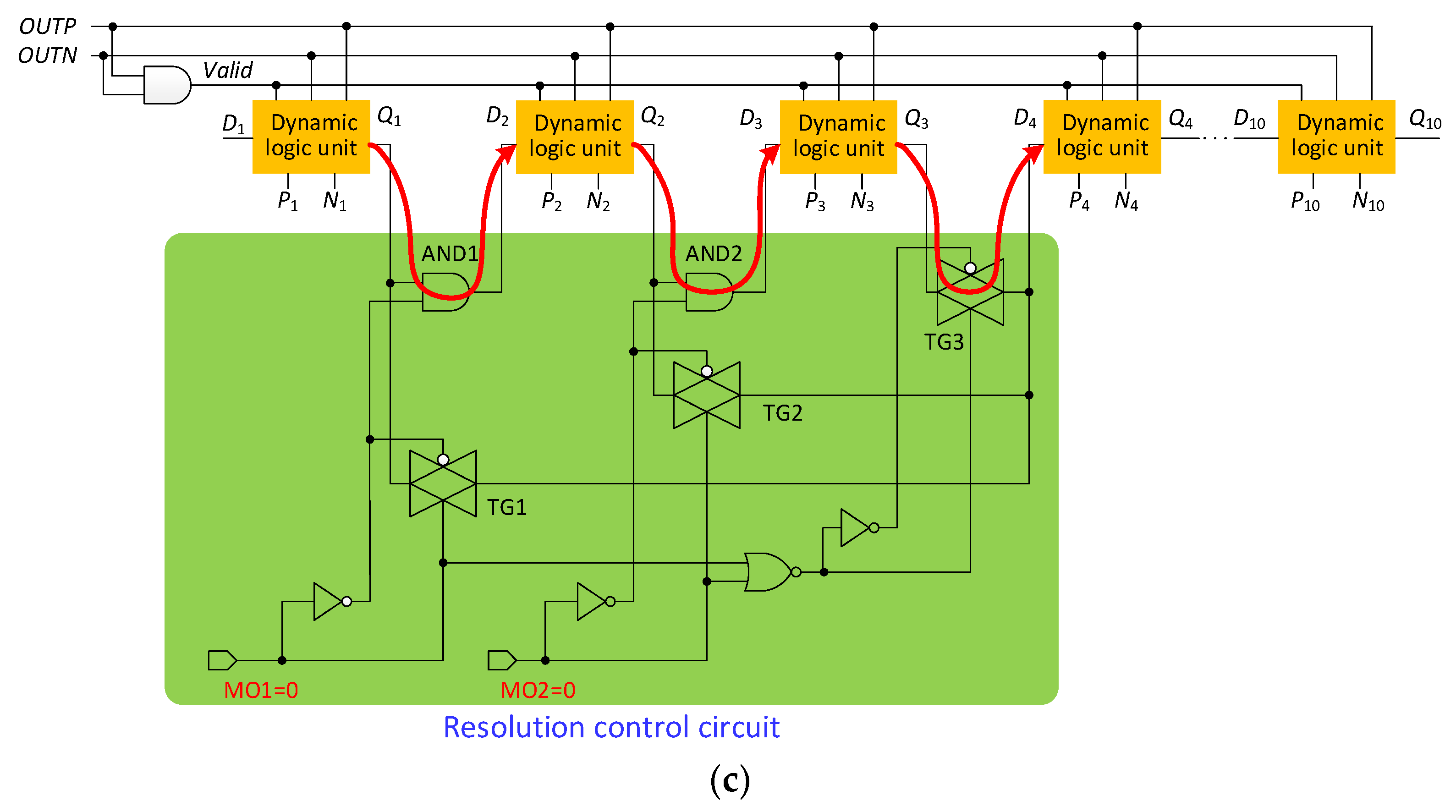

2.4. SAR Control Logic

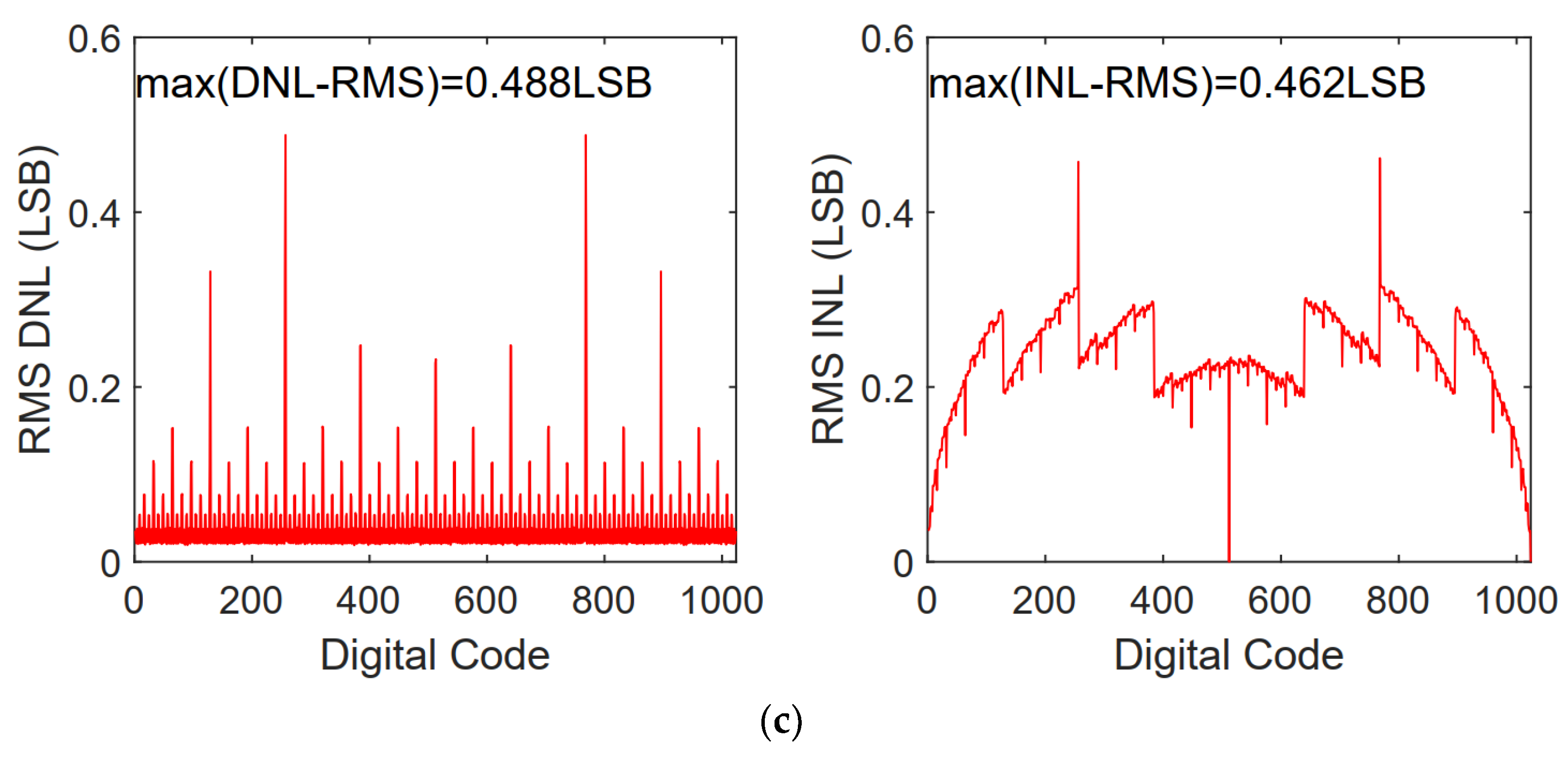

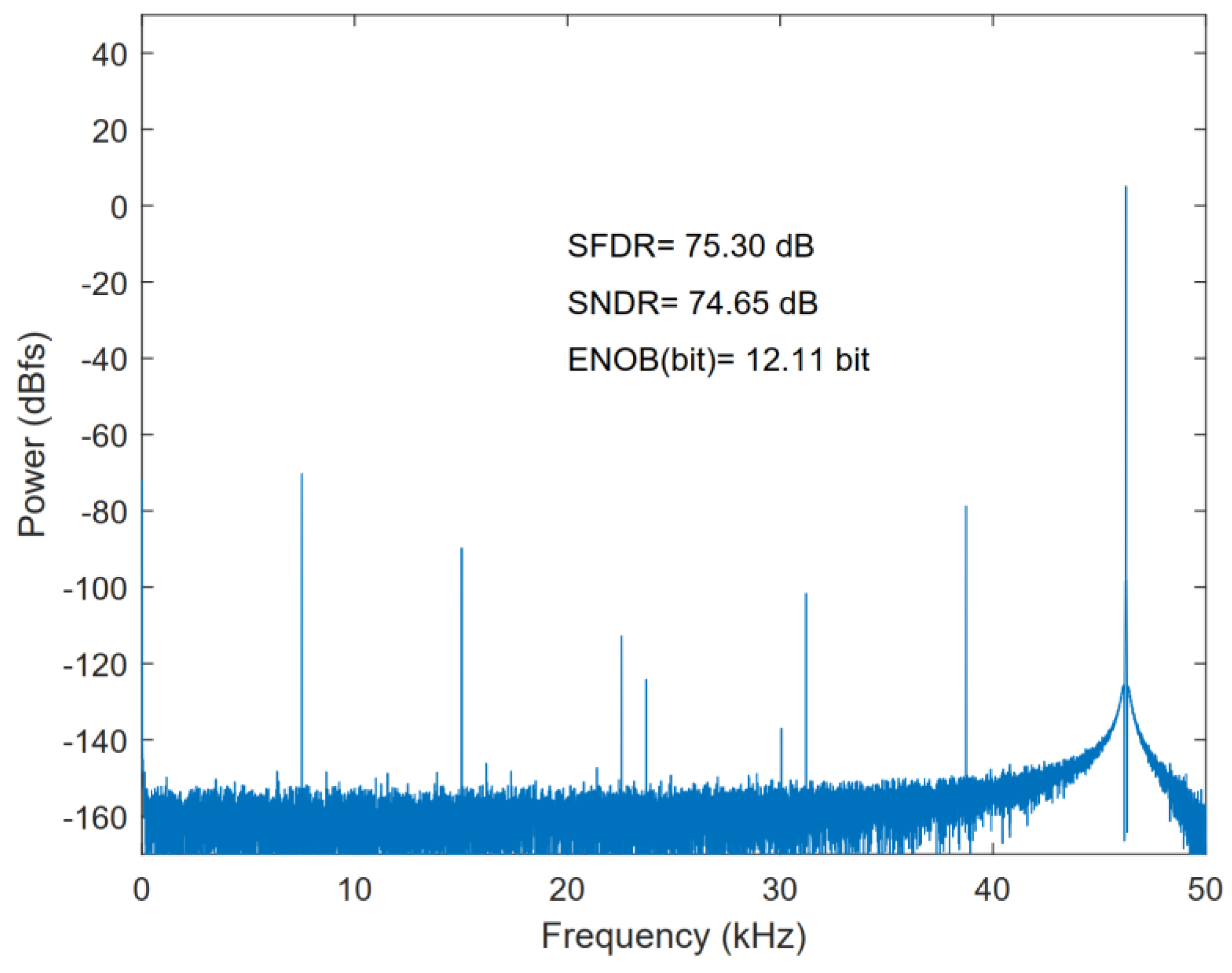

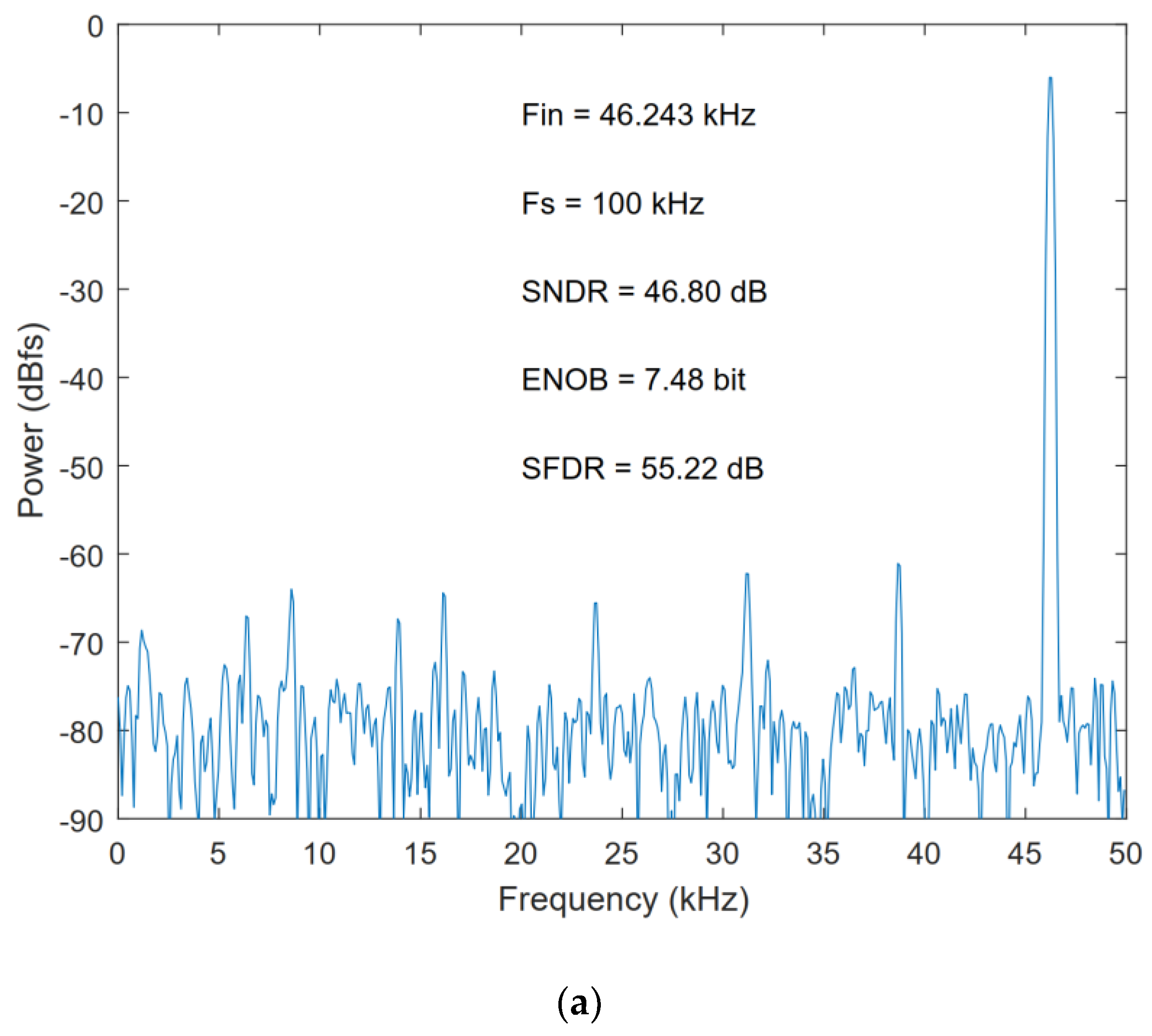

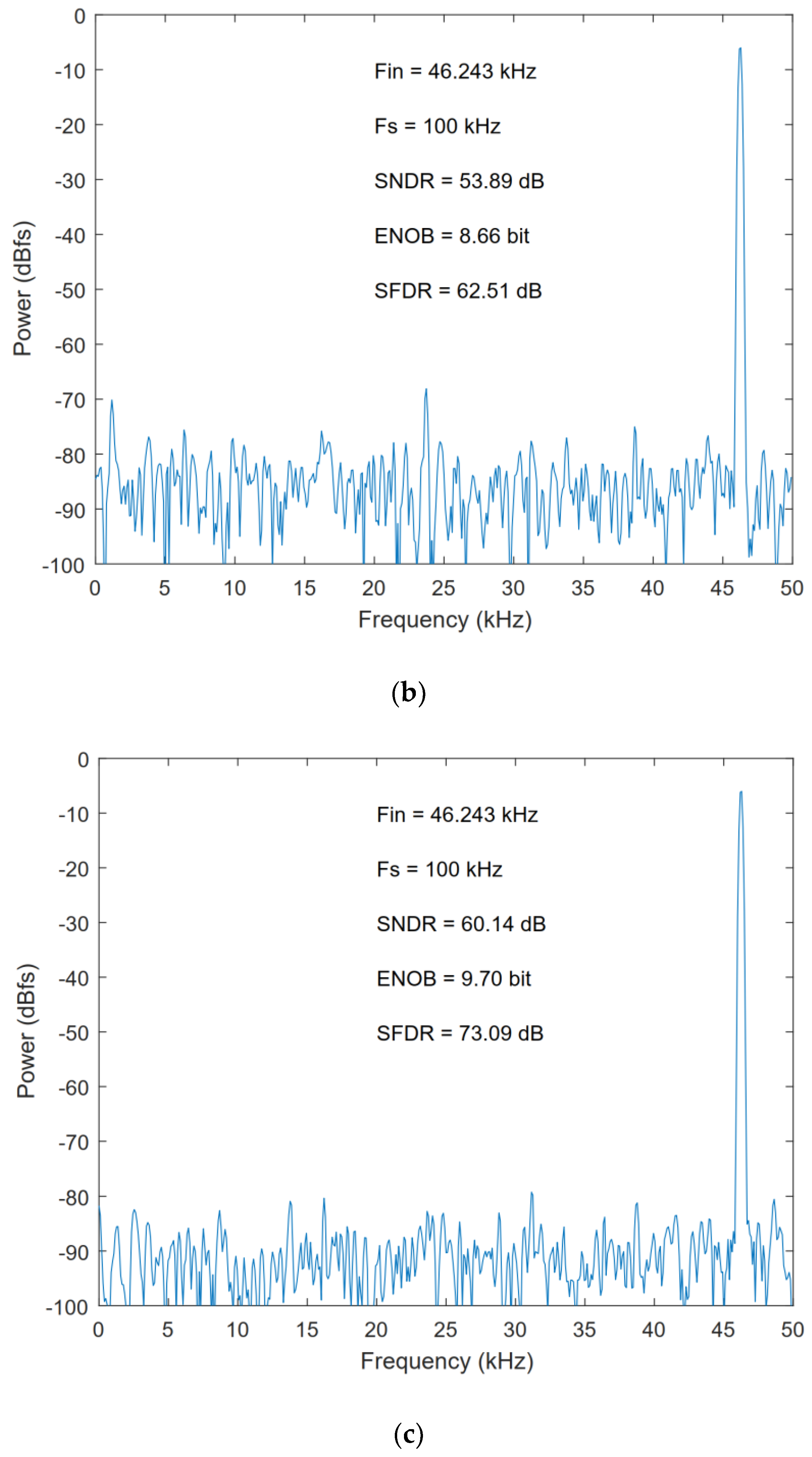

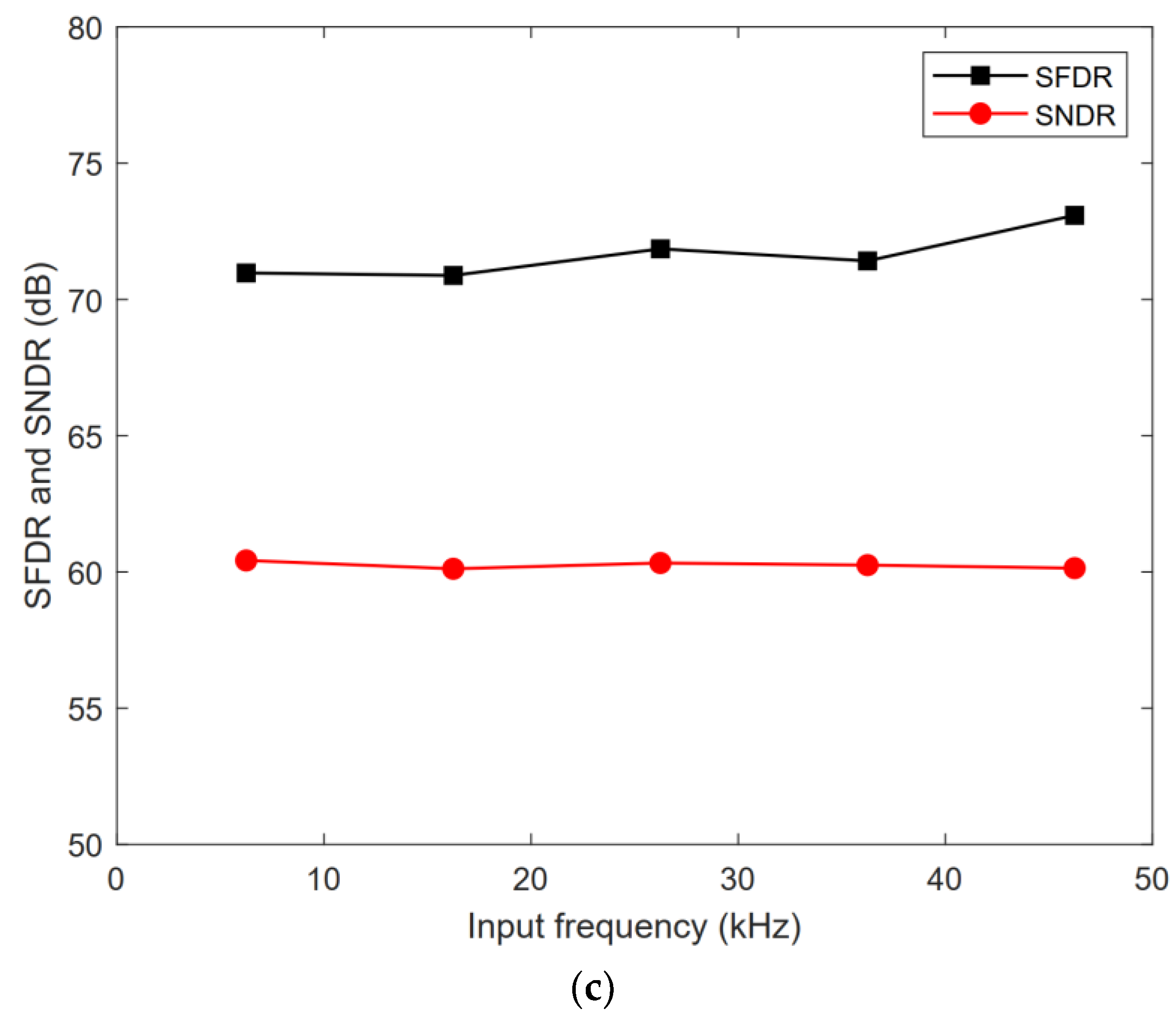

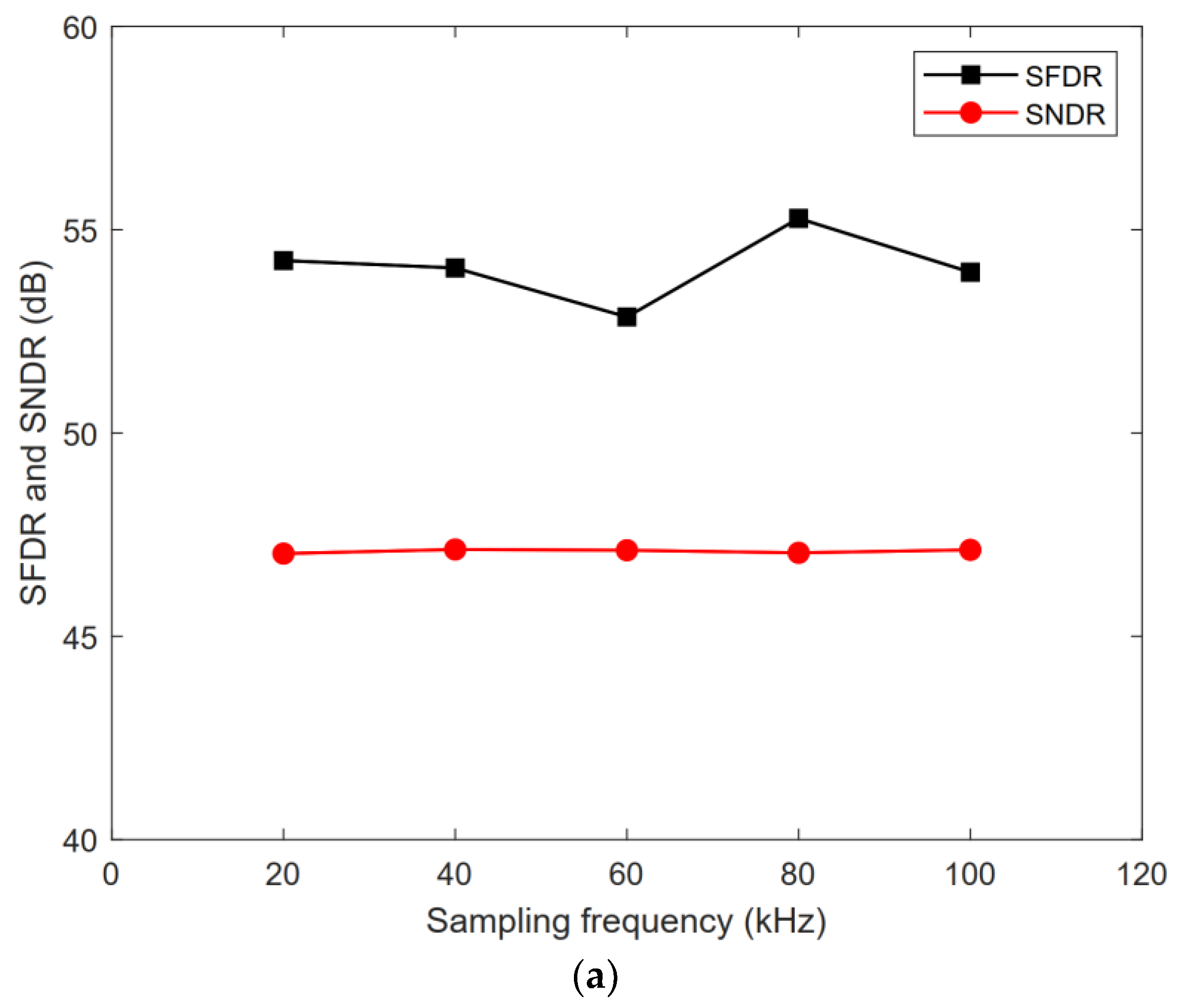

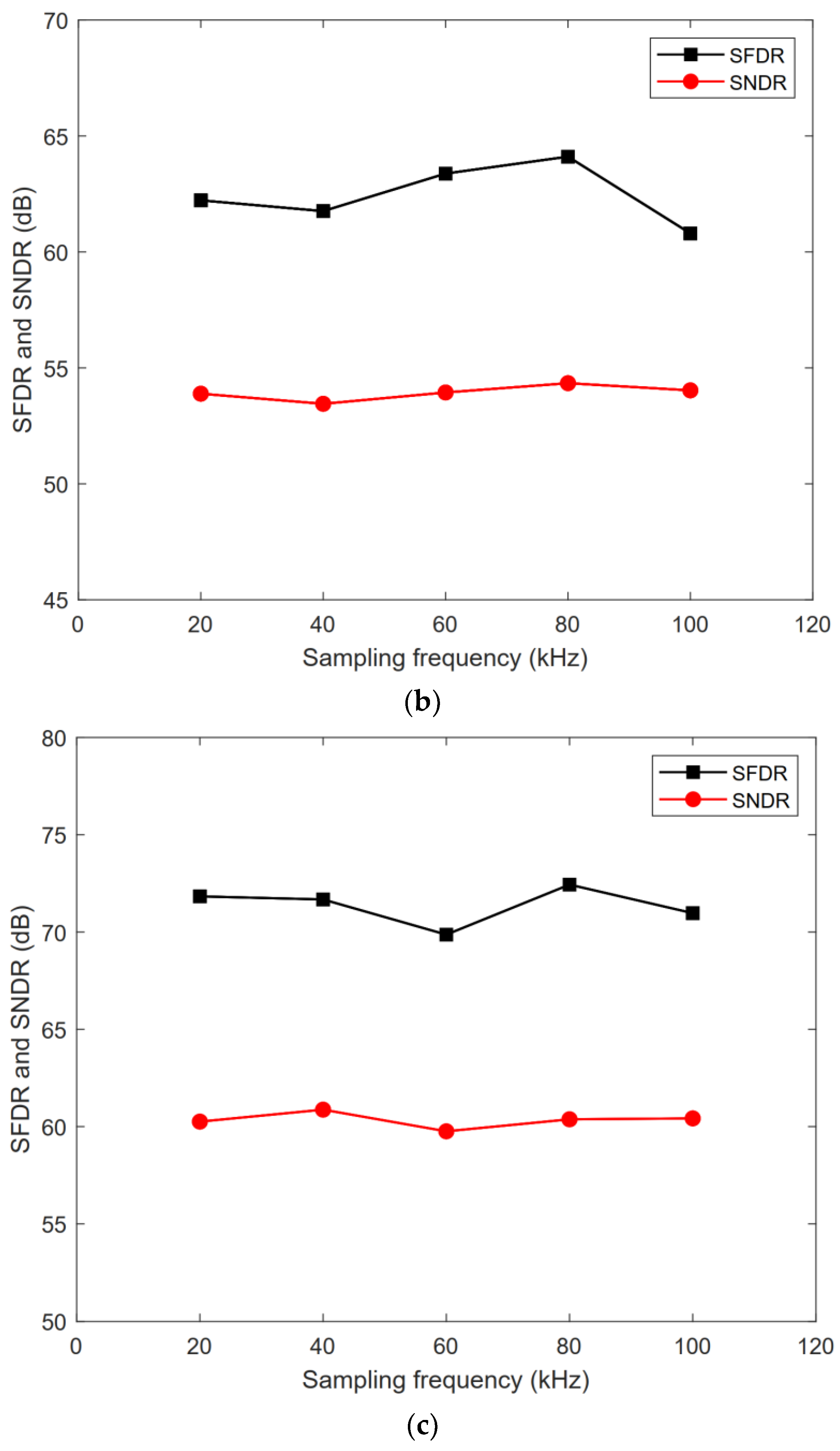

3. Results

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Wang, S.; Hung, C. A 0.3V 10b 3MS/s SAR ADC with Comparator Calibration and Kickback Noise Reduction for Biomedical Applications. IEEE Trans. Biomed. Circuits Syst. 2020, 14, 558–569. [Google Scholar] [CrossRef] [PubMed]

- Tong, X.; Song, M.; Chen, Y.; Dong, S. A 10-Bit 120 kS/s SAR ADC without Reset Energy for Biomedical Electronics. Circuits Syst. Signal Process. 2019, 38, 5411–5425. [Google Scholar] [CrossRef]

- Mao, W.; Li, Y.; Heng, C.; Lian, Y. A Low Power 12-bit 1-kS/s SAR ADC for Biomedical Signal Processing. IEEE Trans. Circuits Syst. I Regul. Pap. 2019, 66, 477–488. [Google Scholar] [CrossRef]

- Sadollahi, M.; Hamashita, K.; Sobue, K.; Temes, G.C. An 11-Bit 250-nW 10-kS/s SAR ADC with Doubled Input Range for Biomedical Applications. IEEE Trans. Circuits Syst. I Regul. Pap. 2018, 65, 61–73. [Google Scholar] [CrossRef]

- Chen, Y.; Zhuang, Y.; Tang, H. A highly energy-efficient, area-efficient switching scheme for SAR ADC in biomedical applications. Analog Integr. Circuits Signal Process. 2019, 101, 133–143. [Google Scholar] [CrossRef]

- Zhu, Z.; Qiu, Z.; Liu, M.; Ding, R. A 6-to-10-Bit 0.5 V-to-0.9 V Reconfigurable 2 MS/s Power Scalable SAR ADC in 0.18 µm CMOS. IEEE Trans. Circuits Syst. I Regul. Pap. 2015, 62, 689–696. [Google Scholar] [CrossRef]

- Yip, M.; Chandrakasan, A.P. A Resolution-Reconfigurable 5-to-10-Bit 0.4-to-1 V Power Scalable SAR ADC for Sensor Applications. IEEE J. Solid-State Circuits 2013, 48, 1453–1464. [Google Scholar] [CrossRef]

- O’Driscoll, S.; Shenoy, K.V.; Meng, T.H. Adaptive Resolution ADC Array for an Implantable Neural Sensor. IEEE Trans. Biomed. Circuits Syst. 2011, 5, 120–130. [Google Scholar] [CrossRef] [PubMed][Green Version]

- Ginsburg, B.P.; Chandrakasan, A.P. An energy-efficient charge recycling approach for a SAR converter with capacitive DAC. In Proceedings of the 2005 IEEE International Symposium on Circuits and Systems, Kobe, Japan, 23–26 May 2005; pp. 184–187. [Google Scholar]

- Liu, C.C.; Chang, S.J.; Huang, G.Y.; Lin, Y.Z. A 10-bit 50-MS/s SAR ADC with a Monotonic Capacitor Switching Procedure. IEEE J. Solid-State Circuits 2010, 45, 731–740. [Google Scholar] [CrossRef]

- Yan, Z.; Chi-Hang, C.; Chio, U.F.; Sai-Weng, S.; Seng-Pan, U.; Martins, R.P.; Maloberti, F. A 10-bit 100-MS/s Reference-Free SAR ADC in 90 nm CMOS. IEEE J. Solid-State Circuits 2010, 45, 1111–1121. [Google Scholar] [CrossRef]

- Johns, D.; Martin, K. Analog Integrated Circuit Design; John Wiley & Sons, Inc.: New York, NY, USA, 1997. [Google Scholar]

- Rabuske, T.; Fernandes, J. A SAR ADC with a MOSCAP-DAC. IEEE J. Solid-State Circuits 2016, 51, 1410–1422. [Google Scholar] [CrossRef]

- Harpe, P.; Cantatore, E.; van Roermund, A. A 10b/12b 40 kS/s SAR ADC with Data-Driven Noise Reduction Achieving up to 10.1b ENOB at 2.2 fJ/Conversion-Step. IEEE J. Solid-State Circuits 2013, 48, 3011–3018. [Google Scholar] [CrossRef]

- Zhu, Z.; Xiao, Y.; Wang, W.; Wang, Q.; Yang, Y. A 0.6 V 100 KS/s 8-10 b resolution configurable SAR ADC in 0.18 mu m CMOS. Analog Integr. Circuits Signal Process. 2013, 75, 335–342. [Google Scholar] [CrossRef]

- Tang, H.; Sun, Z.C.; Chew, K.W.R.; Siek, L. A 1.33 µW 8.02-ENOB 100 kS/s Successive Approximation ADC with Supply Reduction Technique for Implantable Retinal Prosthesis. IEEE Trans. Biomed. Circuits Syst. 2014, 8, 844–856. [Google Scholar] [CrossRef] [PubMed]

- Yuan, C.; Ng, K.A.; Xu, Y.P.; Yen, S.C.; Thakor, N.V. A 1-V 9.8-ENOB 100-kS/s single-ended SAR ADC with symmetrical DAC switching technique for neural signal acquisition. In Proceedings of the 2015 IEEE Asian Solid-State Circuits Conference (A-SSCC), Xiamen, China, 9–11 November 2015. [Google Scholar] [CrossRef]

- Wang, J.; Hua, Y.; Zhu, Z. A 10-bit reconfigurable ADC with SAR/SS mode for neural recording. Analog Integr. Circuits Signal Process. 2019, 101, 297–305. [Google Scholar] [CrossRef]

- Ro, D.; Min, C.; Kang, M.; Chang, I.J.; Lee, H.-M. A Radiation-Hardened SAR ADC with Delay-Based Dual Feedback Flip-Flops for Sensor Readout Systems. Sensors 2019, 20, 171. [Google Scholar] [CrossRef]

| Biomedical Signals | Frequency Range |

|---|---|

| Electroencephalogram (EEG) | 1–150 Hz |

| Electromyogram (EMG) | 25–1 kHz |

| Electrocardiogram (ECG) | 0.5–250 Hz |

| Local Field Potential (LFP) | 0.5–200 Hz |

| Action Potential (AP) | 100–7 kHz |

| Resolution | Phase | ||||

|---|---|---|---|---|---|

| Sampling | Comparison | ||||

| 1st | 2nd | 3rd | 4th | ||

| 8-bit mode | S1:close | S1:open | S1:open | S1:open | S1:open |

| S2:close | S2:open | S2:open | S2:open | S2:open | |

| 9-bit mode | S1:close | S1:open | S1:open | S1:close | S1:close |

| S2:close | S2:open | S2:open | S2:open | S2:open | |

| 10-bit mode | S1:close | S1:open | S1:open | S1:close | S1:close |

| S2:close | S2:open | S2:open | S2:open | S2:close | |

| D1D2 | Phase | |||

|---|---|---|---|---|

| Sampling | Comparison | |||

| 1st | 2nd | 3rd | ||

| 00 | RP2 = Vcm | RP2 = Vcm | RP2 = Vcm | RP2 = Vref |

| RN2 = Vcm | RN2 = Vcm | RN2 = Vcm | RN2 = gnd | |

| 01 | RP2 = Vcm | RP2 = Vcm | RP2 = Vcm | RP2 = Vcm |

| RN2 = Vcm | RN2 = Vcm | RN2 = Vcm | RN2 = Vcm | |

| 10 | RP2 = Vcm | RP2 = Vcm | RP2 = Vcm | RP2 = Vcm |

| RN2 = Vcm | RN2 = Vcm | RN2 = Vcm | RN2 = Vcm | |

| 11 | RP2 = Vcm | RP2 = Vcm | RP2 = Vcm | RP2 = gnd |

| RN2 = Vcm | RN2 = Vcm | RN2 = Vcm | RN2 = Vref | |

| D1D3 | Phase | ||||

|---|---|---|---|---|---|

| Sampling | Comparison | ||||

| 1st | 2nd | 3rd | 4th | ||

| 00 | RP3 = Vcm | RP3 = Vcm | RP3 = Vcm | RP3 = Vcm | RP3 = Vref |

| RN3 = Vcm | RN3 = Vcm | RN3 = Vcm | RN3 = Vcm | RN3 = gnd | |

| 01 | RP3 = Vcm | RP3 = Vcm | RP3 = Vcm | RP3 = Vcm | RP3 = Vcm |

| RN3 = Vcm | RN3 = Vcm | RN3 = Vcm | RN3 = Vcm | RN3 = Vcm | |

| 10 | RP3 = Vcm | RP3 = Vcm | RP3 = Vcm | RP3 = Vcm | RP3 = Vcm |

| RN3 = Vcm | RN3 = Vcm | RN3 = Vcm | RN3 = Vcm | RN3 = Vcm | |

| 11 | RP3 = Vcm | RP3 = Vcm | RP3 = Vcm | RP3 = Vcm | RP3 = gnd |

| RN3 = Vcm | RN3 = Vcm | RN3 = Vcm | RN3 = Vcm | RN3 = Vref | |

| Switching Scheme | Energy Saving | |||||

|---|---|---|---|---|---|---|

| 8-Bit | 9-Bit | 10-Bit | 8-Bit | 9-Bit | 10-Bit | |

| Conventional [12] | 339.3 | 680.7 | 1363.3 | Reference | Reference | Reference |

| Split capacitor [9] | 212.3 | 425.7 | 852.3 | 37.4% | 37.4% | 37.4% |

| Set-and-down [10] | 63.5 | 127.5 | 255.5 | 81.3% | 81.3% | 81.3% |

| Vcm-based [11] | 42.2 | 84.8 | 170.2 | 87.5% | 87.5% | 87.5% |

| Proposed | 21.2 | 26.5 | 37.1 | 93.8% | 96.1% | 97.3% |

| MO1 | MO2 | Bit Mode |

|---|---|---|

| 1 | 0 | 8-bit mode |

| 0 | 1 | 9-bit mode |

| 0 | 0 | 10-bit mode |

| Article Title | [16] | [17] | [18] * | [19] | This Work * | ||

|---|---|---|---|---|---|---|---|

| Technology (nm) | 180 | 180 | 180 | 65 | 180 | 180 | 180 |

| Supply Voltage (V) | 0.9 | 1.0 | 1.8 | 1.2 | 1.8 | 1.8 | 1.8 |

| Resolution (bit) | 9 | 10 | 10 | 10 | 8 | 9 | 10 |

| Sampling Rate (KS/s) | 100 | 100 | 25 | 25 | 100 | 100 | 100 |

| Power (μW) | 1.33 | 1.72 | 2.83 | 0.84 | 0.81 | 0.91 | 1.01 |

| ENOB (bit) | 8.02 | 9.48 | 9.77 | 9.59 | 7.48 | 8.66 | 9.70 |

| FoM (fJ/conv.-step) | 51.3 | 24.1 | 129 | 43.60 | 45.37 | 22.5 | 12.1 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Hu, Y.; Hu, L.; Tang, B.; Li, B.; Wu, Z.; Liu, X. A 100 KS/s 8–10-Bit Resolution-Reconfigurable SAR ADC for Biosensor Applications. Micromachines 2022, 13, 1909. https://doi.org/10.3390/mi13111909

Hu Y, Hu L, Tang B, Li B, Wu Z, Liu X. A 100 KS/s 8–10-Bit Resolution-Reconfigurable SAR ADC for Biosensor Applications. Micromachines. 2022; 13(11):1909. https://doi.org/10.3390/mi13111909

Chicago/Turabian StyleHu, Yunfeng, Lexing Hu, Bin Tang, Bin Li, Zhaohui Wu, and Xiaojia Liu. 2022. "A 100 KS/s 8–10-Bit Resolution-Reconfigurable SAR ADC for Biosensor Applications" Micromachines 13, no. 11: 1909. https://doi.org/10.3390/mi13111909

APA StyleHu, Y., Hu, L., Tang, B., Li, B., Wu, Z., & Liu, X. (2022). A 100 KS/s 8–10-Bit Resolution-Reconfigurable SAR ADC for Biosensor Applications. Micromachines, 13(11), 1909. https://doi.org/10.3390/mi13111909