Investigation of the Temperature Effect on Electrical Characteristics of Al/SiO2/n++-Si RRAM Devices

Abstract

1. Introduction

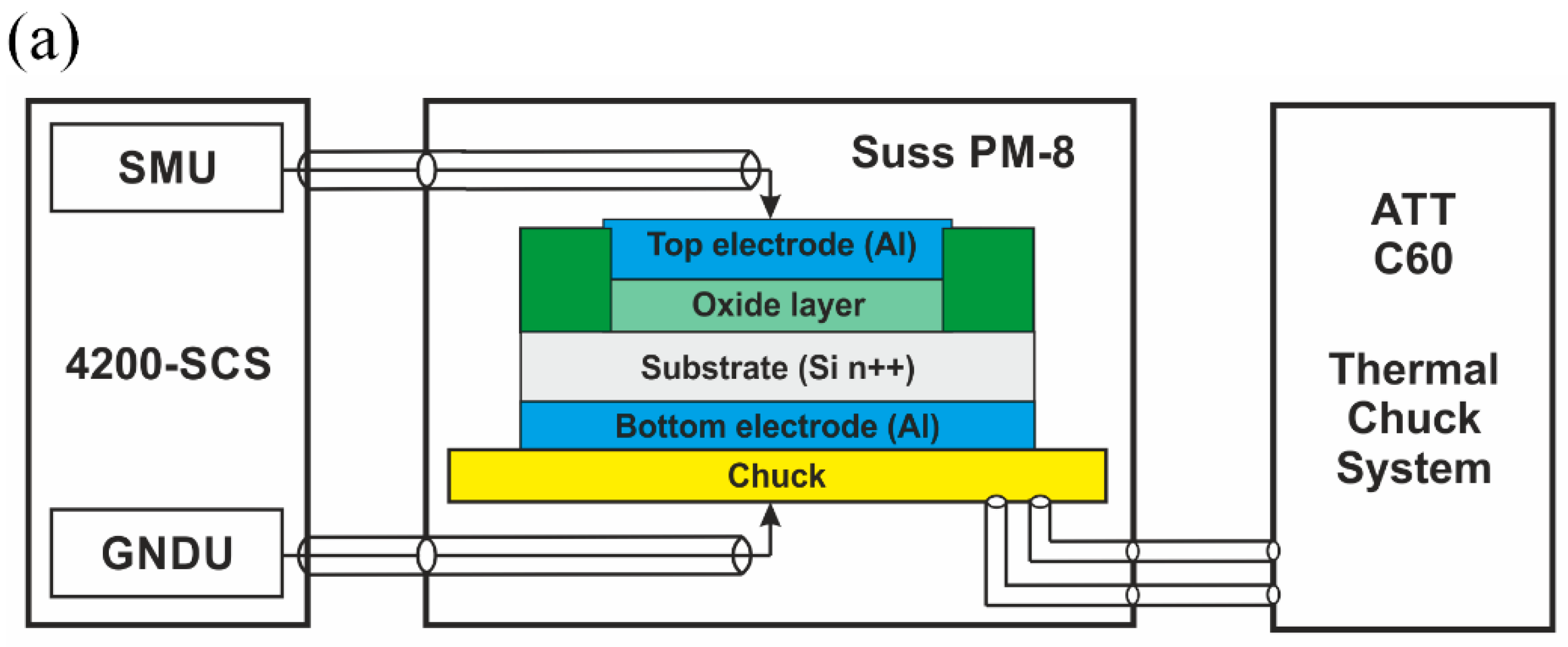

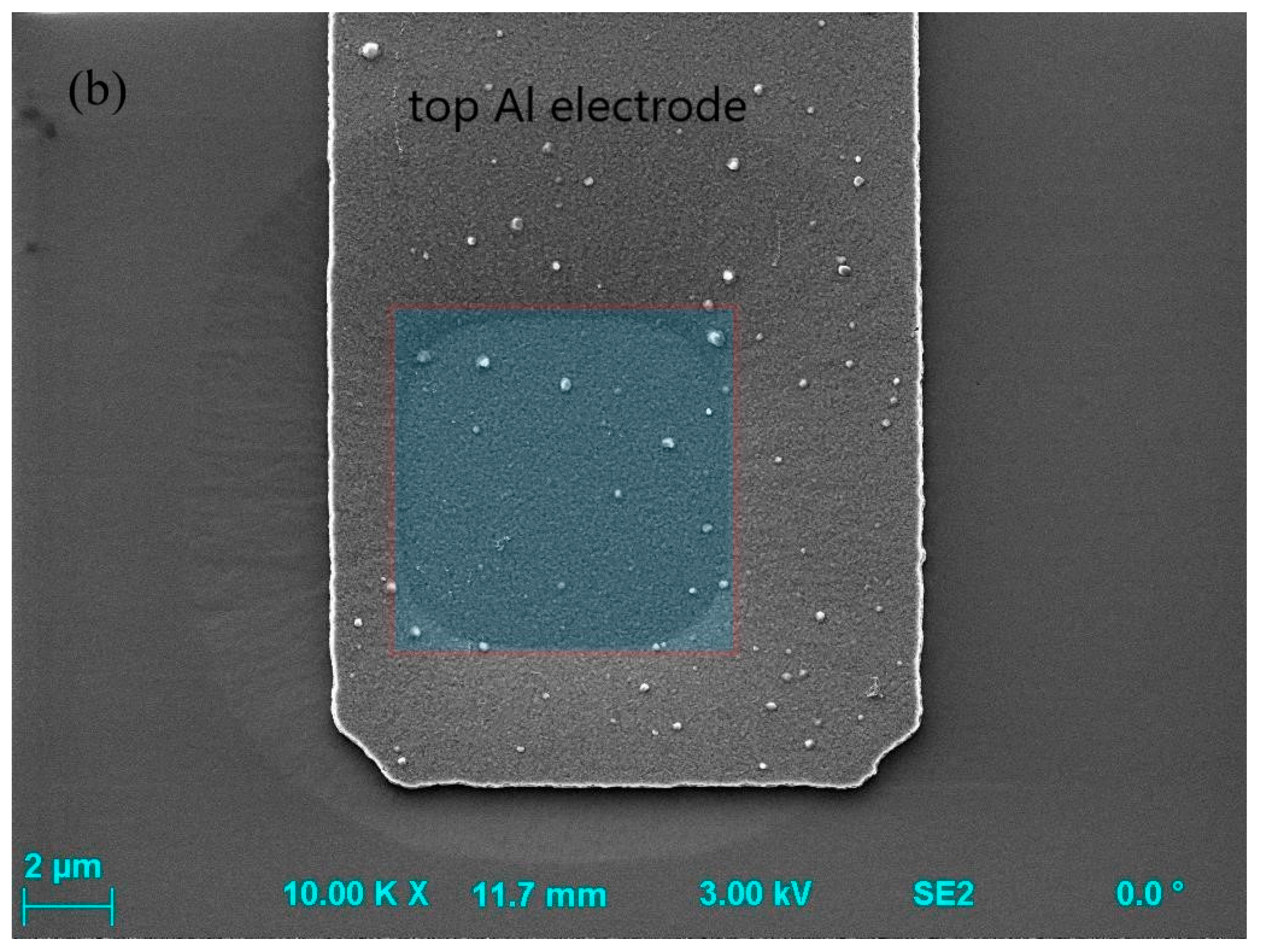

2. Materials and Methods

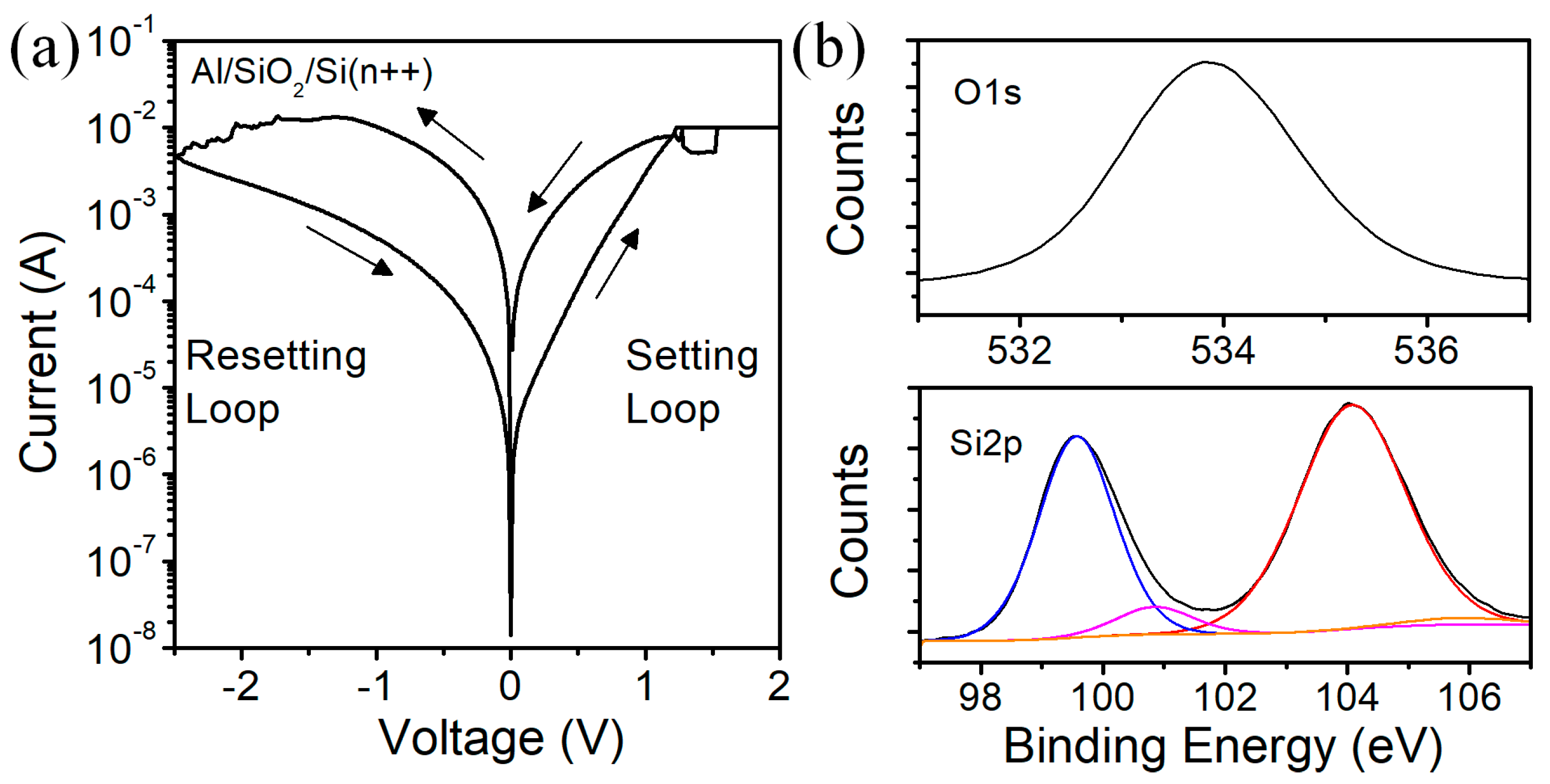

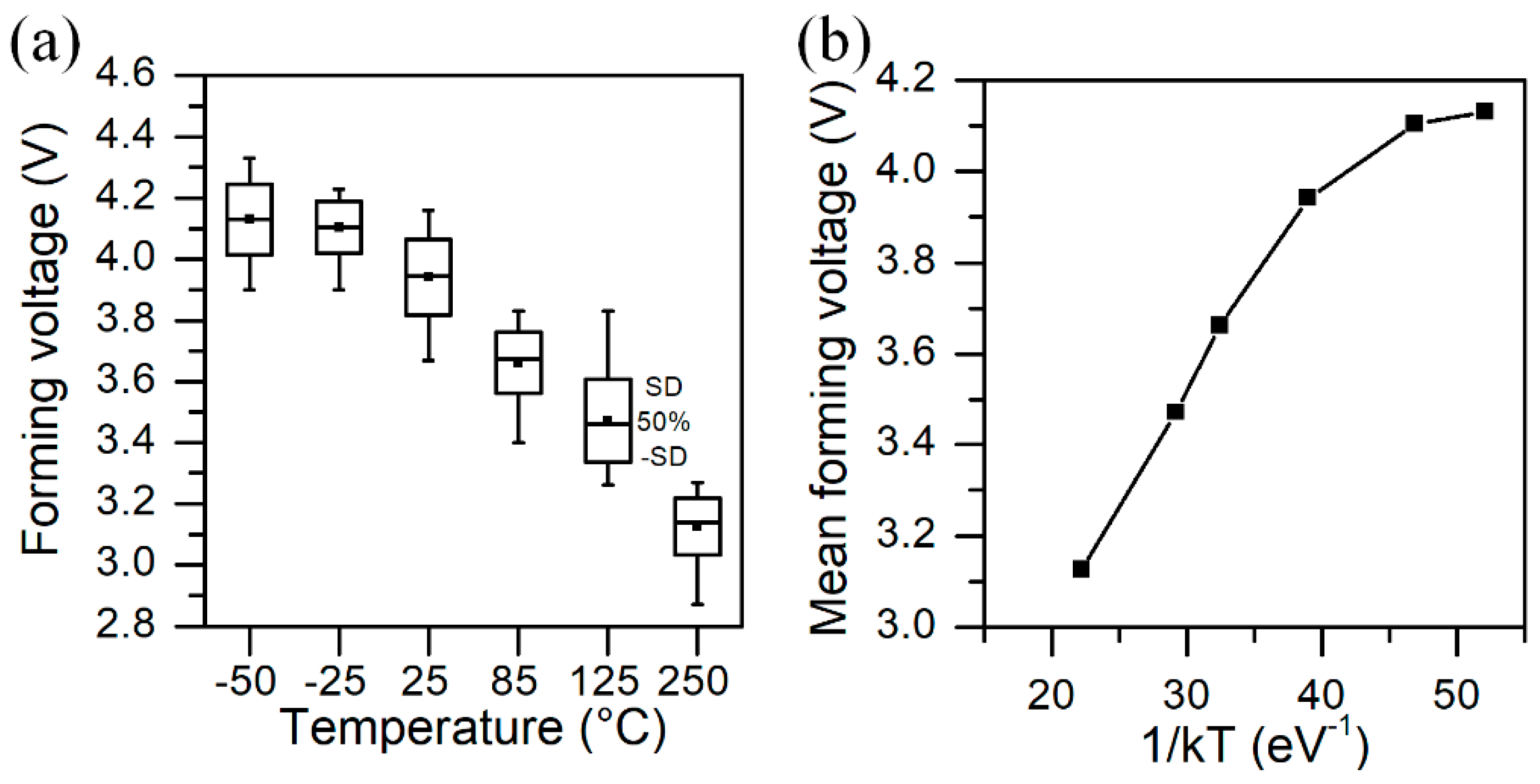

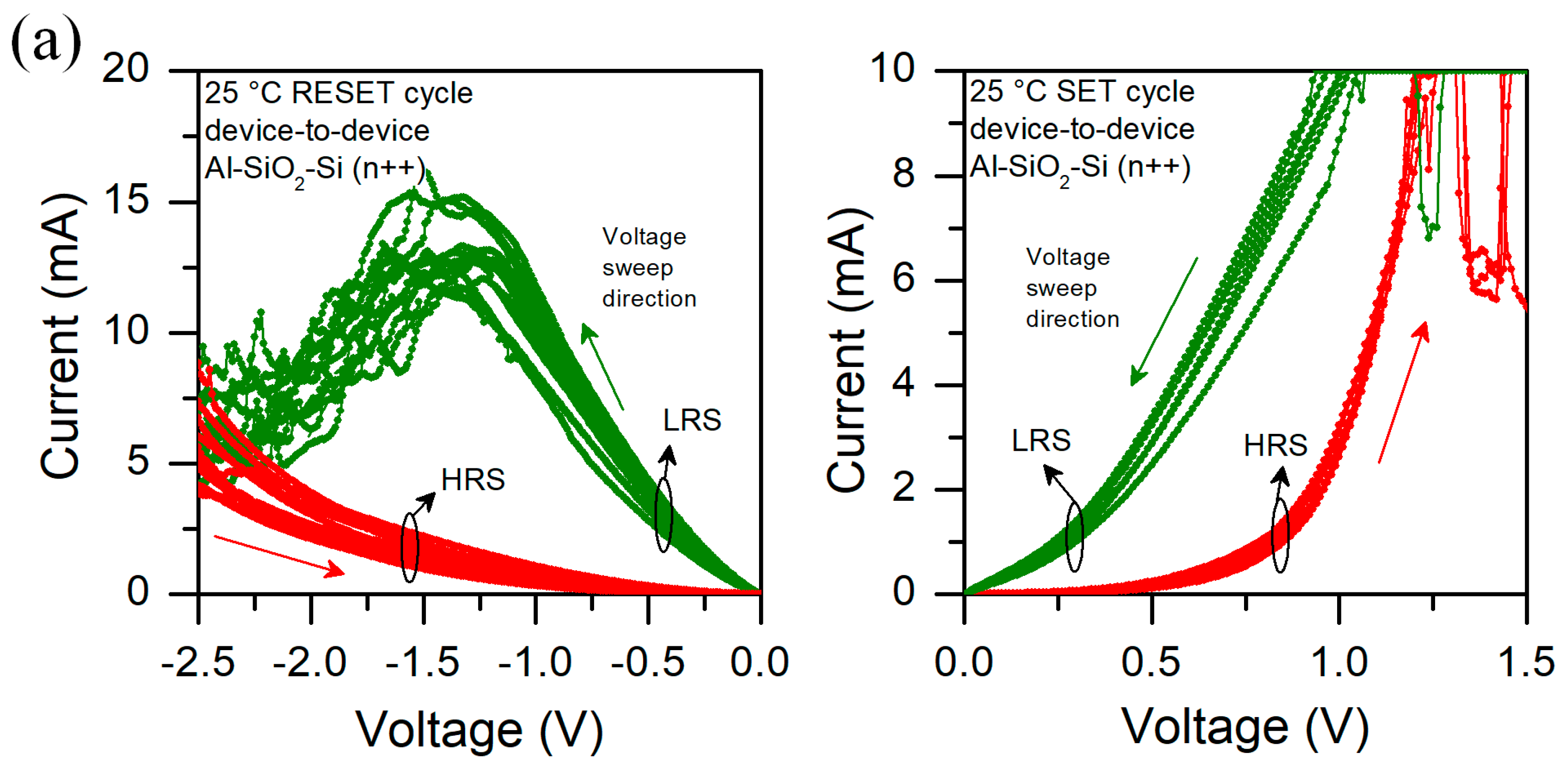

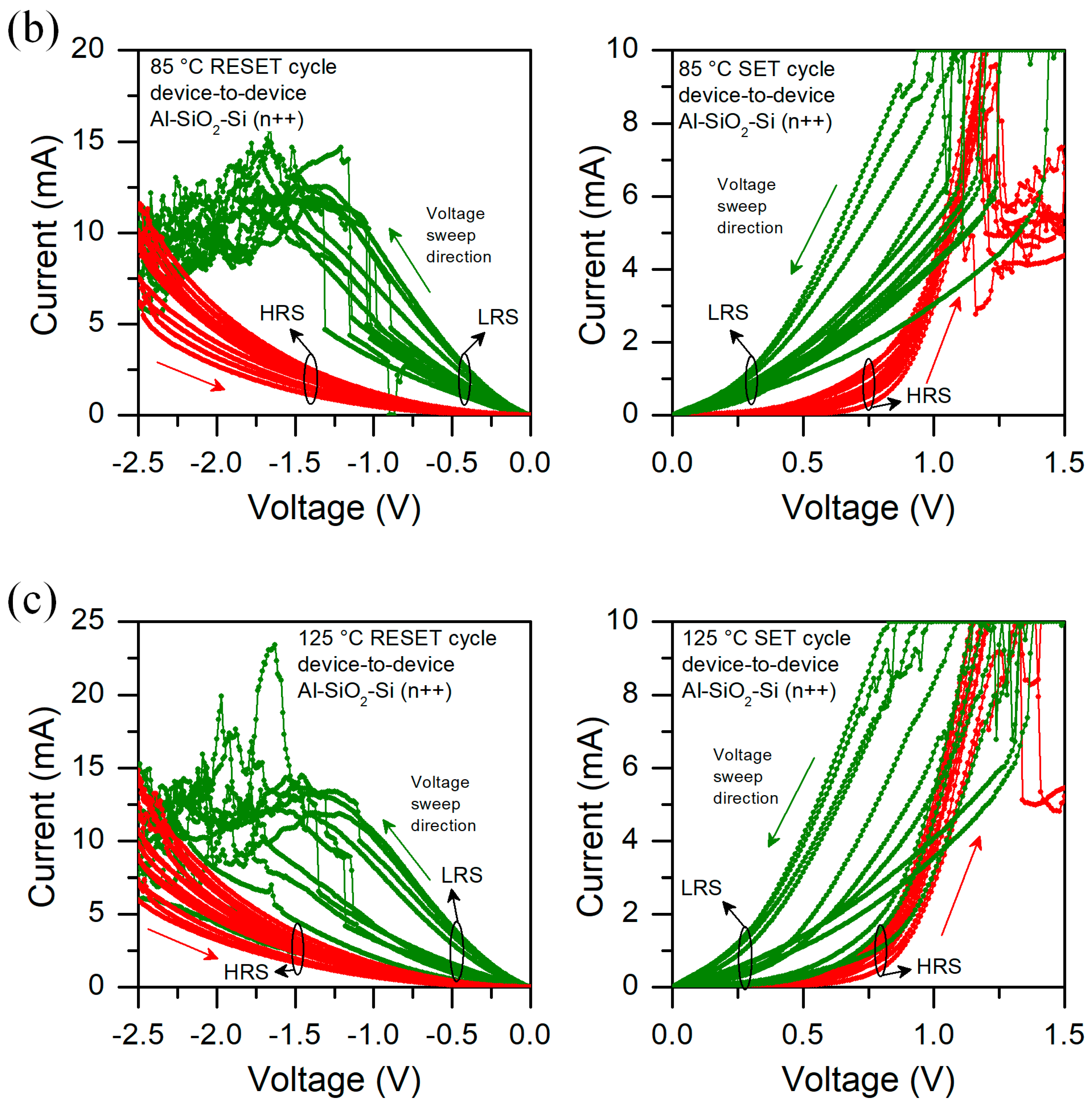

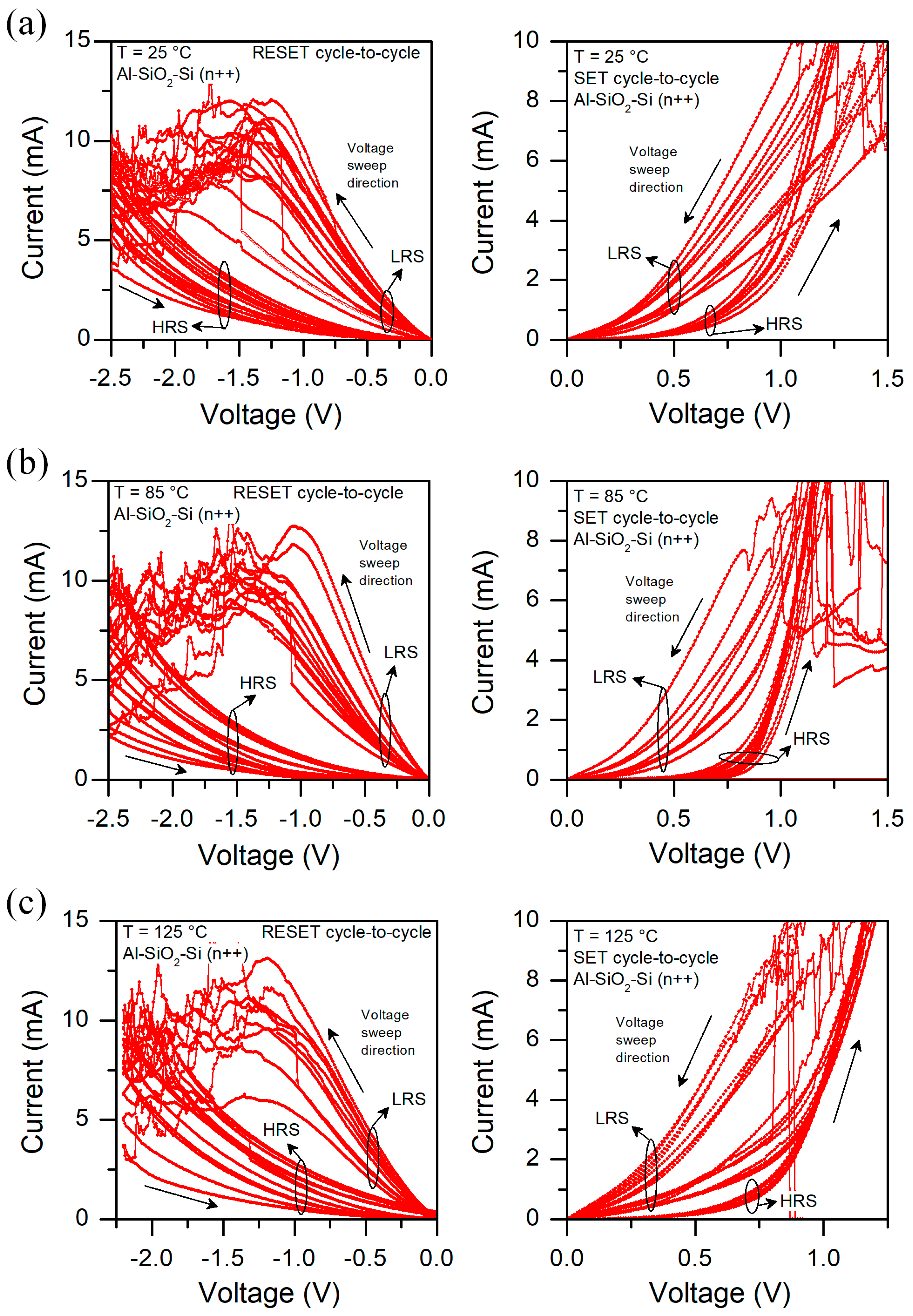

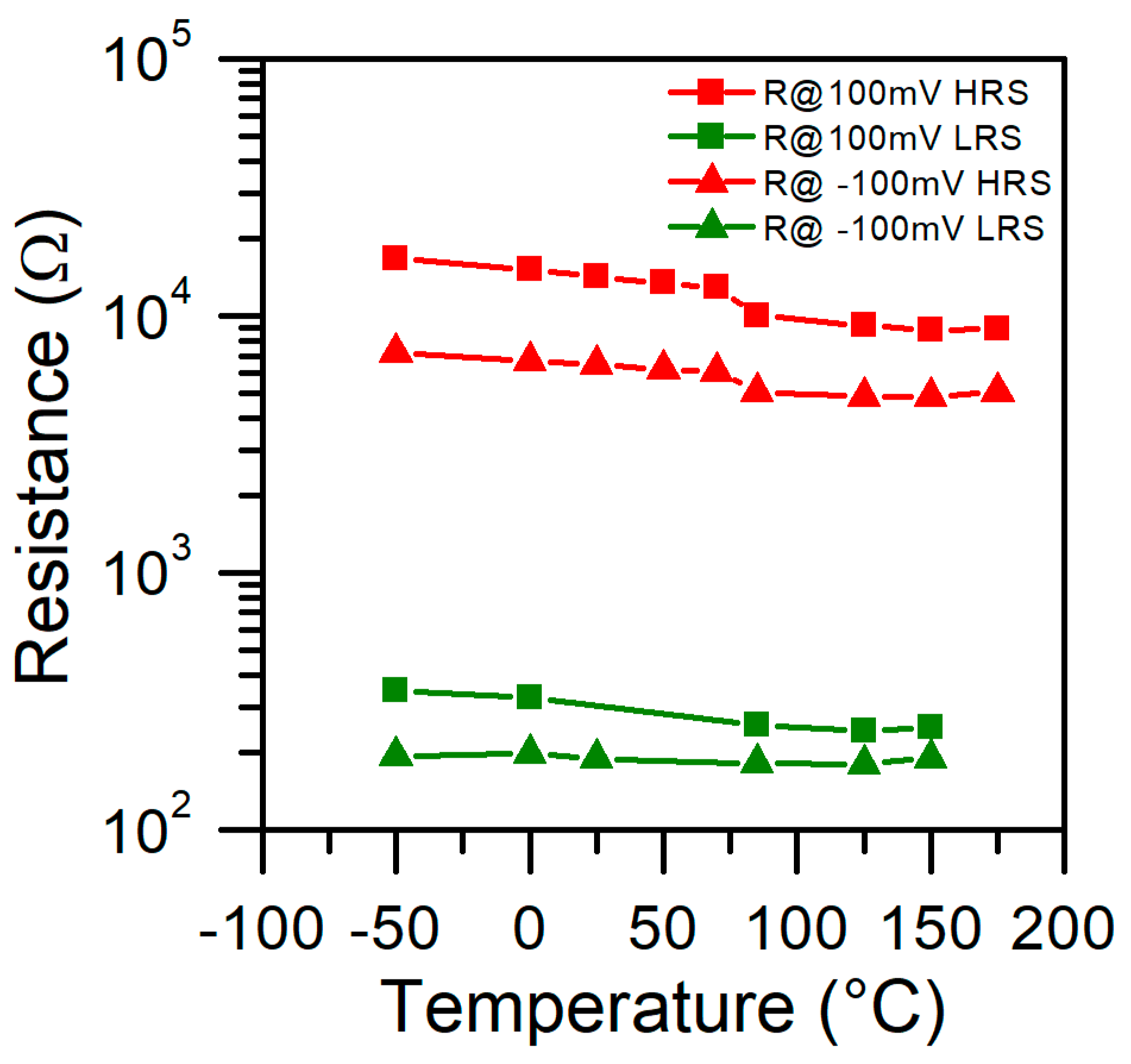

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Kim, Y.-B. Challenges for Nanoscale MOSFETs and Emerging Nanoelectronics. Trans. Electr. Electron. Mater. 2010, 11, 93–105. [Google Scholar] [CrossRef]

- Theis, T.N.; Solomon, P.M. In Quest of the “Next Switch”: Prospects for Greatly Reduced Power Dissipation in a Successor to the Silicon Field-Effect Transistor. Proc. IEEE 2010, 98, 2005–2014. [Google Scholar] [CrossRef]

- Waser, R.; Aono, M. Nanoionics-based resistive switching memories. Nat. Mater. 2007, 6, 833–840. [Google Scholar] [CrossRef]

- Ielmini, D. Resistive switching memories based on metal oxides: Mechanisms, reliability and scaling. Semicond. Sci. Technol. 2016, 31, 063002. [Google Scholar] [CrossRef]

- Akinaga, H.; Shima, H. Resistive random access memory (ReRAM) based on metal oxides. Proc. IEEE 2010, 98, 2237–2251. [Google Scholar] [CrossRef]

- Wong, H.S.P.; Lee, H.Y.; Yu, S.; Chen, Y.S.; Wu, Y.; Chen, P.S.; Lee, B.; Chen, F.T.; Tsai, M.J. Metal-oxide RRAM. Proc. IEEE 2012, 100, 1951–1970. [Google Scholar] [CrossRef]

- Kent, A.D.; Worledge, D.C. A new spin on magnetic memories. Nat. Nanotechnol. 2015, 10, 187–191. [Google Scholar] [CrossRef]

- Wang, Z.; Hao, X.; Xu, P.; Hu, L.; Jung, D.; Kim, W.; Satoh, K.; Yen, B.; Wei, Z.; Wang, L.; et al. STT-MRAM for Embedded Memory Applications. In Proceedings of the 2020 IEEE International Memory Workshop (IMW), Dresden, Germany, 17–20 May 2020. [Google Scholar] [CrossRef]

- Mikolajick, T.; Dehm, C.; Hartner, W.; Kasko, I.; Kastner, M.J.; Nagel, N.; Moert, M.; Mazure, C. FeRAM technology for high density applications. Microelectron. Reliab. 2001, 41, 947–950. [Google Scholar] [CrossRef]

- Raoux, S.; Wełnic, W.; Lelmini, D. Phase change materials and their application to nonvolatile memories. Chem. Rev. 2010, 110, 240–267. [Google Scholar] [CrossRef]

- Zhu, J.; Zhang, T.; Yang, Y.; Huang, R. A comprehensive review on emerging artificial neuromorphic devices. Appl. Phys. Rev. 2020, 7, 011312. [Google Scholar] [CrossRef]

- Molas, G.; Nowak, E. Advances in Emerging Memory Technologies: From Data Storage to Artificial Intelligence. Appl. Sci. 2021, 11, 11254. [Google Scholar] [CrossRef]

- Dang, B.B.; Liu, K.; Wu, X.; Yang, Z.; Xu, L.; Yang, Y.; Huang, R. One-phototransistor-one-memristor Array with High-linearity Light-tunable Weight for Optic Neuromorphic Computing. Adv. Mater. 2022, 2204844. [Google Scholar] [CrossRef]

- Yuan, F.-Y.; Deng, N.; Shih, C.-C.; Tseng, Y.-T.; Chang, T.-C.; Chang, K.-C.; Wang, M.-H.; Chen, W.-C.; Zheng, H.-X.; Wu, H.; et al. Conduction Mechanism and Improved Endurance in HfO 2-Based RRAM with Nitridation Treatment. Nanoscale Res. Lett. 2017, 12, 574. [Google Scholar] [CrossRef]

- Yu, S.; Guan, X.; Wong, H.-S.P. Conduction mechanism of TiN/HfOx/Pt resistive switching memory: A trap-assisted-tunneling model. Appl. Phys. Lett. 2011, 99, 063507. [Google Scholar] [CrossRef]

- Jung, P.Y.; Panda, D.; Chandrasekaran, S.; Rajasekaran, S.; Tseng, T.Y. Enhanced Switching Properties in TaOx Memristors Using Diffusion Limiting Layer for Synaptic Learning. IEEE J. Electron Devices Soc. 2020, 8, 110–115. [Google Scholar] [CrossRef]

- Mehonic, A.; Cueff, S.; Wojdak, M.; Hudziak, S.; Jambois, O.; Labbe, C.; Garrido, B.; Rizk, R.; Kenyon, A.J.; Cueff, S.; et al. Resistive switching in silicon suboxide films. J. Appl. Phys. 2012, 111, 074507. [Google Scholar] [CrossRef]

- Chang, Y.-F.; Chen, P.-Y.; Fowler, B.; Chen, Y.-T.; Xue, F.; Wang, Y.; Zhou, F.; Lee, J.C. Understanding the resistive switching characteristics and mechanism in active SiO x-based resistive switching memory. J. Appl. Phys 2012, 112, 123702. [Google Scholar] [CrossRef]

- Mehonic, A.; Shluger, A.L.; Gao, D.; Valov, I.; Miranda, E.; Ielmini, D.; Bricalli, A.; Ambrosi, E.; Li, C.; Yang, J.J.; et al. Silicon Oxide (SiOx): A Promising Material for Resistance Switching? Adv. Mater. 2018, 30, 1801187. [Google Scholar] [CrossRef]

- Li, C.; Han, L.; Jiang, H.; Jang, M.H.; Lin, P.; Wu, Q.; Barnell, M.; Yang, J.J.; Xin, H.L.; Xia, Q. Three-dimensional crossbar arrays of self-rectifying Si/SiO2/Si memristors. Nat. Commun. 2017, 8, 15666. [Google Scholar] [CrossRef]

- Wiśniewski, P.; Jasiński, J.; Mazurak, A.; Stonio, B.; Majkusiak, B. Investigation of Electrical Properties of the Al/SiO2/n++-Si Resistive Switching Structures by Means of Static, Admittance, and Impedance Spectroscopy Measurements. Materials 2021, 14, 6042. [Google Scholar] [CrossRef]

- Wiśniewski, P.; Jasiński, J.; Mazurak, A. Conductance modulation in Al/SiO2/n-Si MIS resistive switching structures. In Proceedings of the 2021 Joint International EUROSOI Workshop and International Conference on Ultimate Integration on Silicon (EuroSOI-ULIS), Caen, France, 1–3 September 2021; pp. 5–8. [Google Scholar] [CrossRef]

- Polino, N.; Laudato, M.; Ambrosi, E.; Bricalli, A.; Ielmini, D. Joule Heating in SiOx RRAM Device Studied by an Integrated Micro-Thermal Stage. In Proceedings of the ESSDERC 2019—49th European Solid-State Device Research Conference (ESSDERC), Cracow, Poland, 23–26 September 2019; pp. 126–129. [Google Scholar] [CrossRef]

- Yoon, S.J.; Ryu, J.-H.; Ismail, M.; Chen, Y.-C.; Chang, Y.-F.; Yun, M.J.; Kim, H.-D.; Kim, S. Compliance current and temperature effects on non-volatile memory switching and volatile switching dynamics in a Cu/SiOx/p++-Si device. Appl. Phys. Lett. 2019, 115, 212102. [Google Scholar] [CrossRef]

- Das, N.C.; Kim, M.; Hong, S.M.; Jang, J.H. Vacuum and Low-Temperature Characteristics of Silicon Oxynitride-Based Bipolar RRAM. Micromachines 2022, 13, 604. [Google Scholar] [CrossRef]

- Larentis, S.; Nardi, F.; Balatti, S.; Gilmer, D.C.; Ielmini, D. Resistive switching by voltage-driven ion migration in bipolar RRAMPart II: Modeling. IEEE Trans. Electron Devices 2012, 59, 2468–2475. [Google Scholar] [CrossRef]

- Omura, Y.; Yamaguchi, R.; Sato, S. Study on the Impacts of Hole Injection and Inclusion of Sub-Oxide and Metallic Si Atoms on Repeatable Resistance Switching of Sputter-Deposited Silicon Oxide Films. IEEE Trans. Device Mater. Reliab. 2018, 18, 561–567. [Google Scholar] [CrossRef]

- Yamaguchi, R.; Sato, S.; Omura, Y. Roles of chemical stoichiometry and hot electrons in realizing the stable resistive transition of sputter-deposited silicon oxide films. Jpn. J. Appl. Phys. 2017, 56, 041301. [Google Scholar] [CrossRef]

- Chen, G.Y.; Lee, F.M.; Lin, Y.Y.; Tseng, P.H.; Hsu, K.C.; Lee, D.Y.; Lee, M.H.; Lung, H.L.; Hsieh, K.Y.; Wang, K.C.; et al. The impact of forming temperature and voltage on the reliability of filamentary rram. In Proceedings of the 2019 International Symposium on VLSI Technology, Systems and Application (VLSI-TSA), Hsinchu, Taiwan, 22–25 April 2019. [Google Scholar] [CrossRef]

- Pic, D.; Goguenheim, D.; Ogier, J.L. Assessment of temperature and voltage accelerating factors for 2.3–3.2 nm SiO2 thin oxides stressed to hard breakdown. Microelectron. Reliab. 2008, 48, 335–341. [Google Scholar] [CrossRef]

- Kim, Y.H.; Onishi, K.; Kang, C.S.; Cho, H.J.; Choi, R.; Krishnan, S.; Akbar, M.S.; Lee, J.C. Thickness dependence of Weibull slopes of HfO2 gate dielectrics. IEEE Electron Device Lett. 2003, 24, 40–42. [Google Scholar] [CrossRef]

- Kauerauf, T.; Degraeve, R.; Ragnarsson, L.Å.; Roussel, P.; Sahhaf, S.; Groeseneken, G.; O’Connor, R. Methodologies for sub-1nm EOT TDDB evaluation. In Proceedings of the 2011 International Reliability Physics Symposium, Monterey, CA, USA, 10–14 April 2011; pp. 7–16. [Google Scholar] [CrossRef]

- Govoreanu, B.; Kubicek, S.; Kar, G.; Chen, Y.Y.; Paraschiv, V.; Rakowski, M.; Degraeve, R.; Goux, L.; Clima, S.; Jossart, N.; et al. Investigation of Forming and Its Controllability in Novel HfO2-Based 1T1R 40nm-Crossbar RRAM Cells. In Proceedings of the 2011 International Conference on Solid State Devices and Materials, Nagoya, Japan, 27–30 September 2011. [Google Scholar] [CrossRef]

- Long, S.; Lian, X.; Cagli, C.; Perniola, L.; Miranda, E.; Jimenez, D.; Lv, H.; Liu, Q.; Li, L.; Huo, Z.; et al. Compact analytical models for the SET and RESET switching statistics of RRAM inspired in the cell-based percolation model of gate dielectric breakdown. In Proceedings of the 2013 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 14–18 April 2013; pp. 1–8. [Google Scholar] [CrossRef]

- Long, S.; Cagli, C.; Ielmini, D.; Liu, M.; Suñé, J. Reset statistics of nio-based resistive switching memories. IEEE Electron Device Lett. 2011, 32, 1570–1572. [Google Scholar] [CrossRef]

- Luo, W.C.; Lin, K.L.; Huang, J.J.; Lee, C.L.; Hou, T.H. Rapid prediction of rram reset-state disturb by ramped voltage stress. IEEE Electron Device Lett. 2012, 33, 597–599. [Google Scholar] [CrossRef]

- Zhang, X.; Xu, L.; Zhang, H.; Liu, J.; Tan, D.; Chen, L.; Ma, Z.; Li, W. Effect of Joule Heating on Resistive Switching Characteristic in AlOx Cells Made by Thermal Oxidation Formation. Nanoscale Res. Lett. 2020, 15, 11. [Google Scholar] [CrossRef]

- Zhang, P.; Ang, Y.S.; Garner, A.L.; Valfells, Á.; Luginsland, J.W.; Ang, L.K. Space-charge limited current in nanodiodes: Ballistic, collisional, and dynamical effects. J. Appl. Phys. 2021, 129, 100902. [Google Scholar] [CrossRef]

| Temperature (°C) | Shape Parameter β | Scale Parameter (V) |

|---|---|---|

| −50 | 43.57 | 4.18 |

| −25 | 59.93 | 4.14 |

| 25 | 38.95 | 4.00 |

| 85 | 45.30 | 3.71 |

| 125 | 30.01 | 3.54 |

| 250 | 40.99 | 3.17 |

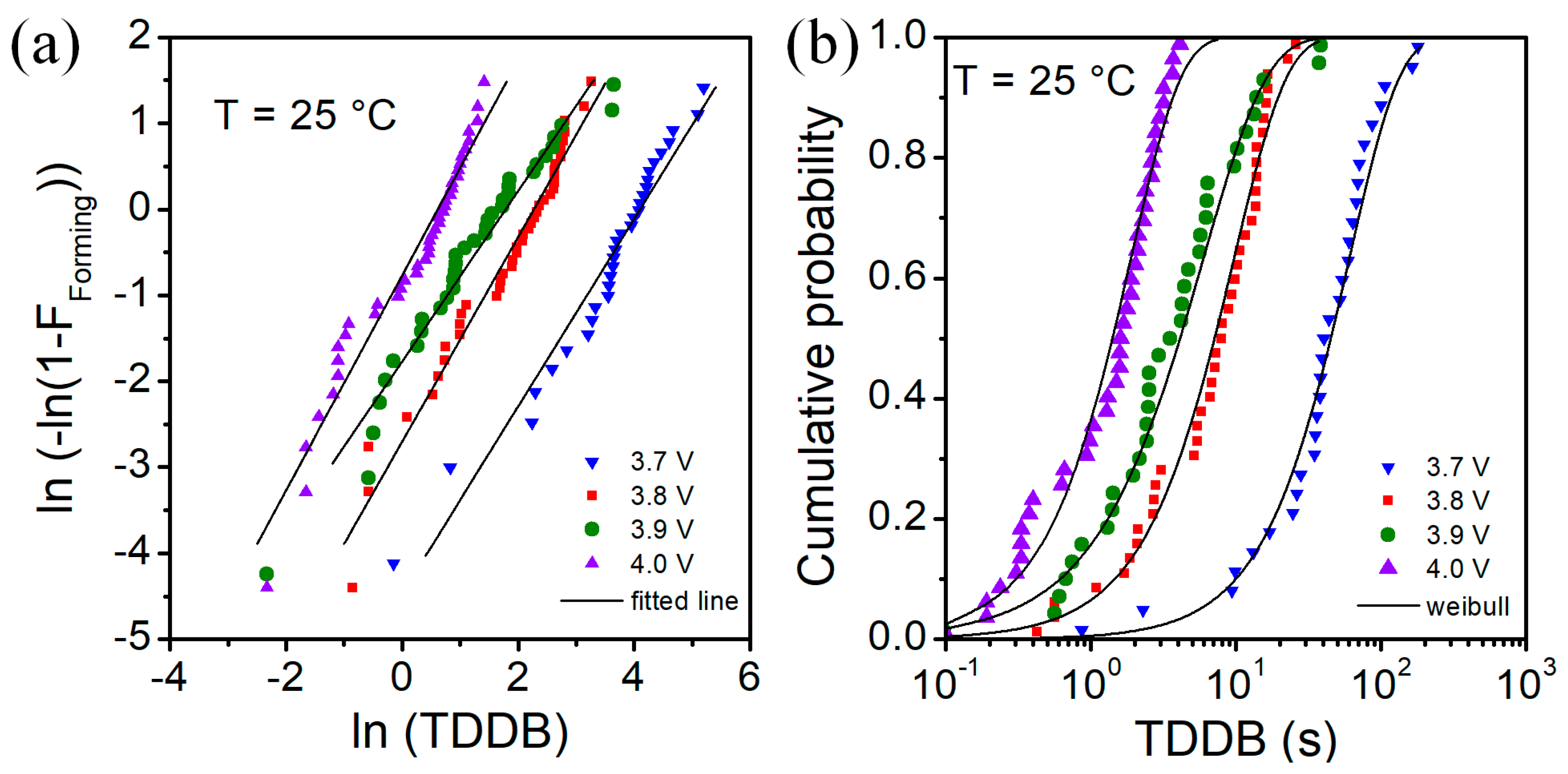

| Temperature (°C) | Stress Voltage (V) | Shape Parameter β | Scale Parameter (s) |

|---|---|---|---|

| 25 | 3.7 | 1.09 | 60.16 |

| 25 | 3.8 | 1.19 | 9.65 |

| 25 | 3.9 | 0.99 | 5.93 |

| 25 | 4.0 | 1.25 | 1.84 |

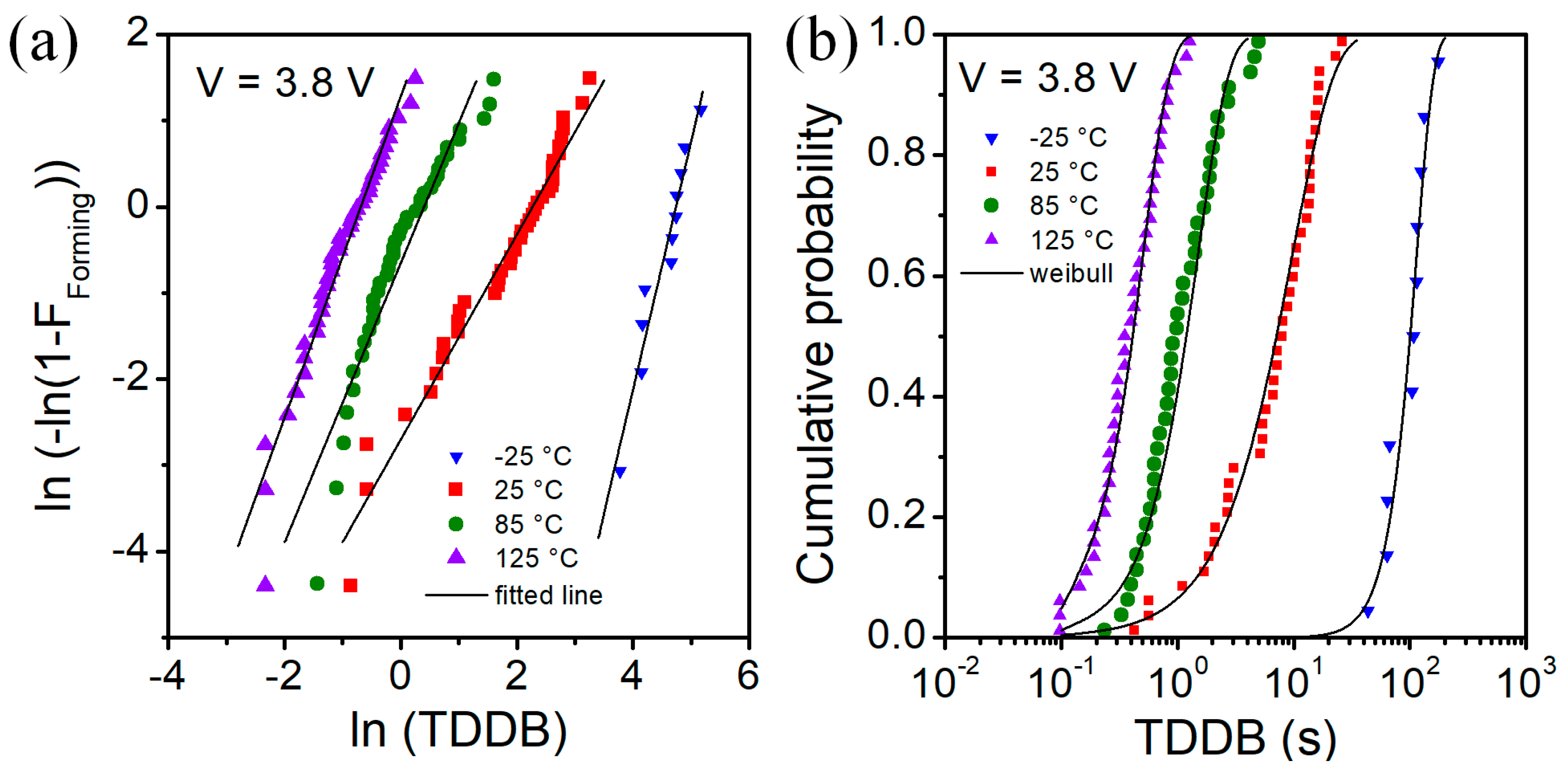

| −25 | 3.8 | 2.88 | 113.78 |

| 85 | 3.8 | 1.62 | 1.49 |

| 85 | 3.9 | 1.24 | 1.12 |

| 85 | 4.1 | 1.20 | 1.03 |

| 125 | 3.8 | 1.86 | 0.50 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wiśniewski, P.; Nieborek, M.; Mazurak, A.; Jasiński, J. Investigation of the Temperature Effect on Electrical Characteristics of Al/SiO2/n++-Si RRAM Devices. Micromachines 2022, 13, 1641. https://doi.org/10.3390/mi13101641

Wiśniewski P, Nieborek M, Mazurak A, Jasiński J. Investigation of the Temperature Effect on Electrical Characteristics of Al/SiO2/n++-Si RRAM Devices. Micromachines. 2022; 13(10):1641. https://doi.org/10.3390/mi13101641

Chicago/Turabian StyleWiśniewski, Piotr, Mateusz Nieborek, Andrzej Mazurak, and Jakub Jasiński. 2022. "Investigation of the Temperature Effect on Electrical Characteristics of Al/SiO2/n++-Si RRAM Devices" Micromachines 13, no. 10: 1641. https://doi.org/10.3390/mi13101641

APA StyleWiśniewski, P., Nieborek, M., Mazurak, A., & Jasiński, J. (2022). Investigation of the Temperature Effect on Electrical Characteristics of Al/SiO2/n++-Si RRAM Devices. Micromachines, 13(10), 1641. https://doi.org/10.3390/mi13101641