The Design of Terahertz Frequency Quadruplers Based on Discrete Schottky Diodes

Abstract

:1. Introduction

2. Quadrupler Design

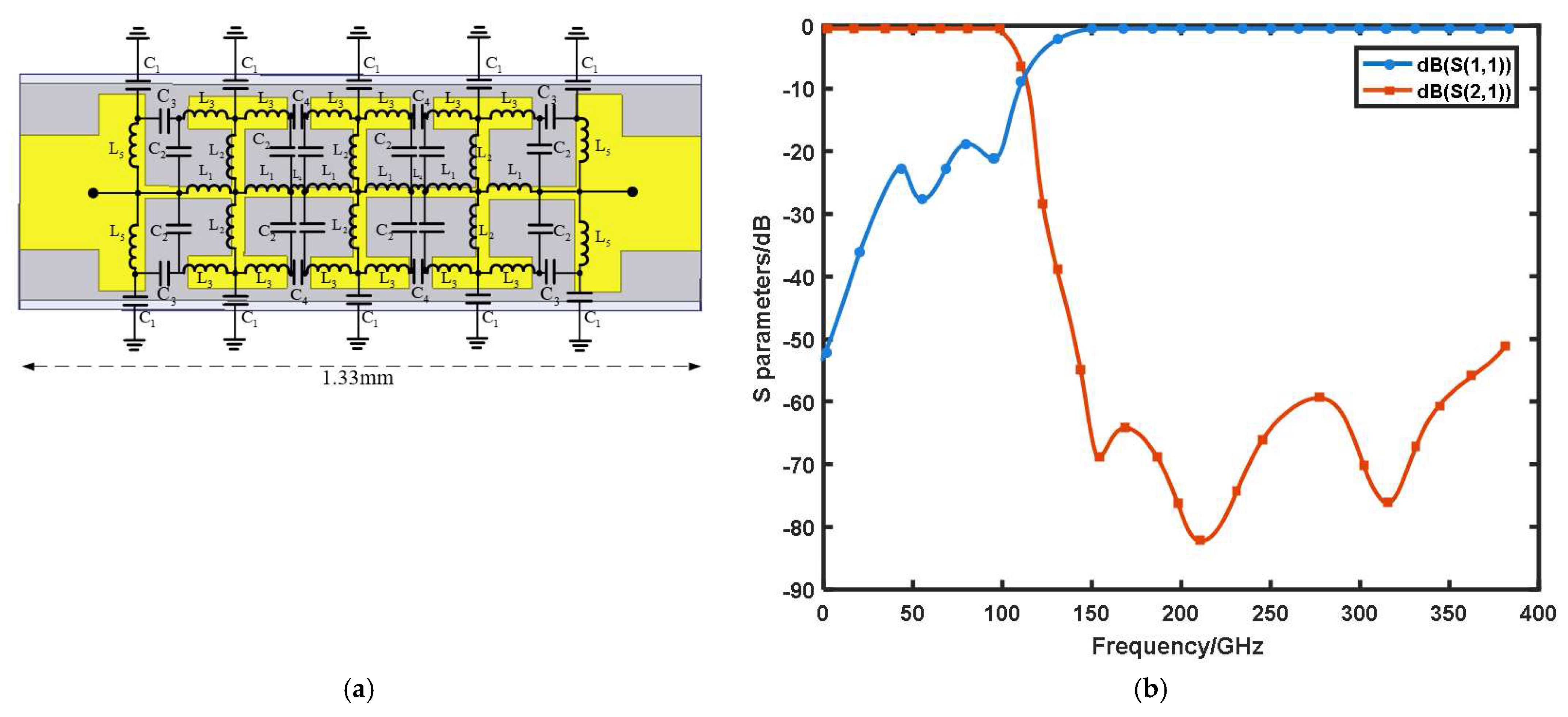

2.1. Idle Loop Theory Analysis and Design

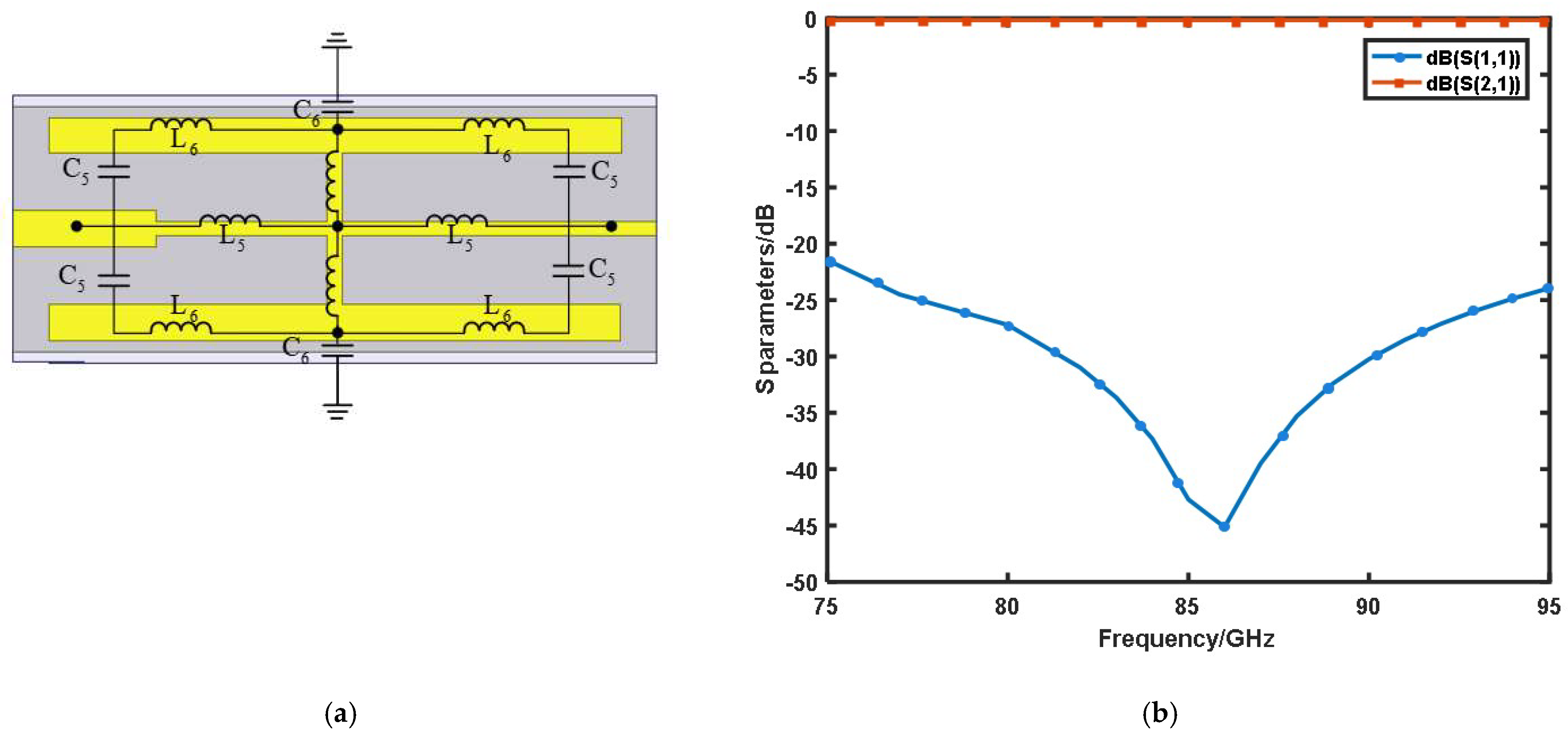

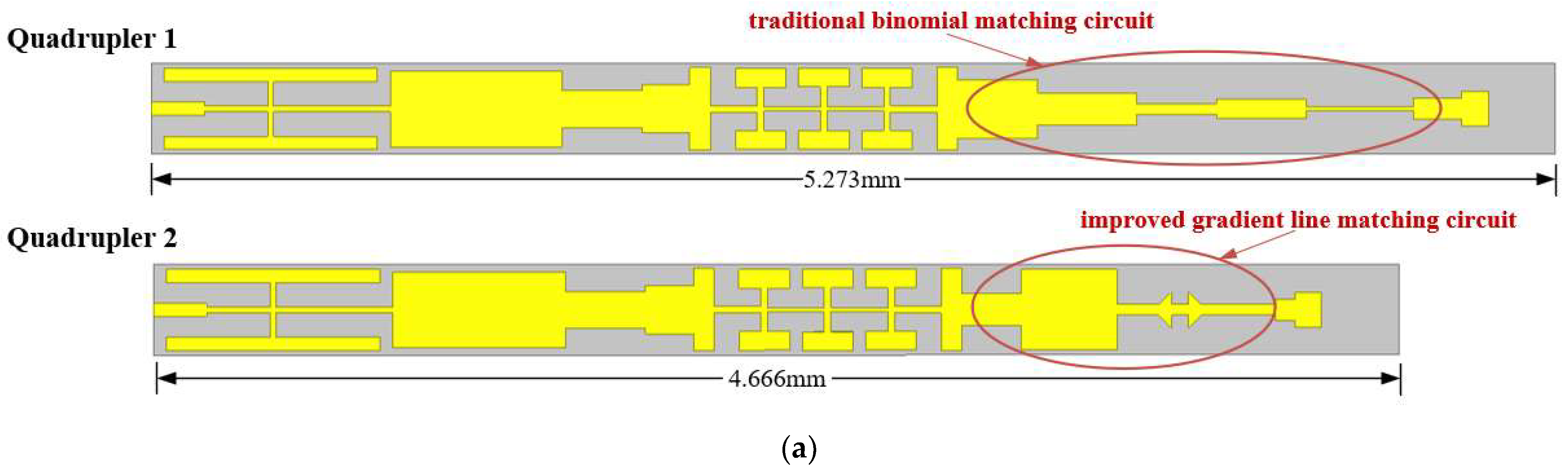

2.2. Matching Circuit Improvement

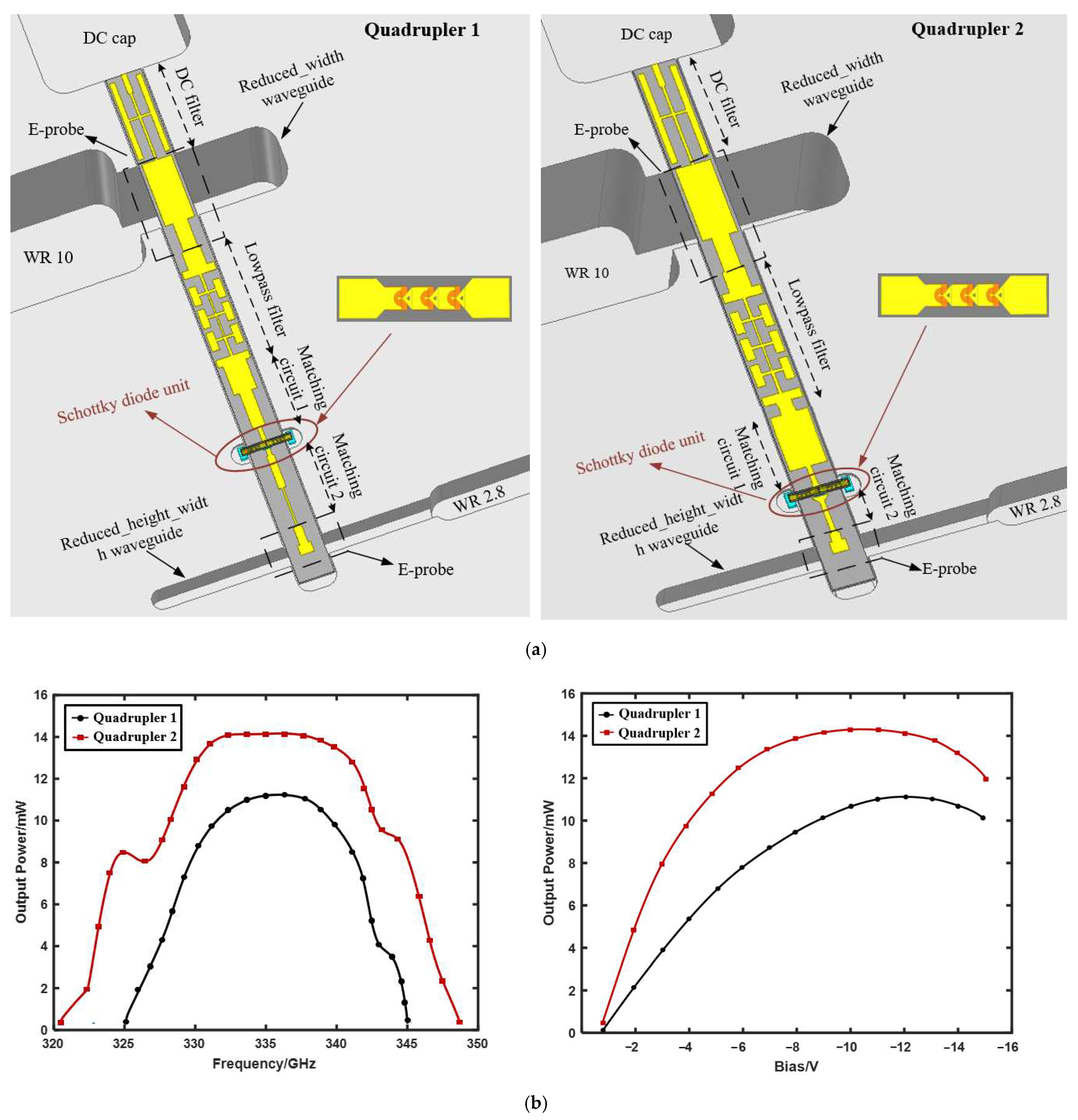

2.3. Overall Models and Simulation Results

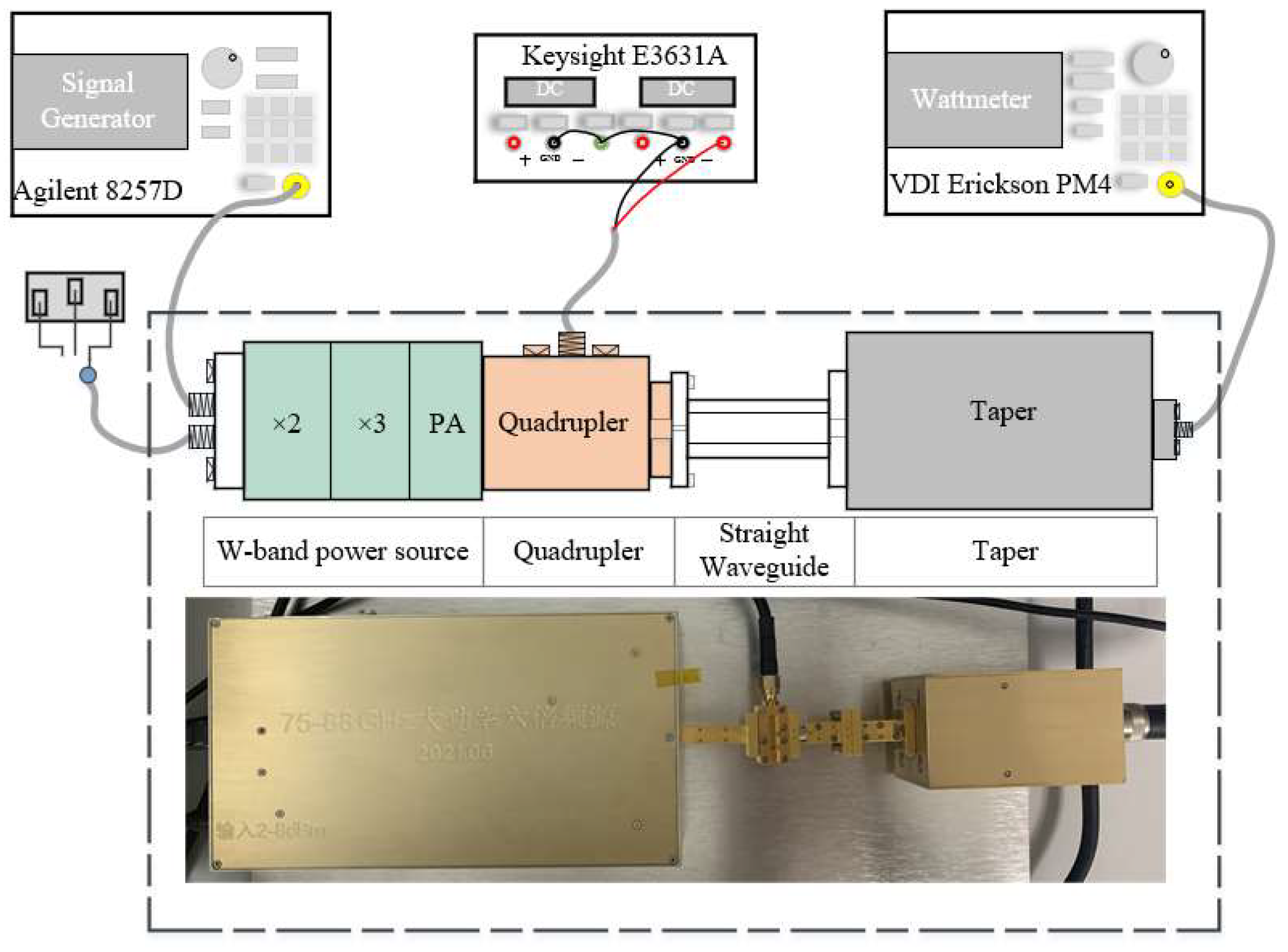

3. Fabrication and Measurement

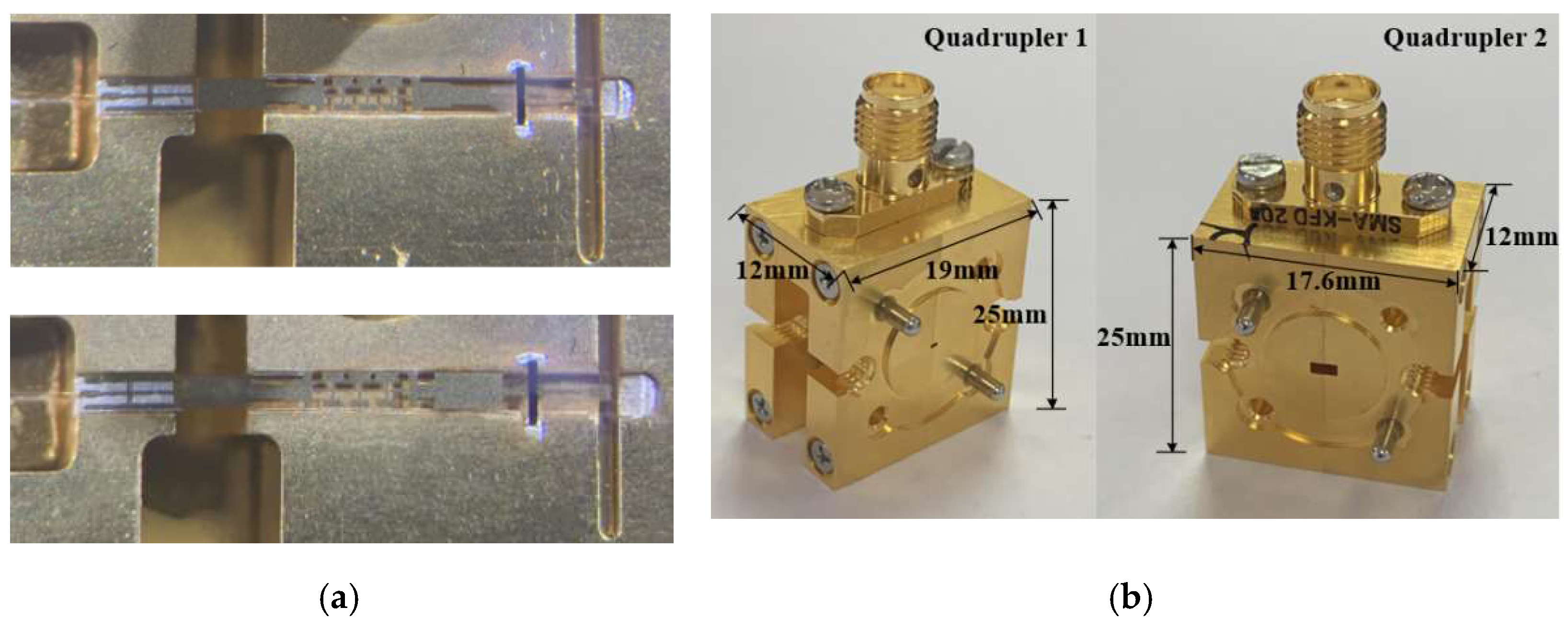

3.1. Assembly and Fabrication

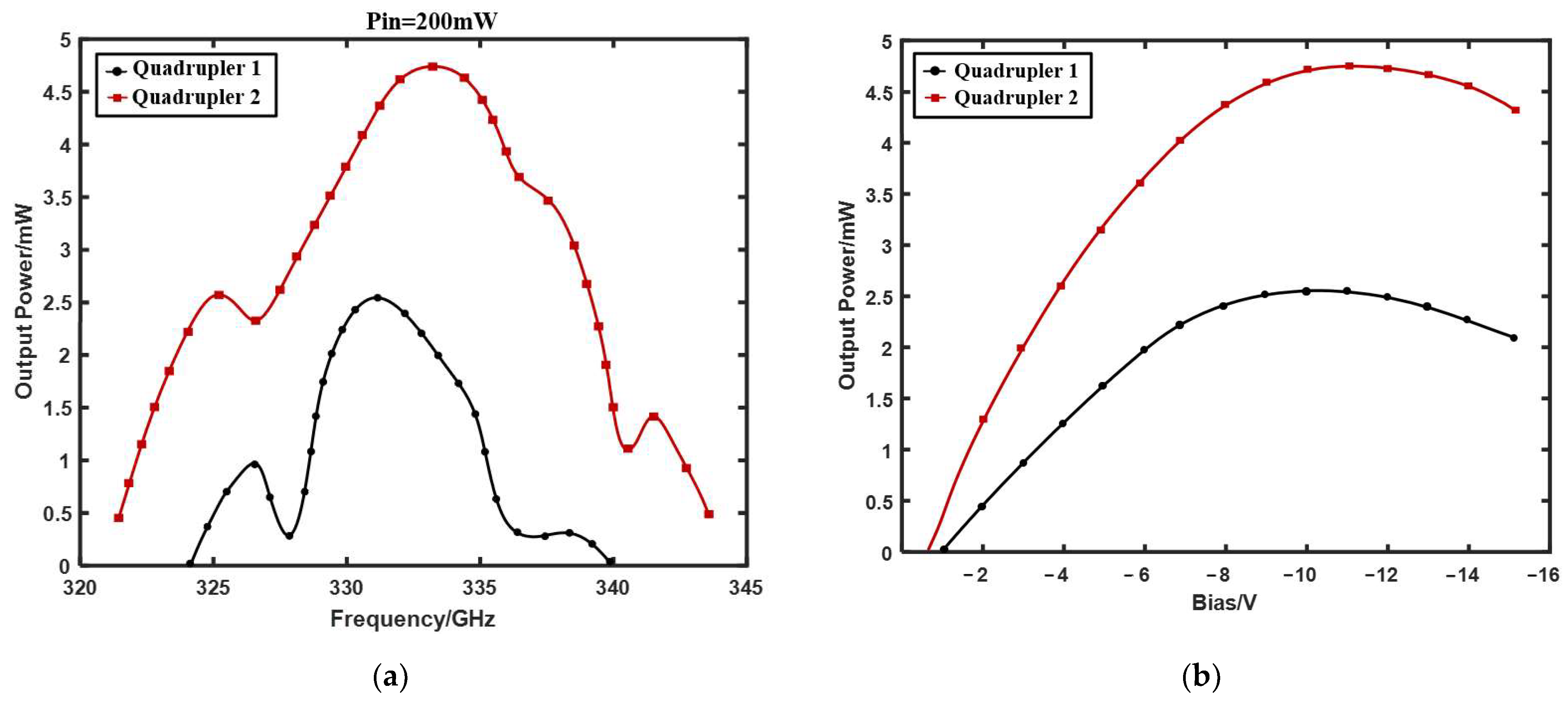

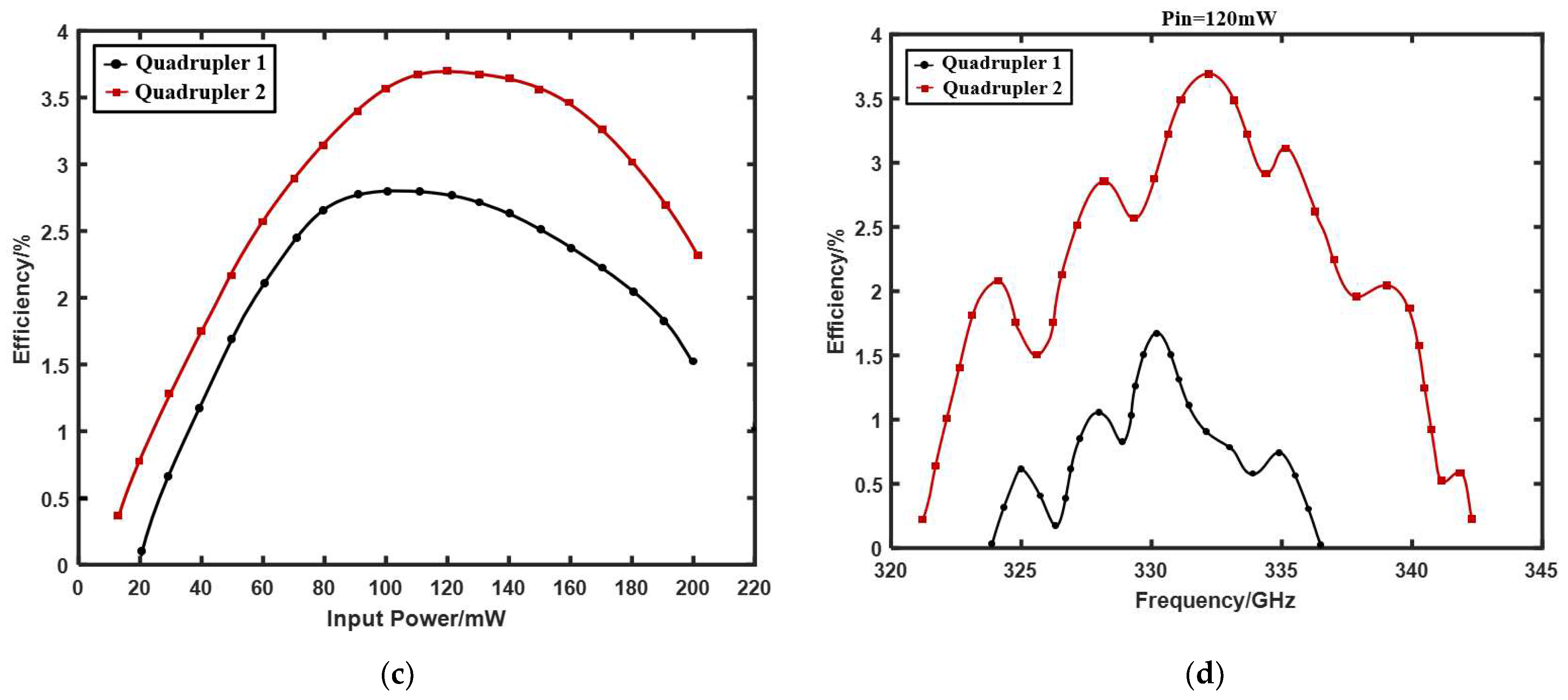

3.2. Test Results

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Kangaslahti, P.; Schlecht, E.; Jiang, J.; Deal, W.R.; Jiang, J.; Deal, W.R.; Zamora, A.; Leong, K.; Reising, S.C.; Bosch, X.; et al. CubeSat scale receivers for measurement of ice in clouds. In Proceedings of the 14th Specialist Meeting on Microwave Radiometry and Remote Sensing of the Environment, Espoo, Finland, 11–14 April 2016. [Google Scholar]

- Arora, A.; Luong, T.Q.; Krüger, M.; Kim, Y.J.; Nam, C.H.; Manz, A.; Havenith, M. Terahertz-time domain spectroscopy for the detection of PCR amplified DNA in aqueous solution. Analyst 2012, 137, 575–579. [Google Scholar] [CrossRef] [PubMed]

- Thomas, B.; Gill, J.; Maestrini, A.; Lee, C.; Lin, R.; Sin, S.; Peralta, A.; Mehdi, I. An integrated 520–600 GHz sub-harmonic mixer and tripler combination based on GaAs MMIC membrane planar Schottky diodes. In Proceedings of the 35th International Conference on Infrared Millimeter & Terahertz Waves, Rome, Italy, 5–10 September 2010. [Google Scholar]

- Waters, J.W.; Froidevaux, L.; Harwood, R.S.; Jarnot, R.F.; Pickett, H.M.; Read, W.G.; Siegel, P.H.; Cofield, R.E.; Filipiak, M.J.; Holden, J.R.; et al. The earth observing system microwave limb sounder (EOS MLS) on the aura satellite. IEEE Trans. Geosci. Remote Sens. 2006, 44, 1075–1092. [Google Scholar] [CrossRef]

- Moyna, B.P.; Charlton, J.E.; Lee, C.; Parker, R.J.; Oldfield, M.M.; Matheson, D.N.; Peter, M.; Kangas, V. Design of a sub-millimetre wave airborne demonstrator for observations of precipitation and ice clouds. In Proceedings of the Antennas and Propagation Society International Symposium, Charleston, SC, USA, 1–5 June 2009. [Google Scholar]

- Mehdi, I.; Siles, J.V.; Lee, C.; Schlecht, E. THz diode technology: Status, prospects, and applications. Proc. IEEE 2017, 990–1007. [Google Scholar] [CrossRef]

- Chattopadhyay, G.; Schlecht, E.; Ward, J.S.; Gill, J.J.; Javadi, H.H.; Maiwald, F.; Mehdi, I. An All-Solid-State Broad-Band Frequency Multiplier Chain at 1500 GHz. IEEE Trans. Microw. Theory Tech. 2004, 52, 1538–1547. [Google Scholar] [CrossRef]

- Alijabbari, N.; Bauwens, M.F.; Weikle, R.M. 160 GHz Balanced Frequency Quadruplers Based on Quasi-Vertical Schottky Varactors Integrated on Micromachined Silicon. IEEE Trans. Terahertz Sci. Technol. 2014, 4, 678–685. [Google Scholar] [CrossRef]

- Mehdi, I.; Holland, W.S.; Zmuidzinas, J.; Thomas, B.; Lin, R.; Maestrini, A.; John, W.; Erich, S.; John, G.; Choonsup, L.; et al. High-power local oscillator sources for 1–2 THz. Int. Soc. Opt. Photonics 2010, 7741, 774112. [Google Scholar] [CrossRef]

- Zhang, B.; Ji, D.; Min, Y.; Fan, Y.; Chen, X. A High-Efficiency 220GHz Doubler Based on the Planar Schottky Varactor Diode. J. Electron. Mater. 2019, 48, 3603–3611. [Google Scholar] [CrossRef] [Green Version]

- Yao, C.; Wei, X.; Luo, Y.; Zhou, M. A 210 GHz power-combined frequency multiplying source with output power of 23.8 mW. Frequenz 2017, 71, 523–530. [Google Scholar] [CrossRef]

- Zhang, Y.; Lu, Q.-Q.; Liu, W.; Li, L.; Xu, R.-M. Design of a 220 GHz frequency tripler based on EM model of Schottky diodes. J. Infrared Millim. Waves 2014, 33, 405–411. [Google Scholar] [CrossRef]

- Burckhardt C, B. Analysis of Varactor Frequency Multipliers for Arbitrary Capacitance Variation and Drive Level. Bell Labs Tech. J. 2013, 44, 675–692. [Google Scholar] [CrossRef]

- Jiang, J.; Liu, J.; Shi, X.Y.; Bin, L.U.; Deng, X.J.; Hao, H.L.; Zhang, J. 340 GHz frequency one stage quadrupler based on schottky varactors and csmrs filter. J. Infrared Millim. Waves 2017, 36, 214–219. [Google Scholar] [CrossRef]

- David, M. Pozar: Microwave Engineering, 3rd ed.; John Wiley & Sons, Inc.: Hoboken, NJ, USA, 2011; pp. 219–223. ISBN 978-0-471-44878-5. [Google Scholar]

- Klopfenstein, R.W. A Transmission Line Taper of Improved Design. Proc. IRE 2007, 44, 31–35. [Google Scholar] [CrossRef]

- Collin R, E. The Optimum Tapered Transmission Line Matching Section. Proc. IRE 1956, 44, 539–548. [Google Scholar] [CrossRef]

- Vadiodes. Available online: http://www.vadiodes.com (accessed on 21 August 2019).

- Maestrini, A.; Tripon-Canseliet, C.; Ward, J.S.; Gill, J.J.; Mehdi, I. A High Efficiency Multiple-Anode 260–340 GHz Frequency Tripler. In Proceedings of the Seventeenth International Symposium on Space Terahertz Technology, Paris, France, 10–12 May 2006. [Google Scholar]

- Liu, H.; Powell, J.; Viegas, C.; Cairns, A.A.; Alderman, B. A 332 GHz frequency doubler using flip-chip mounted planar Schottky diodes. In Proceedings of the 2015 Asia-Pacific Microwave Conference (APMC), Nanjing, China, 6–9 December 2015. [Google Scholar]

- Xiao, Z. Research on 330 GHz Multiplier Based on Planar Schottky Diode; University of Electronic Science and Technology of China: Chengdu, China, 2017. [Google Scholar]

| References | Diode Style | Multiply Factor | Frequency | Input Power | Peak Output Power | FBW |

|---|---|---|---|---|---|---|

| [14] from CAEP (China Academy of Engineering Physics) | Discrete | 4 | 332–345 GHz | 200 | 4 mW at 339 GHz | 335–344 GHz |

| [18] from VDI | Integrated | 2 | 220–330 GHz | 20–50 | 3 mW | - |

| [19] from JPL | Integrated | 3 | 260–340 GHz | 100 | 7.5 mW at 325 GHz | 290–330 GHz |

| [20] from RAL | Discrete | 2 | 329–338 GHz | 25 | 1.2 mW at 332.8 GHz | 329–337 GHz |

| [21] from UESTC (University of Electronic Science and Technology of China) | Discrete | 3 | 320–342 GHz | 10–42 | 0.149 mW at 326.5 GHz | 320–335 GHz |

| This paper | Discrete | 4 | 321–344 GHz | 200 | 4.75 mW at 333 GHz | 324–339 GHz |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Li, Y.; Zhang, D.; Meng, J.; Zhu, H.; Liu, S. The Design of Terahertz Frequency Quadruplers Based on Discrete Schottky Diodes. Micromachines 2022, 13, 69. https://doi.org/10.3390/mi13010069

Li Y, Zhang D, Meng J, Zhu H, Liu S. The Design of Terahertz Frequency Quadruplers Based on Discrete Schottky Diodes. Micromachines. 2022; 13(1):69. https://doi.org/10.3390/mi13010069

Chicago/Turabian StyleLi, Yuhang, Dehai Zhang, Jin Meng, Haotian Zhu, and Siyu Liu. 2022. "The Design of Terahertz Frequency Quadruplers Based on Discrete Schottky Diodes" Micromachines 13, no. 1: 69. https://doi.org/10.3390/mi13010069

APA StyleLi, Y., Zhang, D., Meng, J., Zhu, H., & Liu, S. (2022). The Design of Terahertz Frequency Quadruplers Based on Discrete Schottky Diodes. Micromachines, 13(1), 69. https://doi.org/10.3390/mi13010069