Gateless and Capacitorless Germanium Biristor with a Vertical Pillar Structure

Abstract

:1. Introduction

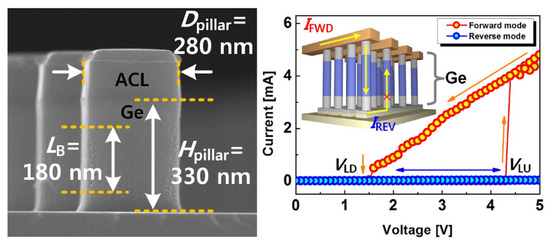

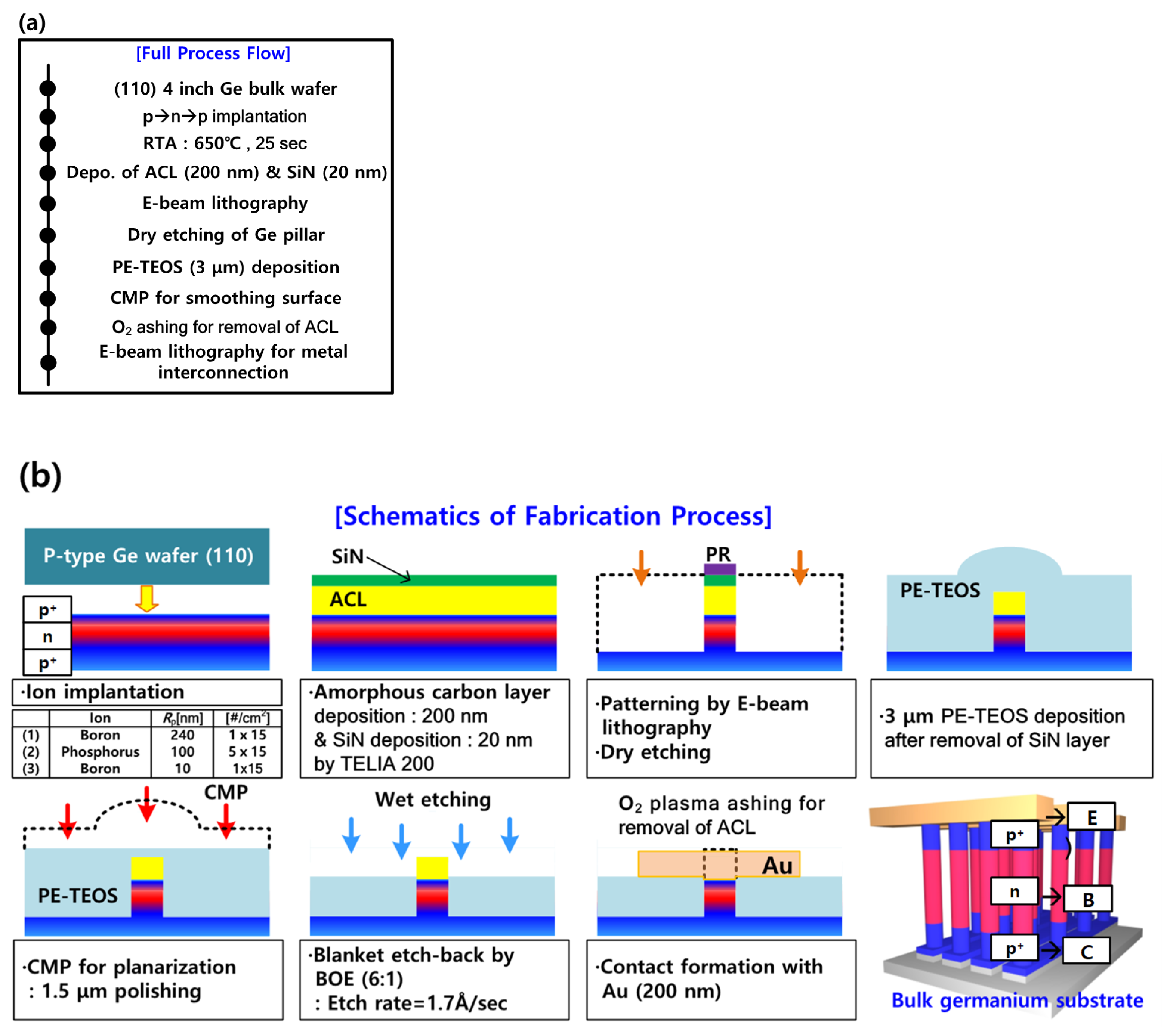

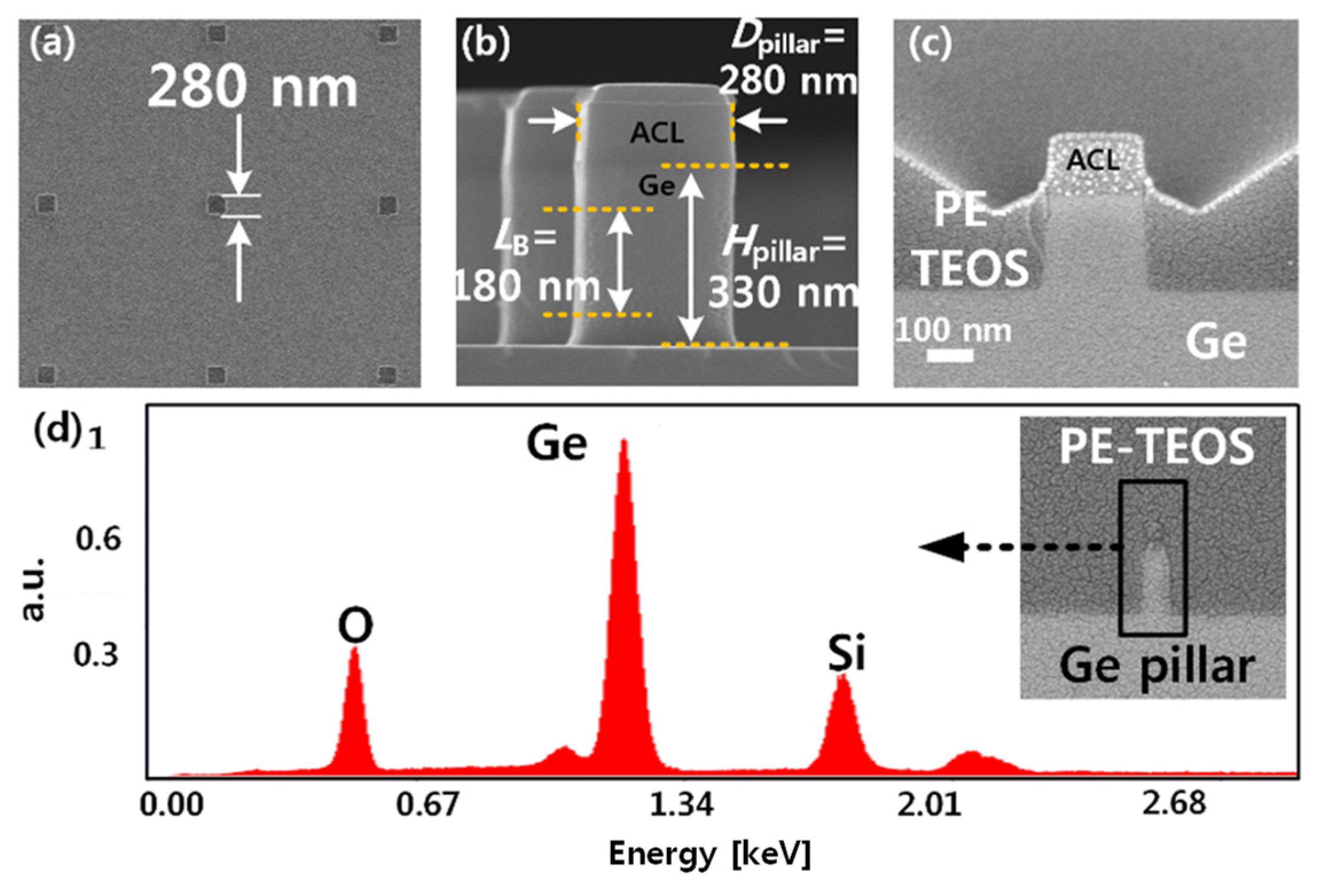

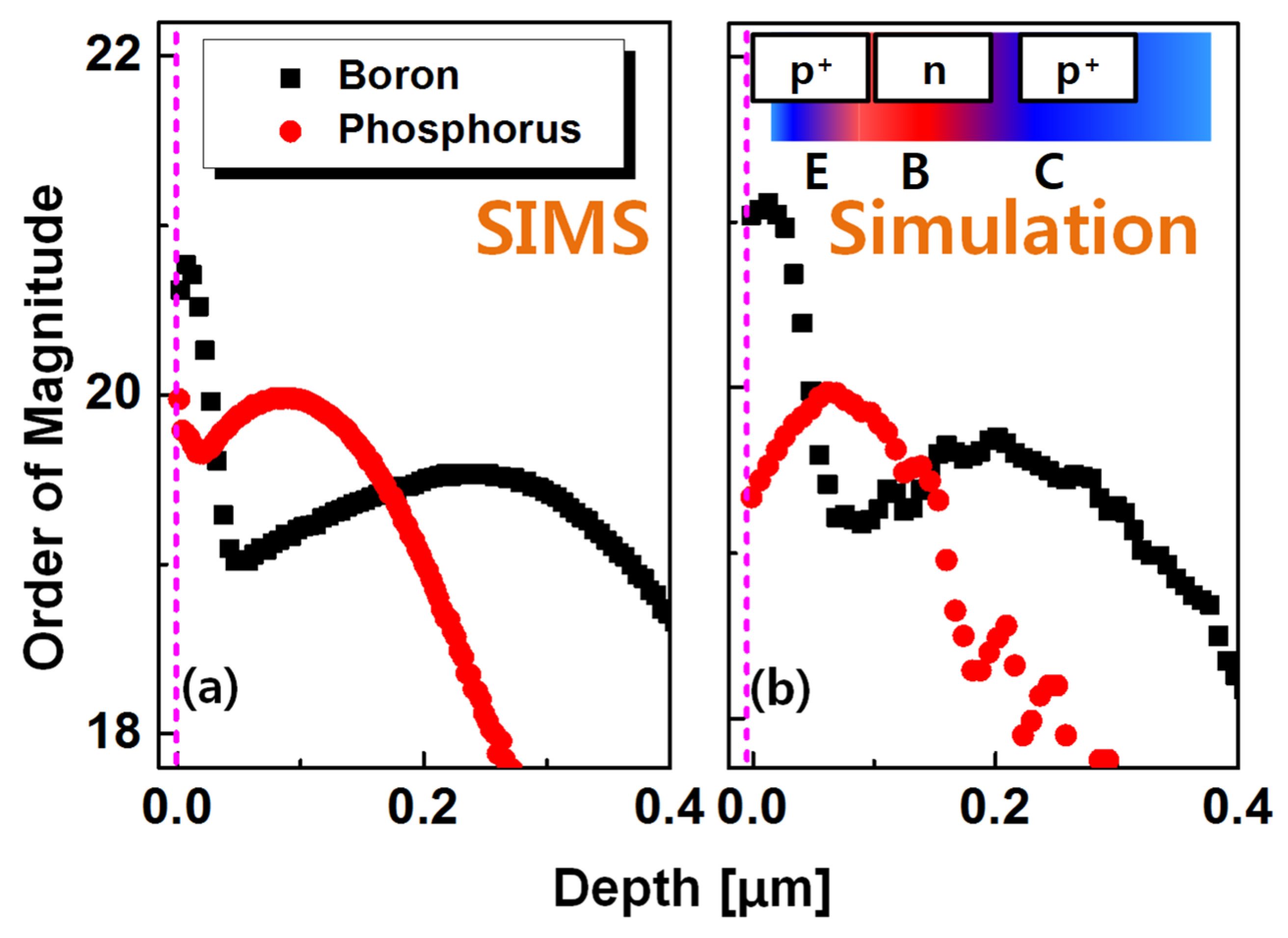

2. Device Fabrication

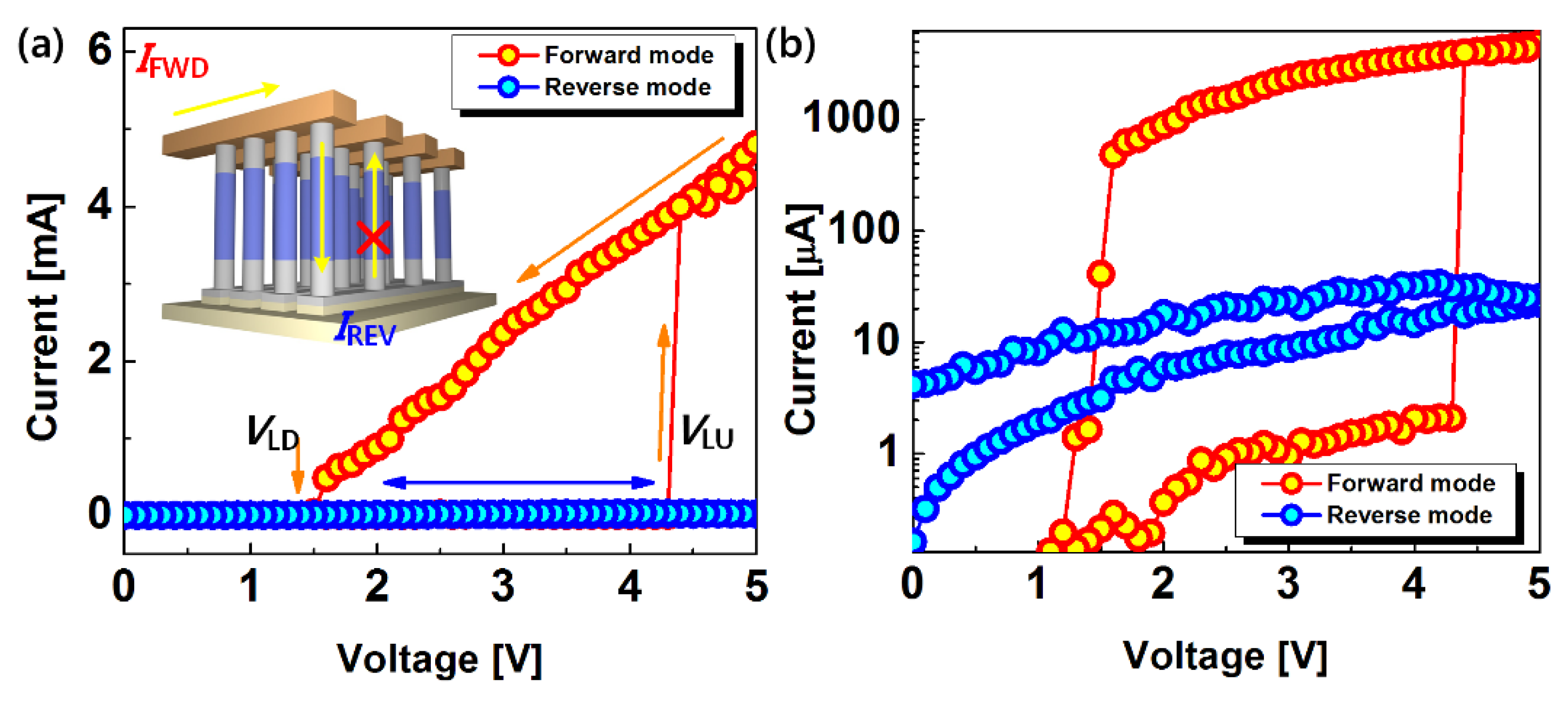

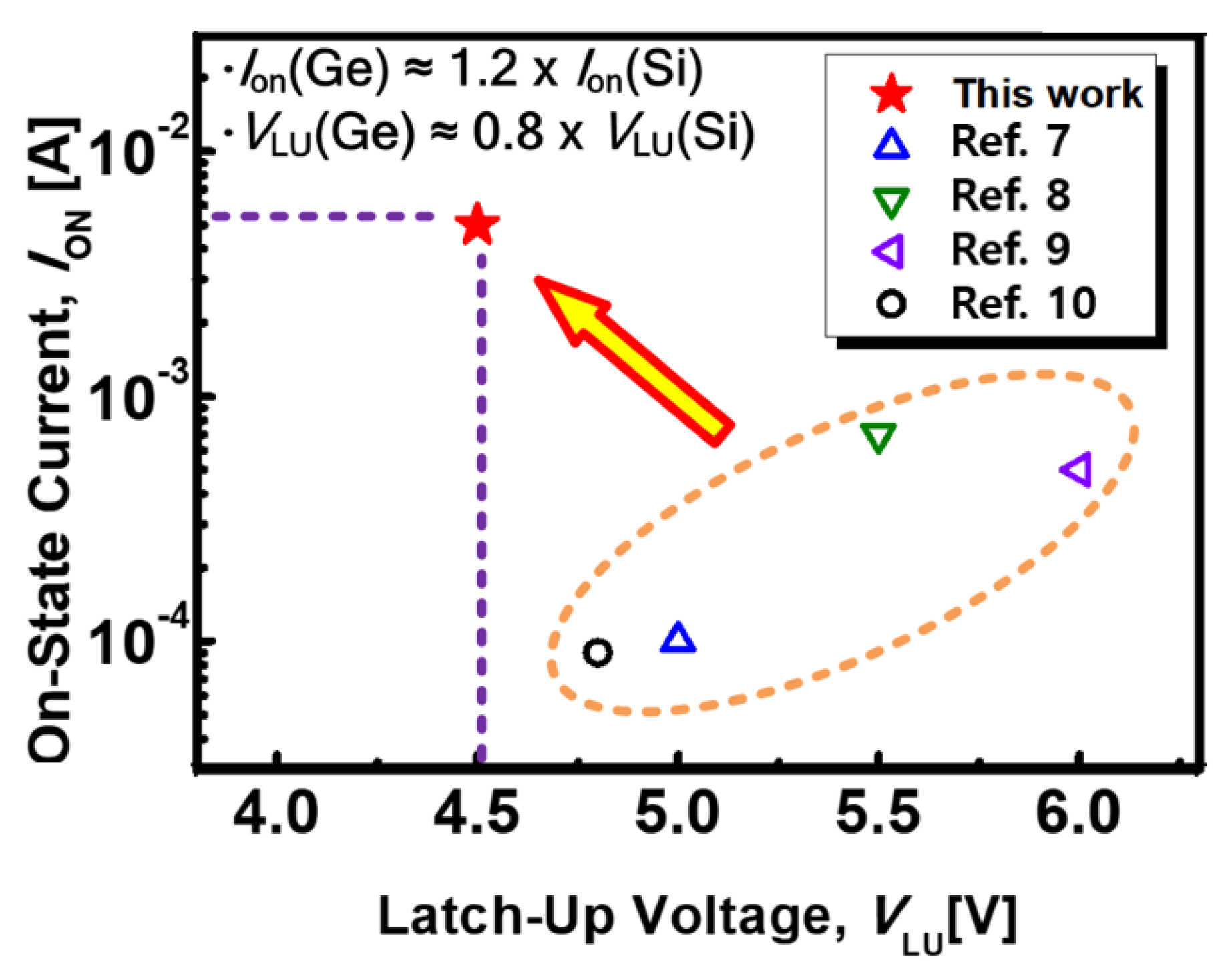

3. Experimental Results and Discussion

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Yamamichi, S.; Yamaichi, A.; Park, D.; Hu, C. Impact of time dependent dielectric breakdown and stress induced leakage current on the reliability of (Ba,Sr)TiO/sub 3/ thin film capacitors for Gbit-scale DRAMs. Mater. Sci. 1999, 46, 342–347. [Google Scholar] [CrossRef]

- Tanaka, T.; Yoshida, E.; Miyashita, T. Scalability Study on a Capacitorless 1T-DRAM: From Single-Gate PD-SOI to Double-Gate DinDRAM. In Proceedings of the IEDM, San Francisco, CA, USA, 13–15 December 2004. [Google Scholar]

- Hofmann, K.; Holzbauser, S.; Kuo, C. A comprehensive analysis of NFET degradation due to off-state stress. In Proceedings of the IEEE International Integrated Reliability Workshop Final Report, South Lake Tahoe, CA, USA, 18–21 October 2004. [Google Scholar]

- Inoh, K.; Shino, T.; Yamada, H.; Nakajima, H.; Minami, Y.; Yamada, T.; Ohsawa, T.; Higashi, T.; Fujita, K.; Ikehashi, T.; et al. FBC (Floating Body Cell) for embedded DRAM on SOI. In Proceedings of the Symposium on VLSI Technology, Digest of Technical Papers (IEEE Cat. No.03CH37407), Kyoto, Japan, 10–12 June 2003. [Google Scholar]

- Reisch, M. On bistable behavior and open-base breakdown of bipolar transistors in the avalanche regime-modeling and applications. IEEE Trans. Electron Devices 1992, 39, 1398–1409. [Google Scholar] [CrossRef]

- Ban, I.; Avci, U.E.; Kencke, D.L.; Chang, P.L. A scaled floating body cell (FBC) memory with high-k + metal gate on thin-silicon and thin-BOX for 16-nm technology node and beyond. In Proceedings of the Symposia on VLSI Technology and Circuits, Honolulu, HI, USA, 17–20 June 2008. [Google Scholar]

- Han, J.-W.; Choi, Y.-K. Bistable resistor (biristor)–gateless silicon nanowire memory. In Proceedings of the 2010 Symposia on VLSI Technology and Circuits, Honolulu, HI, USA, 15–18 June 2010. [Google Scholar]

- Han, J.-W.; Choi, Y.-K. Biristor—Bistable Resistor Based on a Silicon Nanowire. IEEE Electron Device Lett. 2010, 31, 797–799. [Google Scholar] [CrossRef]

- Moon, D.-I.; Choi, S.-J.; Kim, J.-Y.; Ko, S.-W.; Kim, M.-S.; Oh, J.-S.; Lee, G.-S.; Kang, M.-H.; Kim, Y.-S.; Kim, J.-W.; et al. Highly endurable floating body cell memory: Vertical biristor. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 10–13 December 2012. [Google Scholar]

- Moon, D.I.; Choi, S.J.; Kim, S.; Oh, J.S.; Kim, Y.S.; Choi, Y.K. Vertically Integrated Undirectional Biristor. IEEE Electron Device Lett. 2011, 32, 1483–1485. [Google Scholar] [CrossRef]

- Shin, J.S.; Bae, H.; Jang, J.; Yun, D.; Lee, J.; Hong, E.; Kim, D.H.; Kim, D.M. A Novel Double HBT-Based Capacitorless 1T DRAM Cell with Si/SiGe Heterojunctions. IEEE Electron Device Lett. 2011, 32, 850–852. [Google Scholar] [CrossRef]

- Pillarisetty, R.; Chu-Kang, B.; Corcoran, S.; Dewey, G.; Kavalieros, J.; Kennel, H.; Kotlyar, R.; Le, V.; Lionberger, D.; Metz, M.; et al. High Mobility Strained Germanium Quantum Well Field Effect Transistor as the P-Channel Device Option for Low Power (VCC = 0.5V) III-V CMOS Architecture. In Proceedings of the IEDM, San Francisco, CA, USA, 6–8 December 2010. [Google Scholar]

- Moon, J.-B.; Moon, D.-I.; Choi, Y.-K. A Bandgap-Engineered Silicon-Germanium Biristor for Low-Voltage Operation. IEEE Trans. Electron Devices 2013, 61, 2–7. [Google Scholar] [CrossRef]

- Kumar, M.J.; Maheedhar, M.; Varma, P.P. A Silicon Biristor With Reduced Operating Voltage: Proposal and Analysis. IEEE J. Electron Devices Soc. 2014, 3, 67–72. [Google Scholar] [CrossRef]

- Lee, S.; Shin, J.S.; Jang, J.; Bae, H.; Yun, D.; Lee, J.; Kim, D.H.; Kim, D.M. A Novel Capacitorless DRAM Cell Using Superlattice Bandgap-Engineered (SBE) Structure With 30-nm Channel Length. IEEE Trans. Nanotechnol. 2010, 10, 1023–1030. [Google Scholar] [CrossRef]

- Toh, E.-H.; Wang, G.H.; Chan, L.; Lo, G.-Q.; Samudra, G.; Yeo, Y.-C. I-MOS Transistor with an Elevated Silicon–Germanium Impact-Ionization Region for Bandgap Engineering. IEEE Electron Device Lett. 2006, 27, 975–977. [Google Scholar] [CrossRef]

- Han, J.-W.; Ryu, S.-W.; Kim, S.; Kim, C.-J.; Ahn, J.-H.; Choi, S.-J.; Choi, K.J.; Cho, B.J.; Kim, J.S.; Kim, K.H.; et al. Energy band engineered unified-RAM (URAM) for multi-functioning 1T-DRAM and NVM. In Proceedings of the 2008 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2008. [Google Scholar]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Bae, H.; Lee, G.-B.; Hur, J.; Park, J.-Y.; Kim, D.-J.; Kim, M.-S.; Choi, Y.-K. Gateless and Capacitorless Germanium Biristor with a Vertical Pillar Structure. Micromachines 2021, 12, 899. https://doi.org/10.3390/mi12080899

Bae H, Lee G-B, Hur J, Park J-Y, Kim D-J, Kim M-S, Choi Y-K. Gateless and Capacitorless Germanium Biristor with a Vertical Pillar Structure. Micromachines. 2021; 12(8):899. https://doi.org/10.3390/mi12080899

Chicago/Turabian StyleBae, Hagyoul, Geon-Beom Lee, Jae Hur, Jun-Young Park, Da-Jin Kim, Myung-Su Kim, and Yang-Kyu Choi. 2021. "Gateless and Capacitorless Germanium Biristor with a Vertical Pillar Structure" Micromachines 12, no. 8: 899. https://doi.org/10.3390/mi12080899

APA StyleBae, H., Lee, G.-B., Hur, J., Park, J.-Y., Kim, D.-J., Kim, M.-S., & Choi, Y.-K. (2021). Gateless and Capacitorless Germanium Biristor with a Vertical Pillar Structure. Micromachines, 12(8), 899. https://doi.org/10.3390/mi12080899