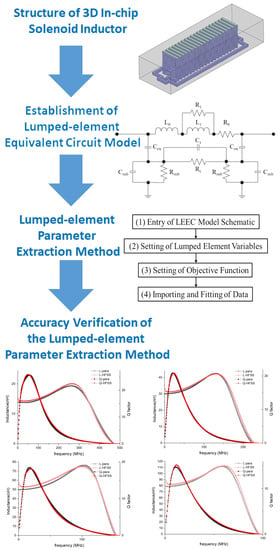

Broadband Lumped-Element Parameter Extraction Method of Two-Port 3D MEMS In-Chip Solenoid Inductors Based on a Physics-Based Equivalent Circuit Model

Abstract

1. Introduction

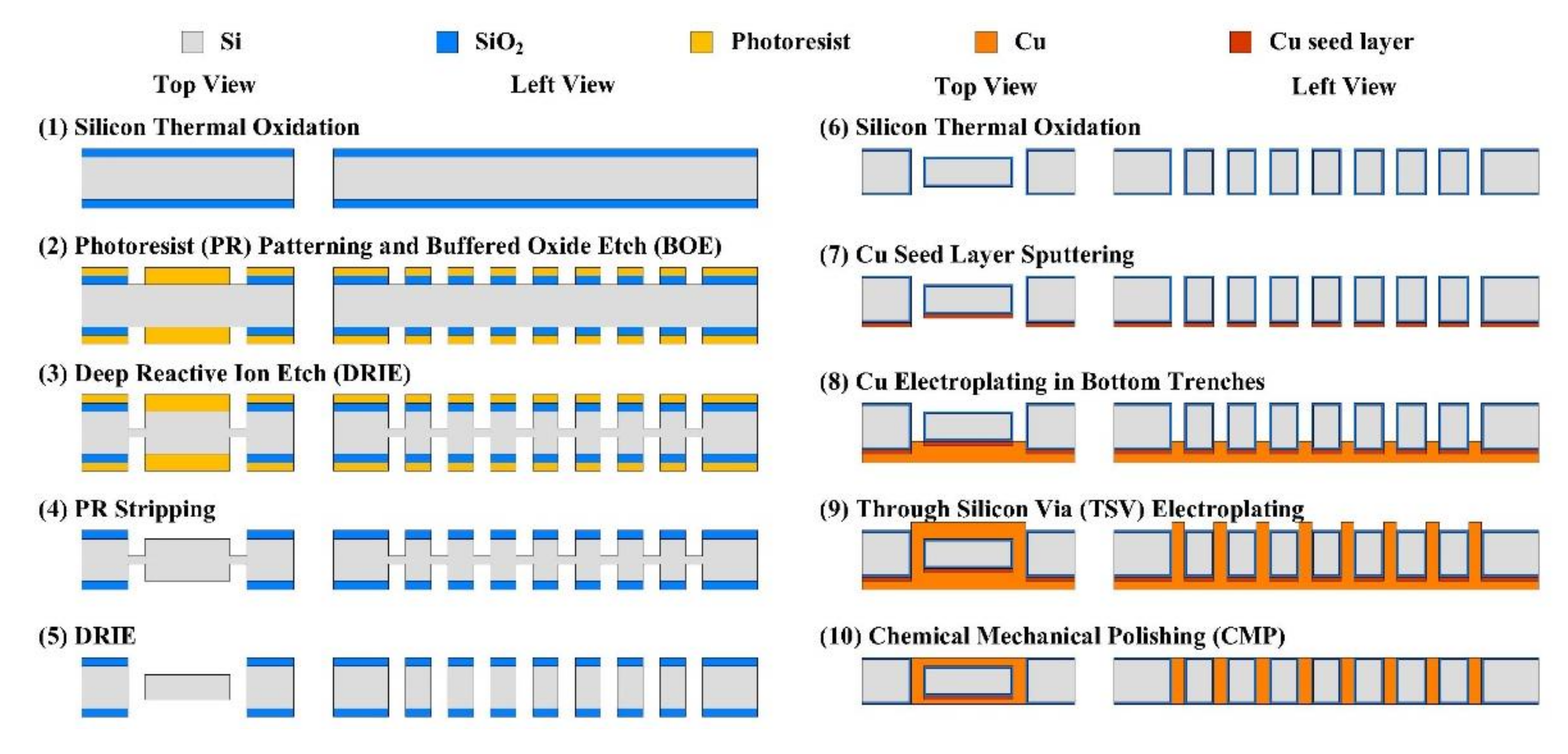

2. Construction of the Lumped-Element Equivalent Circuit Model

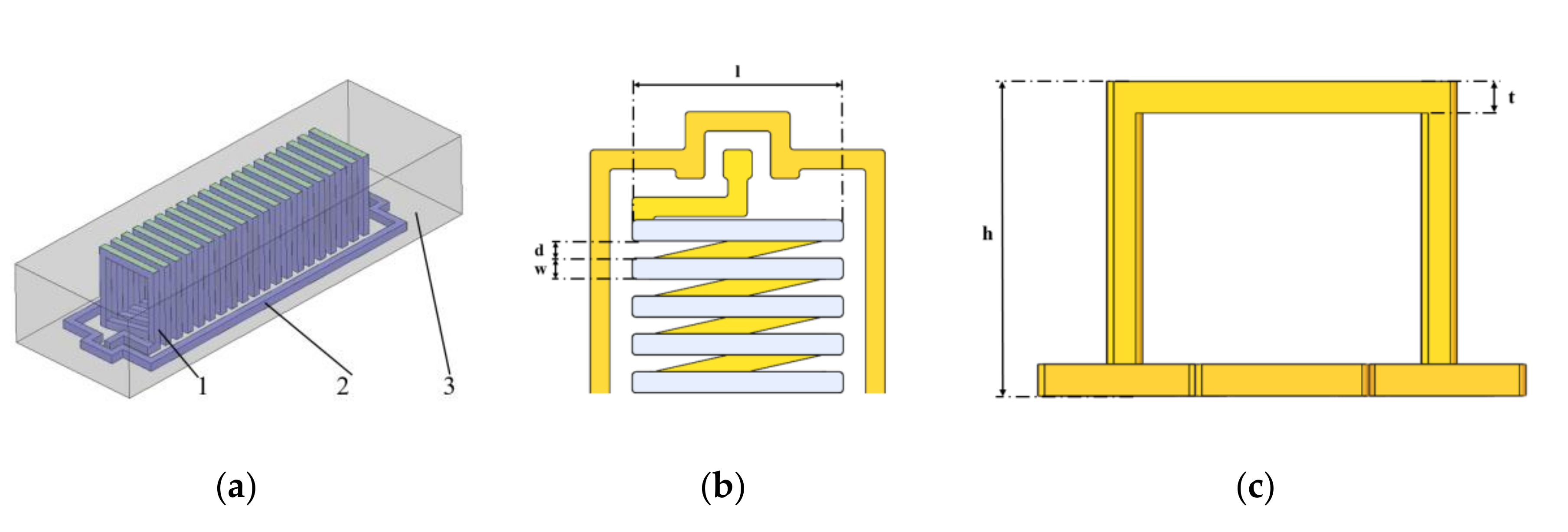

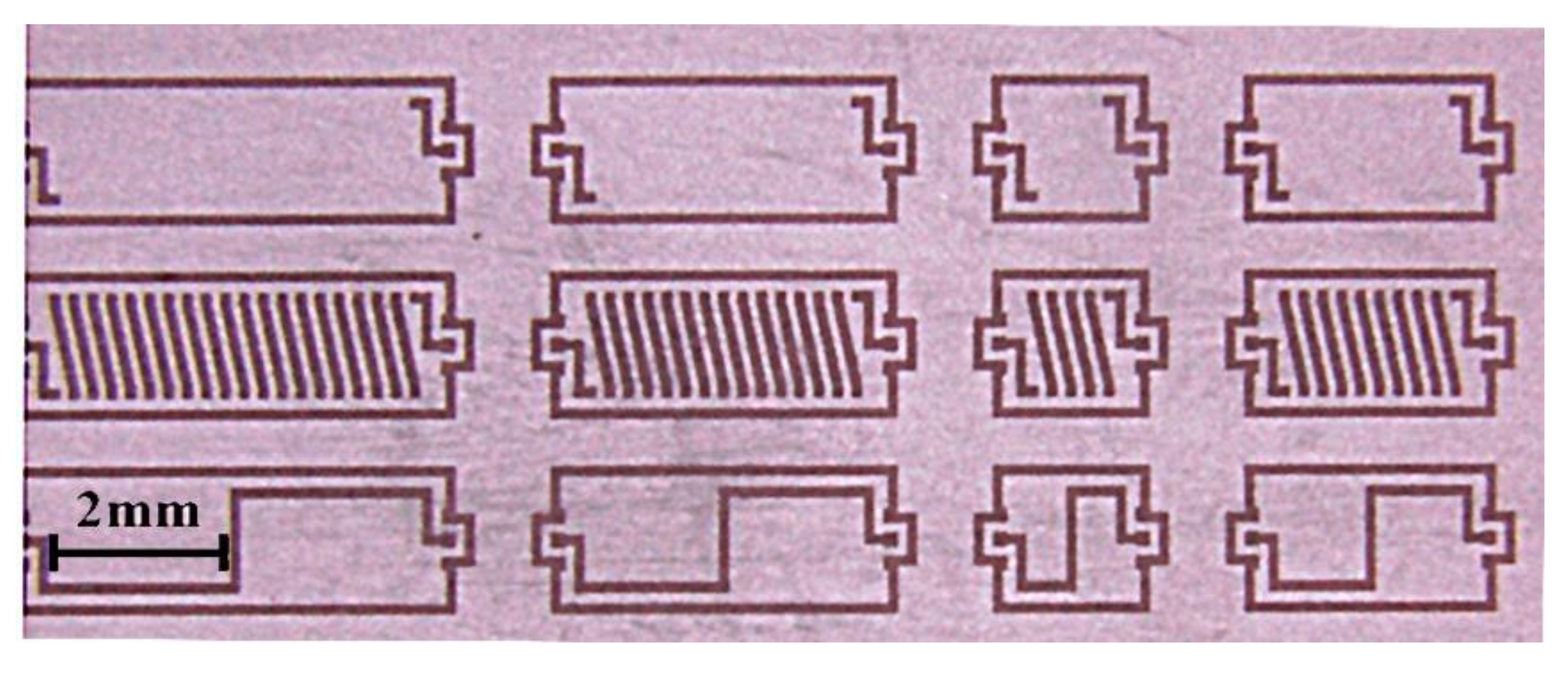

2.1. Description of Inductor Structure

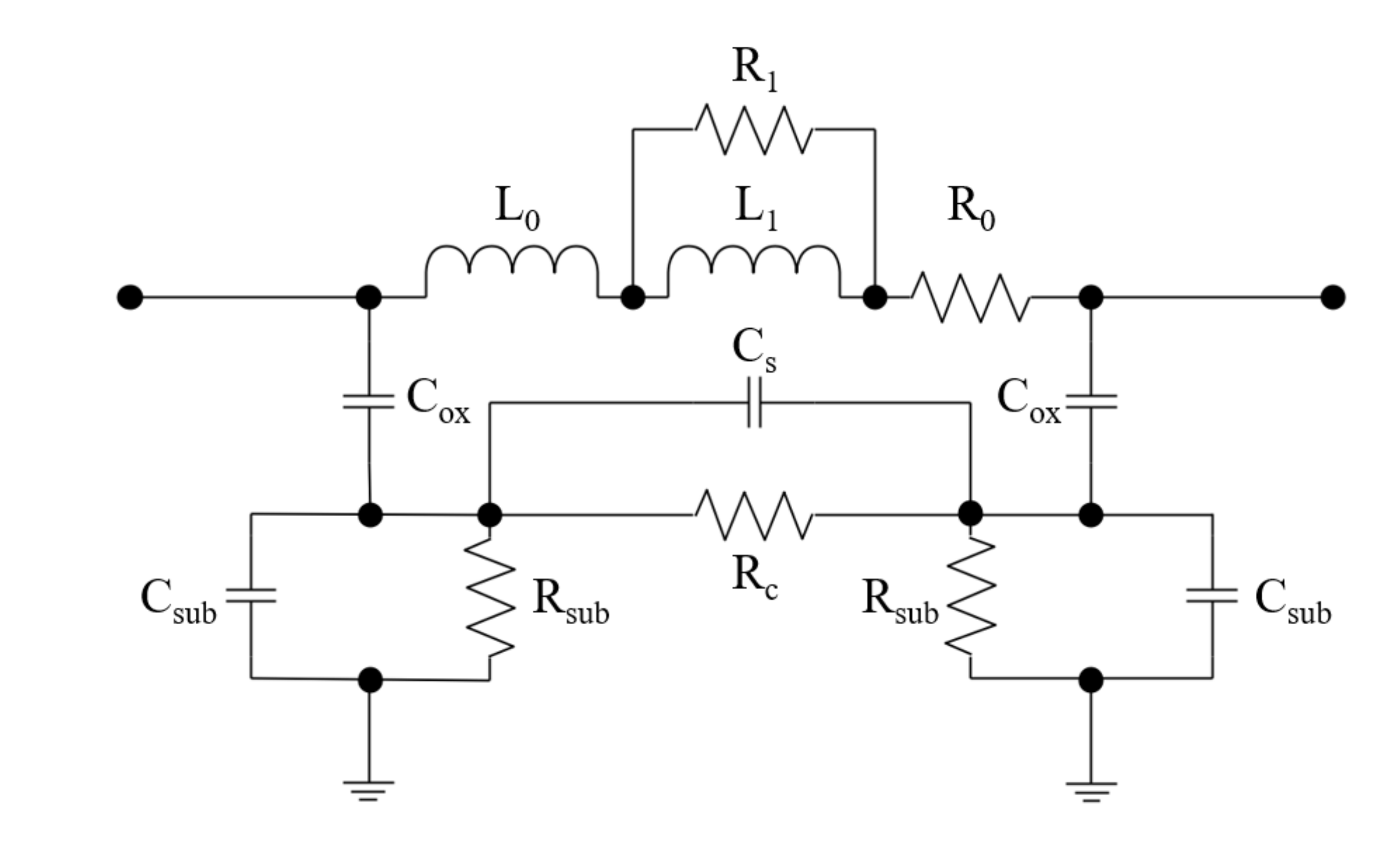

2.2. Classic Physics-Based LEEC Models

2.3. Physics-Based LEEC Models for In-Chip Solenoid Inductors

3. Lumped-Element Parameter Extraction Method

3.1. S-Parameter Dataset Acquisition Method

3.1.1. Testing Method

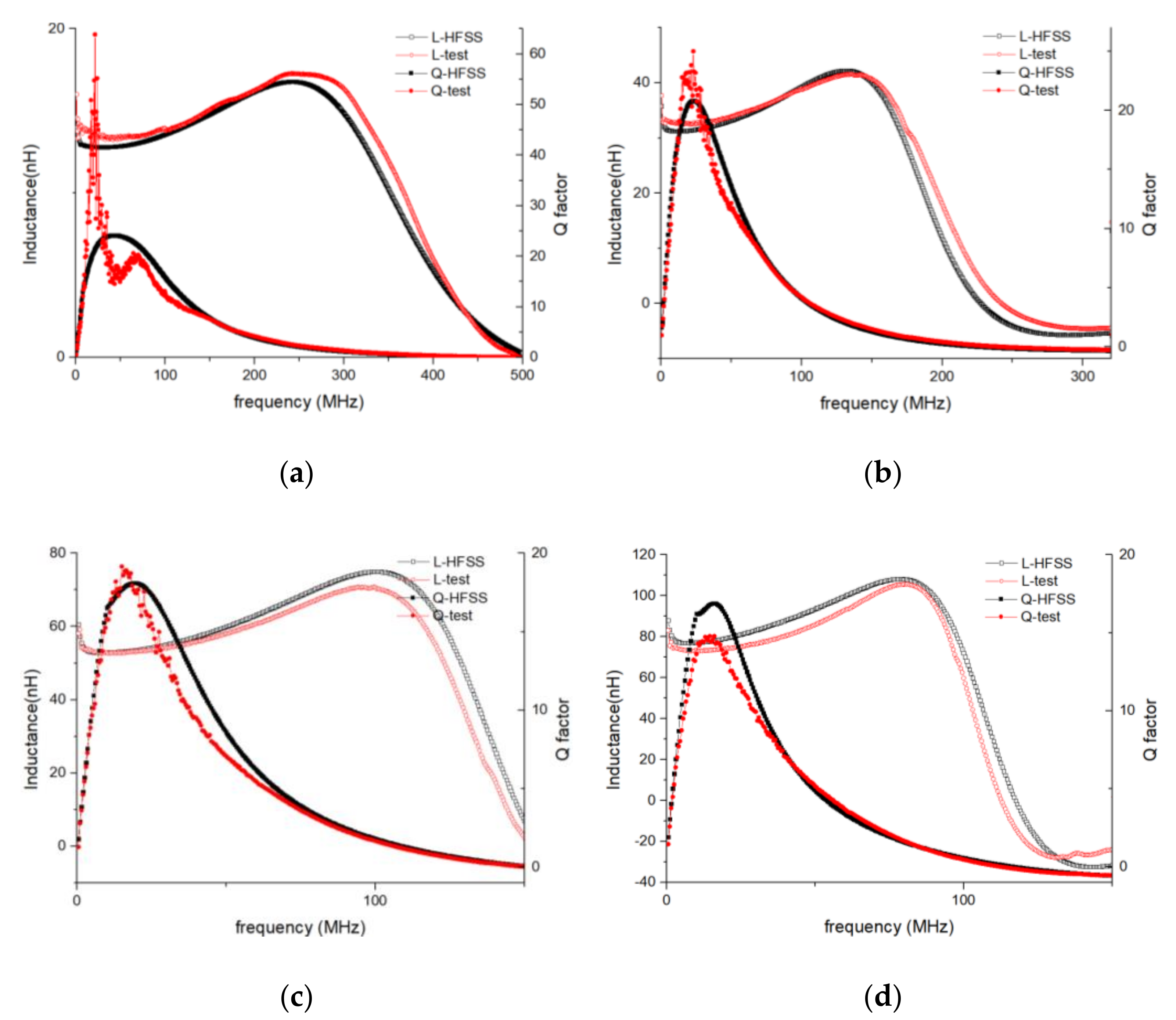

3.1.2. Accuracy Verification of EM Simulation Method

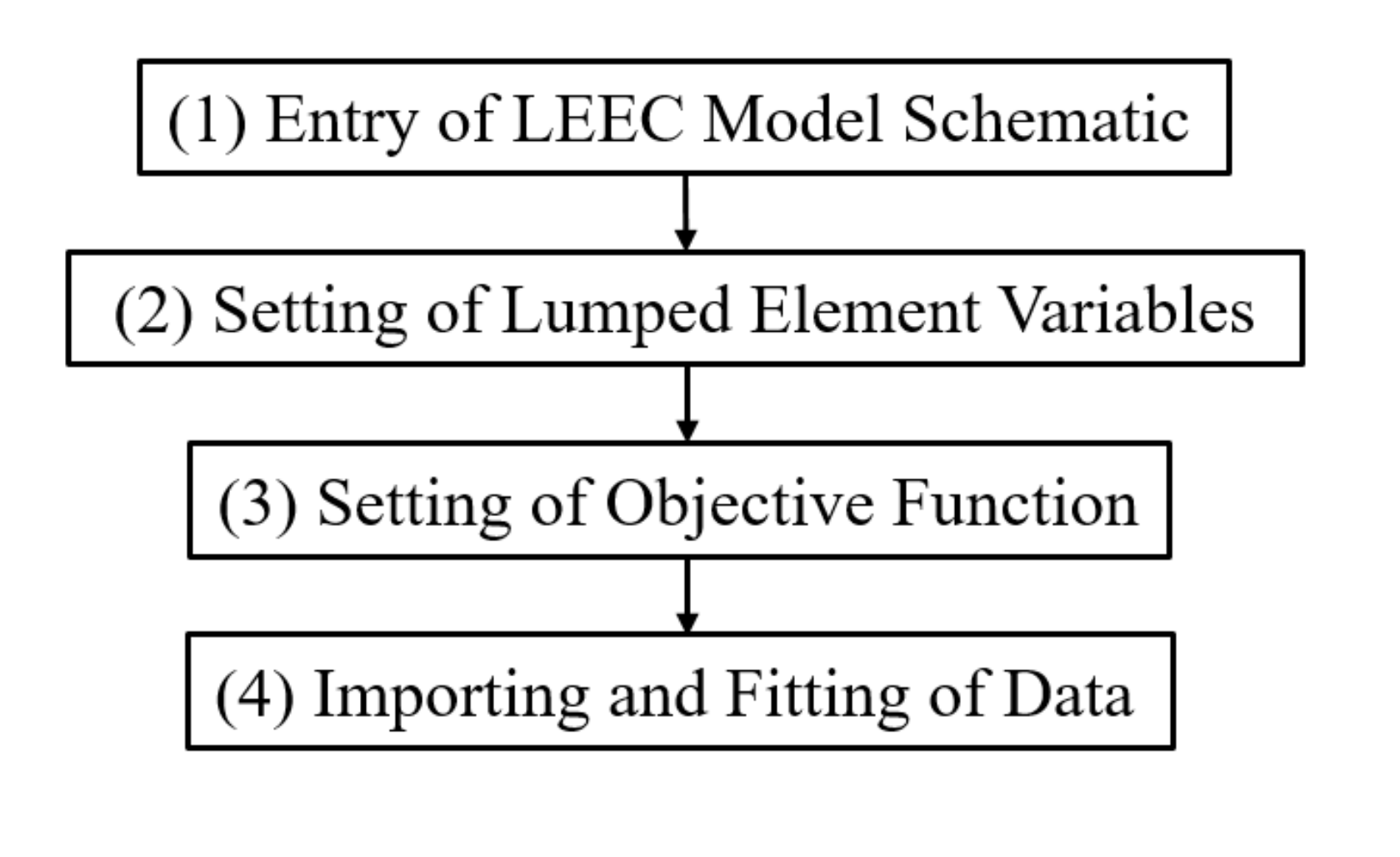

3.2. LEEC Model Fitting Method

4. Results and Discussion

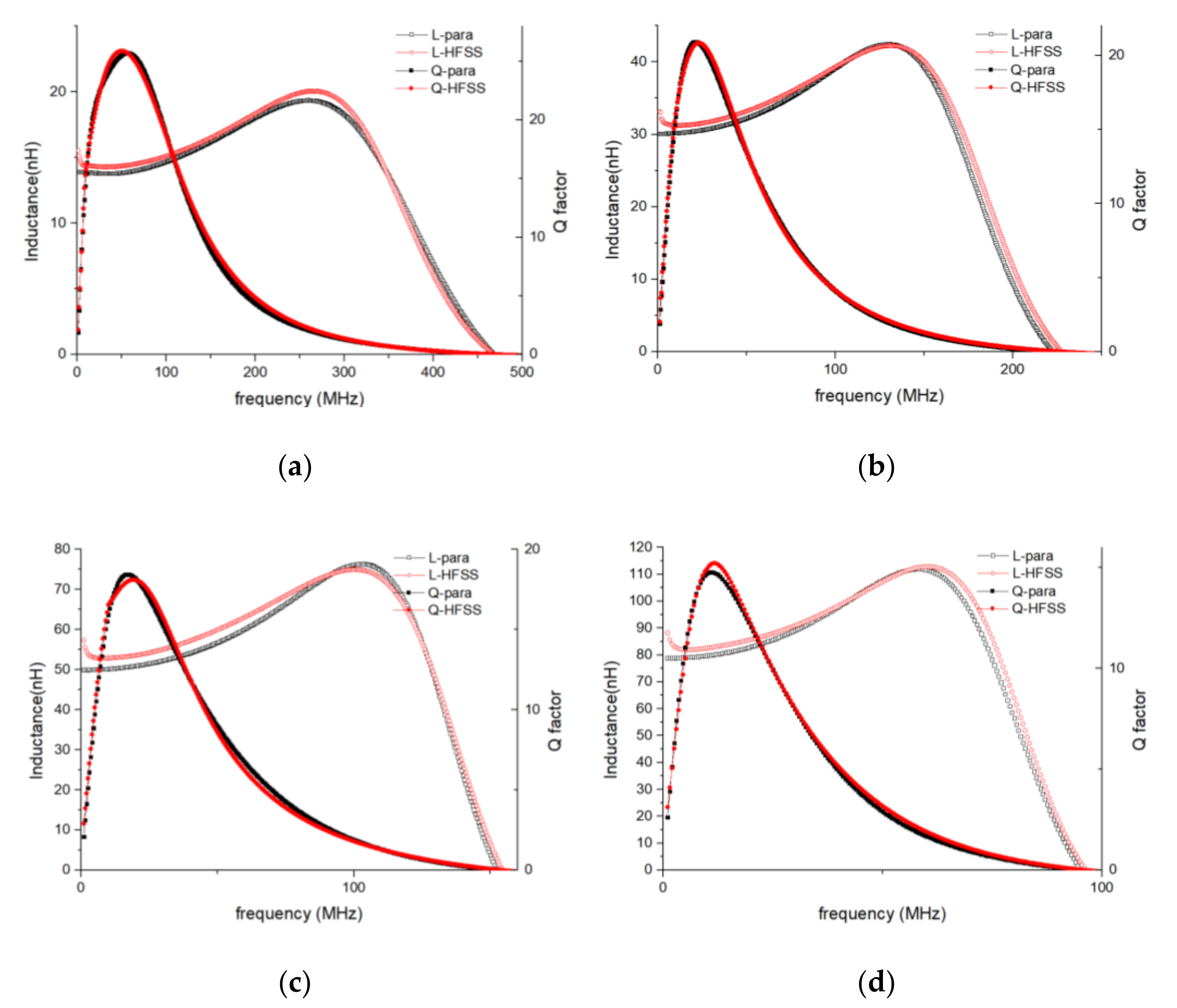

4.1. Lumped-Element Parameter Extraction Method Accuracy Verification

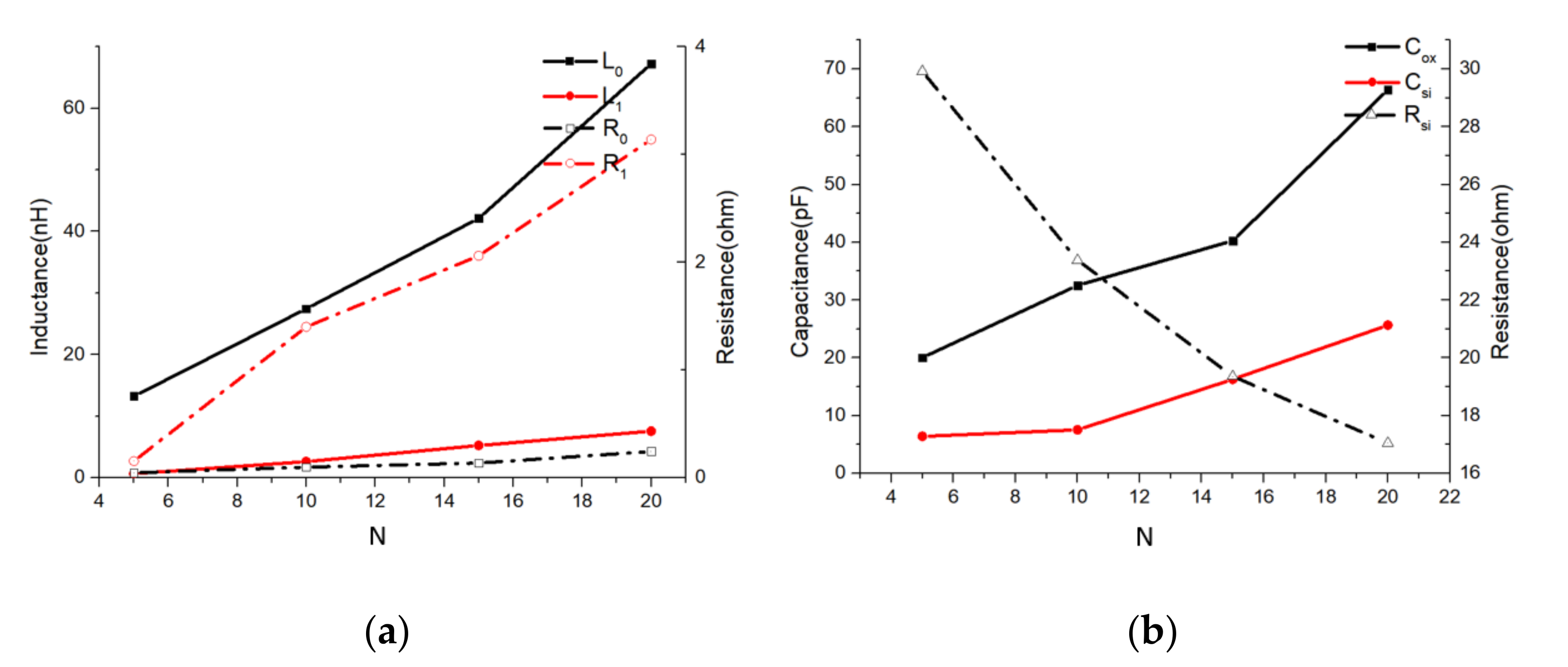

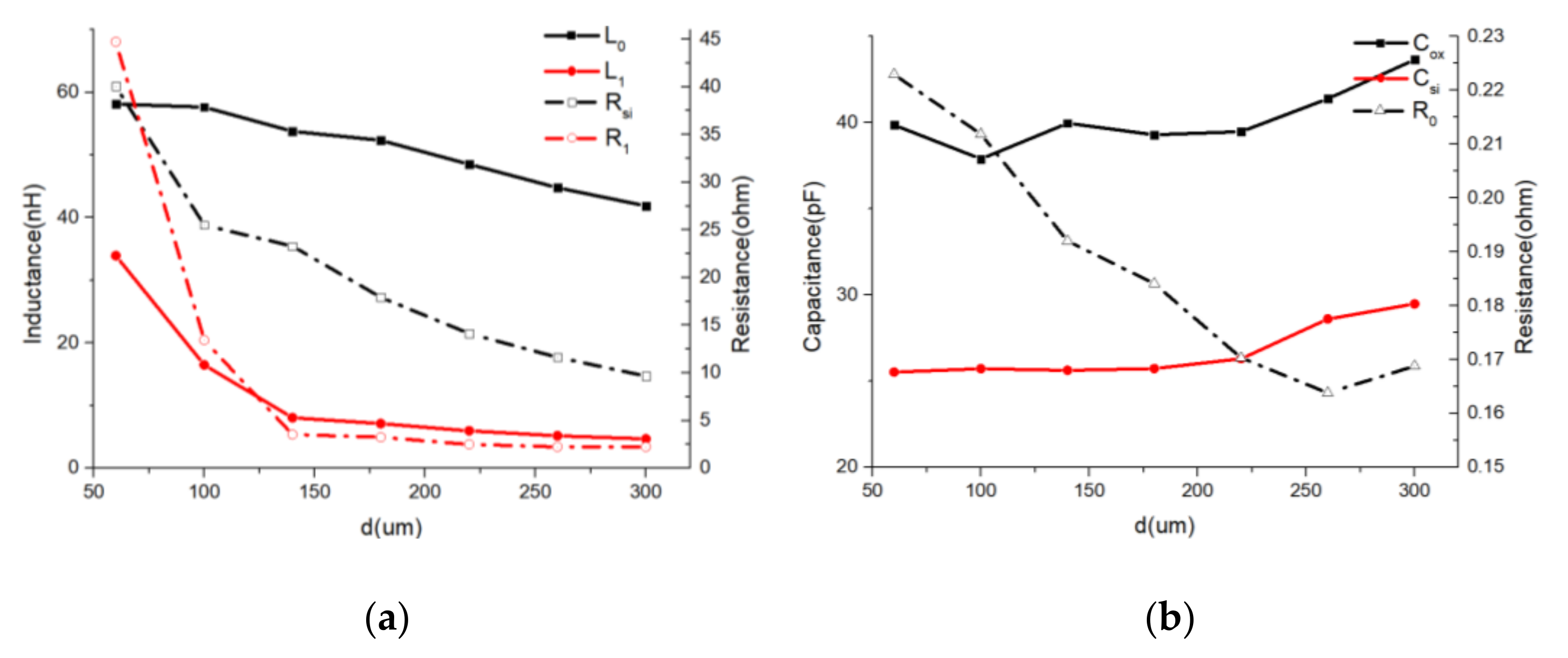

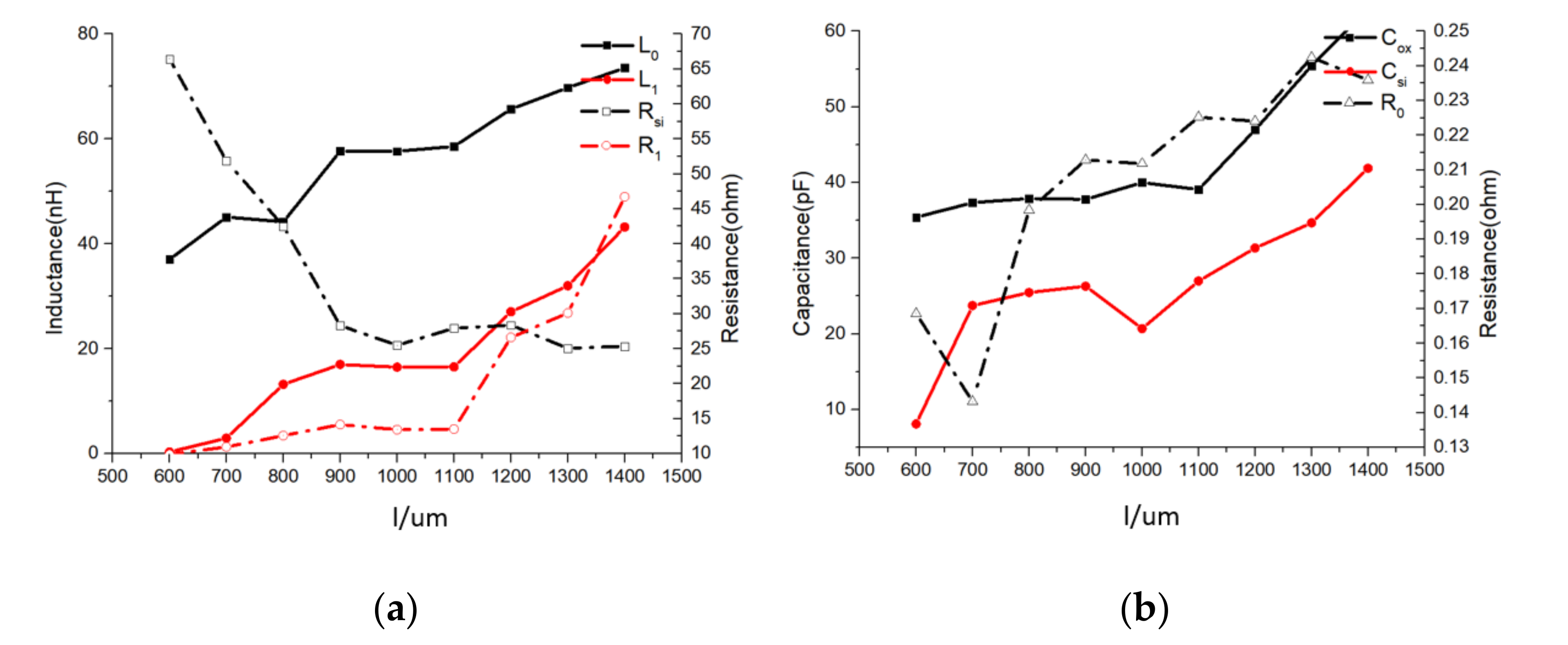

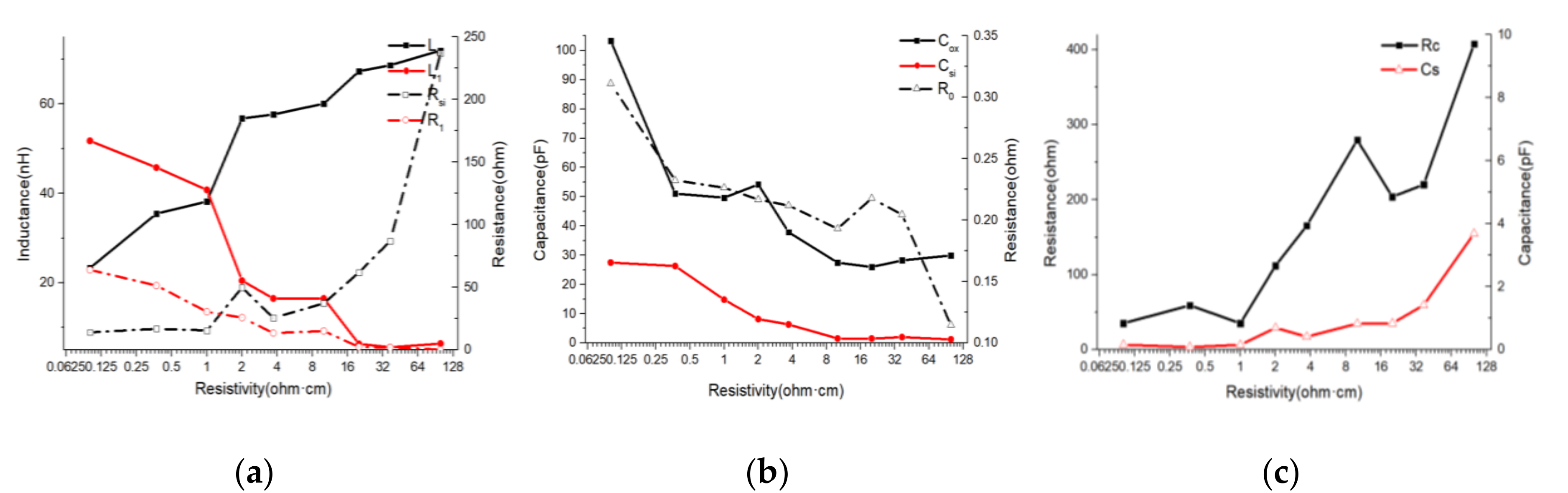

4.2. Influence of Inductor Geometry and Substrate Resistivity on Extracted Parameters

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Hikmat, O.F.; Ali, M.S.M. RF MEMS Inductors and Their Applications—A Review. J. Microelectromechanical Syst. 2017, 26, 17–44. [Google Scholar] [CrossRef]

- Coskun, M.B.; Thotahewa, K.; Ying, Y.S.; Yuce, M.; Neild, A.; Alan, T. Nanoscale Displacement Sensing Using Microfabricated Variable-Inductance Planar Coils. Appl. Phys. Lett. 2013, 103. [Google Scholar] [CrossRef]

- Bedair, S.S.; Pulskamp, J.S.; Meyer, C.D.; Mirabelli, M.; Polcawich, R.G.; Morgan, B. High-Performance Micromachined Inductors Tunable by Lead Zirconate Titanate Actuators. IEEE Electron Device Lett. 2012, 33, 1483–1485. [Google Scholar] [CrossRef]

- Moazenzadeh, A.; Suarez Sandoval, F.; Spengler, N.; Badilita, V.; Wallrabe, U. 3-D Microtransformers for DC-DC On-Chip Power Conversion. IEEE Trans. Power Electron. 2015, 30, 5088–5102. [Google Scholar] [CrossRef]

- Tao, Z.; Sun, J.; Li, H.; Huang, Y.; Li, H.; Xu, T.; Wu, H. A Radial-Flux Permanent Magnet Micromotor with 3D Solenoid Iron-Core MEMS In-Chip Coils of High Aspect Ratio. IEEE Electron Device Lett. 2020, 41, 1090–1093. [Google Scholar] [CrossRef]

- Zhi, T.; Hanxiao, W.; Haiwang, L.; Hanqing, L.; Tiantong, X.; Jiamian, S.; Wenbin, W. Theoretical Model and Analysis of an Electromagnetic Vibration Energy Harvester with Nonlinear Damping and Stiffness Based on 3D MEMS Coils. J. Phys. D Appl. Phys. 2020, in press. [Google Scholar] [CrossRef]

- Yoon, J.B.; Kim, B.K.; Han, C.H.; Yoon, E.; Kim, C.K. Surface Micromachined Solenoid On-Si and on-Glass Inductors for RF Applications. IEEE Electron Device Lett. 1999, 20, 487–489. [Google Scholar] [CrossRef]

- Lee, D.W.; Hwang, K.P.; Wang, S.X. Fabrication and Analysis of High-Performance Integrated Solenoid Inductor with Magnetic Core. IEEE Trans. Magn. 2008, 44 Pt 2, 4089–4095. [Google Scholar] [CrossRef]

- Yun, E.J.; Kim, J.W.; Han, Y.O.; Kim, H.C.; Jung, M.H.; Park, N.K. Development and Characteristics of Solenoid-Type SMD RF Chip Inductors. Curr. Appl. Phys. 2010, 10, 962–966. [Google Scholar] [CrossRef]

- Jensen, F.; Ouyang, Z.; Le, H.T.; Tang, P.T.; Mizushima, I.; Nour, Y.; Han, A.; Knott, A. Fabrication of 3D Air-Core MEMS Inductors for Very-High-Frequency Power Conversions. Microsystems Nanoeng. 2018, 4, 17082. [Google Scholar] [CrossRef]

- Zhou, S.; Xu, L.; Lu, J.; Yang, Y. Simulation and Optimization of High Performance On-Chip Solenoid MEMS Inductor. In Proceedings of the 2018 19th International Conference on Electronic Packaging Technology (ICEPT), Shanghai, China, 8–11 August 2018; pp. 710–715. [Google Scholar] [CrossRef]

- Yue, C.P.; Ryu, C.; Lau, J.; Lee, T.H.; Wong, S.S. Physical Model for Planar Spiral Inductors on Silicon. Tech. Dig.—Int. Electron Devices Meet. 1996, 155–158. [Google Scholar] [CrossRef]

- Melendy, D.; Francis, P.; Pichler, C.; Hwang, K.; Srinivasan, G.; Weisshaar, A. A New Wide-Band Compact Model for Spiral Inductors in RFICs. IEEE Electron Device Lett. 2002, 23, 273–275. [Google Scholar] [CrossRef]

- Ooi, B.L.; Xu, D.X.; Kooi, P.S.; Lin, F.J. An Improved Prediction of Series Resistance in Spiral Inductor Modeling with Eddy-Current Effect. IEEE Trans. Microw. Theory Tech. 2002, 50, 2202–2206. [Google Scholar] [CrossRef]

- Lim, S.F.; Yeo, K.S.; Ma, J.G.; Do, M.A.; Geng, C.Q.; Chew, K.W.; Chu, S.F. A Comprehensive Study and Modeling of Centre-Tap Differentially Driven Single-Turn Integrated Inductors for 10-GHz Applications. Microw. Opt. Technol. Lett. 2003, 38, 182–185. [Google Scholar] [CrossRef]

- Huszka, Z. 3-Port Characterization of Differential Inductors. In Proceedings of the 2004 Meeting Bipolar/BiCMOS Circuits and Technology, Montreal, QC, Canada, 12–14 September 2004; pp. 269–272. [Google Scholar] [CrossRef]

- Wei, J.; Wang, Z. Frequency-Independent T Equivalent Circuit for on-Chip Spiral Inductors. IEEE Electron Device Lett. 2010, 31, 933–935. [Google Scholar] [CrossRef]

- Yang, G.; Wang, Z.; Wang, K. Modified T-Model with an Improved Parameter Extraction Method for Silicon-Based Spiral Inductors. IEEE Microw. Wirel. Components Lett. 2014, 24, 817–819. [Google Scholar] [CrossRef]

- Lim, W.Y.; Arasu, M.A.; Raja, M.K. Modeling of Two Port Center-Tapped to Ground and Three Port Scalable Symmetrical Inductor. In Proceedings of the 2014 International Symposium on Integrated Circuits (ISIC), Singapore, 10–12 December 2014; pp. 540–543. [Google Scholar] [CrossRef]

- Issakov, V.; Member, S.; Kehl-waas, S.; Breun, S. Analytical Equivalent Circuit Extraction Procedure for Broadband Scalable Modeling of Three-Port. IEEE Trans. Circuits Syst. Regul. Pap. 2019, 66, 3557–3570. [Google Scholar] [CrossRef]

- Shin, D.; Oh, C.; Kim, K.; Yun, I. Characteristic Variation of 3-D Solenoid Embedded Inductors for Wireless Communication Systems. ETRI J. 2006, 28, 347–353. [Google Scholar] [CrossRef]

- Gao, X.Y.; Cao, Y.; Zhou, Y.; Ding, W.; Lei, C.; Chen, J.A. Fabrication of Solenoid-Type Inductor with Electroplated NiFe Magnetic Core. J. Magn. Magn. Mater. 2006, 305, 207–211. [Google Scholar] [CrossRef]

- Duplessis, M.; Tesson, O.; Neuilly, F.; Tenailleau, J.R.; Descamps, P. Physical Implementation of 3D Integrated Solenoids within Silicon Substrate for Hybrid IC Applications. In Proceedings of the European Microwave Conference (EuMC), Rome, Italy, 29 September–1 October 2009; pp. 1006–1009. [Google Scholar] [CrossRef]

- Chen, B.; Zhuo, C.; Shi, Y. A Physics-Aware Methodology for Equivalent Circuit Model Extraction of TSV-Inductors. Integration 2018, 63, 160–166. [Google Scholar] [CrossRef]

- Xu, T.; Sun, J.; Wu, H.; Li, H.; Li, H.; Tao, Z. 3D MEMS In-Chip Solenoid Inductor with High Inductance Density for Power MEMS Device. IEEE Electron Device Lett. 2019, 40, 1816–1819. [Google Scholar] [CrossRef]

- Massarini, A.; Kazimierczuk, M.K. Self-Capacitance of Inductors. IEEE Trans. Power Electron. 1997, 12, 671–676. [Google Scholar] [CrossRef]

- Patrick Yue, C.; Simon Wong, S. Physical Modeling of Spiral Inductors on Silicon. IEEE Trans. Electron Devices 2000, 47, 560–568. [Google Scholar] [CrossRef]

- Müller, J.E.; Ablassmeier, U.; Schelle, J.; Kellner, W.; Kniepkamp, H. Design of Planar Rectangular Microelectronic Inductors. Integr. Circuits Wirel. Commun. 1998, II, 581–584. [Google Scholar] [CrossRef]

- Jenei, S.; Nauwelaers, B.K.J.C.; Decoutere, S. Physics-Based Closed-Form Inductance Expression for Compact Modeling of Integrated Spiral Inductors. IEEE J. Solid-State Circuits 2002, 37, 77–80. [Google Scholar] [CrossRef]

- Fang, D.M.; Zhou, Y.; Jing, X.M.; Zhao, X.L.; Wang, X.N. Modeling, Optimization and Performance of High-Q MEMS Solenoid Inductors. Microsyst. Technol. 2008, 14, 185–191. [Google Scholar] [CrossRef]

| Symbol | Parameter | Value | Symbol | Parameter | Value |

|---|---|---|---|---|---|

| l | inductor width/μm | 1000 | d | spacing between adjacent turns/μm | 100 |

| w | linewidth of conductors/μm | 100 | h | height of the whole inductor/μm | 1000 |

| t | height of horizontal conductors/μm | 100 | N | inductor turns | 5/10/15/20 |

| s | oxide insulating layer thickness/μm | 1 | ρ | silicon resistivity/(Ω·cm) | 3.7 |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Sun, J.; Li, H.; Wu, S.; Xu, T.; Li, H.; Wu, H.; Xia, S. Broadband Lumped-Element Parameter Extraction Method of Two-Port 3D MEMS In-Chip Solenoid Inductors Based on a Physics-Based Equivalent Circuit Model. Micromachines 2020, 11, 836. https://doi.org/10.3390/mi11090836

Sun J, Li H, Wu S, Xu T, Li H, Wu H, Xia S. Broadband Lumped-Element Parameter Extraction Method of Two-Port 3D MEMS In-Chip Solenoid Inductors Based on a Physics-Based Equivalent Circuit Model. Micromachines. 2020; 11(9):836. https://doi.org/10.3390/mi11090836

Chicago/Turabian StyleSun, Jiamian, Haiwang Li, Sifan Wu, Tiantong Xu, Hanqing Li, Hanxiao Wu, and Shuangzhi Xia. 2020. "Broadband Lumped-Element Parameter Extraction Method of Two-Port 3D MEMS In-Chip Solenoid Inductors Based on a Physics-Based Equivalent Circuit Model" Micromachines 11, no. 9: 836. https://doi.org/10.3390/mi11090836

APA StyleSun, J., Li, H., Wu, S., Xu, T., Li, H., Wu, H., & Xia, S. (2020). Broadband Lumped-Element Parameter Extraction Method of Two-Port 3D MEMS In-Chip Solenoid Inductors Based on a Physics-Based Equivalent Circuit Model. Micromachines, 11(9), 836. https://doi.org/10.3390/mi11090836