Improving the Recognition Accuracy of Memristive Neural Networks via Homogenized Analog Type Conductance Quantization

Abstract

1. Introduction

2. Materials and Methods

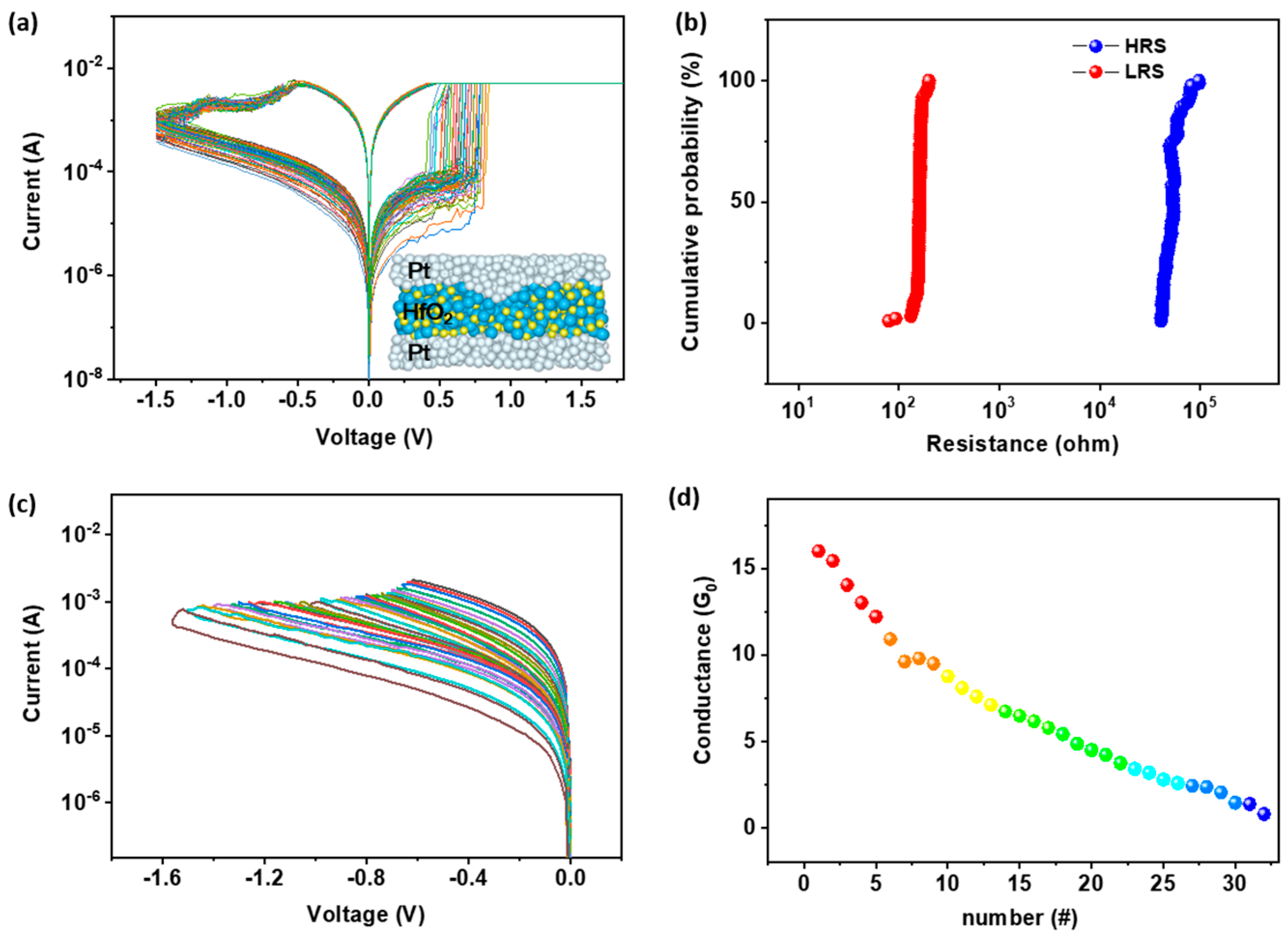

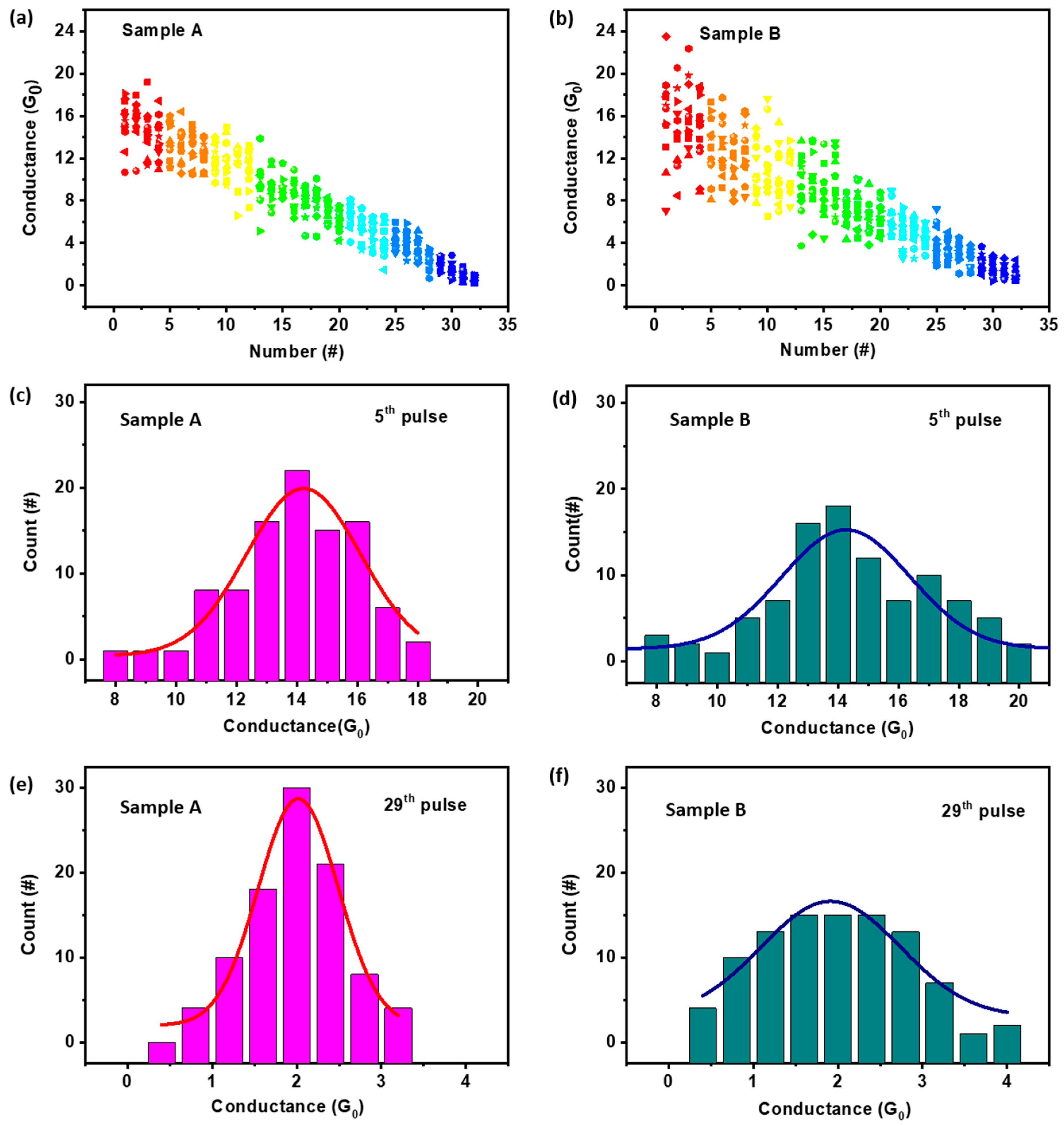

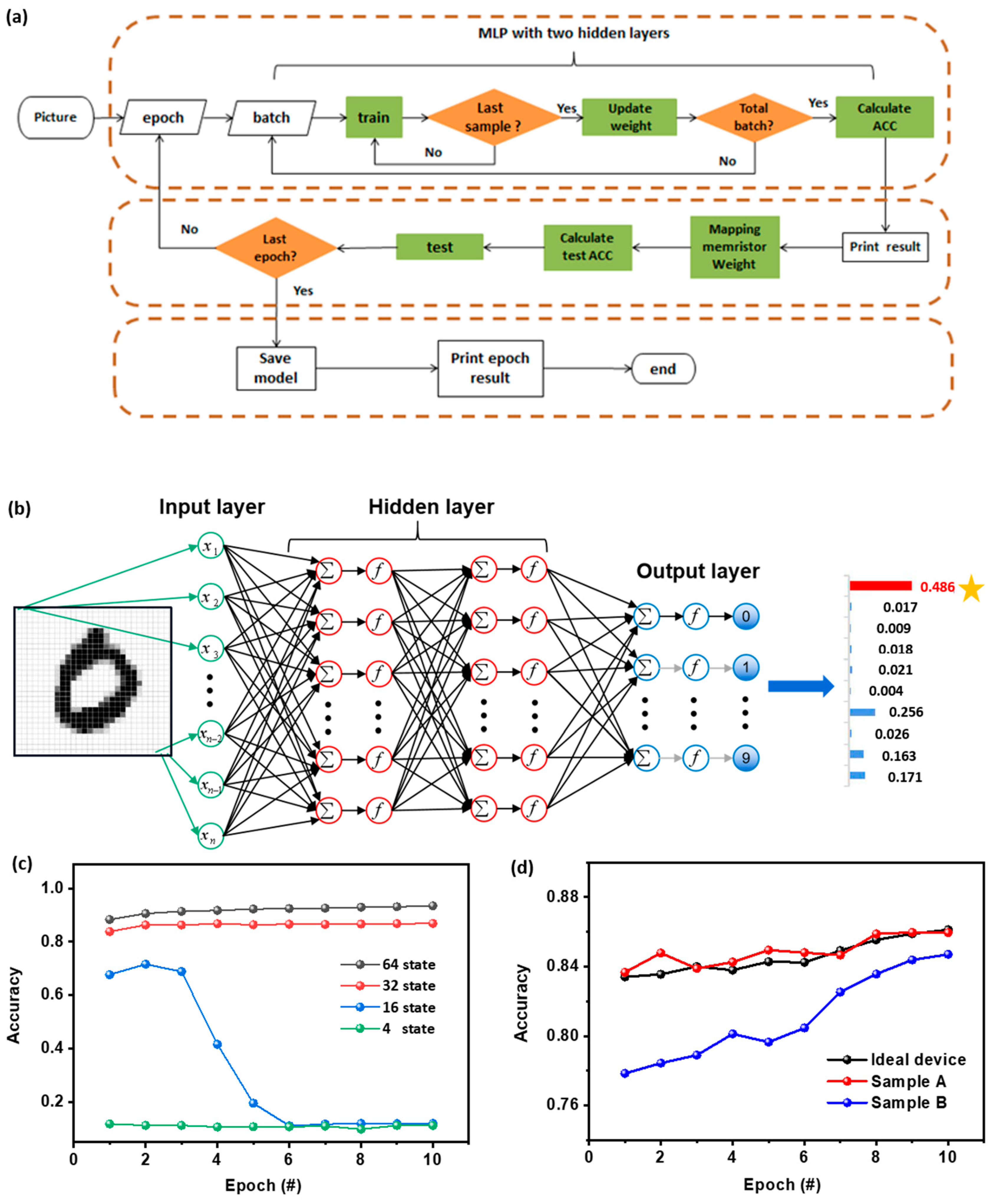

3. Results and Discussion

4. Conclusion

Author Contributions

Funding

Conflicts of Interest

References

- Wang, C.; He, W.; Tong, Y.; Zhao, R. Investigation and manipulation of different analog behaviors of memristor as electronic synapse for neuromorphic applications. Sci. Rep. 2016, 6, 22970. [Google Scholar] [CrossRef] [PubMed]

- Banerjee, W.; Liu, Q.; Lv, H.; Long, S.; Liu, M. Electronic imitation of behavioral and psychological synaptic activities using TiOx/Al2O3-based memristor devices. Nanoscale 2017, 9, 14442–14450. [Google Scholar] [CrossRef] [PubMed]

- Park, S.; Kim, H.; Choo, M.; Noh, J.; Sheri, A.; Jung, S.; Shin, J. RRAM-based synapse for neuromorphic system with pattern recognition function. In Proceedings of the IEEE International Electron Devices Meeting, San Francisco, CA, USA, 10–12 December 2012; pp. 10–12. [Google Scholar]

- Mandal, S.; El-Amin, A.; Alexander, K.; Rajendran, B.; Jha, R. Novel synaptic memory device for neuromorphic computing. Sci. Rep. 2014, 4, 5333. [Google Scholar] [CrossRef] [PubMed]

- Wang, Z.; Joshi, S.; Savelev, S.; Jiang, H.; Midya, R.; Lin, P.; Hu, M.; Ge, N.; Strachan, J.P.; Li, Z.Y. Memristors with diffusive dynamics as synaptic emulators for neuromorphic computing. Nat. Mater. 2017, 16, 101–108. [Google Scholar] [CrossRef] [PubMed]

- Torrejon, J.; Riou, M.; Araujo, F.A.; Tsunegi, S.; Khalsa, G.; Querlioz, D.; Bortolotti, P.; Cros, V.; Yakushiji, K.; Fukushima, A. Neuromorphic computing with nanoscale spintronic oscillators. Nature 2017, 547, 428–431. [Google Scholar] [CrossRef]

- Chicca, E.; Stefanini, F.; Bartolozzi, C.; Indiveri, G. Neuromorphic electronic circuits for building autonomous cognitive systems. Proc. IEEE 2014, 102, 1367–1388. [Google Scholar] [CrossRef]

- Kaneko, Y.; Nishitani, Y.; Ueda, M. Ferroelectric artificial synapses for recognition of a multishaded image. IEEE. Trans. Electron. Dev. 2014, 61, 2827–2833. [Google Scholar] [CrossRef]

- Jo, S.H.; Chang, T.; Ebong, I.; Bhadviya, B.B.; Mazumder, P.; Lu, W. Nanoscale memristor device as synapse in neuromorphic systems. Nano Lett. 2010, 10, 1297–1301. [Google Scholar] [CrossRef]

- Vincent, A.F.; Larroque, J.; Locatelli, N.; Romdhane, N.B.; Bichler, O.; Gamrat, C.; Zhao, W.S.; Klein, J.; Galdinretailleau, S.; Querlioz, D. Spin-transfer torque magnetic memory as a stochastic memristive synapse for neuromorphic systems. IEEE. Trans. Biomed. Circ. Symp. 2015, 9, 166–174. [Google Scholar] [CrossRef]

- Yang, J.J.; Pickett, M.D.; Li, X.; Ohlberg, D.A.; Stewart, D.R.; Williams, R.S. Memristive switching mechanism for metal/oxide/metal nanodevices. Nat. Nanotechnol. 2008, 3, 429–433. [Google Scholar] [CrossRef]

- Lee, M.J.; Lee, C.B.; Lee, D.; Lee, S.R.; Chang, M.; Hur, J.H.; Chung, U.I. A fast, high-endurance and scalable non-volatile memory device made from asymmetric Ta2O5-x/TaO2-x bilayer structures. Nat. Mater. 2011, 10, 625–630. [Google Scholar] [CrossRef] [PubMed]

- Zhang, Z.H.; Wang, Z.W.; Shi, T.; Bi, C.; Rao, F.; Cai, Y.M.; Liu, Q.; Wu, H.Q.; Zhou, P. Memory materials and devices: From concept to application. InfoMat 2020, 2, 261–290. [Google Scholar] [CrossRef]

- Chang, Y.; Fowler, B.; Chen, Y.; Zhou, F.; Pan, C.; Chang, T.; Lee, J.C. Demonstration of Synaptic Behaviors and Resistive Switching Characterizations by Proton Exchange Reactions in Silicon Oxide. Sci. Rep. 2016, 6, 21268. [Google Scholar] [CrossRef] [PubMed]

- Kim, S.; Kim, H.; Hwang, S.; Kim, M.H.; Chang, Y.F.; Park, B.G. Analog synaptic behavior of a silicon nitride memristor. ACS Appl. Mater. Interfaces 2017, 9, 40420–40427. [Google Scholar] [CrossRef]

- Chandrasekaran, S.; Simanjuntak, F.M.; Panda, D.; Tseng, T.-Y. Enhanced Synaptic Linearity in ZnO-Based Invisible Memristive Synapse by Introducing Double Pulsing Scheme. IEEE Trans. Electron. Dev. 2019, 66, 4722–4726. [Google Scholar] [CrossRef]

- Liu, S.; Li, K.; Sun, Y.; Zhu, X.; Li, Z.; Song, B.; Liu, H.J.; Li, Q. A TaOx-Based Electronic Synapse with High Precision for Neuromorphic Computing. IEEE Access 2019, 7, 184700–184706. [Google Scholar] [CrossRef]

- Govoreanu, B.; Kar, G.S.; Chen, Y.Y.; Paraschiv, V.; Kubicek, S.; Fantini, A.; Jossart, N. 10 × 10 nm2 Hf/HfOx crossbar resistive RAM with excellent performance, reliability and low-energy operation. In Proceedings of the IEEE International Electron Devices Meeting, Washington, DC, USA, 5–7 December 2011; pp. 31–36. [Google Scholar]

- Liu, Q.; Long, S.; Lv, H.; Wang, W.; Niu, J.; Huo, Z.; Chen, J.; Liu, M. Controllable growth of nanoscale conductive filaments in solid-electrolyte-based ReRAM by using a metal nanocrystal covered bottom electrode. ACS Nano 2010, 4, 6162–6168. [Google Scholar] [CrossRef]

- Bersuker, G.; Gilmer, D.C.; Veksler, D.; Kirsch, P.D.; Vandelli, L.; Padovani, A.; Larcher, L.; Mckenna, K.P.; Shluger, A.L.; Iglesias, V. Metal oxide resistive memory switching mechanism based on conductive filament properties. J. Appl. Phys. 2011, 110, 124518. [Google Scholar] [CrossRef]

- Yang, J.J.; Strukov, D.B.; Stewart, D.R. Memristive devices for computing. Nat. Nanotechnol. 2013, 8, 13–24. [Google Scholar] [CrossRef]

- Gokmen, T.; Vlasov, Y. Acceleration of deep neural network training with resistive cross-point devices: Design considerations. Front. Neurosci. Switz. 2016, 10, 333. [Google Scholar] [CrossRef]

- Merced-Grafals, E.J.; Dávila, N.; Ge, N.; Williams, R.S.; Strachan, J.P. Repeatable, accurate, and high speed multi-level programming of memristor 1T1R arrays for power efficient analog computing applications. Nanotechnology 2016, 27, 365202. [Google Scholar] [CrossRef] [PubMed]

- Hu, M.; Strachan, J.P.; Li, Z.; Grafals, E.M.; Davila, N.; Graves, C.; Sity, L.; Ge, N.; Yang, J.J.; Williams, R.S. Dot-product engine for neuromorphic computing: Programming 1T1M crossbar to accelerate matrix-vector multiplication. In Proceedings of the 2016 53nd ACM/EDAC/IEEE Design Automation Conference (DAC), Austin, TX, USA, 2–10 June 2016; pp. 1–6. [Google Scholar]

- Chakrabarti, B.; Lastrasmontano, M.A.; Adam, G.C.; Prezioso, M.; Hoskins, B.D.; Payvand, M.; Madhavan, A.; Ghofrani, A.; Theogarajan, L.; Cheng, K. A multiply-add engine with monolithically integrated 3D memristor crossbar/CMOS hybrid circuit. Sci. Rep. 2017, 7, 42429. [Google Scholar] [CrossRef] [PubMed]

- Ambrogio, S.; Balatti, S.; Milo, V.; Carboni, R.; Wang, Z.; Calderoni, A.; Ramaswamy, N.; Ielmini, D. Neuromorphic Learning and Recognition with One-Transistor-One-Resistor Synapses and Bistable Metal Oxide RRAM. IEEE. Trans. Electron. Dev. 2016, 63, 1508–1515. [Google Scholar] [CrossRef]

- Prezioso, M.; Bayat, F.M.; Hoskins, B.; Likharev, K.; Strukov, D. Self-adaptive spike-time-dependent plasticity of metal-oxide memristors. Sci. Rep. 2016, 6, 21331. [Google Scholar] [CrossRef]

- Klidbary, S.H.; Shouraki, S.B. A novel adaptive learning algorithm for low-dimensional feature space using memristor-crossbar implementation and on-chip training. Appl. Intell. 2018, 48, 4174–4191. [Google Scholar] [CrossRef]

- Shin, S.; Kim, K.; Kang, S.M. Memristor-based fine resolution programmable resistance and its applications. In Proceedings of the 2009 International Conference on Communications, Circuits and Systems, Milpitas, CA, USA, 23–25 July 2009; pp. 948–951. [Google Scholar]

- Yu, S.; Wu, Y.; Jeyasingh, R.; Kuzum, D.; Wong, H.S.P. An electronic synapse device based on metal oxide resistive switching memory for neuromorphic computation. IEEE. Trans. Electron. Dev. 2011, 58, 2729–2737. [Google Scholar] [CrossRef]

- Dietrich, S.W.; Goelman, D.; Borror, C.M.; Crook, S.M. An animated introduction to relational databases for many majors. IEEE. Trans. Electron. Dev. 2014, 58, 81–89. [Google Scholar] [CrossRef]

- Kuzum, D.; Jeyasingh, R.G.; Lee, B.; Wong, H.S.P. Nanoelectronic programmable synapses based on phase change materials for brain-inspired computing. Nano Lett. 2012, 12, 2179–2186. [Google Scholar] [CrossRef]

- Yu, S.; Gao, B.; Fang, Z.; Yu, H.; Kang, J.; Wong, H.S.P. A low energy oxide-based electronic synaptic device for neuromorphic visual systems with tolerance to device variation. Adv. Mater. 2013, 25, 1774–1779. [Google Scholar] [CrossRef]

- Waser, R.; Aono, M. Nanoionics-based resistive switching memories. Nat. Mater. 2007, 6, 833–840. [Google Scholar] [CrossRef]

- Wong, H.S.P.; Lee, H.Y.; Yu, S.; Chen, Y.S.; Wu, Y.; Chen, P.S.; Tsai, M.J. Metal-oxide RRAM. Proc. IEEE 2012, 100, 1951–1970. [Google Scholar] [CrossRef]

- Arruda, T.M.; Kumar, A.; Kalinin, S.V.; Jesse, S. Mapping Irreversible Electrochemical Processes on the Nanoscale: Ionic Phenomena in Li Ion Conductive Glass Ceramics. Nano Lett. 2011, 11, 4161. [Google Scholar] [CrossRef] [PubMed]

- Chen, Q.L.; Liu, G.; Xue, W.H.; Shang, J.; Gao, S.; Yi, X.H.; Lu, Y.; Tang, M.H.; Zheng, X.J.; Li, R.W. Controlled Construction of Atomic Point Contact with 16 Quantized Conductance States in Oxide Resistive Switching Memory. ACS Appl. Electron. Mater. 2019, 1, 789–798. [Google Scholar] [CrossRef]

- Hu, M.; Graves, C.E.; Li, C.; Li, Y.; Ge, N.; Montgomery, E.; Xia, Q. Memristor-based analog computation and neural network classification with a dot product engine. Adv. Mater. 2018, 30, 1705914. [Google Scholar] [CrossRef]

- Li, C.; Belkin, D.; Li, Y.; Yan, P.; Hu, M.; Ge, N.; Jiang, H.; Montgomery, E.; Lin, P.; Wang, Z.R. Efficient and self-adaptive in-situ learning in multilayer memristor neural networks. Nat. Commun. 2018, 9, 2385. [Google Scholar] [CrossRef]

- Zhu, X.; Su, W.; Liu, Y.; Hu, B.; Pan, L.; Lu, W.; Zhang, J.D.; Li, R.W. Observation of conductance quantization in oxide-based resistive switching memory. Adv. Mater. 2012, 24, 3941–3946. [Google Scholar] [CrossRef]

- Xue, W.; Gao, S.; Shang, J.; Shang, J.; Yi, X.H.; Liu, G.; Li, R.W. Recent advances of quantum conductance in memristors. Adv. Electron. Mater. 2019, 5, 1800854. [Google Scholar] [CrossRef]

- Xue, W.H.; Li, Y.; Liu, G.; Wang, Z.R.; Xiao, W.; Jiang, K.; Zhong, Z.; Gao, S.; Ding, J.; Miao, X. Controllable and Stable Quantized Conductance States in a Pt/HfOx/ITO Memristor. Adv. Electron. Mater. 2019, 5, 1901055. [Google Scholar]

- Chollet, F. Keras. 2015. Available online: keras.io (accessed on 4 January 2020).

- Yu, S.; Li, Z.; Chen, P.Y.; Wu, H.; Gao, B.; Wang, D.; Wu, W.; Qian, H. Binary Neural Network with 16 Mb RRAM Macro Chip for Classification and Online Training. In Proceedings of the 2016 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 3–7 December 2016; pp. 416–419. [Google Scholar]

- Wang, J.; Wang, X.; Eckert, C.; Subramaniyan, A.; Das, R.; Blaauw, D.; Sylvester, D. A Compute SRAM with Bit-Serial Integer/Floating-Point Operations for Programmable In-Memory Vector Acceleration. In Proceedings of the ISSCC 2019: International Solid-State Circuits Conference, San Francisco, CA, USA, 17–21 February 2019; pp. 224–226. [Google Scholar]

- Khwa, W.S.; Chen, J.J.; Li, J.F.; Si, X.; Yang, E.Y.; Sun, X.; Liu, R.; Chen, P.Y.; Li, Q.; Yu, S.; et al. A 65nm 4Kb Algorithm-Dependent Computing-in-Memory SRAM Unit-Macro with 2.3ns and 55.8TOPS/W Fully Parallel Product-Sum Operation for Binary DNN Edge Processors. In Proceedings of the 2018 IEEE International Solid-State Circuits Conference-(ISSCC), San Francisco, CA, USA, 4–8 February 2018; pp. 496–497. [Google Scholar]

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chen, Q.; Han, T.; Tang, M.; Zhang, Z.; Zheng, X.; Liu, G. Improving the Recognition Accuracy of Memristive Neural Networks via Homogenized Analog Type Conductance Quantization. Micromachines 2020, 11, 427. https://doi.org/10.3390/mi11040427

Chen Q, Han T, Tang M, Zhang Z, Zheng X, Liu G. Improving the Recognition Accuracy of Memristive Neural Networks via Homogenized Analog Type Conductance Quantization. Micromachines. 2020; 11(4):427. https://doi.org/10.3390/mi11040427

Chicago/Turabian StyleChen, Qilai, Tingting Han, Minghua Tang, Zhang Zhang, Xuejun Zheng, and Gang Liu. 2020. "Improving the Recognition Accuracy of Memristive Neural Networks via Homogenized Analog Type Conductance Quantization" Micromachines 11, no. 4: 427. https://doi.org/10.3390/mi11040427

APA StyleChen, Q., Han, T., Tang, M., Zhang, Z., Zheng, X., & Liu, G. (2020). Improving the Recognition Accuracy of Memristive Neural Networks via Homogenized Analog Type Conductance Quantization. Micromachines, 11(4), 427. https://doi.org/10.3390/mi11040427