Power Management IC for a Dual-Input-Triple-Output Energy Harvester

Abstract

1. Introduction

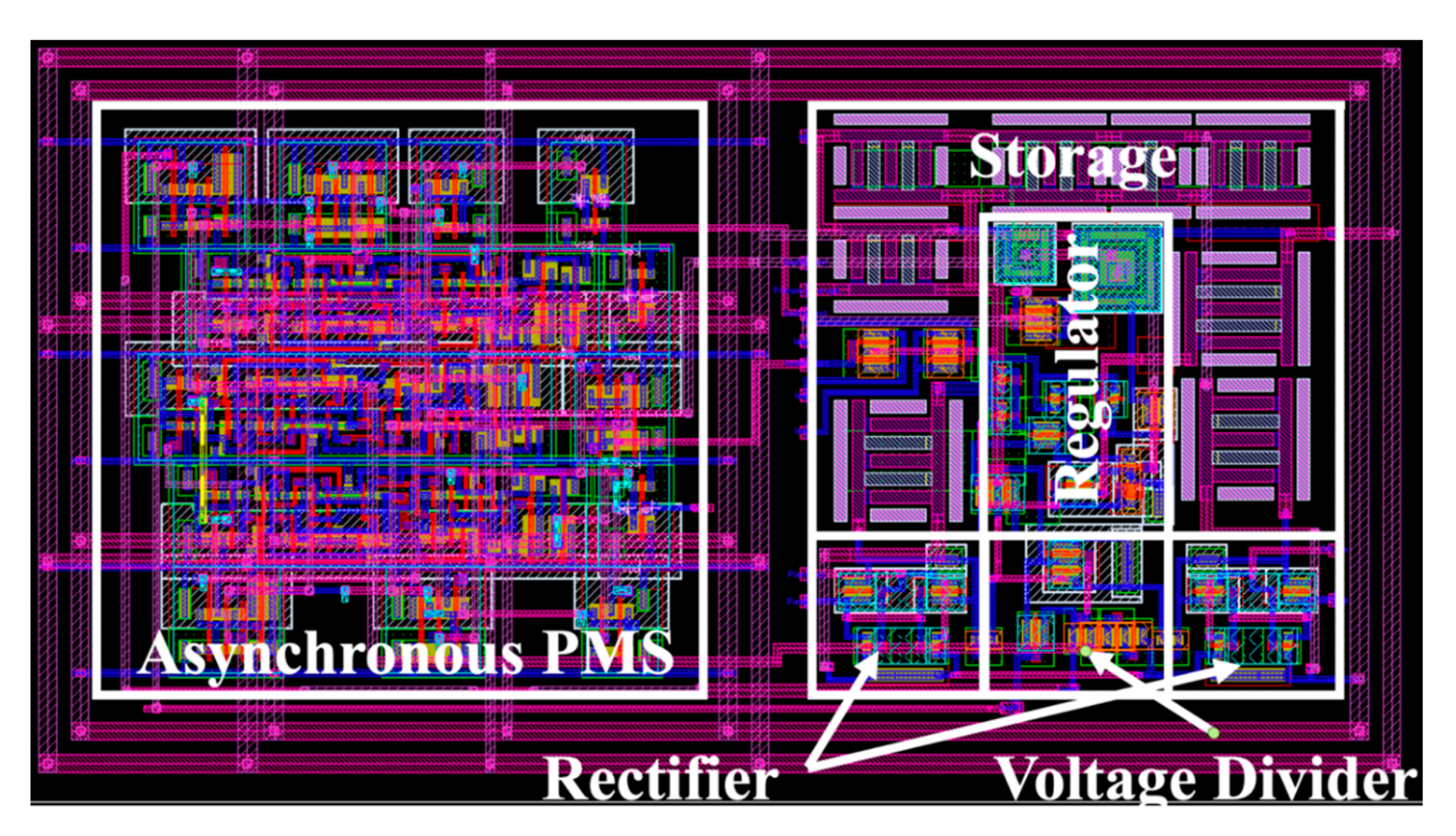

2. Methods

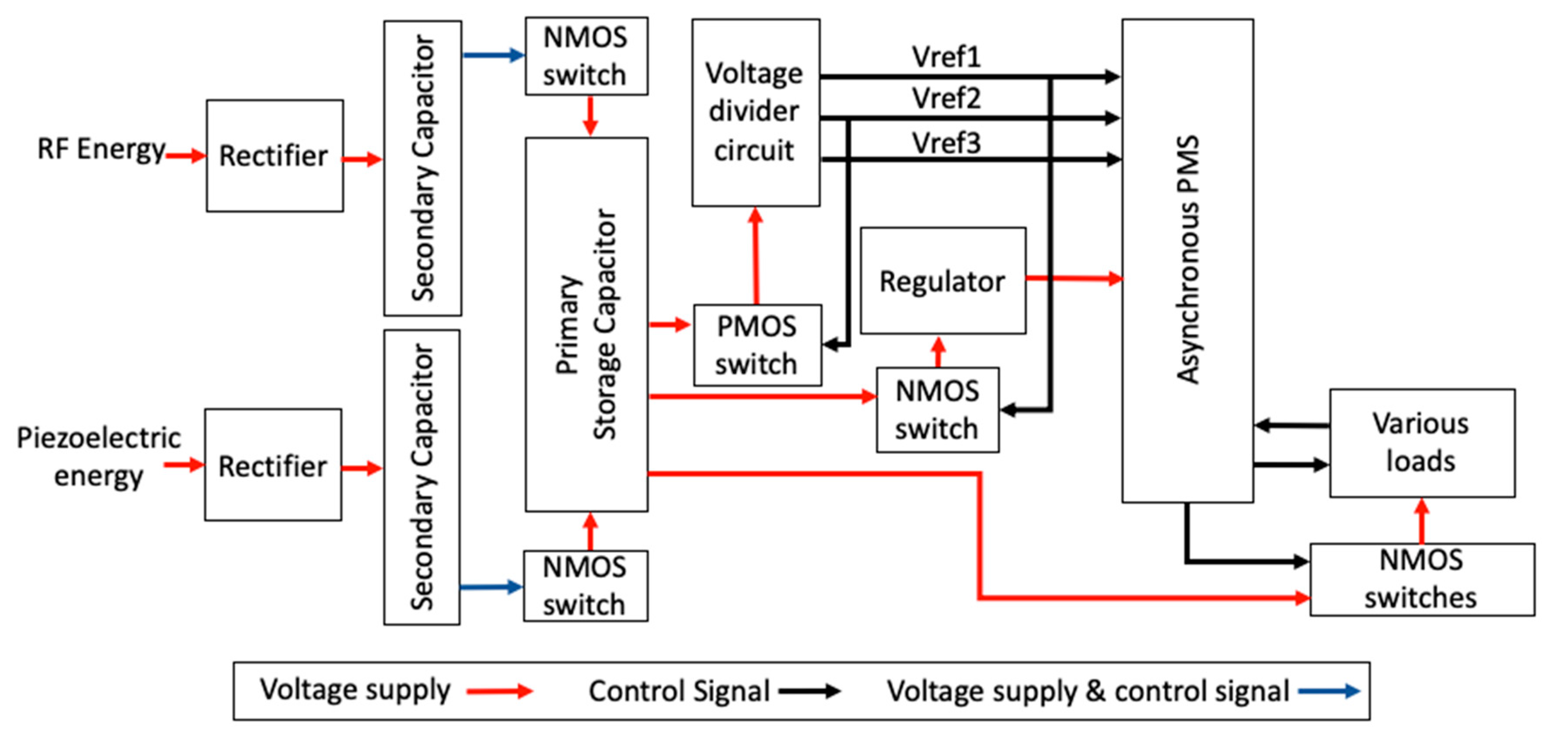

2.1. Description of the Whole System

2.1.1. RF Waves

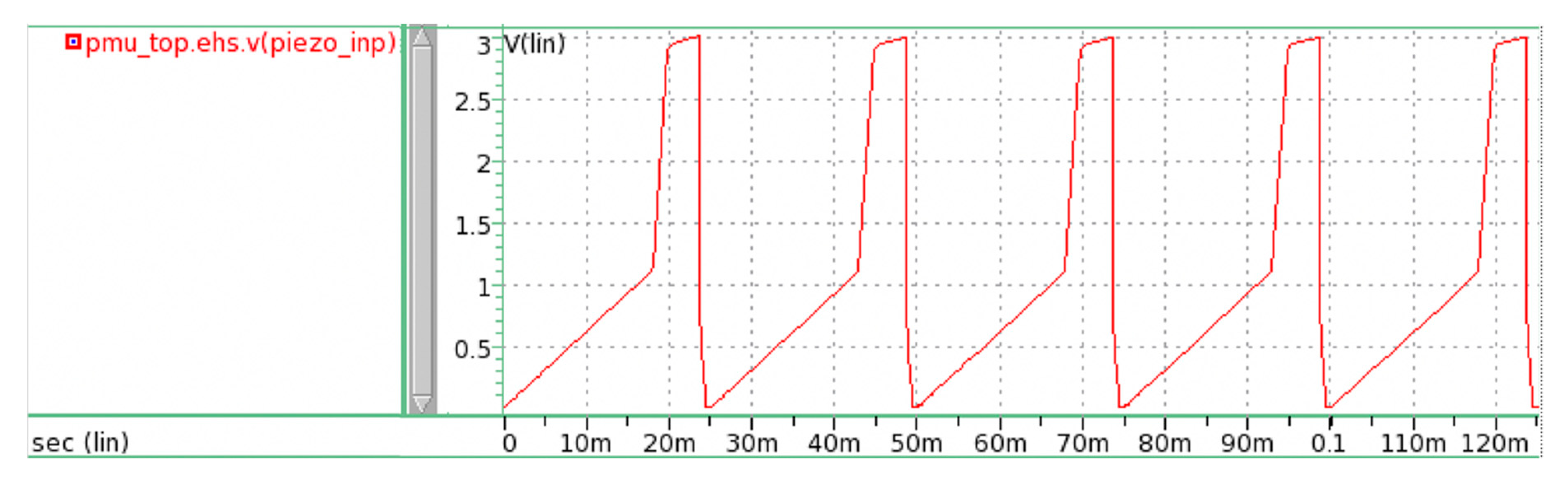

2.1.2. Piezoelectric

2.1.3. Rectifier

2.1.4. Energy Storage

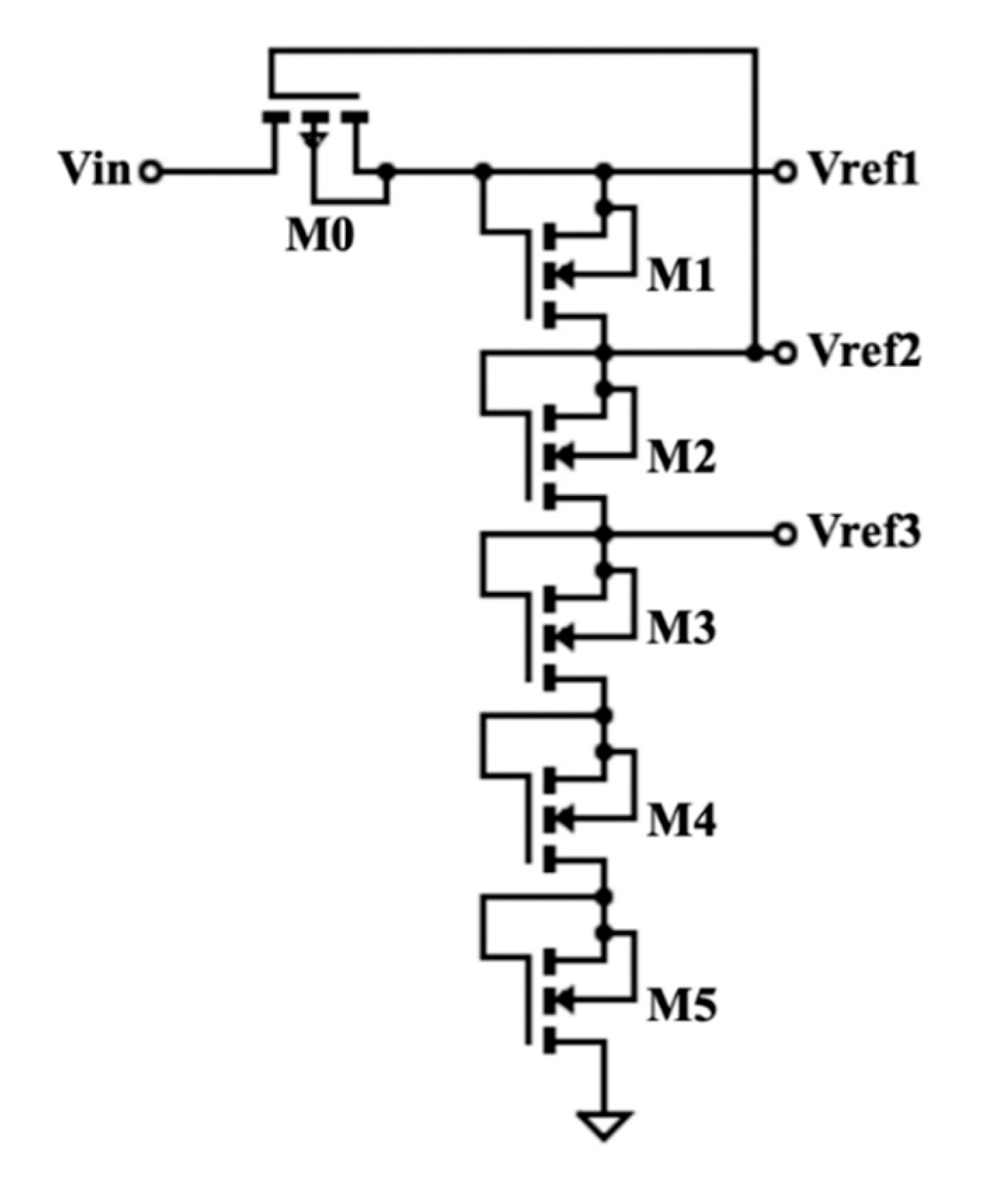

2.1.5. Voltage Divider

2.1.6. Voltage Regulator

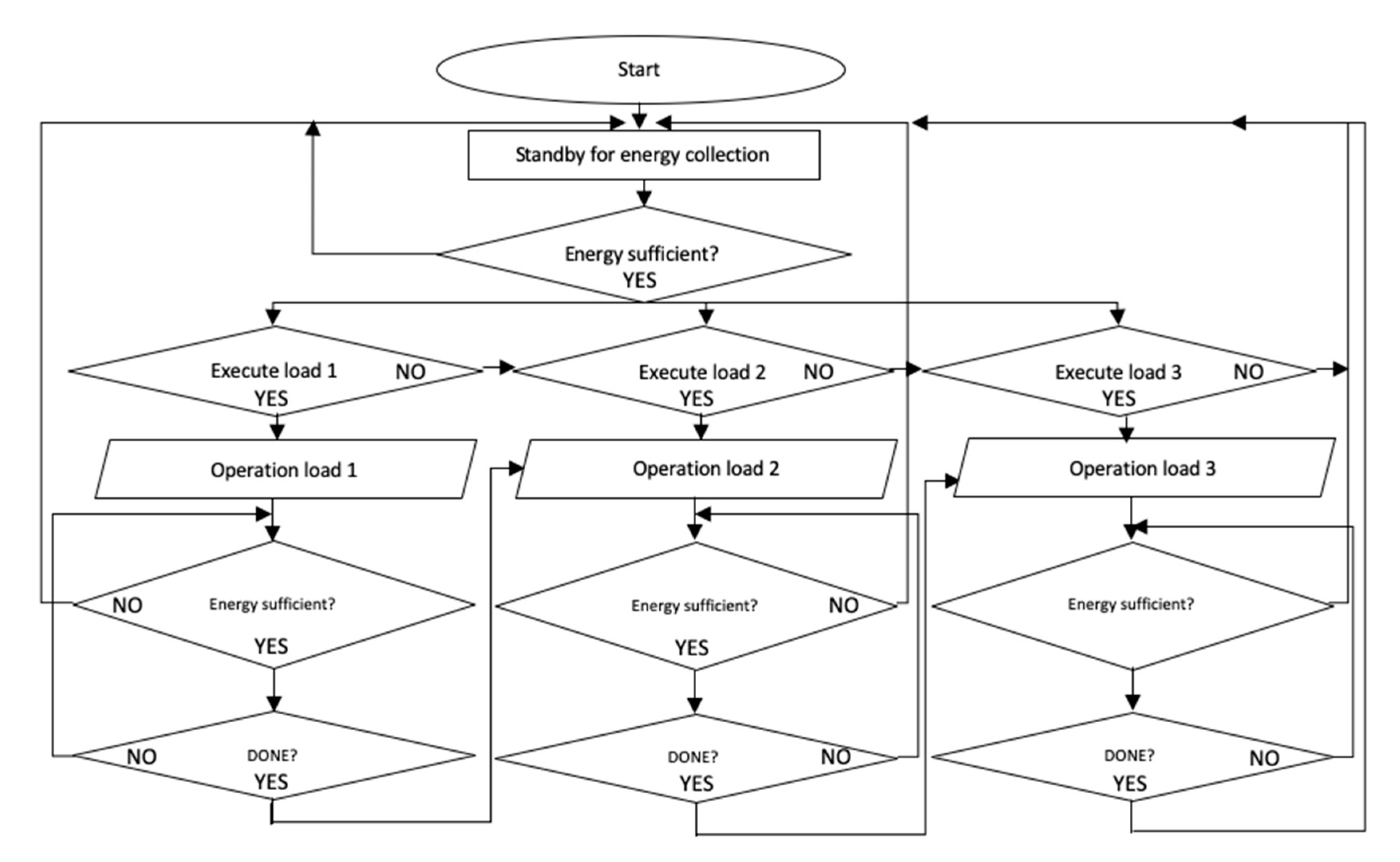

2.1.7. Control Unit (Asynchronous PMS)

2.1.8. Loads

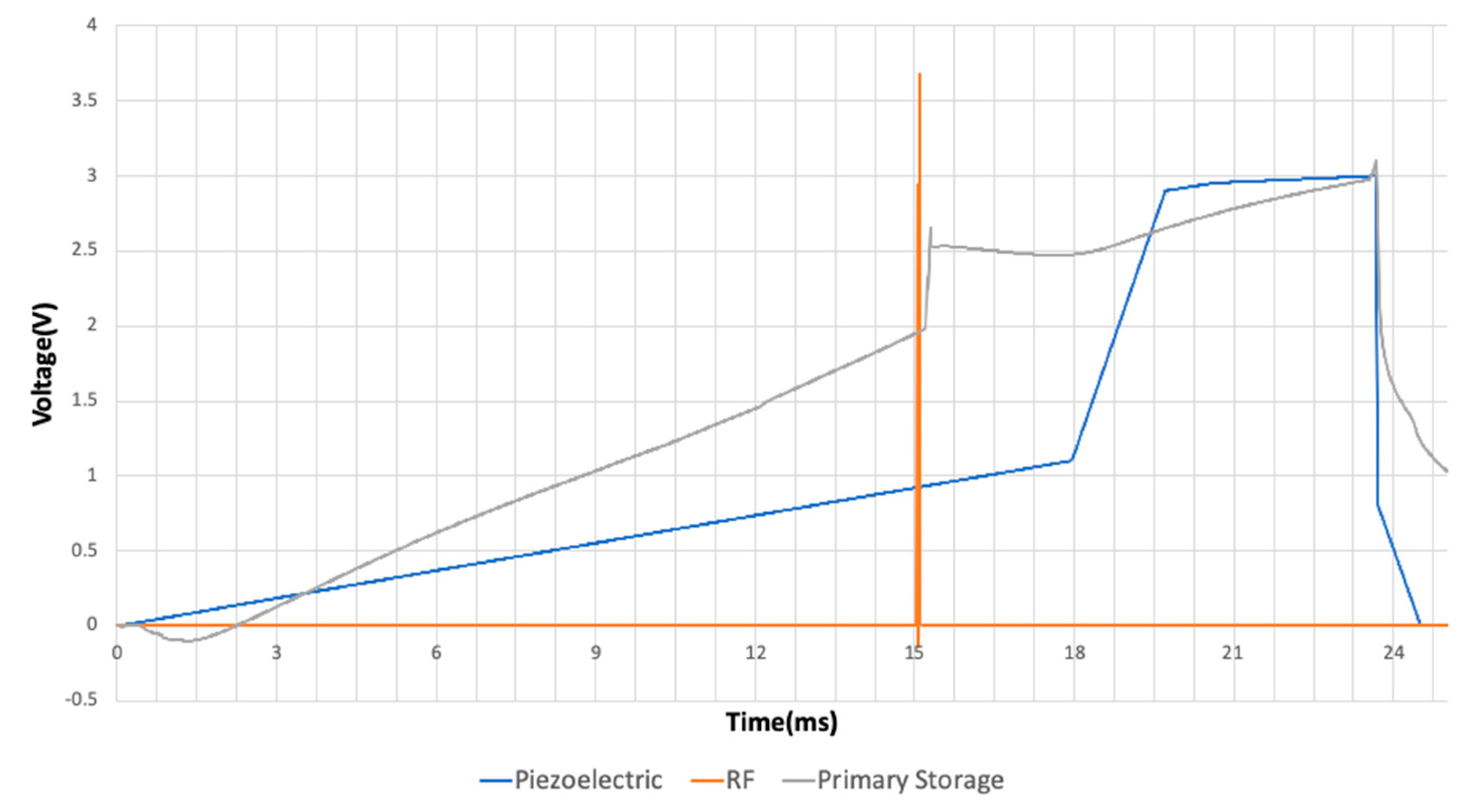

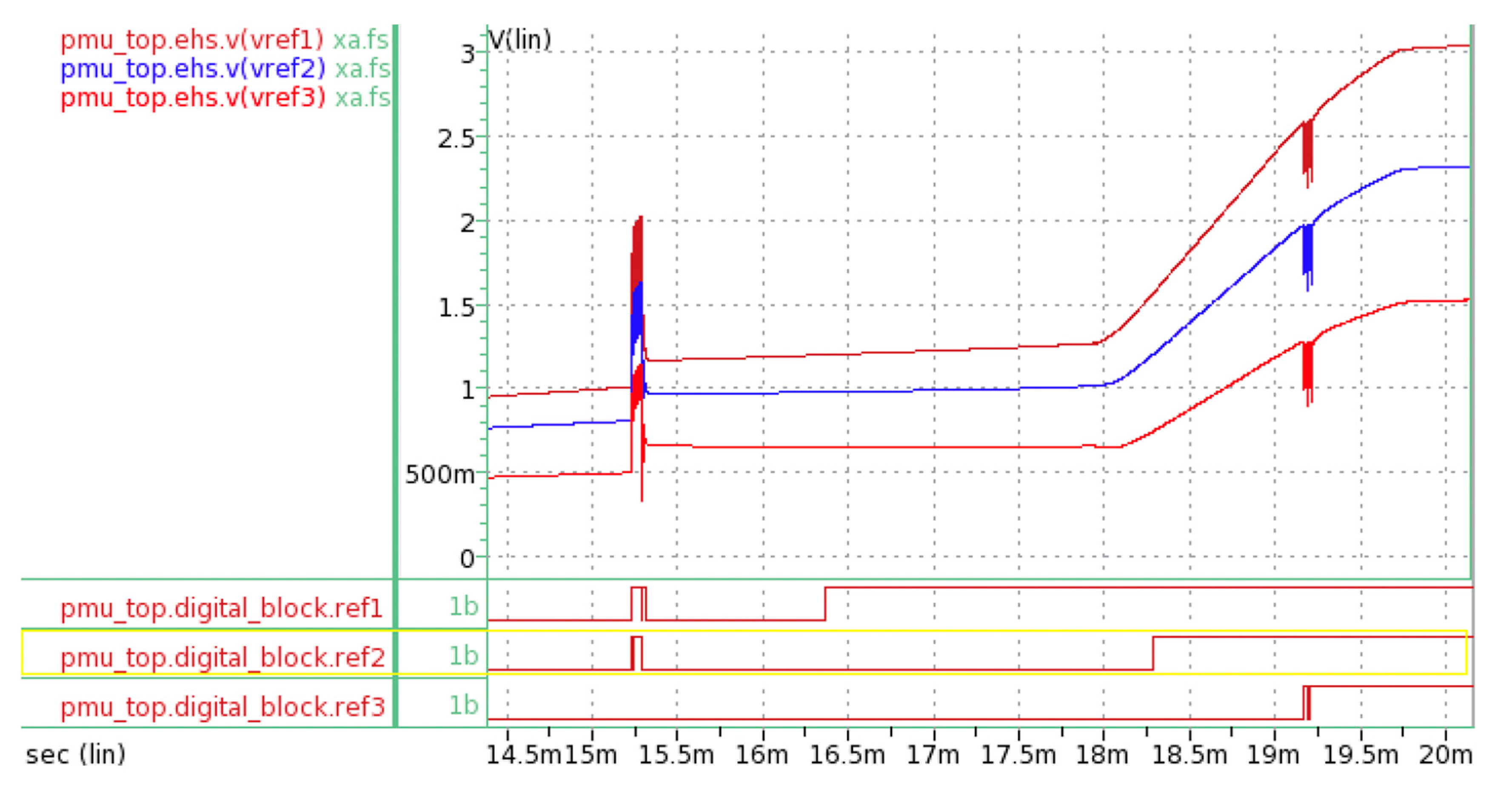

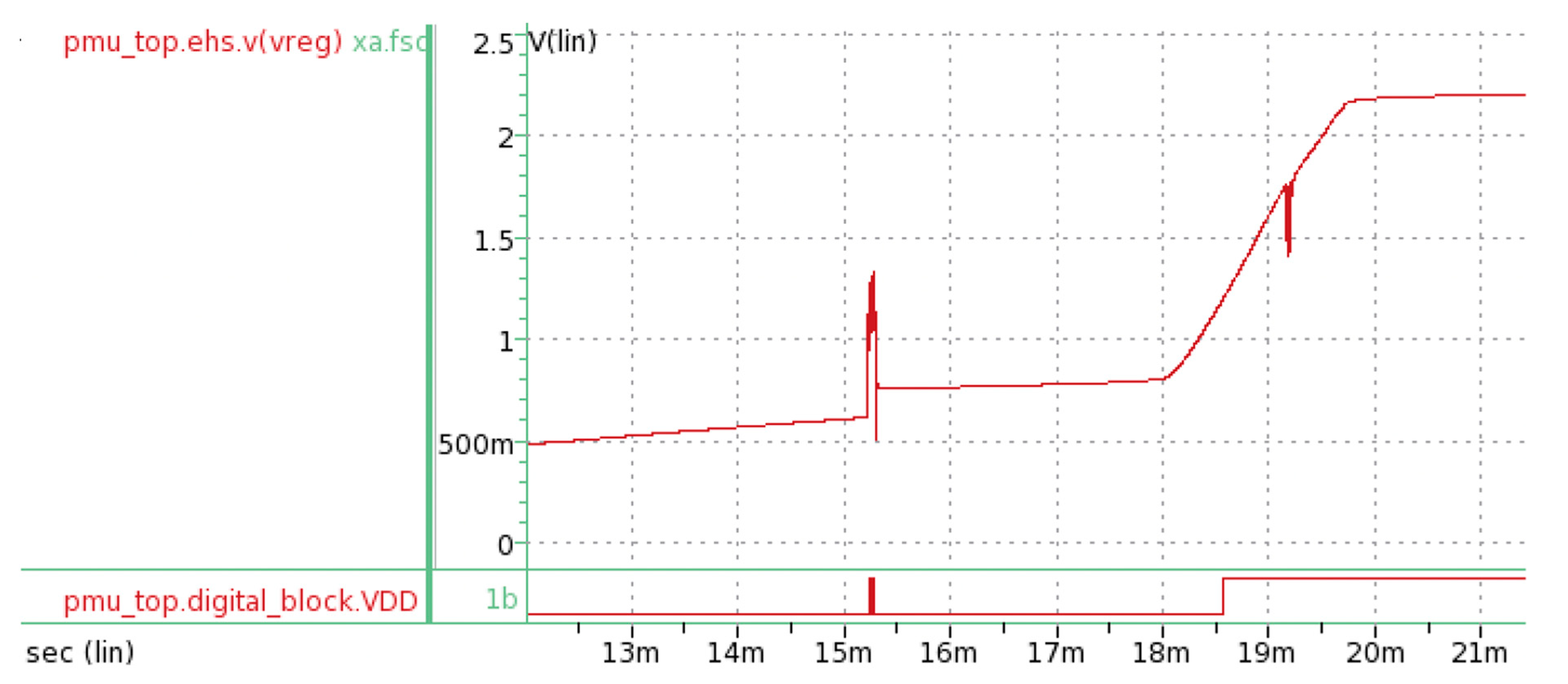

3. Results and Discussion

3.1. Analog Circuits

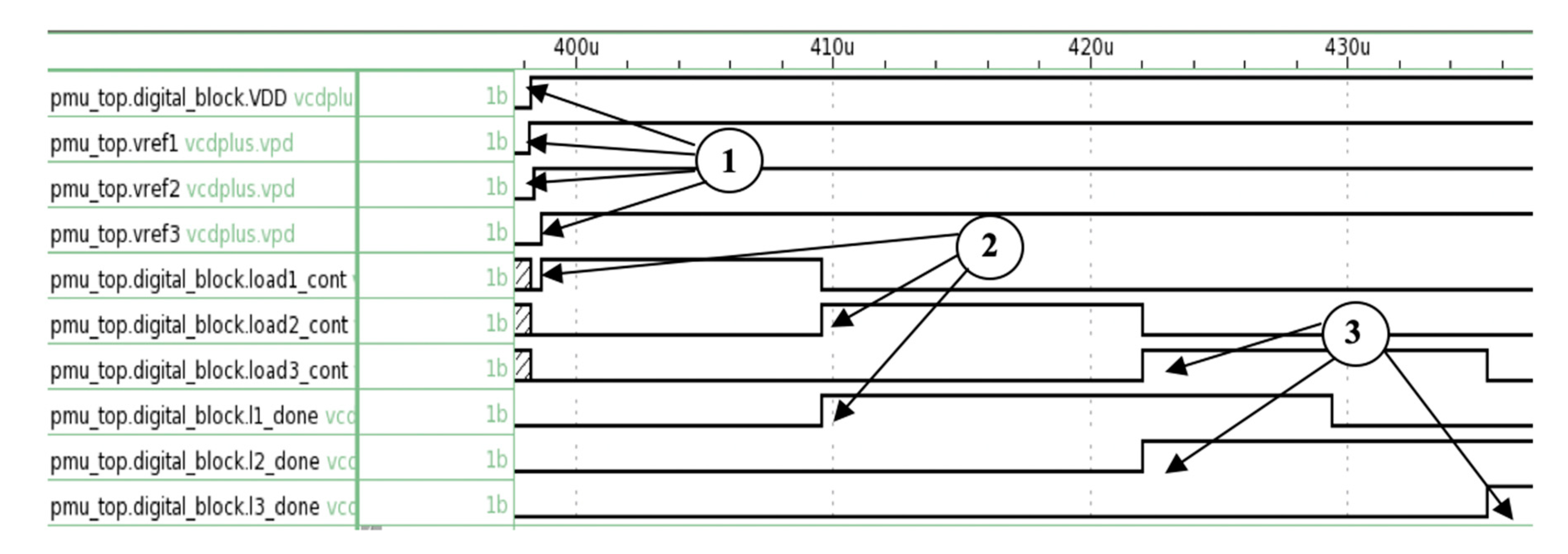

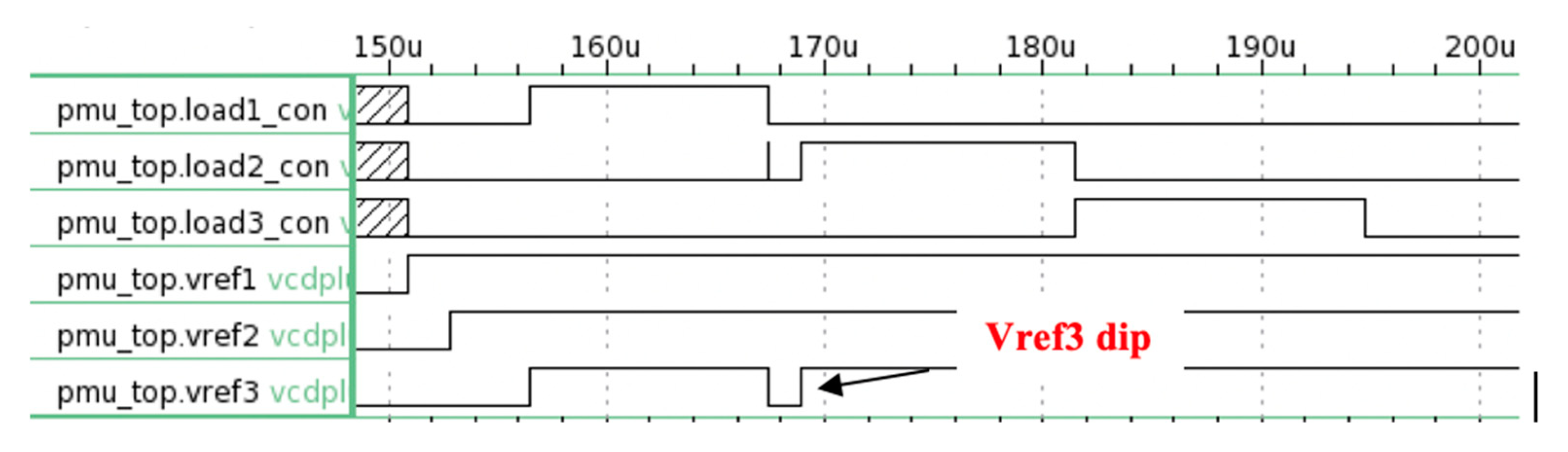

3.2. Control Unit

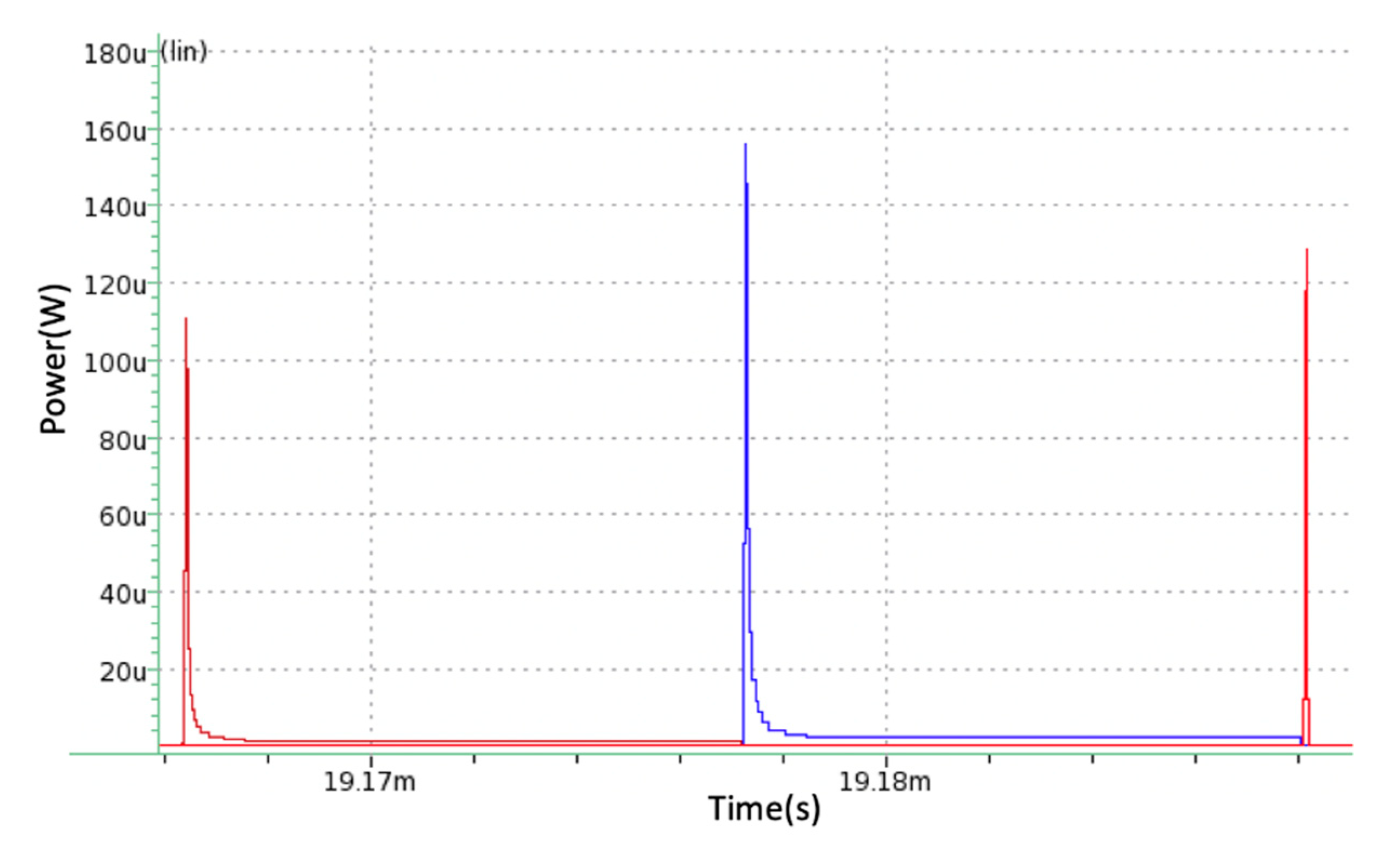

3.3. Power Generation and Consumption

3.4. Power Generation at Varying Distance of RF Source

4. Conclusions

Supplementary Materials

Author Contributions

Funding

Conflicts of Interest

References

- Gungor, V.C.; Hancke, G.P. Industrial Wireless Sensor Networks: Challenges, Design Principles, and Technical Approaches. IEEE Trans. Ind. Electron. 2009, 56, 4258–4265. [Google Scholar] [CrossRef]

- Yang, Y.; Fan, Z.; Gao, R.X. Optimal battery control strategy for wireless sensor networks with solar energy supply. In Proceedings of the 2014 American Control Conference, Portland, OR, USA, 4–6 June 2014; pp. 3559–3564. [Google Scholar]

- Han, C.; Harrold, T.; Armour, S.; Krikidis, I.; Videv, S.; Grant, P.M.; Haas, H.; Thompson, J.S.; Ku, I.; Wang, C.-X.; et al. Green radio: Radio techniques to enable energy-efficient wireless networks. IEEE Commun. Mag. 2011, 49, 46–54. [Google Scholar] [CrossRef]

- Paradiso, J.; Starner, T. Energy Scavenging for Mobile and Wireless Electronics. IEEE Pervasive Comput. 2005, 4, 18–27. [Google Scholar] [CrossRef]

- Sudevalayam, S.; Kulkarni, P. Energy Harvesting Sensor Nodes: Survey and Implications. IEEE Commun. Surv. Tutor. 2010, 13, 443–461. [Google Scholar] [CrossRef]

- Ku, M.-L.; Chen, Y.; Liu, K.R. Data-Driven Stochastic Models and Policies for Energy Harvesting Sensor Communications. IEEE J. Sel. Areas Commun. 2015, 33, 1. [Google Scholar] [CrossRef]

- Ku, M.-L.; Li, W.; Chen, Y.; Liu, K.J.R. Advances in Energy Harvesting Communications: Past, Present, and Future Challenges. IEEE Commun. Surv. Tutor. 2015, 18, 1384–1412. [Google Scholar] [CrossRef]

- Kim, S.; Vyas, R.; Bito, J.; Niotaki, K.; Collado, A.; Georgiadis, A.; Tentzeris, M.M. Ambient RF Energy-Harvesting Technologies for Self-Sustainable Standalone Wireless Sensor Platforms. Proc. IEEE 2014, 102, 1649–1666. [Google Scholar] [CrossRef]

- Visser, H.J.; Vullers, R.J.M. RF Energy Harvesting and Transport for Wireless Sensor Network Applications: Principles and Requirements. Proc. IEEE 2013, 101, 1410–1423. [Google Scholar] [CrossRef]

- Psomas, C.; Krikidis, I. A Wireless Powered Feedback Protocol for Opportunistic Beamforming Using Rectenna Arrays. IEEE Trans. Green Commun. Netw. 2018, 2, 100–113. [Google Scholar] [CrossRef]

- Monti, G.; Masotti, D.; Paolini, G.; Corchia, L.; Costanzo, A.; Dionigi, M.; Mastri, F.; Mongiardo, M.; Sorrentino, R.; Tarricone, L. EMC and EMI issues of WPT systems for wearable and implantable devices. IEEE Electromagn. Compat. Mag. 2018, 7, 67–77. [Google Scholar] [CrossRef]

- Dardari, D.; Feuillen, T.; Raucy, C.; Vandendorpe, L.; Craeye, C.; DeCarli, N.; Fabbri, D.; Guerra, A.; Fantuzzi, M.; Masotti, D.; et al. An Ultra-wideband Battery-less Positioning System for Space Applications. In Proceedings of the 2019 IEEE International Conference on RFID Technology and Applications (RFID-TA), Pisa, Italy, 25–27 September 2019; pp. 104–109. [Google Scholar]

- Costanzo, A.; Masotti, D.; Fantuzzi, M.; Del Prete, M. Co-Design Strategies for Energy-Efficient UWB and UHF Wireless Systems. IEEE Trans. Microw. Theory Tech. 2017, 65, 1852–1863. [Google Scholar] [CrossRef]

- Correia, R.; Carvalho, N.B.; Kawasaki, S. Continuously Power Delivering for Passive Backscatter Wireless Sensor Networks. IEEE Trans. Microw. Theory Tech. 2016, 64, 3723–3731. [Google Scholar] [CrossRef]

- Sun, H.; Guo, Y.; He, M.; Zhong, Z. A dual-band rectenna using broad- band yagi antenna array for ambient RF power harvesting. IEEE Antennas Wirel. Propag. Lett. 2013, 12, 918–921. [Google Scholar] [CrossRef]

- Ren, Y.-J.; Farooqui, M.F.; Chang, K. A Compact Dual-Frequency Rectifying Antenna with High-Orders Harmonic-Rejection. IEEE Trans. Antennas Propag. 2007, 55, 2110–2113. [Google Scholar] [CrossRef]

- Seneviratne, S.; Hu, Y.; Nguyen, T.; Lan, G.; Khalifa, S.; Thilakarathna, K.; Hassan, M.; Seneviratne, A. A Survey of Wearable Devices and Challenges. IEEE Commun. Surv. Tutor. 2017, 19, 2573–2620. [Google Scholar] [CrossRef]

- Kim, H.S.; Kim, J.-H.; Kim, J. A review of piezoelectric energy harvesting based on vibration. Int. J. Precis. Eng. Manuf. 2011, 12, 1129–1141. [Google Scholar] [CrossRef]

- Bowen, C.R.; Kim, H.A.; Weaver, P.M.; Dunn, S. Piezoelectric and ferroelectric materials and structures for energy harvesting applications. Energy Environ. Sci. 2014, 7, 25–44. [Google Scholar] [CrossRef]

- Jang, J.; Berdy, D.; Lee, J.; Peroulis, D.; Jung, B. A Wireless Condition Monitoring System Powered by a Sub-100 /spl mu/W Vibration Energy Harvester. IEEE Trans. Circuits Syst. I Regul. Pap. 2013, 60, 1082–1093. [Google Scholar] [CrossRef]

- Sankman, J.; Ma, D. A 12-μW to 1.1-mW AIM Piezoelectric Energy Harvester for Time-Varying Vibrations With 450-nA IQ. IEEE Trans. Power Electron. 2015, 30, 632–643. [Google Scholar] [CrossRef]

- Bai, Y.; Jantunen, H.; Juuti, J. Energy Harvesting Research: The Road from Single Source to Multisource. Adv. Mater. 2018, 30, 1707271. [Google Scholar] [CrossRef]

- Estrada-López, J.J.; Abuellil, A.; Zeng, Z.; Sánchez-Sinencio, E. Multiple Input Energy Harvesting Systems for Autonomous IoT End-Nodes. J. Low Power Electron. Appl. 2018, 8, 6. [Google Scholar] [CrossRef]

- Colomer-Farrarons, J.; Miribel-Català, P.L.; Saiz-Vela, A.; Samitier, J. A Multiharvested Self-Powered System in a Low-Voltage Low-Power Technology. IEEE Trans. Ind. Electron. 2010, 58, 4250–4263. [Google Scholar] [CrossRef]

- Chowdary, G.; Singh, A.; Chatterjee, S. An 18 nA, 87% Efficient Solar, Vibration and RF Energy-Harvesting Power Management System With a Single Shared Inductor. IEEE J. Solid-State Circuits 2016, 51, 2501–2513. [Google Scholar] [CrossRef]

- Dini, M.; Romani, A.; Filippi, M.; Bottarel, V.; Ricotti, G.; Tartagni, M. A Nanocurrent Power Management IC for Multiple Heterogeneous Energy Harvesting Sources. IEEE Trans. Power Electron. 2014, 30, 5665–5680. [Google Scholar] [CrossRef]

- Mohd-Yasin, F.; Khaw, M.K.; Reaz, M.B.I. Techniques of RFID Systems: Architectures and Applications. Microw. J. 2006, 49, 62. [Google Scholar]

- Vyas, R.; Cook, B.B.; Kawahara, Y.; Tentzeris, M.M. E-WEHP: A Batteryless Embedded Sensor-Platform Wirelessly Powered From Ambient Digital-TV Signals. IEEE Trans. Microw. Theory Tech. 2013, 61, 2491–2505. [Google Scholar] [CrossRef]

- Pinuela, M.; Mitcheson, P.D.; Lucyszyn, S. Ambient RF Energy Harvesting in Urban and Semi-Urban Environments. IEEE Trans. Microw. Theory Tech. 2013, 61, 2715–2726. [Google Scholar] [CrossRef]

- Ferdik, M.; Saxl, G.; Ussmueller, T. Battery-less UHF RFID controlled transistor switch for Internet of Things applications—A feasibility study. In Proceedings of the 2018 IEEE Topical Conference on Wireless Sensors and Sensor Networks (WiSNet), Anaheim, CA, USA, 14–17 January 2018; pp. 96–98. [Google Scholar] [CrossRef]

- Romani, A.; Filippi, M.; Tartagni, M. Micropower Design of a Fully Autonomous Energy Harvesting Circuit for Arrays of Piezoelectric Transducers. IEEE Trans. Power Electron. 2013, 29, 729–739. [Google Scholar] [CrossRef]

- Kim, Y.-J.; Bhamra, H.S.; Joseph, J.; Irazoqui, P.P. An Ultra-Low-Power RF Energy-Harvesting Transceiver for Multiple-Node Sensor Application. IEEE Trans. Circuits Syst. II Express Briefs 2015, 62, 1028–1032. [Google Scholar] [CrossRef]

- Chang, K.-L.; Gwee, B.-H. A Low-Energy Low-Voltage Asynchronous 8051 Microcontroller Core. In Proceedings of the 2006 IEEE International Symposium on Circuits and Systems, Island of Kos, Greece, 21–24 May 2006; pp. 4–3184. [Google Scholar] [CrossRef]

- Hoang, V.-P.; Dao, V.-L.; Pham, C.-K. Design of ultra-low power AES encryption cores with silicon demonstration in SOTB CMOS process. Electron. Lett. 2017, 53, 1512–1514. [Google Scholar] [CrossRef]

| Loads | Power Consumption (μW) |

|---|---|

| AES | 52.36 |

| MCU | 70 |

| RF Transceiver | 98 |

| Total power consumption | 220.36 |

| Distance | 2.5 m | 5 m | 7.5 m | 10 m |

| RF input power (μW) | 654.7 | 163.7 | 72.7 | 40.9 |

| Generated power after rectifier (μW) | 489.0609 | 122.2839 | 54.3069 | 30.5523 |

| Generated power after deducting power consumption by PMIC (μW) | 476.9909 | 110.2139 | 42.2369 | 18.4823 |

| Minimum amount of power from piezoelectric input that is needed to supplement power from RF input (μW) | 0 | 122.2161 | 190.1931 | 213.9477 |

| Min. number of Piezoelectric input source (times) | 0 | 1 | 2 | 2 |

| Piezoelectric input power (μW) | 0 | 143.4 | 286.8 | 286.8 |

| Piezoelectric input power after rectifier (μW) | 0 | 125.80 | 251.60 | 251.60 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Mui, K.-M.; Khaw, M.-K.; Mohd-Yasin, F. Power Management IC for a Dual-Input-Triple-Output Energy Harvester. Micromachines 2020, 11, 937. https://doi.org/10.3390/mi11100937

Mui K-M, Khaw M-K, Mohd-Yasin F. Power Management IC for a Dual-Input-Triple-Output Energy Harvester. Micromachines. 2020; 11(10):937. https://doi.org/10.3390/mi11100937

Chicago/Turabian StyleMui, Kai-Meng, Mei-Kum Khaw, and Faisal Mohd-Yasin. 2020. "Power Management IC for a Dual-Input-Triple-Output Energy Harvester" Micromachines 11, no. 10: 937. https://doi.org/10.3390/mi11100937

APA StyleMui, K.-M., Khaw, M.-K., & Mohd-Yasin, F. (2020). Power Management IC for a Dual-Input-Triple-Output Energy Harvester. Micromachines, 11(10), 937. https://doi.org/10.3390/mi11100937