Design and Implementation of a High Step-Up DC-DC Converter Based on the Conventional Boost and Buck-Boost Converters with High Value of the Efficiency Suitable for Renewable Application

Abstract

:1. Introduction

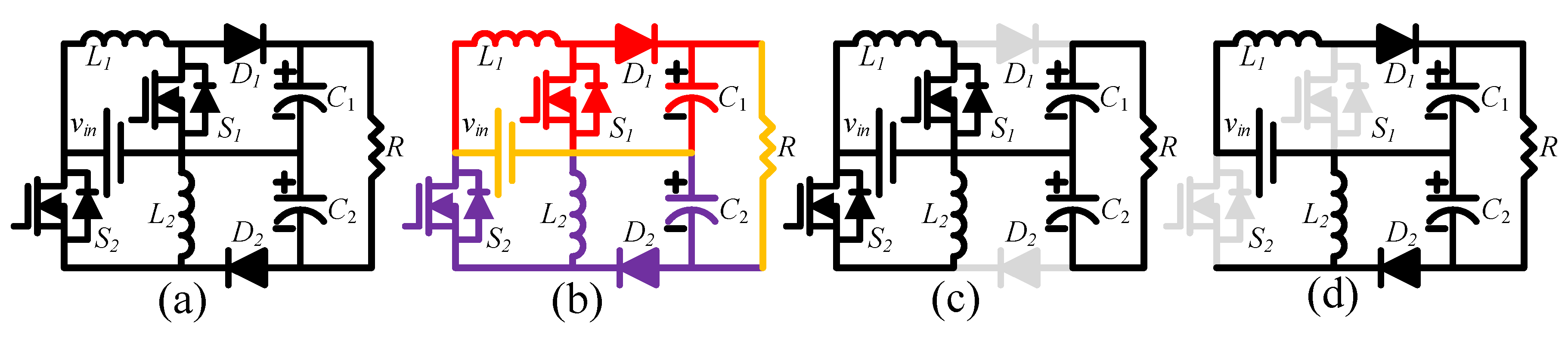

2. Proposed Converter

- The operation of the converter takes place in the continuous conduction mode (CCM).

- All the circuit components are ideal and their parasitic components are neglected.

- The capacitors are large enough to keep their voltage constant.

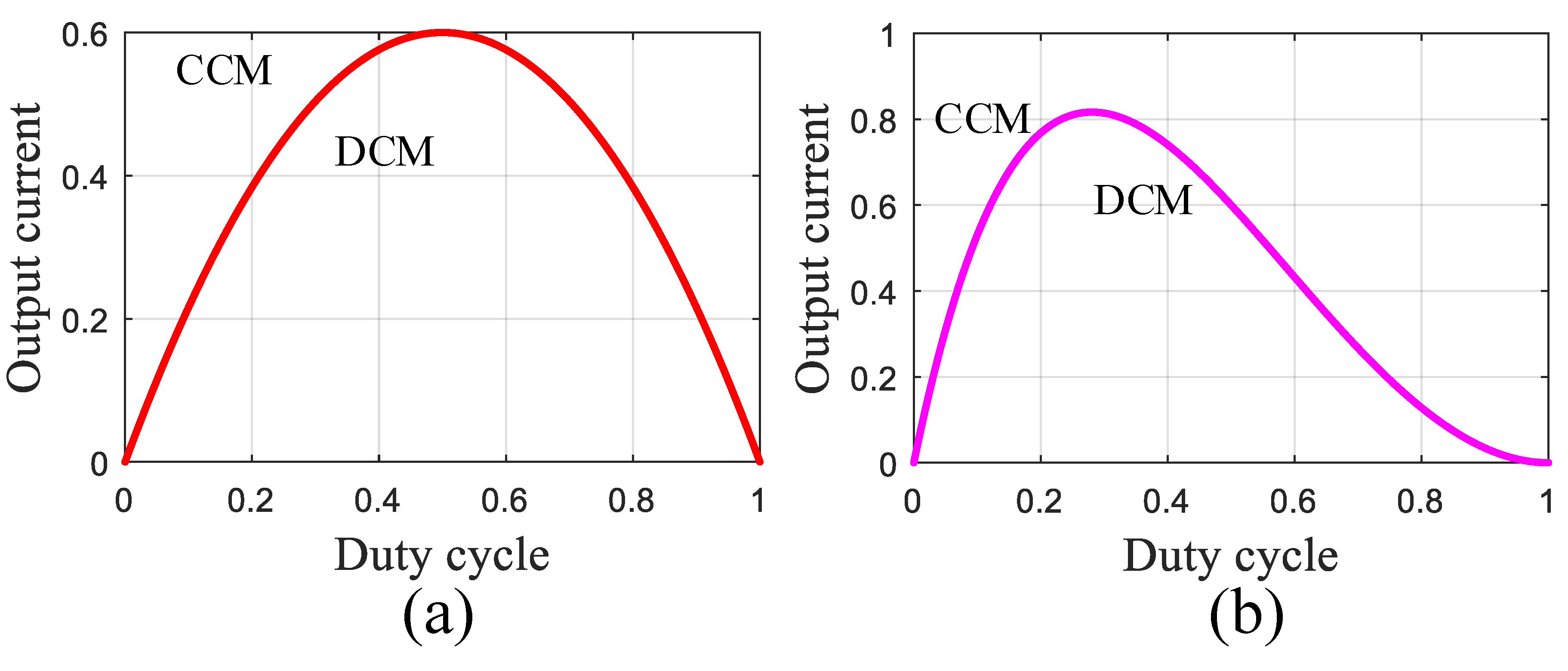

3. DCM Mode

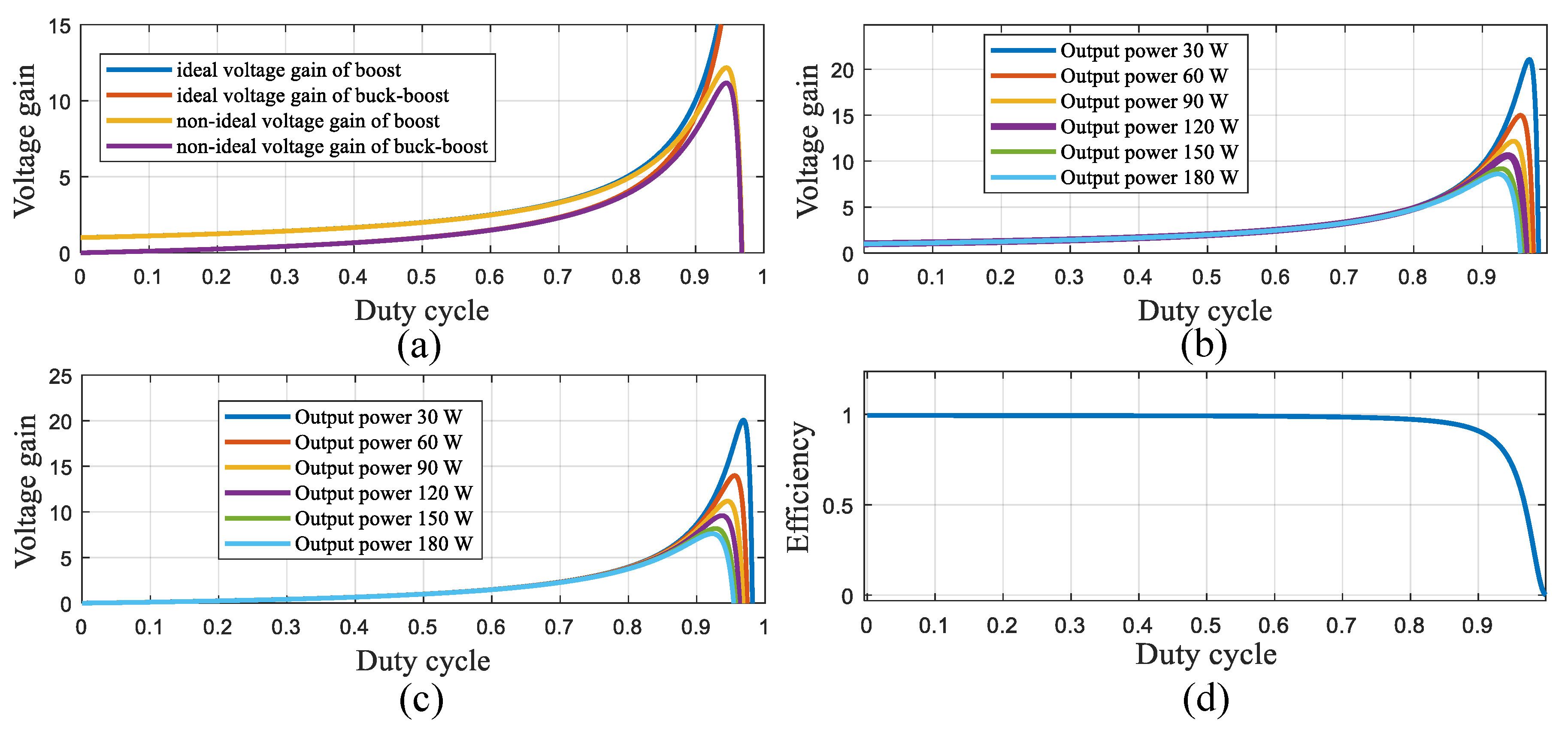

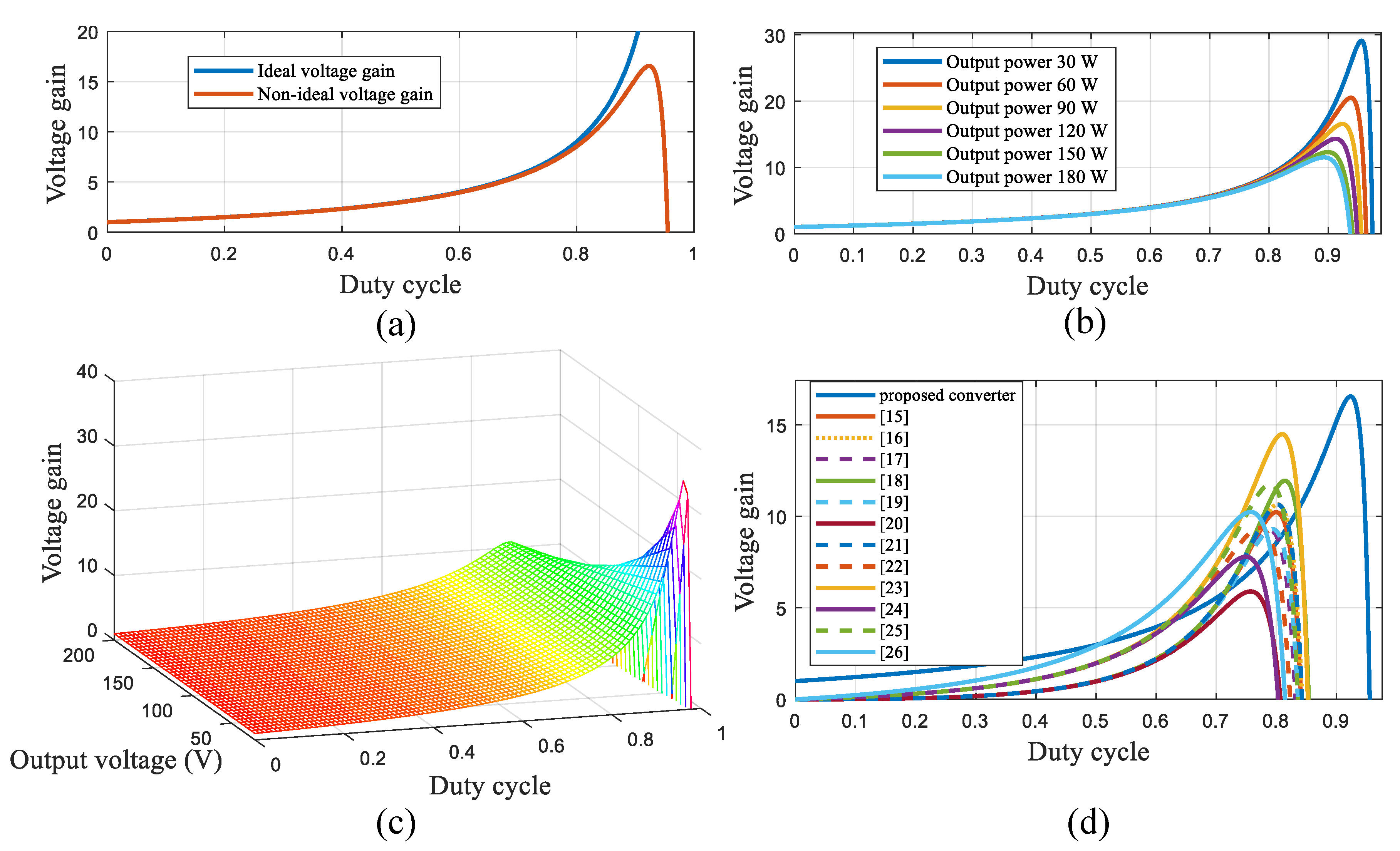

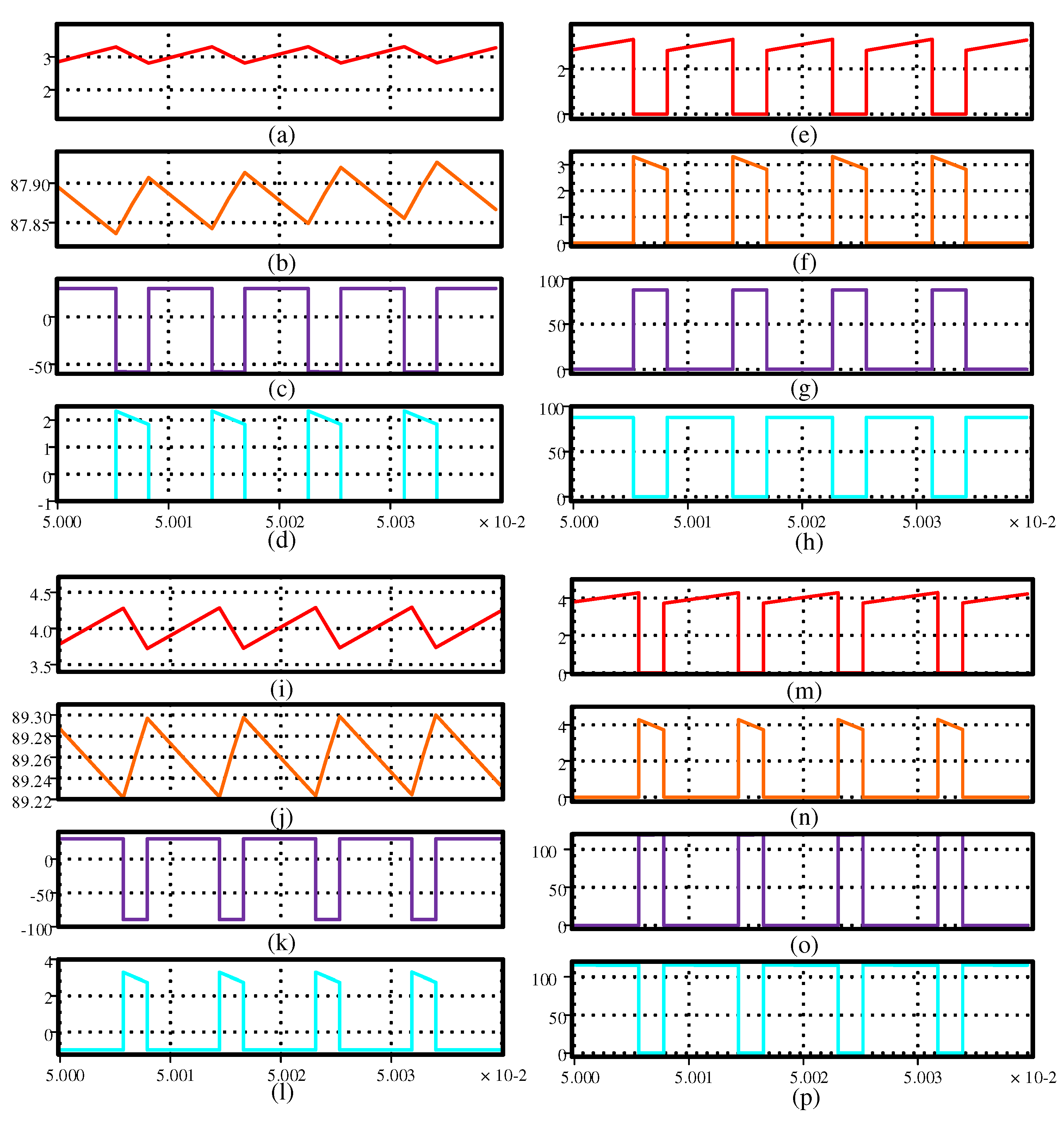

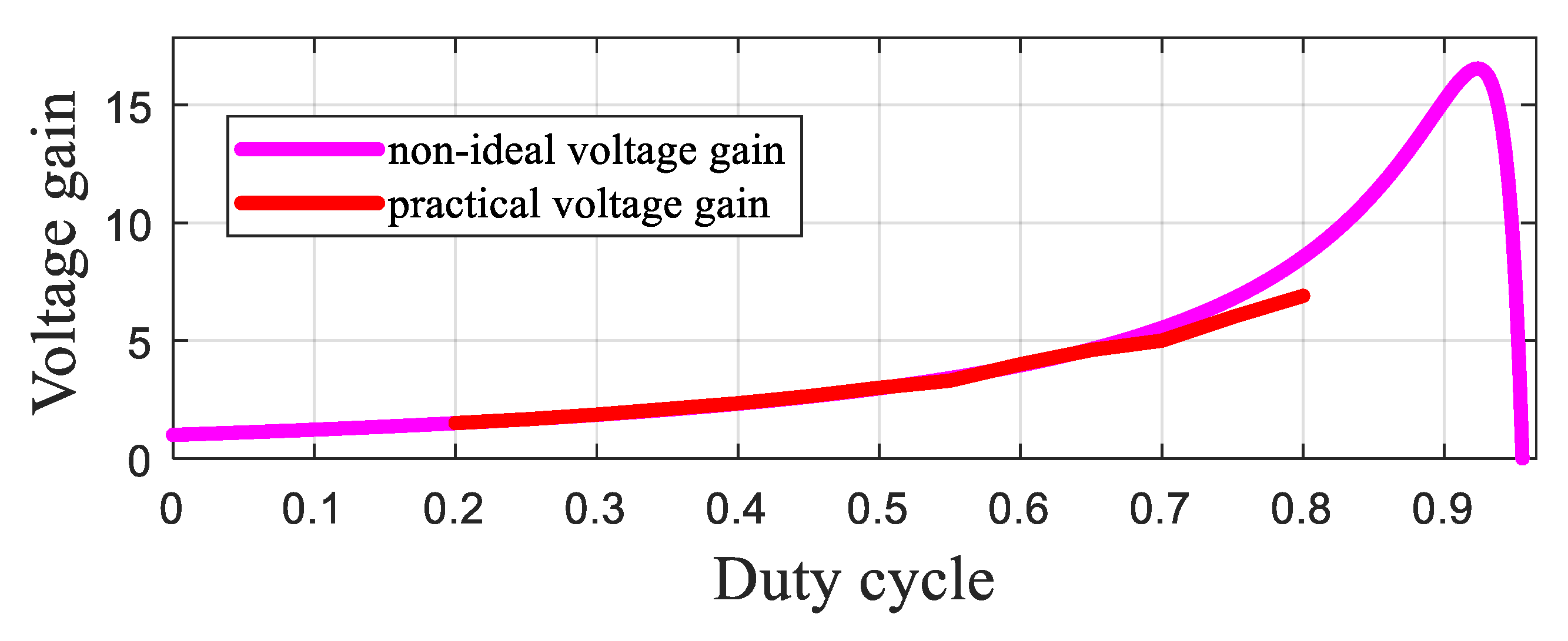

4. Non-Ideal Voltage Gain

The Relation of the Non-Ideal Voltage Gain

5. Efficiency

5.1. Mathematical Relations of the Efficiency

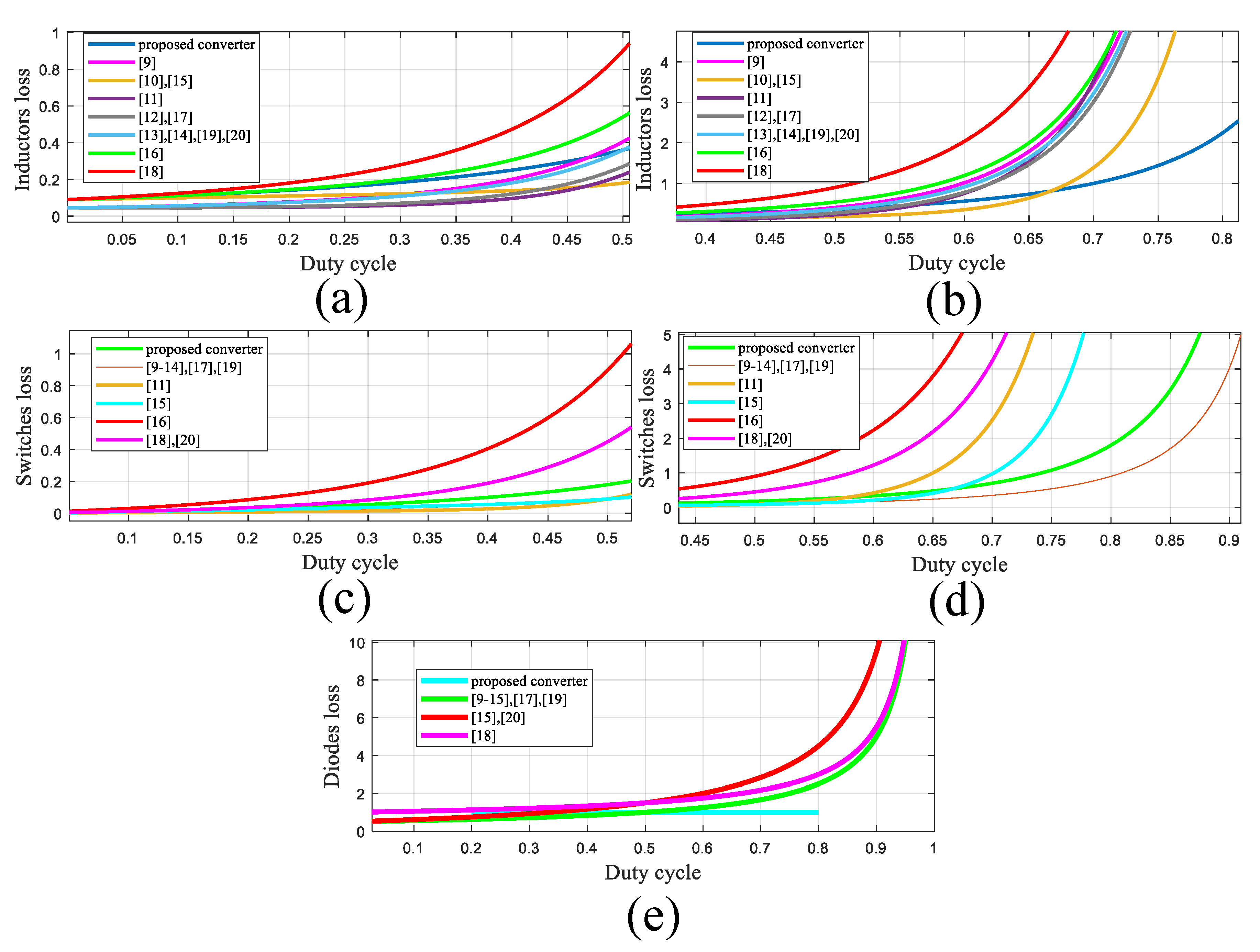

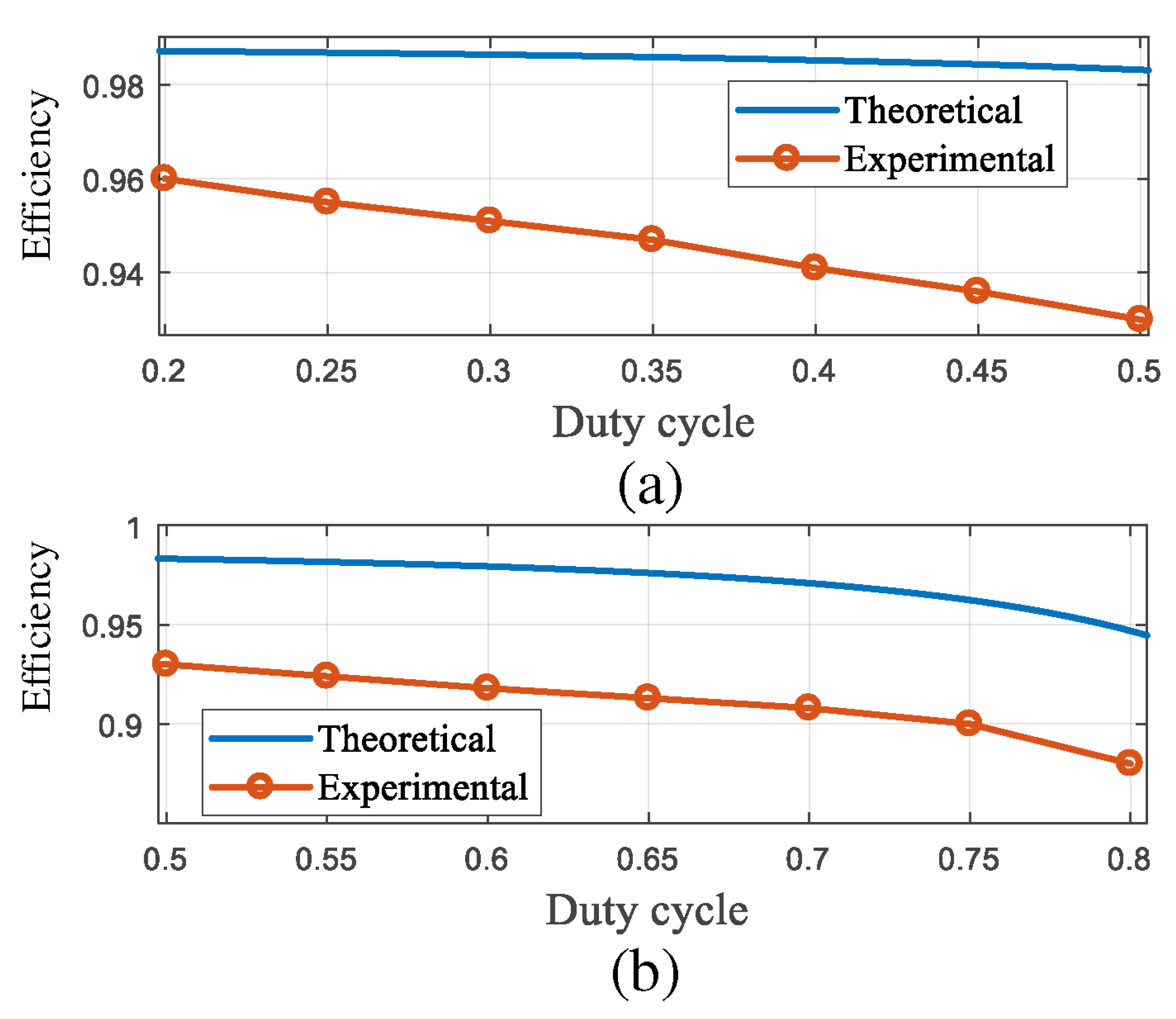

5.2. Comparison of the Various Losses of the Proposed Converter with the Other Step-Up Topologies While the Duty Cycle Is Varying and Output Power Is 90 W

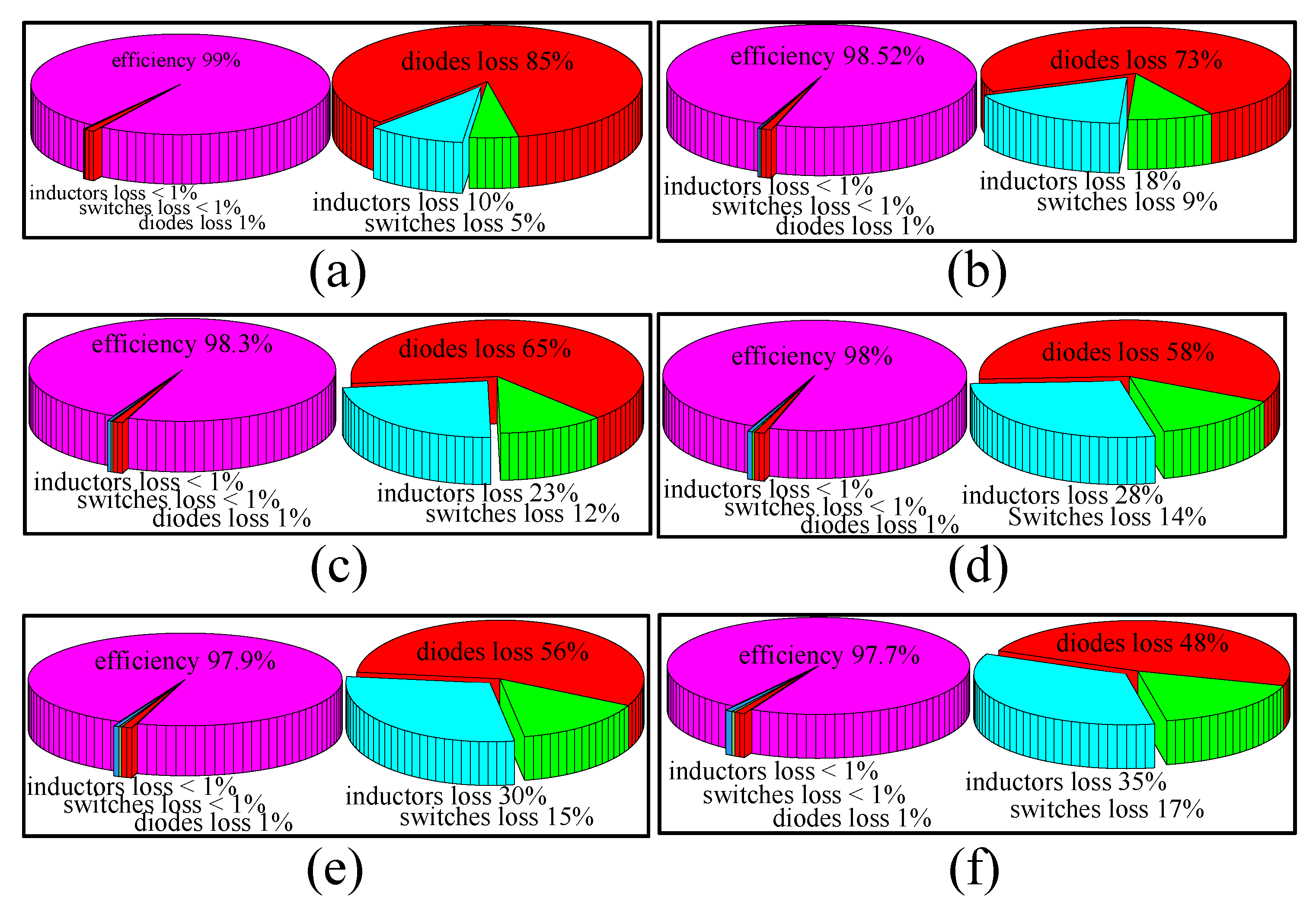

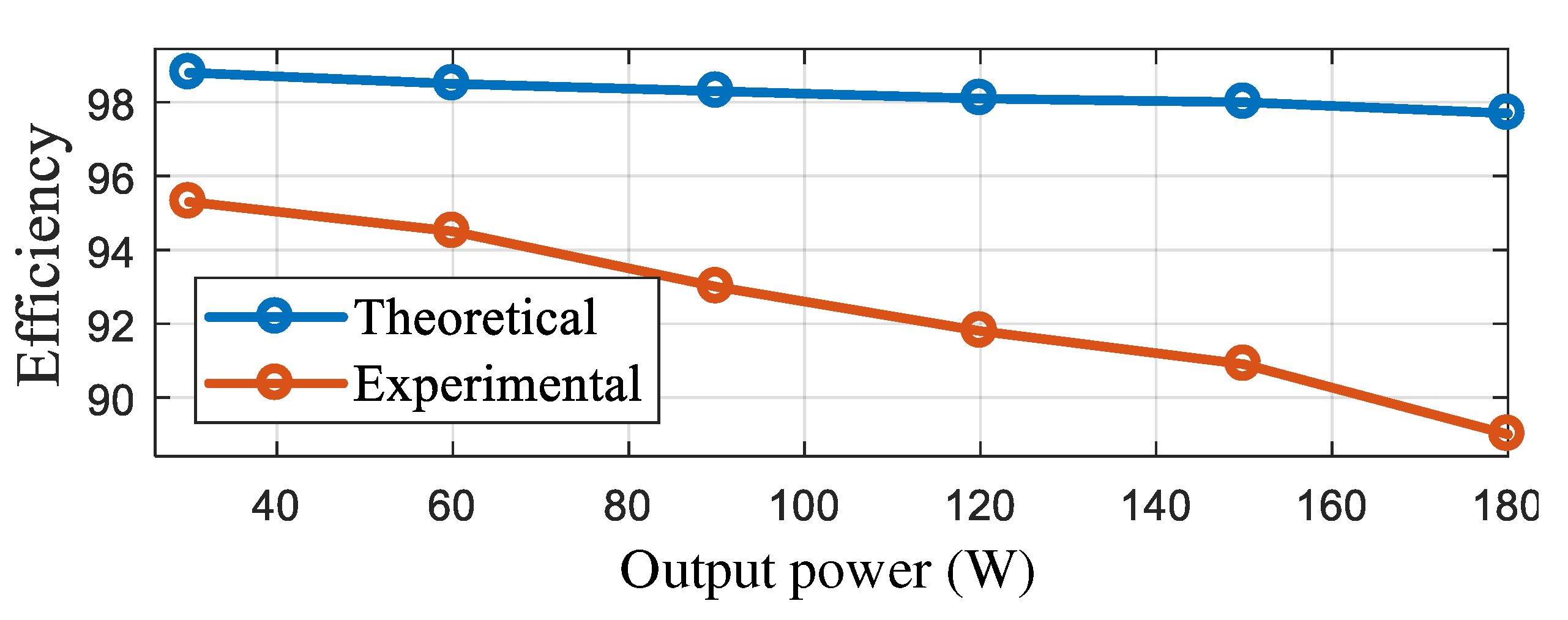

5.3. The Efficiency and Losses of the Proposed Converter for the Different Vales of the Output Power

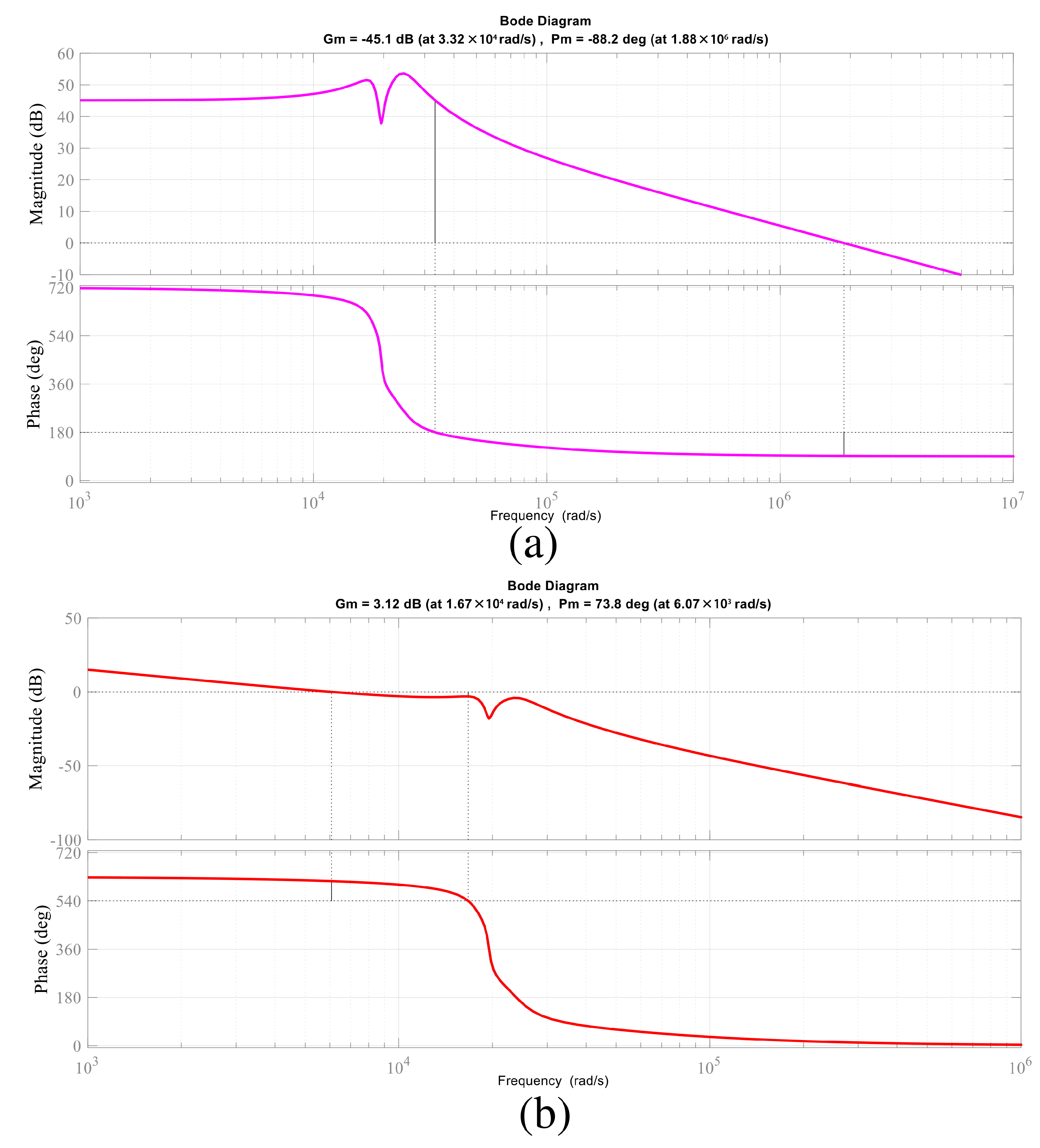

6. Small Signal Analysis

7. The Comparison of the Different Features of the Proposed Converter and Recently Suggested Topologies in an Operating Point

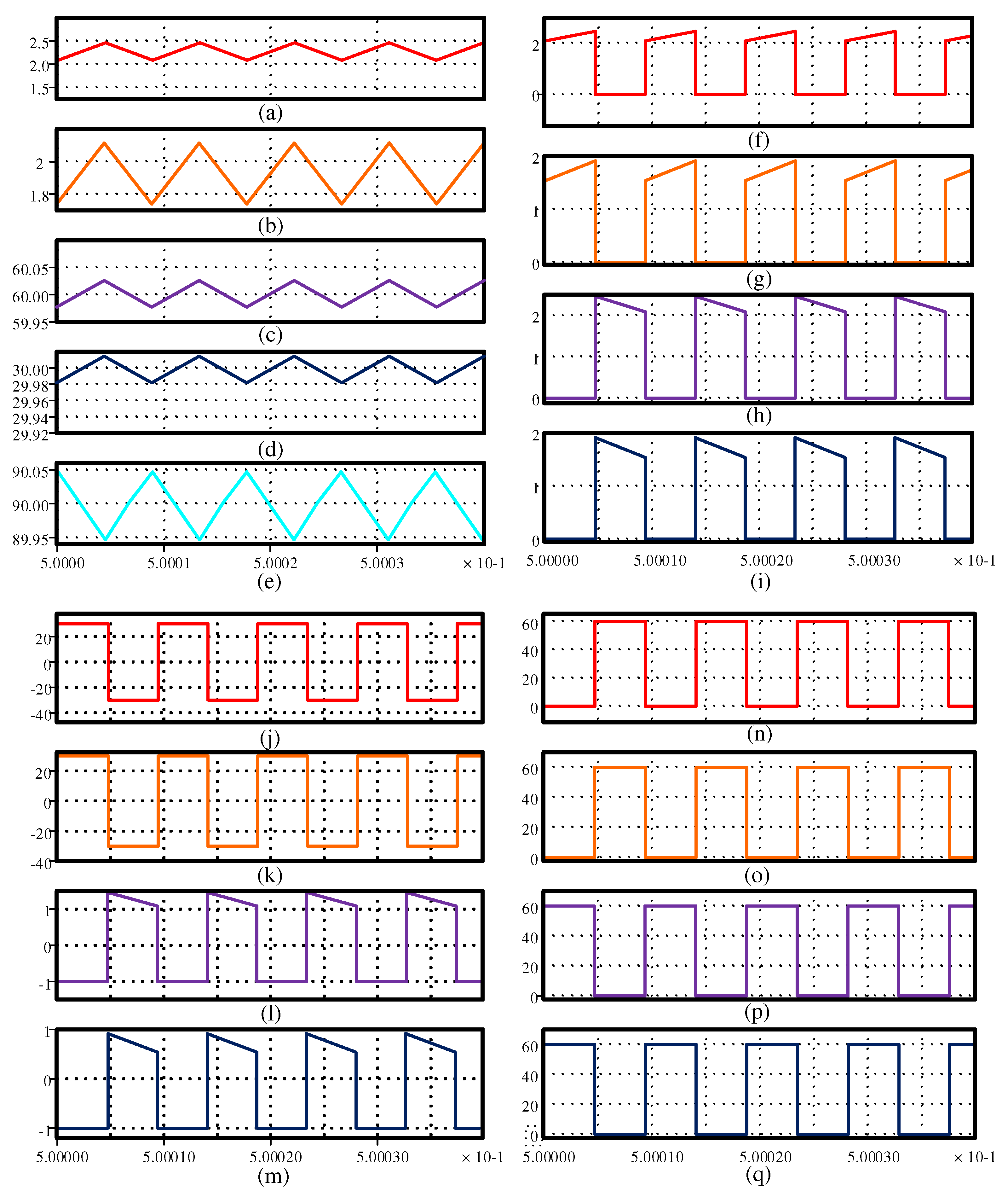

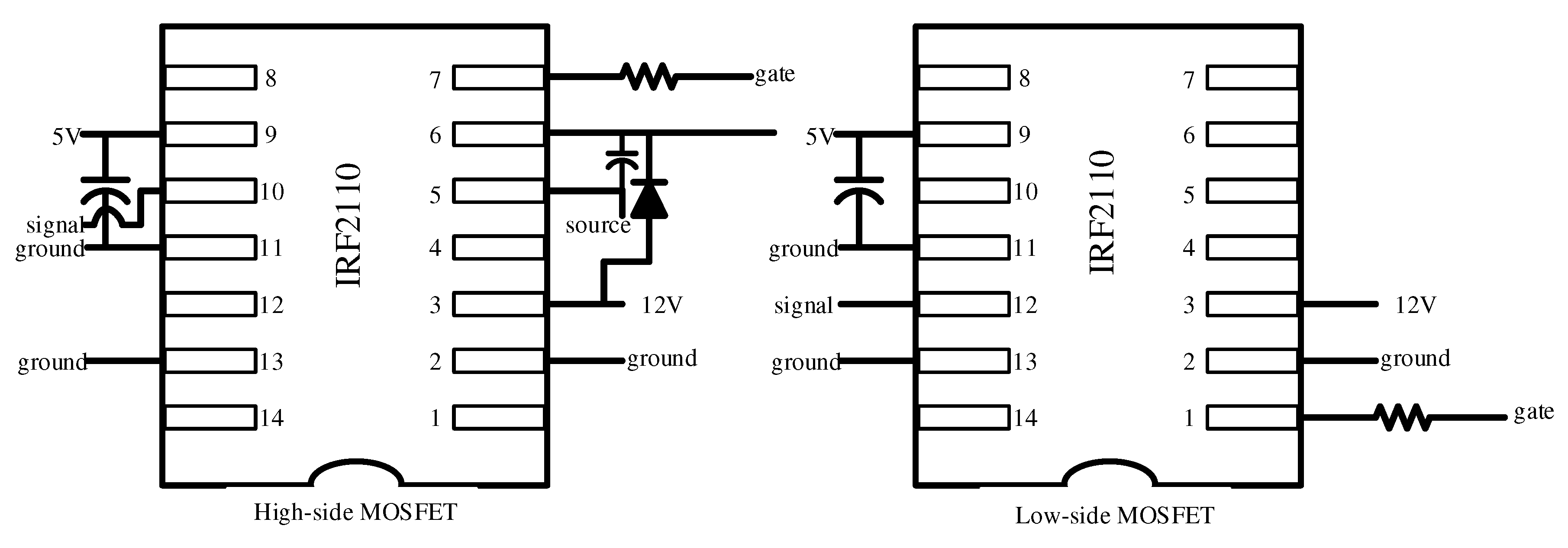

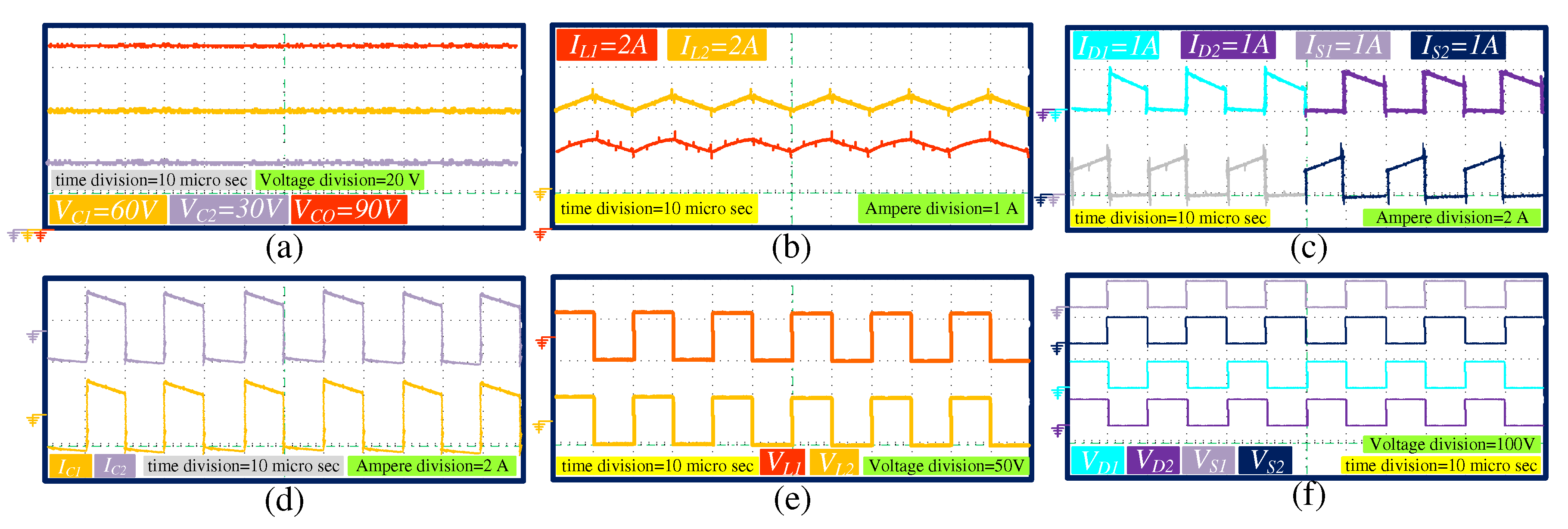

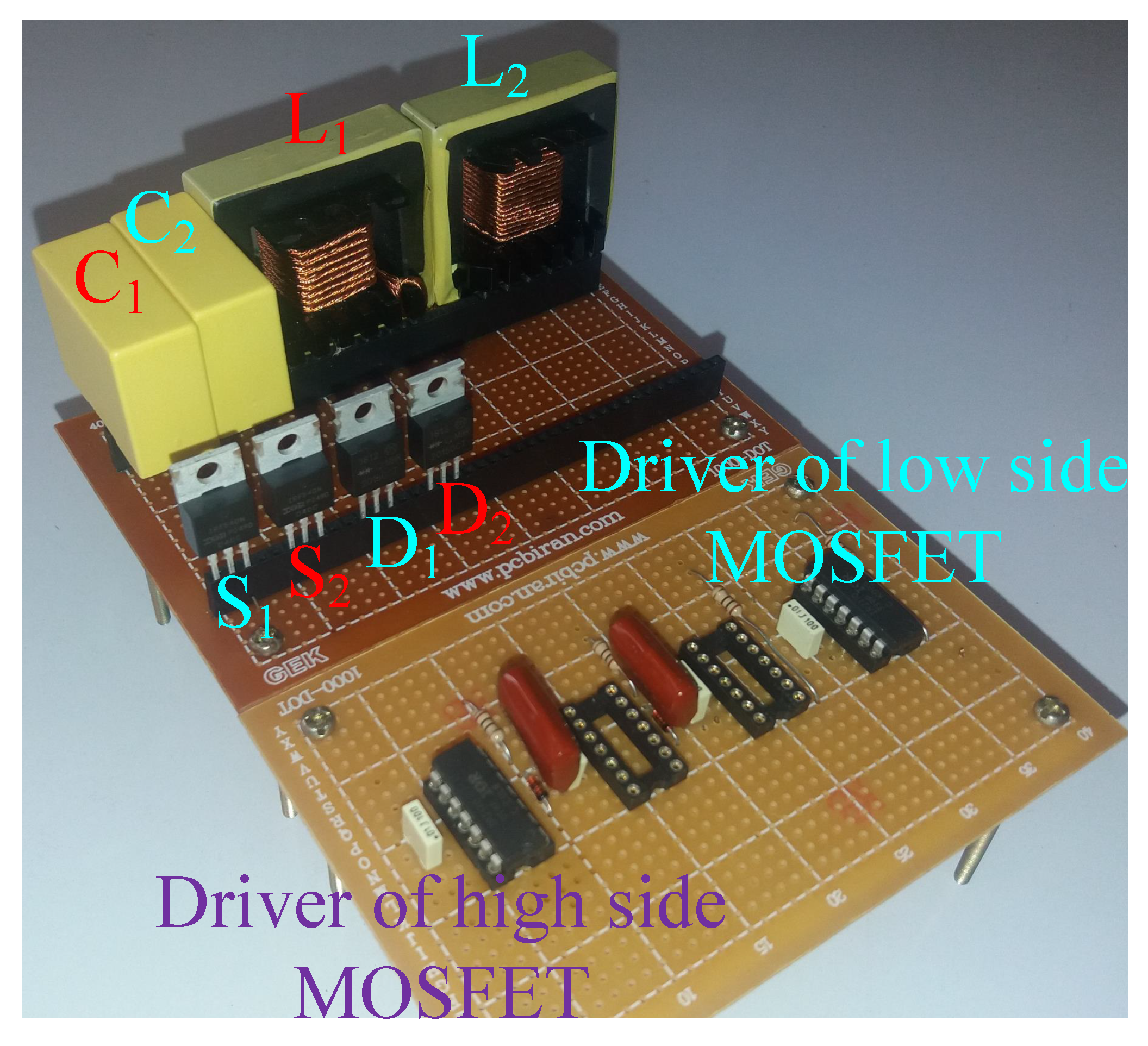

8. Simulation and Experimental Results

9. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Gopi, R.R.; Sreejith, S. Converter topologies in photovoltaic applications—A review. Renew. Sustain. Energy Rev. 2018, 94, 1–14. [Google Scholar] [CrossRef]

- Amir, A.; Amir, A.; Che, H.S.; Elkhateb, A.; Abd Rahim, N. Comparative analysis of high voltage gain DC-DC converter topologies for photovoltaic systems. Renew. Energy 2019, 136, 1147–1163. [Google Scholar] [CrossRef] [Green Version]

- Revathi, B.S.; Prabhakar, M. Non isolated high gain DC-DC converter topologies for PV applications—A comprehensive review. Renew. Sustain. Energy Rev. 2016, 66, 920–933. [Google Scholar] [CrossRef]

- Taghvaee, M.; Radzi, M.; Moosavain, S.; Hizam, H.; Marhaban, M.H. A current and future study on non-isolated DC–DC converters for photovoltaic applications. Renew. Sustain. Energy Rev. 2013, 17, 216–227. [Google Scholar] [CrossRef]

- Marjani, J.; Imani, A.; Hekmati, A.; Afjei, E. A new dual output DC-DC converter based on SEPIC and Cuk converters. In Proceedings of the 2016 International Symposium on Power Electronics, Electrical Drives, Automation and Motion (SPEEDAM), Capri, Italy, 1 August 2016; pp. 946–950. [Google Scholar]

- Gholizadeh, H.; Sharifi Shahrivar, R.; Hashemi, M.R.; Afjei, E.; A Gorji, S. Design and Implementation a Single-Switch Step-Up DC-DC Converter Based on Cascaded Boost and Luo Converters. Energies 2021, 14, 3584. [Google Scholar] [CrossRef]

- Tewari, N.; Sreedevi, V. A novel single switch DC-DC converter with high voltage gain capability for solar PV based power generation systems. Sol. Energy 2018, 171, 466–477. [Google Scholar] [CrossRef]

- Ghaderi, D.; Maroti, P.K.; Sanjeevikumar, P.; Holm-Nielsen, J.B.; Hossain, E.; Nayyar, A. A Modified Step-Up Converter with Small Signal Analysis-Based Controller for Renewable Resource Applications. Appl. Sci. 2020, 10, 102. [Google Scholar] [CrossRef] [Green Version]

- Almalaq, Y.; Matin, M. Three Topologies of a Non-Isolated High Gain Switched-Inductor Switched-Capacitor Step-Up Cuk Converter for Renewable Energy Applications. Electronics 2018, 7, 94. [Google Scholar] [CrossRef] [Green Version]

- Wu, Y.-E.; Hsiao, S.-L. Novel High-Efficiency Three-Port Bidirectional Step-Up/Step-Down DC–DC Converter for Photovoltaic Systems. Sustainability 2021, 13, 7913. [Google Scholar] [CrossRef]

- Meraj, M.; Bhaskar, M.S.; Reddy, B.P.; Iqbal, A. Non-Isolated DC–DC Power Converter With High Gain and Inverting Capability. IEEE Access 2021, 9, 62084–62092. [Google Scholar] [CrossRef]

- Abbasi, M.; Abbasi, E.; Li, L.; Tousi, B. Design and Analysis of a High-Gain Step-Up/Down Modular DC–DC Converter with Continuous Input Current and Decreased Voltage Stress on Power Switches and Switched-Capacitors. Sustainability 2021, 13, 5243. [Google Scholar] [CrossRef]

- Rajaei, A.; Shahparasti, M.; Nabinejad, A.; Savaghebi, M. A High Step-Up Partial Power Processing DC/DC T-Source Converter for UPS Application. Sustainability 2020, 12, 10464. [Google Scholar] [CrossRef]

- Forouzesh, M.; Siwakoti, Y.P.; Gorji, S.A.; Blaabjerg, F.; Lehman, B. Step-Up DC–DC Converters: A Comprehensive Review of Voltage-Boosting Techniques, Topologies, and Applications. IEEE Trans. Power Electron. 2017, 32, 9143–9178. [Google Scholar] [CrossRef]

- Gholizadeh, H.; Salehi, M.; Rafiee, Z.; Afjei, E.; Hamzeh, M. A Transformer less Quadratic Buck-Boost Converter with Wide Range of Output Voltage and Low Switch Stresses. In Proceedings of the 2020 11th Power Electronics, Drive Systems, and Technologies Conference (PEDSTC), Tehran, Iran, 4–6 February 2020; pp. 1–6. [Google Scholar]

- Miao, S.; Wang, F.; Ma, X. A New Transformerless Buck-Boost Converter With Positive Output Voltage. IEEE Trans. Ind. Electron. 2016, 63, 2965–2975. [Google Scholar] [CrossRef]

- Sarikhani, A.; Allahverdinejad, B.; Hamzeh, M.; Afjei, E. A continuous input and output current quadratic buck-boost converter with positive output voltage for photovoltaic applications. Sol. Energy 2019, 188, 19–27. [Google Scholar] [CrossRef]

- Gholizadeh, H.; Sarikhani, A.; Hamzeh, M. A Transformerless Quadratic Buck-Boost Converter Suitable for Renewable Applications. In Proceedings of the 2019 10th International Power Electronics, Drive Systems and Technologies Conference (PEDSTC), Shiraz, Iran, 25 April 2019; pp. 470–474. [Google Scholar]

- Babazadeh, Y.; Babaei, E.; Sabahi, M. A New Non-Isolated Buck-Boost Converter with High Voltage Gain and Positive Output Voltage for Renewable Energy Applications. In Proceedings of the 2019 10th International Power Electronics, Drive Systems and Technologies Conference (PEDSTC), Shiraz, Iran, 25 April 2019; pp. 201–206. [Google Scholar]

- Rosas-Caro, J.C.; Valdez-Resendiz, J.E.; Mayo-Maldonado, J.C.; Alejo-Reyes, A.; Valderrabano-Gonzalez, A. Quadratic buck–boost converter with positive output voltage and minimum ripple point design. IET Power Electron. 2018, 11, 1306–1313. [Google Scholar] [CrossRef]

- Rosas-Caro, J.C.; Sanchez, V.M.; Valdez-Resendiz, J.E.; Mayo-Maldonado, J.C.; Beltran-Carbajal, F.; Valderrabano-Gonzalez, A. Quadratic buck-boost converter with positive output-voltage and continuous input-current. In Proceedings of the 2018 International Conference on Electronics, Communications and Computers (CONIELECOMP), Cholula, Mexico, 21–23 February 2018; pp. 152–158. [Google Scholar]

- Totonchi, N.; Gholizadeh, H.; Afjei, E.; Hamzeh, M. A Novel Transformer less High Gain DC-DC Converter with Continuous Input Current and Suitable for Photo Voltaic Panels. In Proceedings of the 2020 11th Power Electronics, Drive Systems, and Technologies Conference (PEDSTC), Tehran, Iran, 4–6 February 2020; pp. 1–6. [Google Scholar]

- Gholizadeh, H.; Aboufazeli, S.; Rafiee, Z.; Afjei, E.; Hamzeh, M. A Non-Isolated High Gain DC-DC Converters with Positive Output Voltage and Reduced Current Stresses. In Proceedings of the 2020 11th Power Electronics, Drive Systems, and Technologies Conference (PEDSTC), Tehran, Iran, 4–6 February 2020; pp. 1–6. [Google Scholar]

- Garcia-Vite, P.M.; Soriano-Rangel, C.A.; Rosas-Caro, J.C.; Mancilla-David, F. A DC-DC converter with quadratic gain and input current ripple cancelation at a selectable duty cycle. Renew. Energy 2017, 101, 431–436. [Google Scholar] [CrossRef]

- Garcia-Vite, P.M.; Valdez-Resendiz, J.E.; Mayo-Maldonado, J.C.; Rosas-Caro, J.C.; Rosario Rivera-Espinosa, M.; Valderrabano-Gonzalez, A. Quadratic gain converter with output voltage ripple mitigation. In Proceedings of the 2017 IEEE Energy Conversion Congress and Exposition (ECCE), Cincinnati, OH, USA, 1–5 October 2017; pp. 2253–2259. [Google Scholar]

- Ding, S.; Wang, F. A New Negative Output Buck–Boost Converter with Wide Conversion Ratio. IEEE Trans. Ind. Electron. 2017, 64, 9322–9333. [Google Scholar] [CrossRef]

| Inductors Loss | Switches Conduction Loss | |

|---|---|---|

| proposed converters | ||

| [15] | ||

| [16] | ||

| [17] | ||

| [18] | ||

| [19] | ||

| [20] | ||

| [21] | ||

| [22] | ||

| [23] | ||

| [24] | ||

| [25] | ||

| [26] |

| Switching Loss of Switches | Diodes Loss | Duty Cycle | |

|---|---|---|---|

| proposed converters | 0.5 | ||

| [15] | 0.62 | ||

| [16] | 0.62 | ||

| [17] | 0.62 | ||

| [18] | 0.62 | ||

| [19] | 0.62 | ||

| [20] | 0.62 | ||

| [21] | 0.62 | ||

| [22] | 0.57 | ||

| [23] | 0.57 | ||

| [24] | 0.57 | ||

| [25] | 0.57 | ||

| [26] | 0.5 |

| proposed converter | ||||

| [15] | = 1 | 1 | = 1 | = 1.61 |

| [16] | = 1 | = 1.61 | = 1 | = 1.61 |

| [17] | = 2.68 | = 1.61 | = 1 | = 1.61 |

| [18] | = 1 | = 1.61 | = 1 | = 1.61 |

| [19] | = 1 | = 1.61 | = 1 | = 1.61 |

| [20] | = 1 | = 1.61 | = 1 | = 1.61 |

| [21] | = 1 | = 1.61 | = 1 | = 1.61 |

| [22] | = 1.32 | = 1.61 | = 0.75 | 1 |

| [23] | = 0.75 | = 1.61 | = 0.75 | = 1.75 |

| [24] | = 0.75 | 1 | = 0.75 | 1 |

| [25] | = 0.75 | = 1.75 | = 0.75 | = 1.75 |

| [26] | = 0.67 | = 1.33 | = 0.67 | = 1.33 |

| D | |||||

|---|---|---|---|---|---|

| proposed converter | 0.5 | ||||

| [15] | 1 | = 0.61 | = 0.61 | = 0.34 | 0.62 |

| [16] | 1 | = 0.61 | = 0.61 | = 0.34 | 0.62 |

| [17] | 1 | = 0.61 | = 0.61 | = 0.34 | 0.62 |

| [18] | 1 | = 0.61 | = 0.61 | = 0.34 | 0.62 |

| [19] | 1 | = 0.61 | = 0.61 | = 0.34 | 0.62 |

| [20] | 1 | = 0.61 | = 0.61 | = 0.34 | 0.62 |

| [21] | 1 | = 0.61 | = 0.61 | = 0.34 | 0.62 |

| [22] | = 1.43 | = 0.43 | = 0.75 | = 0.34 | 0.57 |

| [23] | D = 0.57 | = 0.43 | = 0.43 | = 0.34 | 0.57 |

| [24] | 1 | = 0.43 | = 0.75 | = 0.34 | 0.57 |

| [25] | D = 0.57 | = 0.43 | = 0.43 | = 0.34 | 0.57 |

| [26] | = 1.34 | = 0.34 | = 0.67 | = 0.34 | 0.5 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Rahimi, T.; Islam, M.R.; Gholizadeh, H.; Mahdizadeh, S.; Afjei, E. Design and Implementation of a High Step-Up DC-DC Converter Based on the Conventional Boost and Buck-Boost Converters with High Value of the Efficiency Suitable for Renewable Application. Sustainability 2021, 13, 10699. https://doi.org/10.3390/su131910699

Rahimi T, Islam MR, Gholizadeh H, Mahdizadeh S, Afjei E. Design and Implementation of a High Step-Up DC-DC Converter Based on the Conventional Boost and Buck-Boost Converters with High Value of the Efficiency Suitable for Renewable Application. Sustainability. 2021; 13(19):10699. https://doi.org/10.3390/su131910699

Chicago/Turabian StyleRahimi, Tohid, Md Rabiul Islam, Hossein Gholizadeh, Saeed Mahdizadeh, and Ebrahim Afjei. 2021. "Design and Implementation of a High Step-Up DC-DC Converter Based on the Conventional Boost and Buck-Boost Converters with High Value of the Efficiency Suitable for Renewable Application" Sustainability 13, no. 19: 10699. https://doi.org/10.3390/su131910699

APA StyleRahimi, T., Islam, M. R., Gholizadeh, H., Mahdizadeh, S., & Afjei, E. (2021). Design and Implementation of a High Step-Up DC-DC Converter Based on the Conventional Boost and Buck-Boost Converters with High Value of the Efficiency Suitable for Renewable Application. Sustainability, 13(19), 10699. https://doi.org/10.3390/su131910699