Operation of a UXE-Type 11-Level Inverter with Voltage-Balance Modulation Using NLC and ACO-Based SHE

Abstract

:1. Introduction

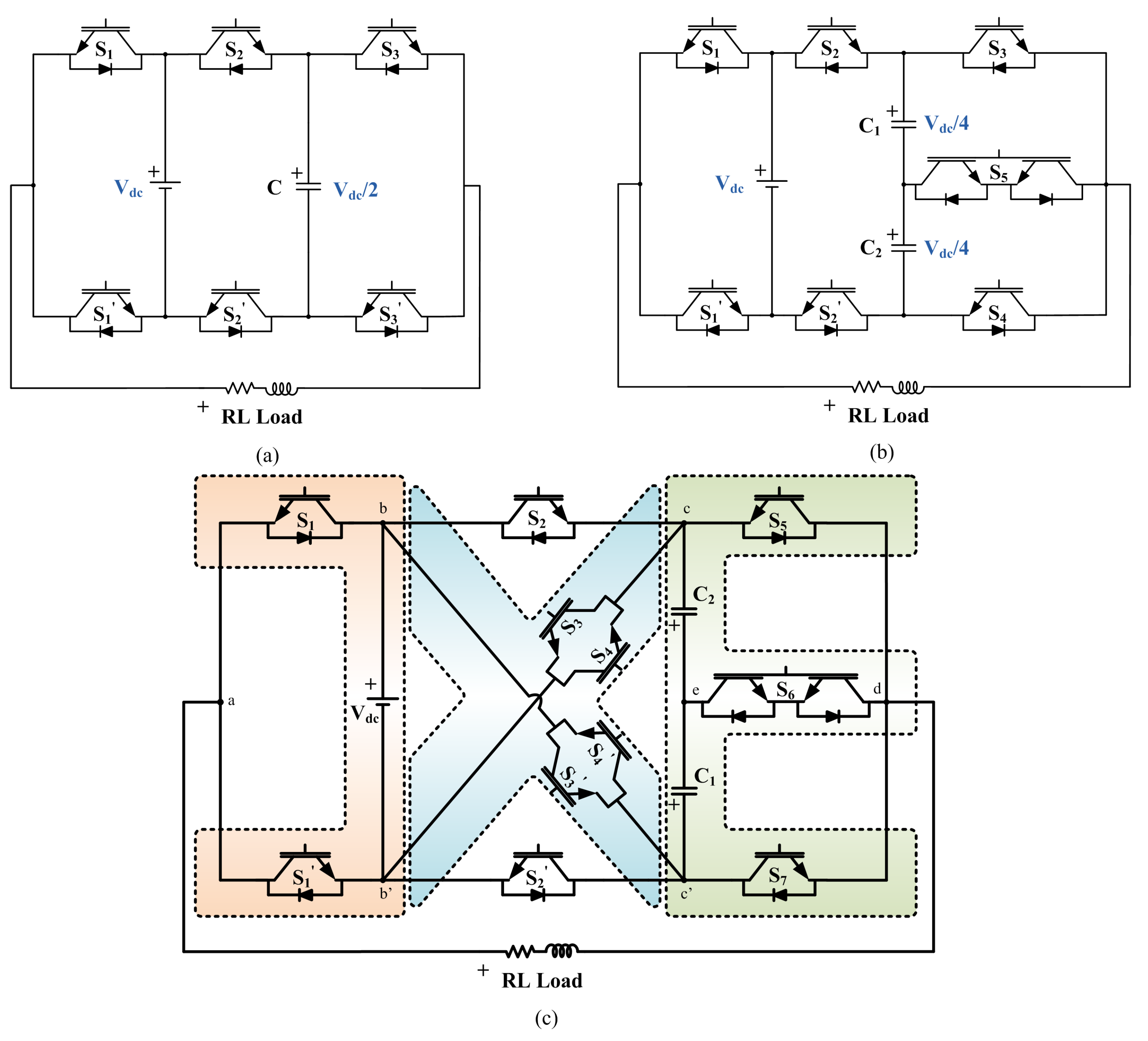

2. The UXE-Type Inverter

2.1. UXE-Type Inverter Circuit

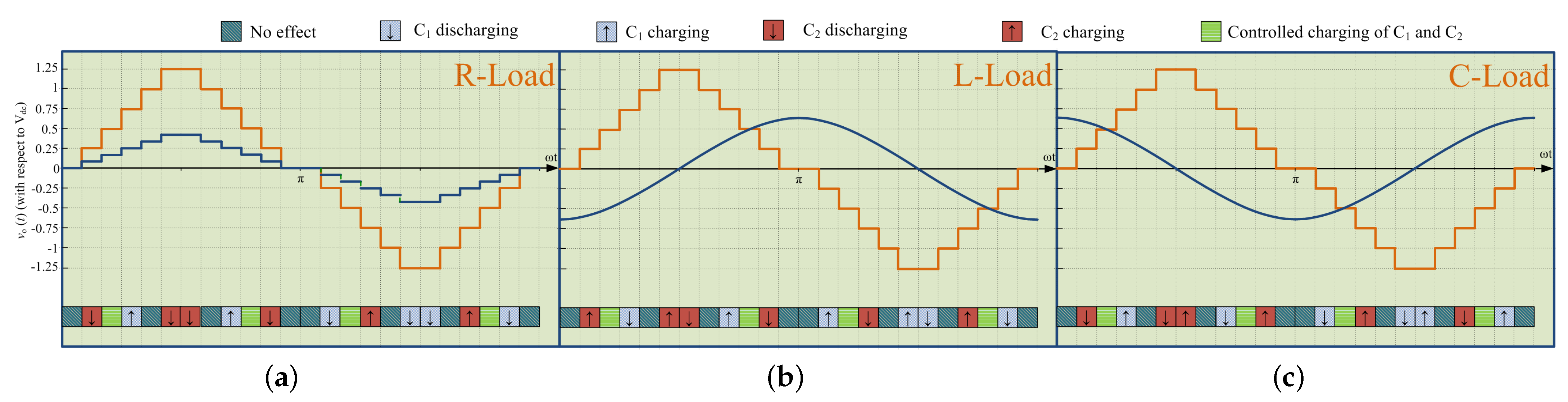

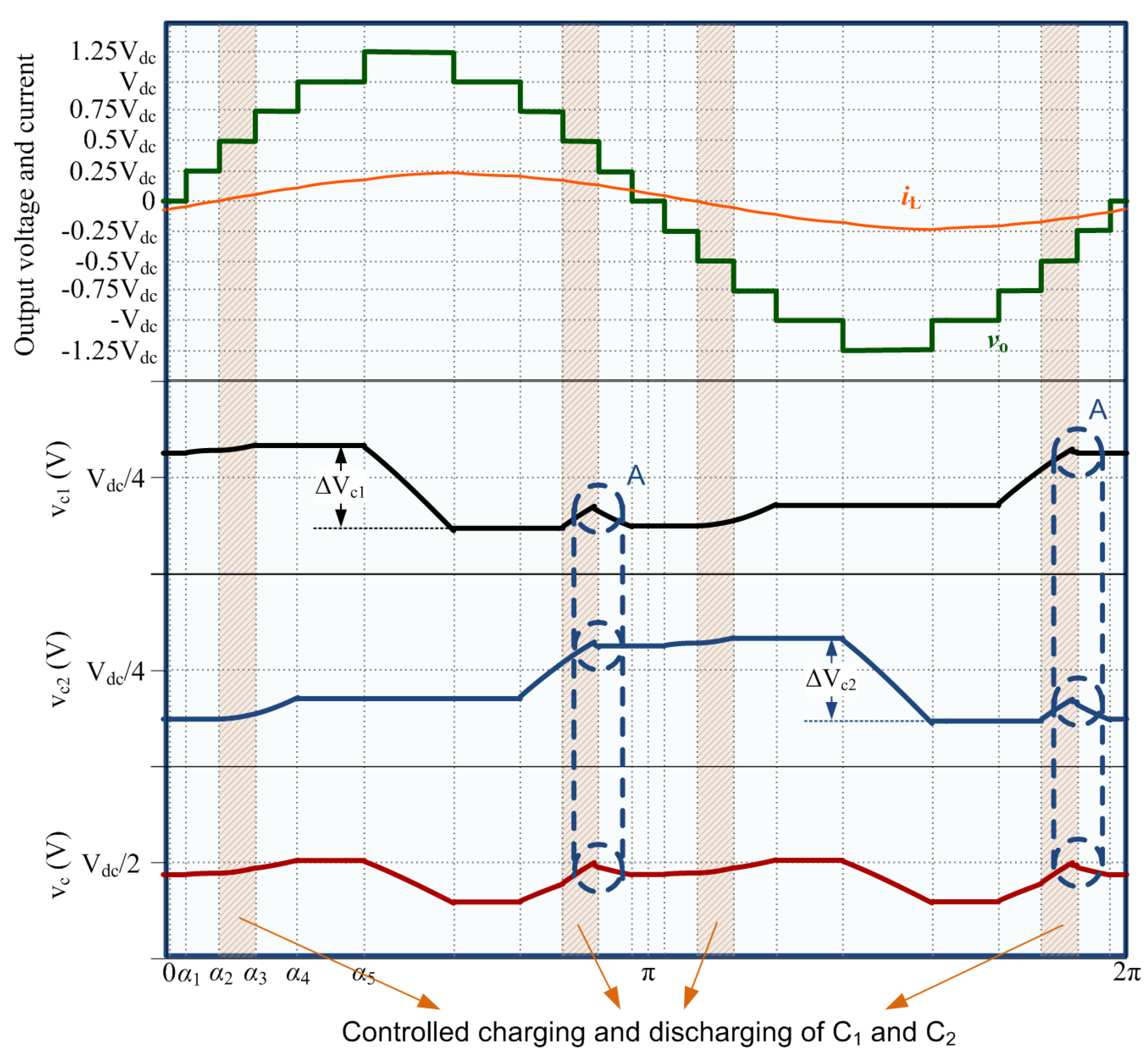

2.2. Voltage Balancing of and

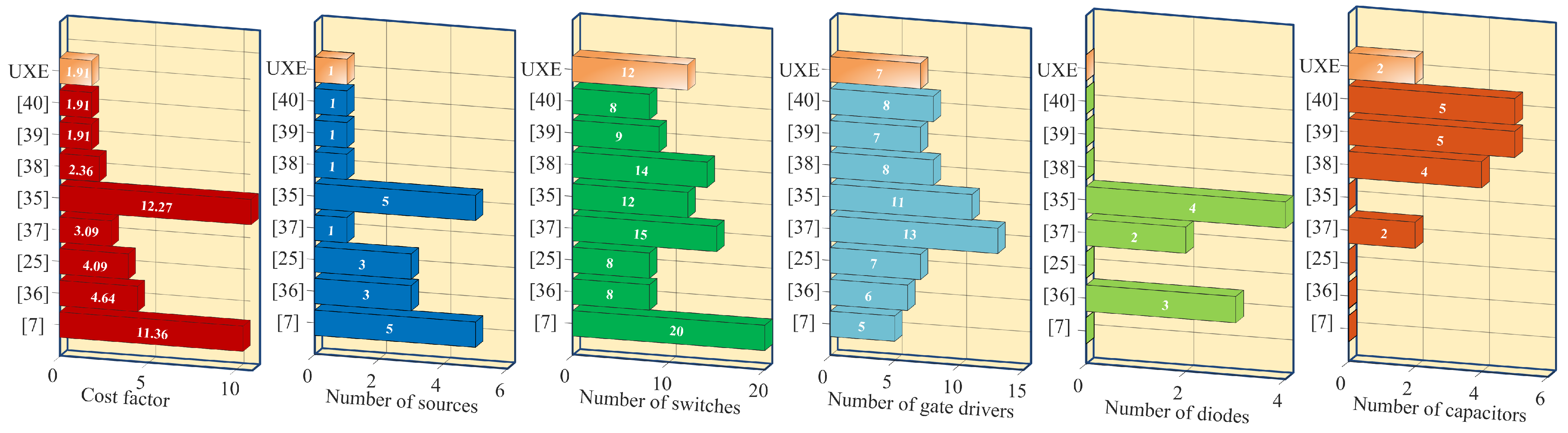

3. Comparison with Recent Inverters

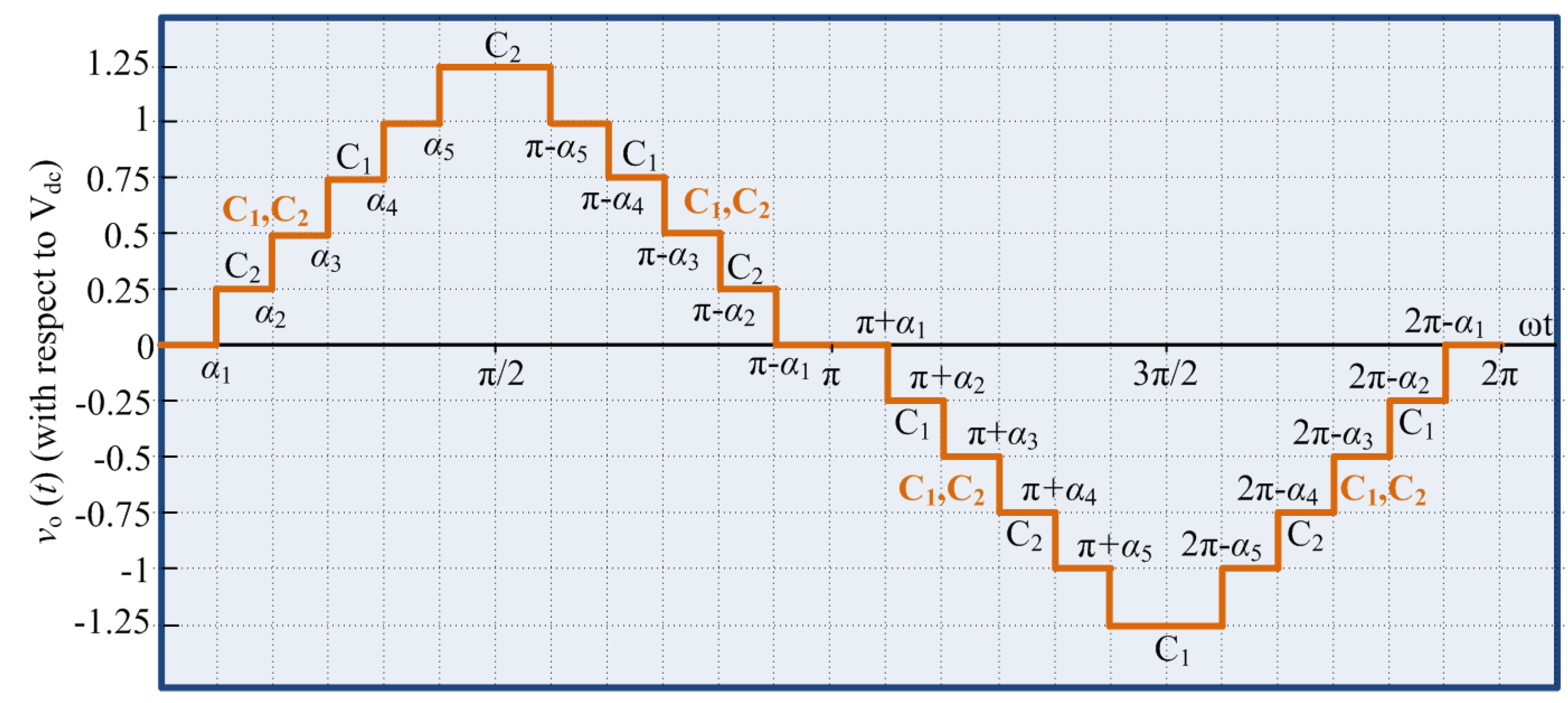

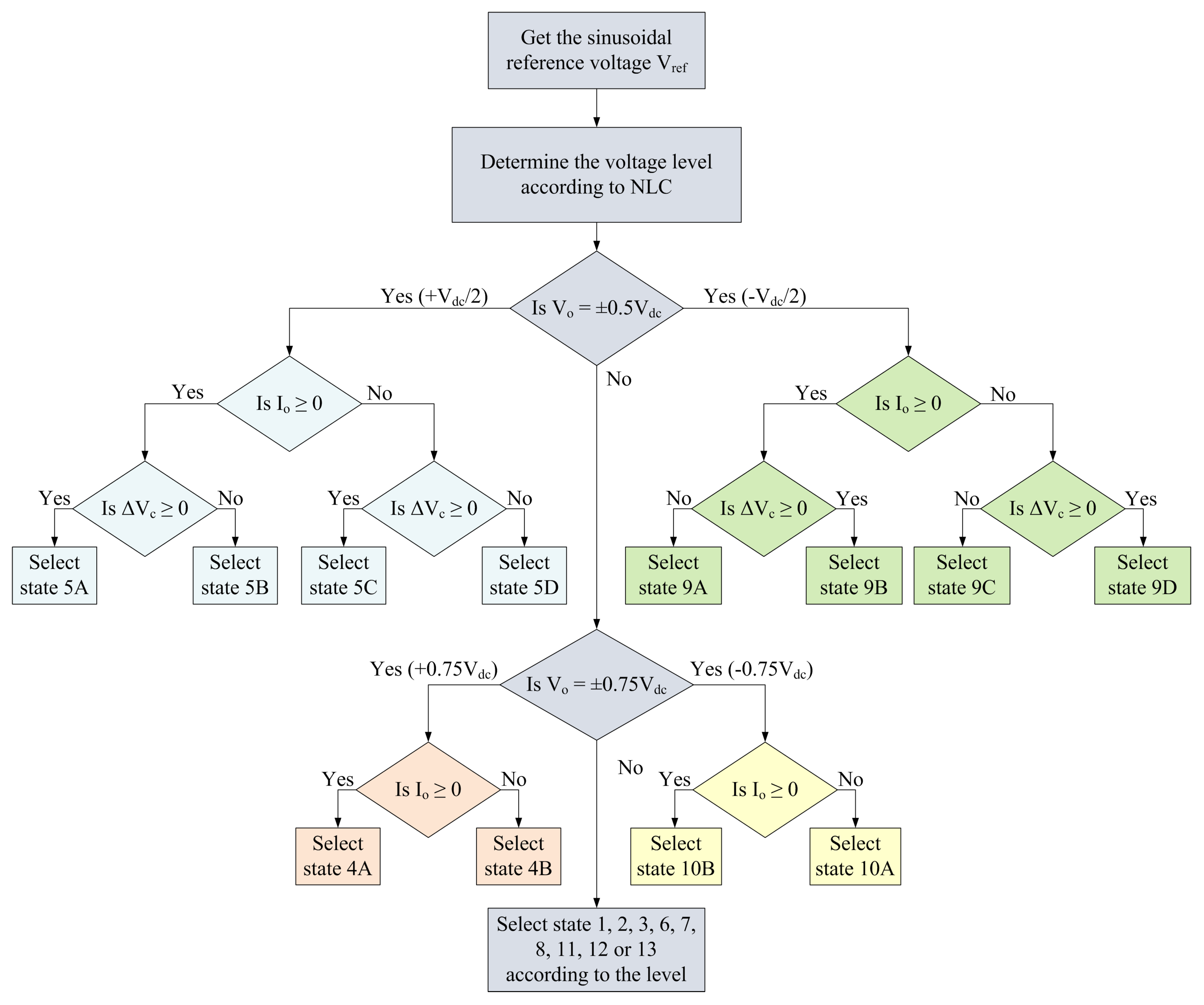

4. Modulation of the UXE-11 Inverter

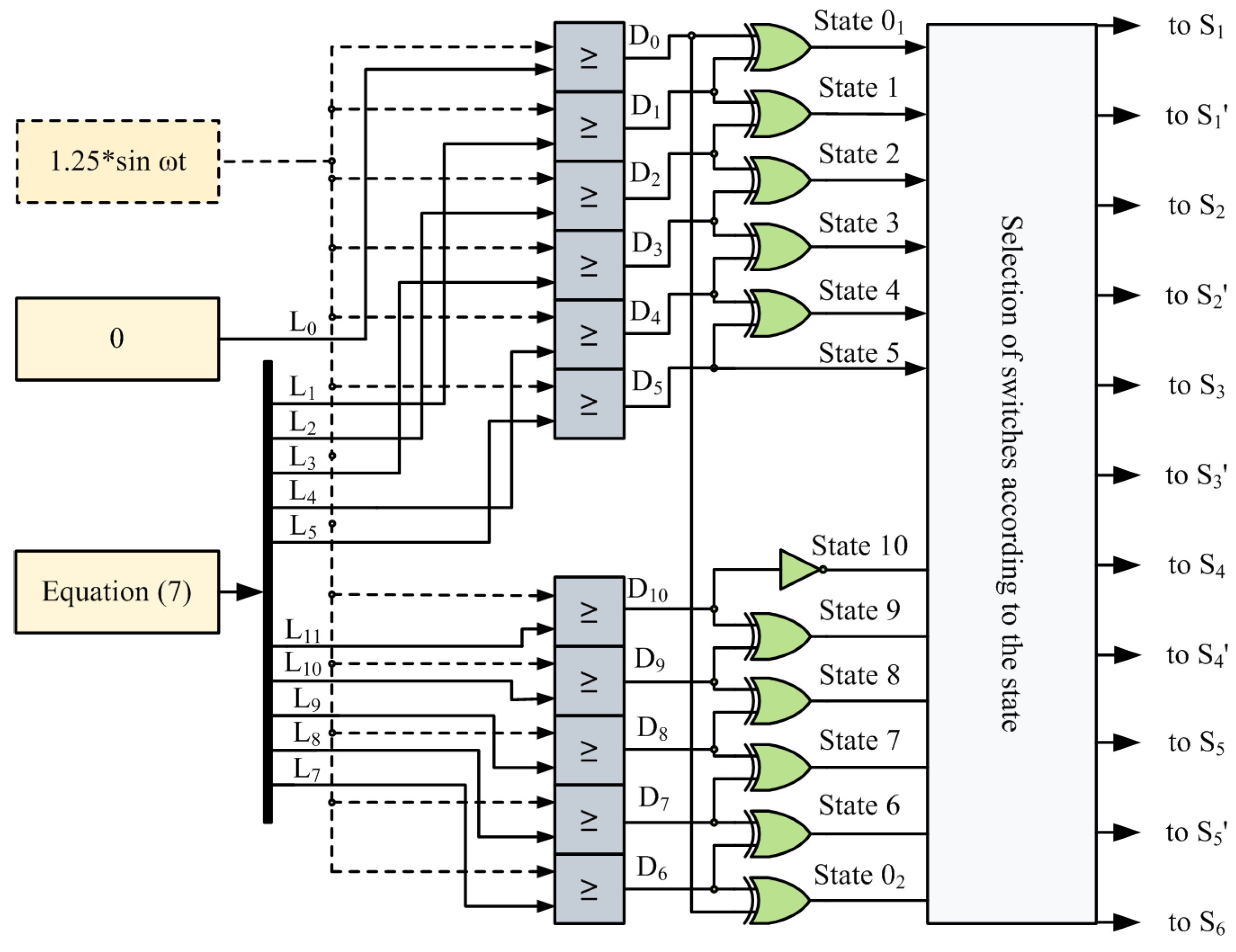

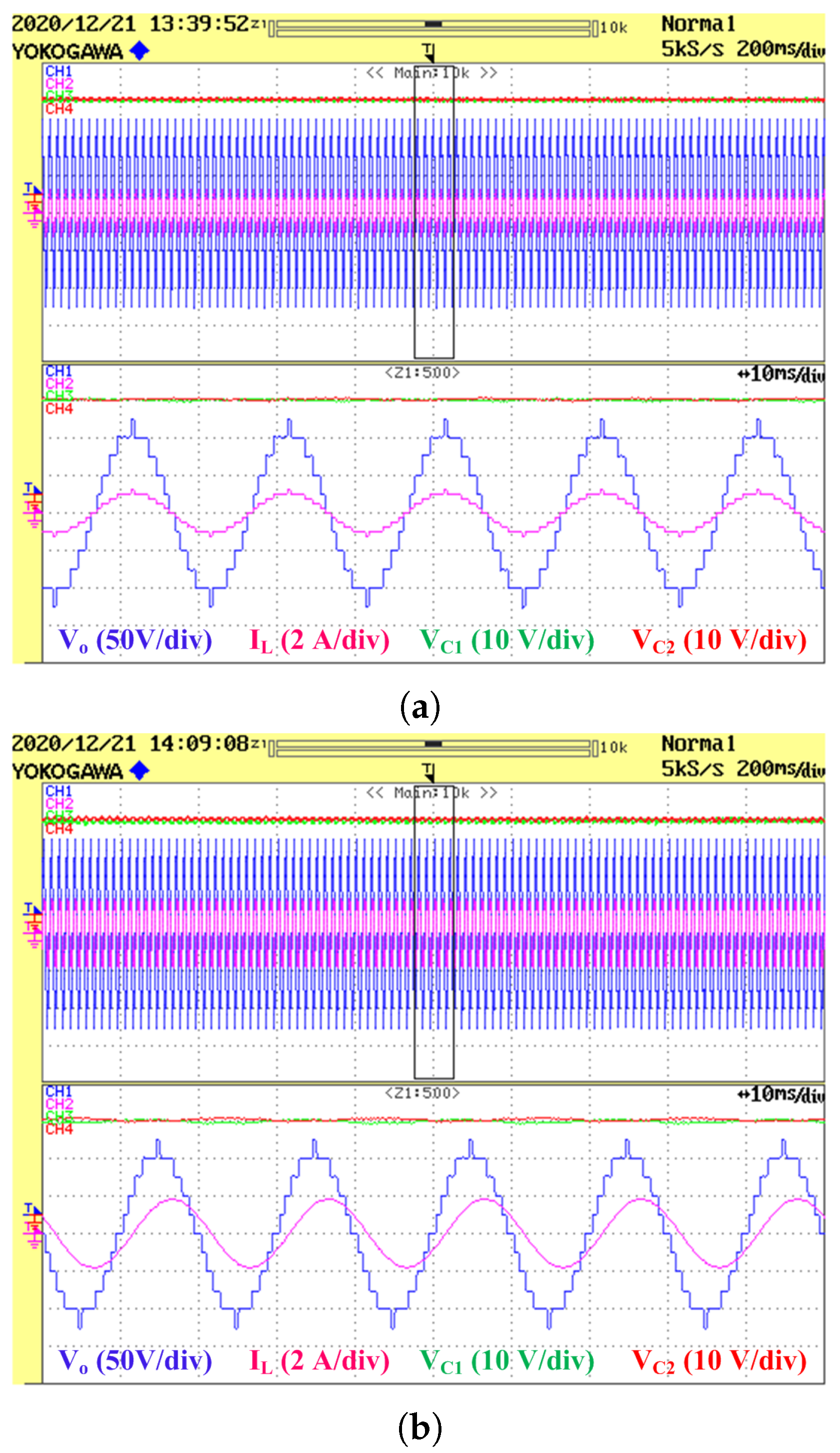

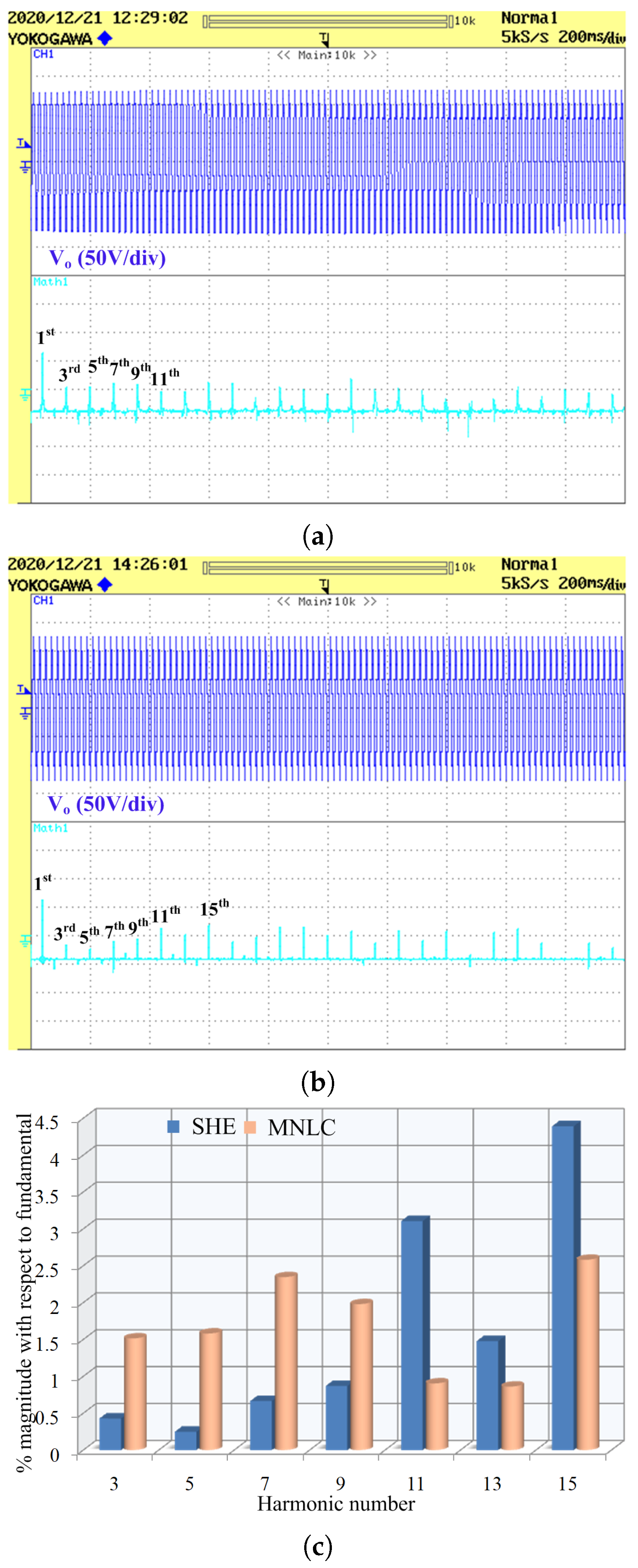

4.1. Nearest Level Control of UXE-11 Inverter

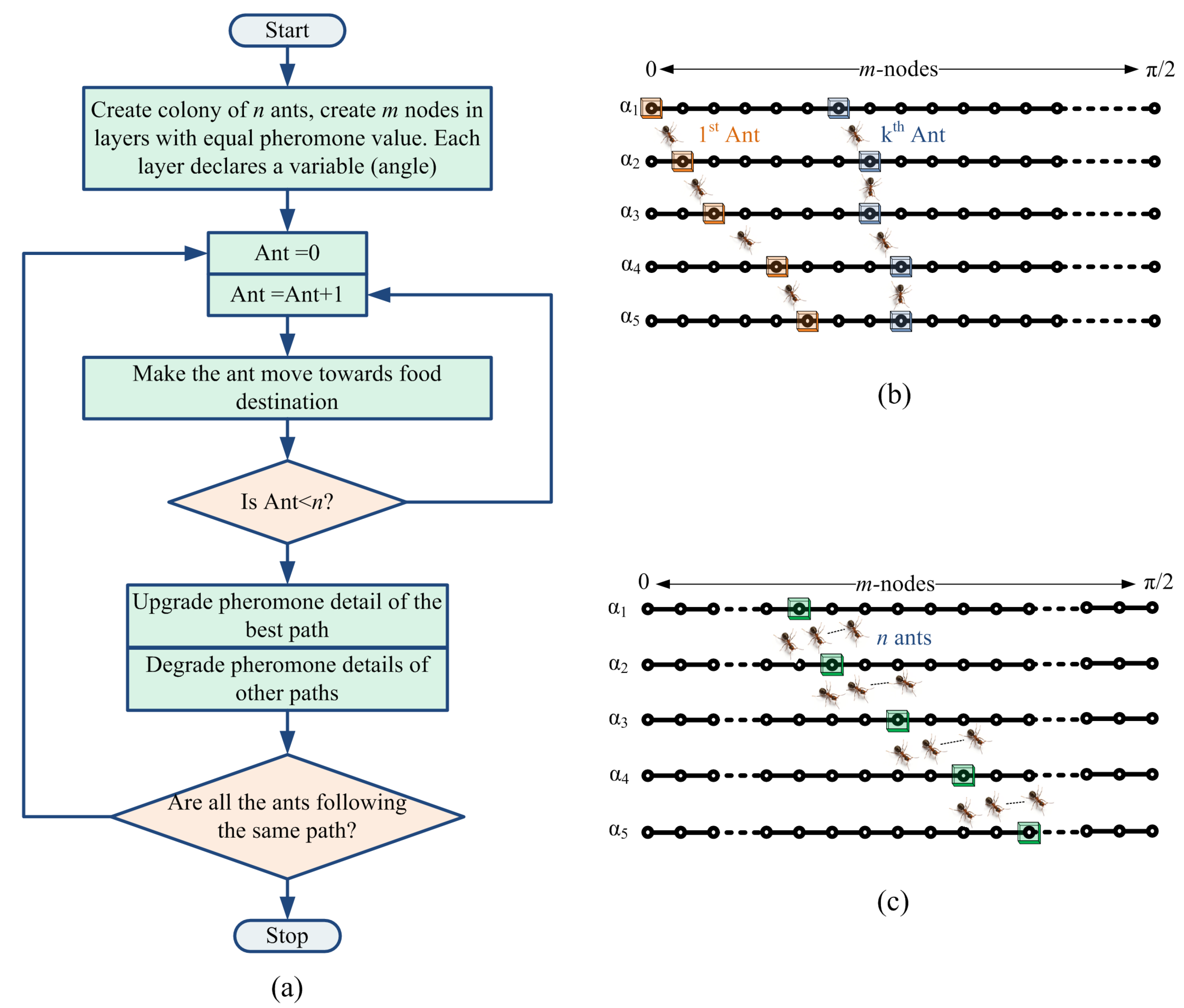

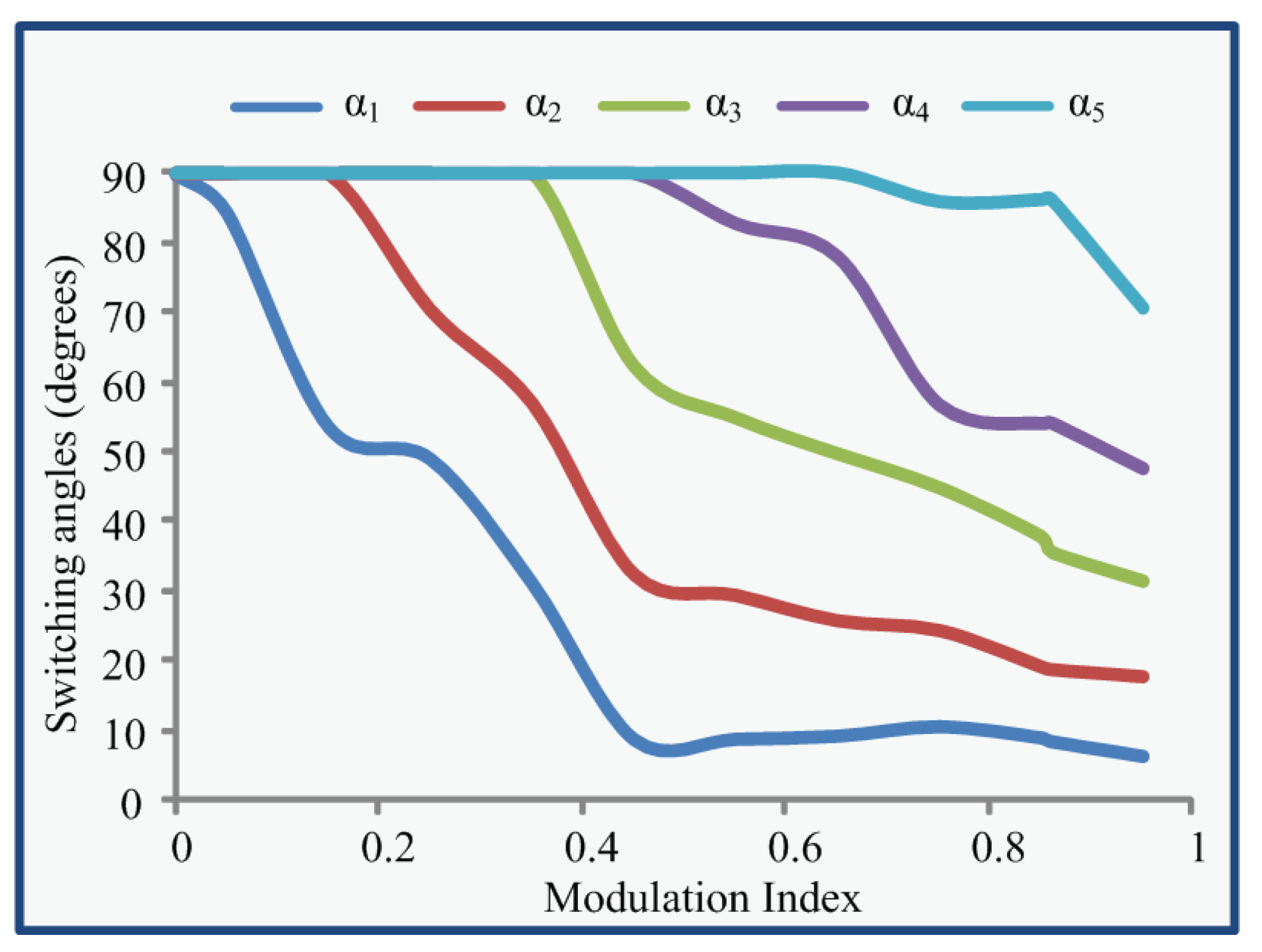

4.2. ACO-SHE Based Selective Harmonic Elimination

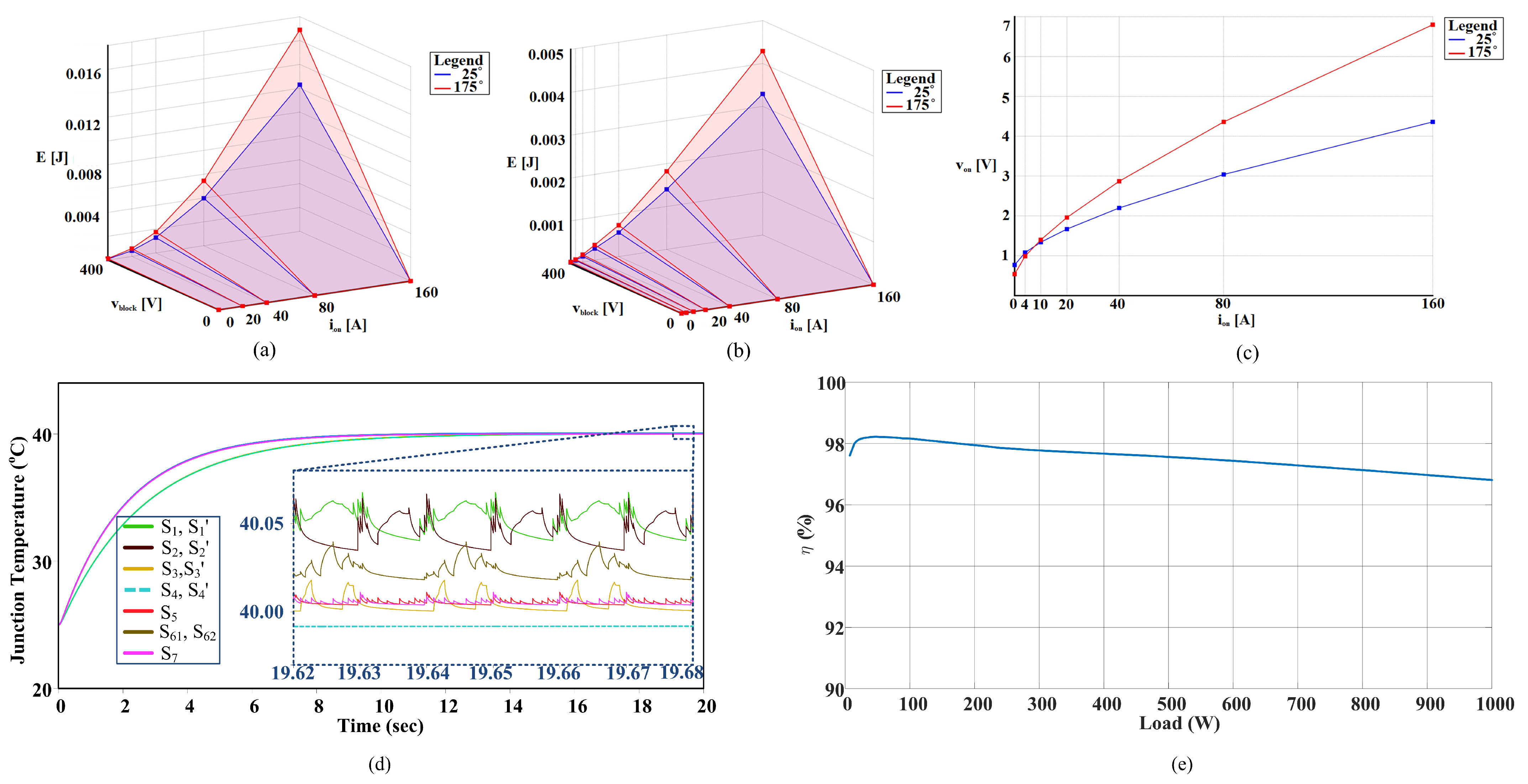

5. Analysis of Power Loss

5.1. Switching Losses

5.2. Conduction Losses

6. Hardware-in-the-Loop Validation

7. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Acknowledgments

Conflicts of Interest

References

- Mishra, N.; Singh, B. Modified reduced switch converter for grid interfaced systems. In Proceedings of the 2018 IEEE Industry Applications Society Annual Meeting (IAS), Portland, OR, USA, 23–27 September 2018; pp. 1–8. [Google Scholar] [CrossRef]

- Salem, A. Design, implementation and control of a SiC-Based T5MLC induction drive system. IEEE Access 2020, 8, 82769–82780. [Google Scholar] [CrossRef]

- Gupta, K.K.; Ranjan, A.; Bhatnagar, P.; Sahu, L.K.; Jain, S. Multilevel Inverter Topologies with Reduced Device Count: A Review. IEEE Trans. Power Electron. 2016, 31, 135–151. [Google Scholar] [CrossRef]

- Kouro, S.; Malinowski, M.; Gopakumar, K.; Pou, J.; Franquelo, L.G.; Wu, B.; Rodriguez, J.; Member, S.; Pérez, M.A.; Leon, J.I. Recent Advances and Industrial Applications of Multilevel Converters. IEEE Trans. Ind. Electron. 2010, 57, 2553–2580. [Google Scholar] [CrossRef]

- Lai, J.S.; Peng, F.Z. Multilevel Converters-A New Breed of Power Converters. IEEE Trans. Ind. Appl. 1996, 32, 509–517. [Google Scholar] [CrossRef]

- Bana, P.R.; Panda, K.P.; Naayagi, R.T.; Siano, R.; Panda, G. Recently Developed Reduced Switch Multilevel Inverter for Renewable Energy Integration and Drives Application: Topologies, Comprehensive Analysis and Comparative Evaluation. IEEE Access 2019, 7, 54888–54909. [Google Scholar] [CrossRef]

- Malinowski, M.; Gopakumar, K.; Rodriguez, J.; Perez, M.A. A survey on cascaded multilevel inverters. IEEE Trans. Ind. Electron. 2010, 57, 2197–2206. [Google Scholar] [CrossRef]

- Salem, A.; Khang, H.V.; Robbersmyr, K.G.; Norambuena, M.; Rodriguez, J. Voltage Source Multilevel Inverters with Reduced Device Count: Topological Review and Novel Comparative Factors. IEEE Trans. Power Electron. 2021, 36, 2720–2747. [Google Scholar] [CrossRef]

- Ounejjar, Y.; Al-Haddad, K.; Grégoire, L.A. Packed U Cells Multilevel Converter Topology: Theoretical Study and Experimental Validation. IEEE Trans. Ind. Electron. 2011, 58, 1294–1306. [Google Scholar] [CrossRef]

- Vahedi, H.; Sharifzadeh, M.; Al-Haddad, K. Modified Seven-Level Pack U-Cell Inverter for Photovoltaic Applications. IEEE J. Emerg. Sel. Top. Power Electron. 2018, 6, 1508–1516. [Google Scholar] [CrossRef]

- Mohamed Ali, J.S.; Krishnasamy, V. Compact Switched Capacitor Multilevel Inverter (CSCMLI) with Self-Voltage Balancing and Boosting Ability. IEEE Trans. Power Electron. 2019, 34, 4009–4013. [Google Scholar] [CrossRef]

- Siddique, M.D.; Sathik, J.M.A.; Mekhilef, S.; Mustafa, A.; Sandeep, N.; Almakhles, D. Reduce Switch Count Based Single Source 7L Boost Inverter Topology. IEEE Trans. Circuits Syst. II Express Briefs 2020, 67, 3252–3256. [Google Scholar] [CrossRef]

- Roy, T.; Sadhu, P.K.; Dasgupta, A. Cross-Switched Multilevel Inverter Using Novel Switched Capacitor Converters. IEEE Trans. Ind. Electron. 2019, 66, 8521–8532. [Google Scholar] [CrossRef]

- Saeedian, M.; Adabi, M.E.; Hosseini, S.M.; Adabi, J.; Pouresmaeil, E. A Novel Step-Up Single Source Multilevel Inverter: Topology, Operating Principle, and Modulation. IEEE Trans. Power Electron. 2019, 34, 3269–3282. [Google Scholar] [CrossRef] [Green Version]

- Siddique, M.D.; Mekhilef, S.; Shah, N.M.; Sarwar, A.; Tayyab, M.; Ansari, M.K. Low Switching Frequency Based Asymmetrical Multilevel Inverter Topology with Reduced Switch Count. IEEE Access 2019, 7, 86374–86383. [Google Scholar] [CrossRef]

- Lodi, K.A.; Ali, M.; Tariq, M.; Meraj, M.; Iqbal, A.; Chakrabortty, R.K.; Ryan, M.J. Modulation with Metaheuristic Approach for Cascaded-MPUC49 Asymmetrical Inverter with Boosted Output. IEEE Access 2020, 8, 96867–96877. [Google Scholar] [CrossRef]

- Mishra, N.; Yadav, S.K.; Singh, B.; Padmanaban, S.; Blaabjerg, F. Binary-Quintuple Progression Based Twelve Switch Twenty-Five Level Converter with Nearest Level Modulation Technique for Grid-Tied and Standalone. IEEE Trans. Ind. Appl. 2020, 57, 3214–3223. [Google Scholar] [CrossRef]

- Sharifzadeh, M.; Al-Haddad, K. Packed E-Cell (PEC) Converter Topology Operation and Experimental Validation. IEEE Access 2019, 7, 93049–93061. [Google Scholar] [CrossRef]

- Kim, K.M.; Han, J.K.; Moon, G.W. A High Step-Up Switched-Capacitor 13-Level Inverter with Reduced Number of Switches. IEEE Trans. Power Electron. 2020, 36, 2505–2509. [Google Scholar] [CrossRef]

- Sotoodeh, P.; Miller, R.D. Design and implementation of an 11-level inverter with FACTS capability for distributed energy systems. IEEE J. Emerg. Sel. Top. Power Electron. 2014, 2, 87–96. [Google Scholar] [CrossRef]

- Saggu, T.S.; Singh, L.; Gill, B.; Member, S. Harmonics Mitigation in a Steel Industry Using 11-Level Cascaded Multilevel Inverter-Based DSTATCOM. Can. J. Electr. Comput. Eng. 2017, 40, 110–115. [Google Scholar]

- Routray, A.; Kumar Singh, R.; Mahanty, R. Harmonic Minimization in Three-Phase Hybrid Cascaded Multilevel Inverter Using Modified Particle Swarm Optimization. IEEE Trans. Ind. Inform. 2019, 15, 4407–4417. [Google Scholar] [CrossRef]

- Routray, A.; Singh, R.K.; Mahanty, R. Harmonic Reduction in Hybrid Cascaded Multilevel Inverter Using Modified Grey Wolf Optimization. IEEE Trans. Ind. Appl. 2020, 56, 1827–1838. [Google Scholar] [CrossRef]

- Shuvo, S.; Hossain, E.; Islam, T.; Akib, A.; Padmanaban, S.; Khan, M.Z.R. Design and Hardware Implementation Considerations of Modified Multilevel Cascaded H-Bridge Inverter for Photovoltaic System. IEEE Access 2019, 7, 16504–16524. [Google Scholar] [CrossRef]

- Siddique, M.D.; Mekhilef, S.; Shah, N.M.; Memon, M.A. Optimal Design of a New Cascaded Multilevel Inverter Topology with Reduced Switch Count. IEEE Access 2019, 7, 24498–24510. [Google Scholar] [CrossRef]

- Sharifzadeh, M.; Babaie, M.; Sebaaly, F.; Mehrasa, M.; Chouinard, G.; Al-Haddad, K. Low Switching Frequency Operation of PEC9 Multilevel Inverter Using Modified SHM-PWM. In Proceedings of the IECON 2020: The 46th Annual Conference of the IEEE Industrial Electronics Society, Singapore, 18–21 October 2020; pp. 4215–4220. [Google Scholar]

- Taheri, A.; Rasulkhani, A.; Ren, H.P. An Asymmetric Switched Capacitor Multilevel Inverter with Component Reduction. IEEE Access 2019, 7, 127166–127176. [Google Scholar] [CrossRef]

- Al-Hitmi, M.; Ahmad, S.; Iqbal, A.; Padmanaban, S.; Ashraf, I. Selective Harmonic Elimination in a Wide Modulation Range using Modified Newton-Raphson and Pattern Generation Methods for a Multilevel Inverter. Energies 2018, 11, 458. [Google Scholar] [CrossRef] [Green Version]

- Lodi, K.A.; Azeem, A.; Tariq, M.; Ali, M.; Bharatiraja, C. Harmonic Minimization in Modified PUC-5 Inverter Using Genetic Algorithm. In Proceedings of the 2018 IEEE International Conference on Power Electronics, Drives and Energy Systems (PEDES), Chennai, India, 18–21 December 2018; pp. 1–6. [Google Scholar] [CrossRef]

- Ali, M.; Iqbal, A.; Anees, M.A.; Khan, M.R.; Rahman, K.; Ayyub, M. Differential evolution-based pulse-width modulation technique for multiphase MC. IET Power Electron. 2019, 12, 2224–2235. [Google Scholar] [CrossRef]

- Tayyab, M.; Sarwar, A.; Tariq, M.; Chakraborty, R.K.; Ryan, M.J. Hardware-In-the-Loop Implementation of projectile target search algorithm for selective harmonic elimination in a 3-phase multilevel converter. IEEE Access 2020, 9, 30626–30635. [Google Scholar] [CrossRef]

- Dorigo, M.; Gambardella, L.M.; Martinoli, M.; Poli, R.; Stützle, T. Ant Colony Optimization and Swarm Intelligence. In Proceedings of the 5th International Workshop, ANTS 2006, Brussels, Belgium, 4–7 September 2006. [Google Scholar]

- Zhang, Y.; Hu, C.; Wang, Q.; Zhou, Y.; Sun, Y. Neutral-point potential balancing control strategy for three-level ANPC converter using SHEPWM scheme. Energies 2019, 12, 4328. [Google Scholar] [CrossRef] [Green Version]

- Samadaei, E.; Kaviani, M.; Bertilsson, K. A 13-Levels Module (K-Type) with Two DC Sources for Multilevel Inverters. IEEE Trans. Ind. Electron. 2019, 66, 5186–5196. [Google Scholar] [CrossRef]

- Hassan, A.M.M.; Yang, X.; Ali, A.I.M. A Study of Level- Shifted PWM Single-phase 11-Level Multilevel Inverter. In Proceedings of the 21st International Middle East Power Systems Conference (MEPCON), Cairo, Egypt, 17–19 December 2019; pp. 170–176. [Google Scholar]

- Tjokro, C.; Pratomo, L.H. Design and Simulation of an Asymmetrical 11-Level Inverter for Photovoltaic Applications. In Proceedings of the 2018 5th International Conference on Information Technology, Computer, and Electrical Engineering (ICITACEE), Semarang, Indonesia, 27–28 September 2018; pp. 93–98. [Google Scholar] [CrossRef]

- Babu, S.M.; Narasimharaju, B.L.; Rathore, A.K. New Single-Stage Boost Multilevel Inverter. In Proceedings of the 2019 IEEE Transportation Electrification Conference (ITEC-India), Bengaluru, India, 17–19 December 2019; pp. 1–4. [Google Scholar]

- Karimi, M.; Kargar, P.; Varesi, K. A Novel High-Gain Switched-Capacitor Based 11- Level Inverter Topology. In Proceedings of the 2019 International Power System Conference (PSC), Tehran, Iran, 9–11 December 2019; pp. 404–409. [Google Scholar] [CrossRef]

- Rooholahi, B. A New Transformerless Single-Phase Eleven-Level Inverter with Reduction of Switches Based on Model Predictive Control Method. In Proceedings of the 2020 2nd Global Power, Energy and Communication Conference (GPECOM), Izmir, Turkey, 20–23 October 2020; pp. 102–107. [Google Scholar]

- Shahrukh, M.; Usmani, A.A.; Shrivastava, P.; Kidwai, S. New Single Phase 11 Level Inverter Topology usng Multilevel PWM Switching with Lesser Components Count. In Proceedings of the 2018 IEEE Texas Power and Energy Conference (TPEC), College Station, TX, USA, 8–9 February 2018; pp. 1–6. [Google Scholar]

- Dorigo, M. Optimization, Learning and Natural Algorithms. Ph.D. Thesis, Politecnico di Milano, Milan, Italy, 1992. [Google Scholar]

| State | |||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 1A. | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1.25E | + | D | - |

| 1B. | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1.25E | − | C | - |

| 2A. | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | E | + | - | - |

| 2B. | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | E | − | - | - |

| 3A. | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0.75E | + | - | C |

| 3B. | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0.75E | − | - | D |

| 4A. | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0.5E | + | C | C |

| 4B. | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0.5E | + | D | D |

| 4C. | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0.5E | − | C | C |

| 4D. | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0.5E | − | D | D |

| 5A. | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0.25E | + | D | - |

| 5B. | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0.25E | − | C | - |

| 6A. | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | − | - | - |

| 6B. | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | − | - | - |

| 7A. | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | −0.25E | + | - | C |

| 7B. | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | −0.25E | − | - | D |

| 8A. | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | −0.5E | + | C | C |

| 8B. | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | −0.5E | + | D | D |

| 8C. | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | −0.5E | − | C | C |

| 8D. | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | −0.5E | − | D | D |

| 9A. | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | −0.75E | − | C | - |

| 9B. | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | −0.75E | + | D | - |

| 10A. | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | −E | + | - | - |

| 10B. | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | −E | − | - | - |

| 11A. | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | −1.25E | + | - | D |

| 11B. | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | −1.25E | − | - | C |

| MLI | |||||||||

|---|---|---|---|---|---|---|---|---|---|

| [35] | 11 | 5 | 12 | 4 | 11 | 0 | 0 | ND | 12.27 |

| CHB [7] | 11 | 5 | 20 | 0 | 5 | 0 | 0 | No | 11.36 |

| [36] | 11 | 3 | 8 | 3 | 6 | 0 | 0 | ND | 4.64 |

| [25] | 11 | 3 | 8 | 0 | 7 | 0 | 0 | ND | 4.09 |

| [37] | 11 | 1 | 15 | 2 | 13 | 2 | 2 | Yes | 3.09 |

| [38] | 11 | 1 | 14 | 0 | 8 | 4 | 0 | Yes | 2.36 |

| [39] | 11 | 1 | 9 | 0 | 7 | 5 | 0 | No | 1.91 |

| [40] | 11 | 1 | 8 | 0 | 8 | 5 | 0 | No | 1.91 |

| [11] | 9 | 1 | 11 | 0 | 9 | 2 | 0 | Yes | 2.44 |

| UXE-11 | 12 | 1 | 11 | 0 | 7 | 2 | 0 | Yes | 1.91 |

| S. No. | Parameters | Value |

|---|---|---|

| 1. | DC-Source Voltage | 100 V |

| 2. | Capacitors | 2500 μF, 50 V |

| 3. | Resistive Load | 50 & 100 Ω |

| 4. | Inductive Load | 100 mH |

| 5. | Power frequency | 50 Hz |

| MI | |||||

|---|---|---|---|---|---|

| 0.86 | 8.461 | 18.941 | 35.822 | 54.195 | 86.228 |

| FFT analysis with MNLC (MI = 0.94) | |||||

| Unit | 1st | 3rd | 5th | 7th | 9th |

| dBV | 38.545 | 2.148 | 2.520 | 5.947 | 4.4727 |

| Peak (V) | 119.61 | 1.811 | 1.890 | 2.8046 | 2.367 |

| FFT analysis with SHE (MI = 0.86) | |||||

| dBV | 37.734 | −9.627 | −14.336 | −5.8008 | −3.477 |

| peak (V) | 108.95 | 0.467 | 0.272 | 0.725 | 0.947 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ali, M.; Tariq, M.; Lin, C.-H.; Chakrobortty, R.K.; Alamri, B.; Alahmadi, A.; Ryan, M.J. Operation of a UXE-Type 11-Level Inverter with Voltage-Balance Modulation Using NLC and ACO-Based SHE. Sustainability 2021, 13, 9035. https://doi.org/10.3390/su13169035

Ali M, Tariq M, Lin C-H, Chakrobortty RK, Alamri B, Alahmadi A, Ryan MJ. Operation of a UXE-Type 11-Level Inverter with Voltage-Balance Modulation Using NLC and ACO-Based SHE. Sustainability. 2021; 13(16):9035. https://doi.org/10.3390/su13169035

Chicago/Turabian StyleAli, Mohammad, Mohd Tariq, Chang-Hua Lin, Ripon K. Chakrobortty, Basem Alamri, Ahmad Alahmadi, and Michael J. Ryan. 2021. "Operation of a UXE-Type 11-Level Inverter with Voltage-Balance Modulation Using NLC and ACO-Based SHE" Sustainability 13, no. 16: 9035. https://doi.org/10.3390/su13169035

APA StyleAli, M., Tariq, M., Lin, C.-H., Chakrobortty, R. K., Alamri, B., Alahmadi, A., & Ryan, M. J. (2021). Operation of a UXE-Type 11-Level Inverter with Voltage-Balance Modulation Using NLC and ACO-Based SHE. Sustainability, 13(16), 9035. https://doi.org/10.3390/su13169035