Modification of Cockcroft–Walton-Based High-Voltage Multipliers with 220 V and 50 Hz Input for Non-Thermal Food Processing Apparatus

Abstract

1. Introduction

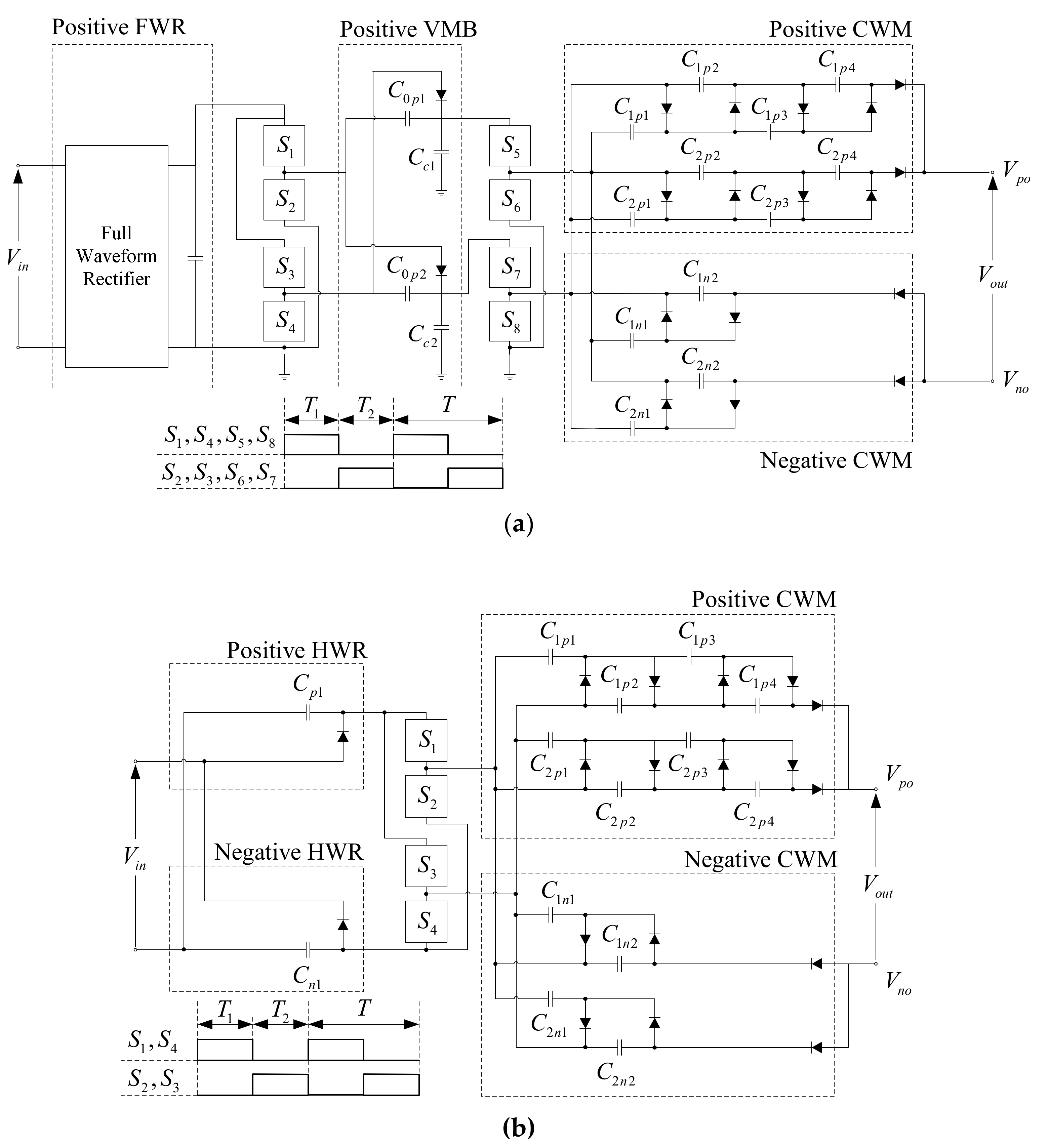

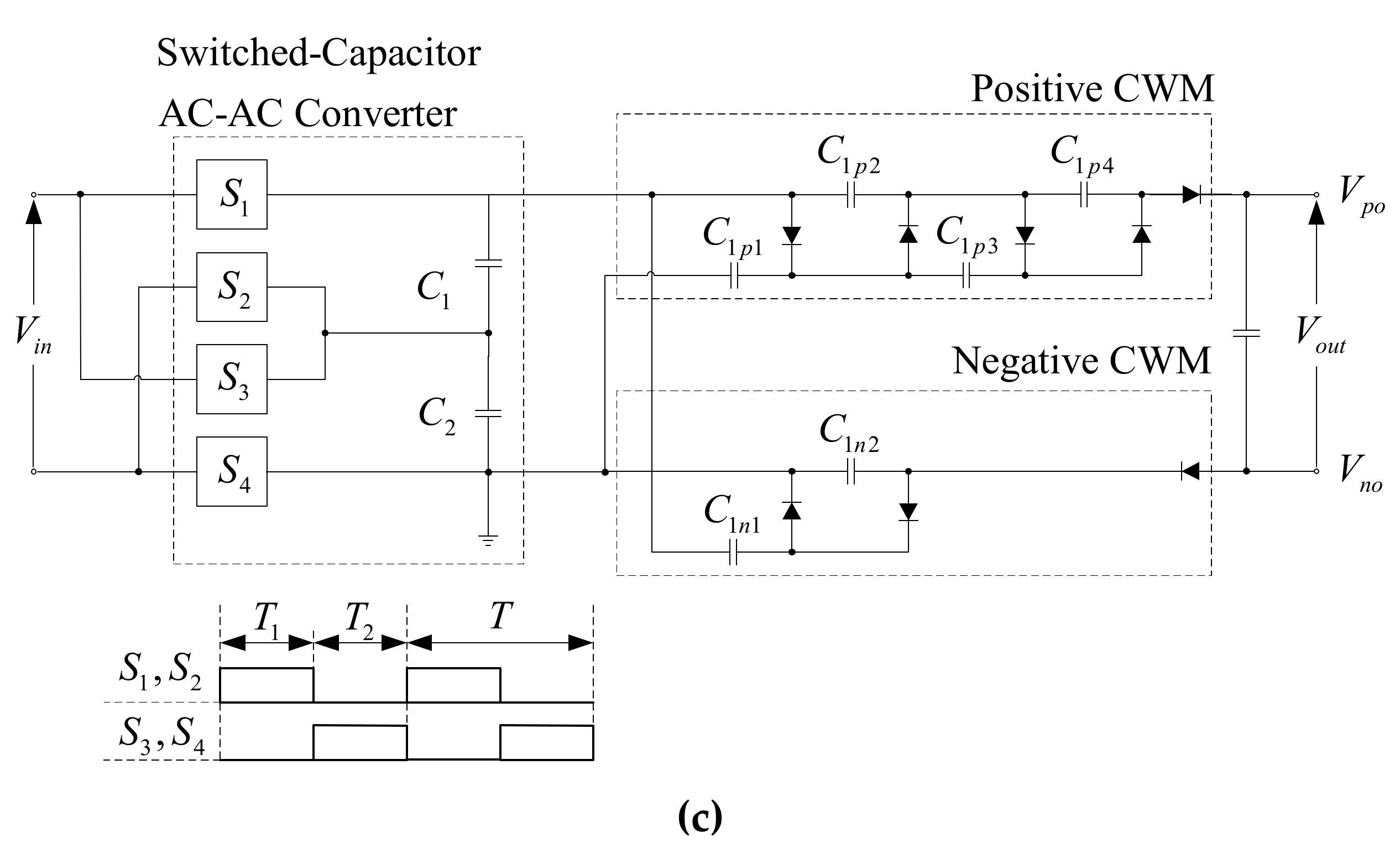

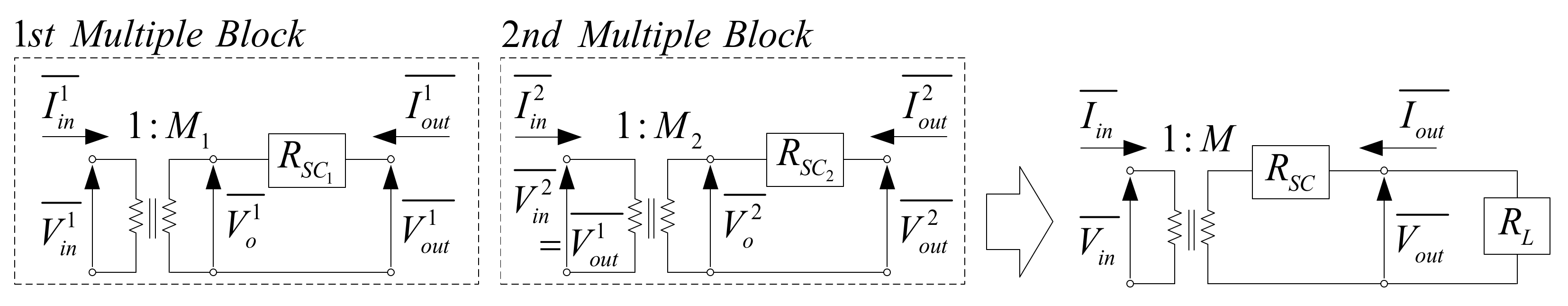

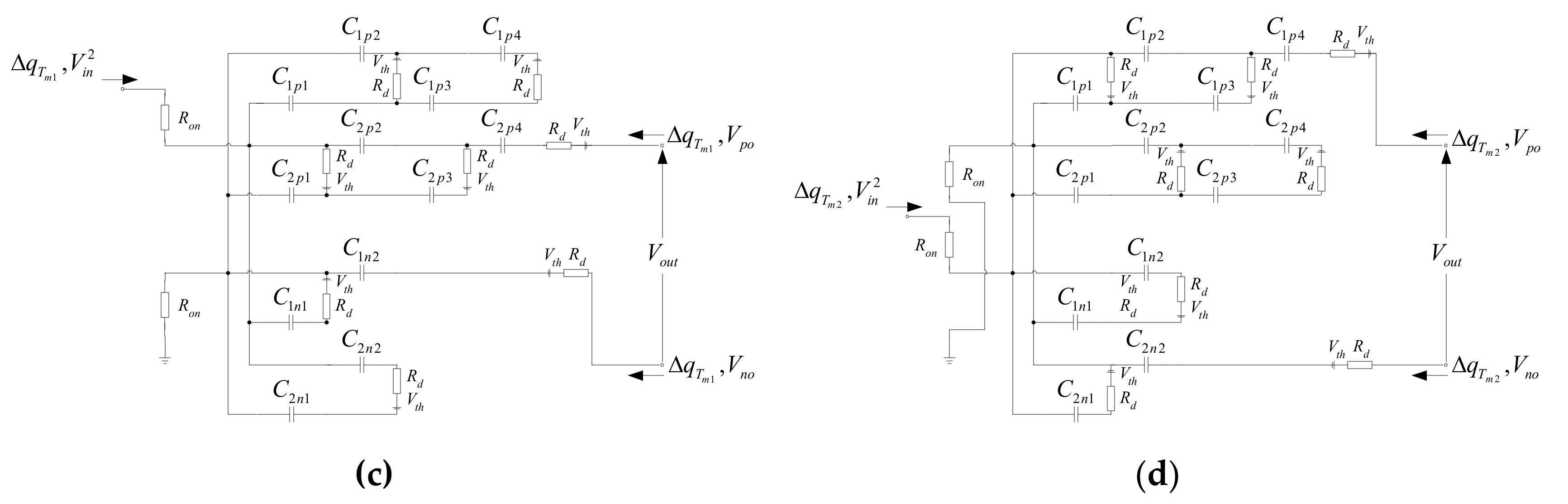

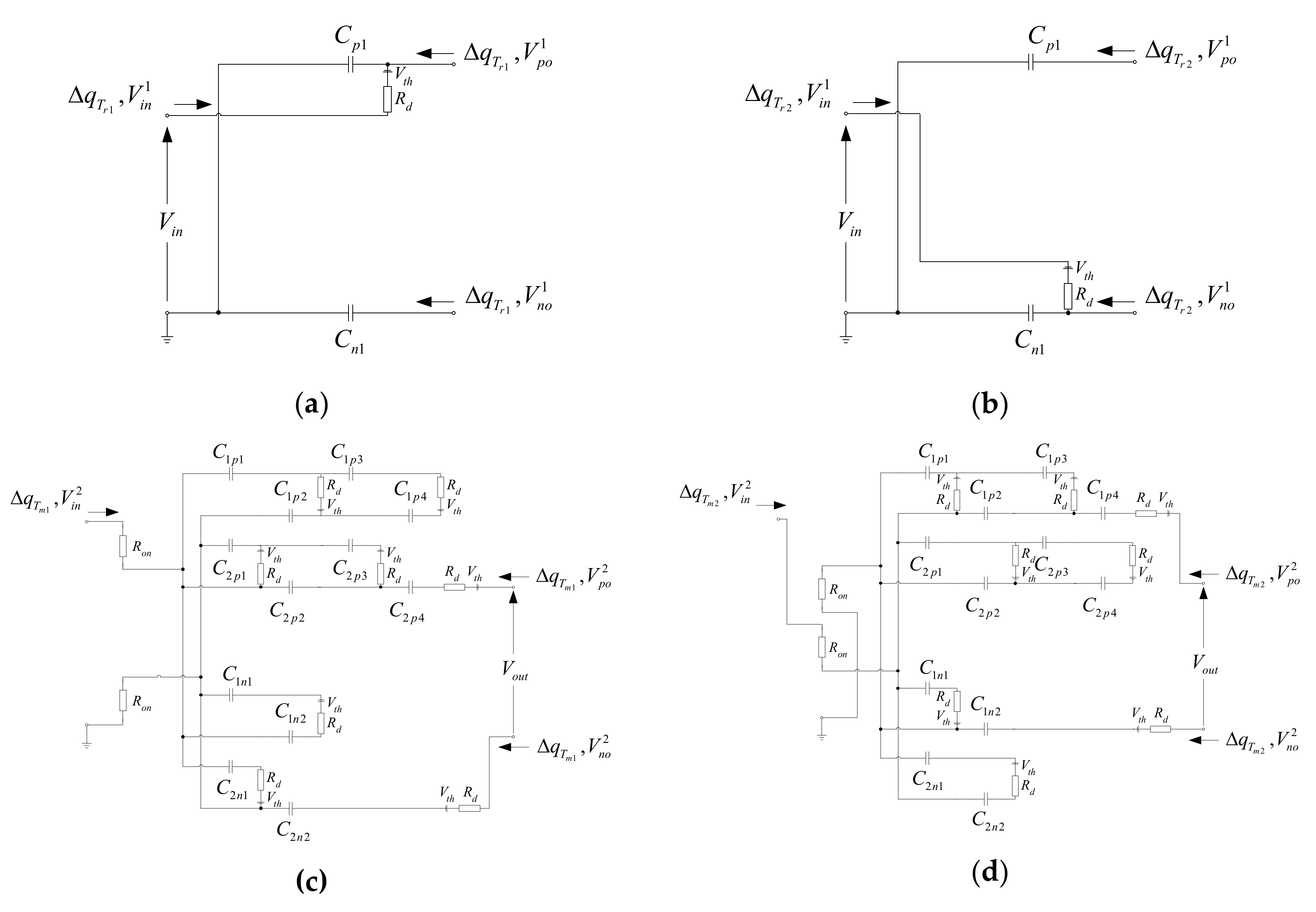

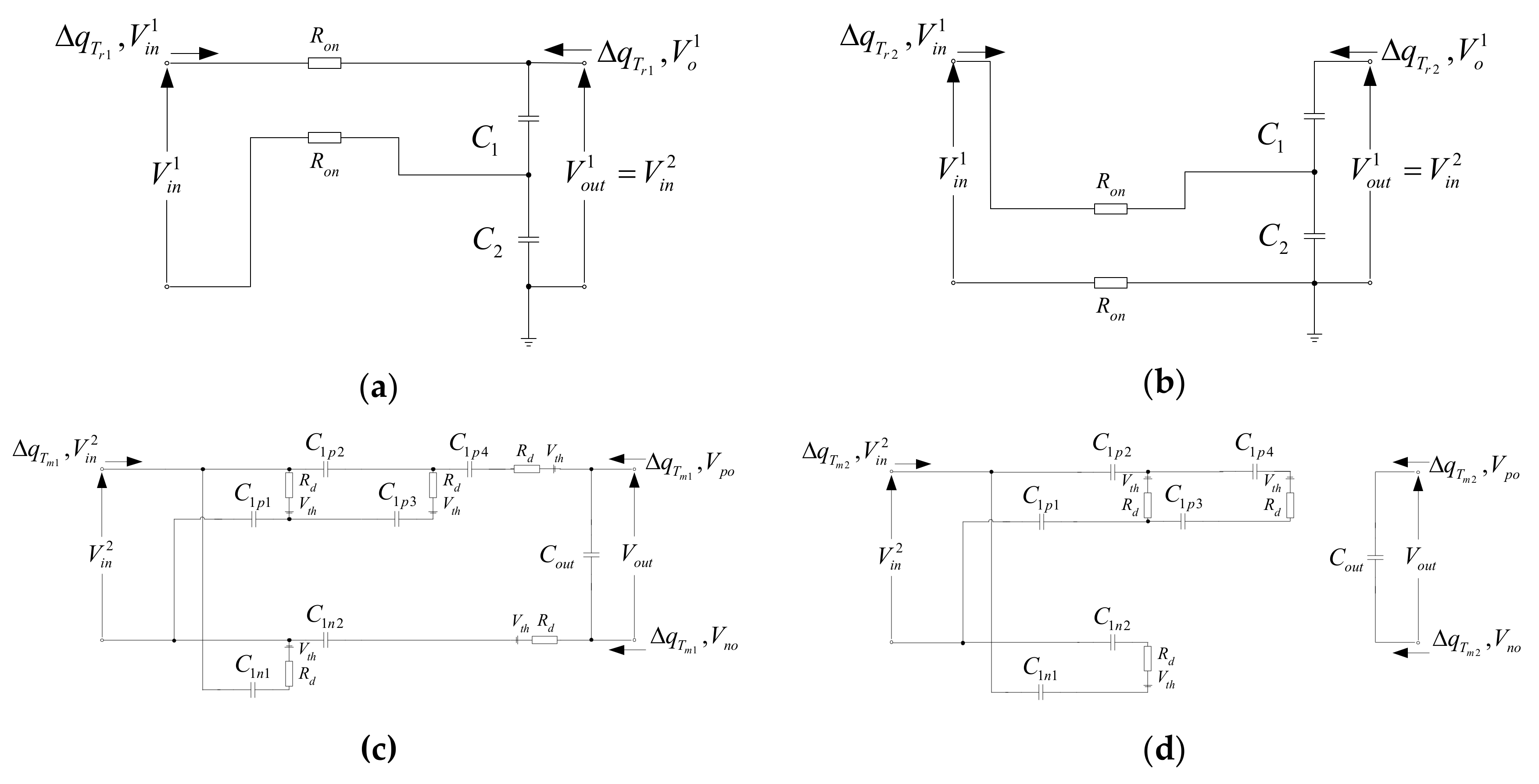

2. Proposed Modification

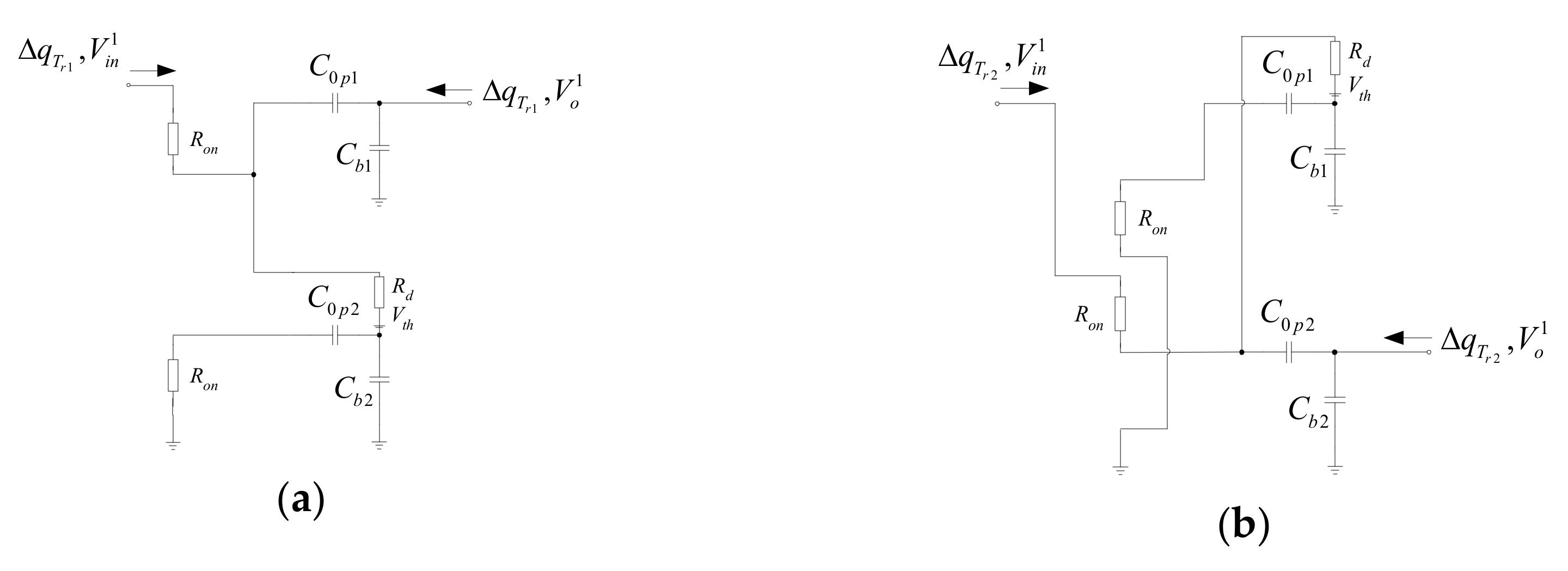

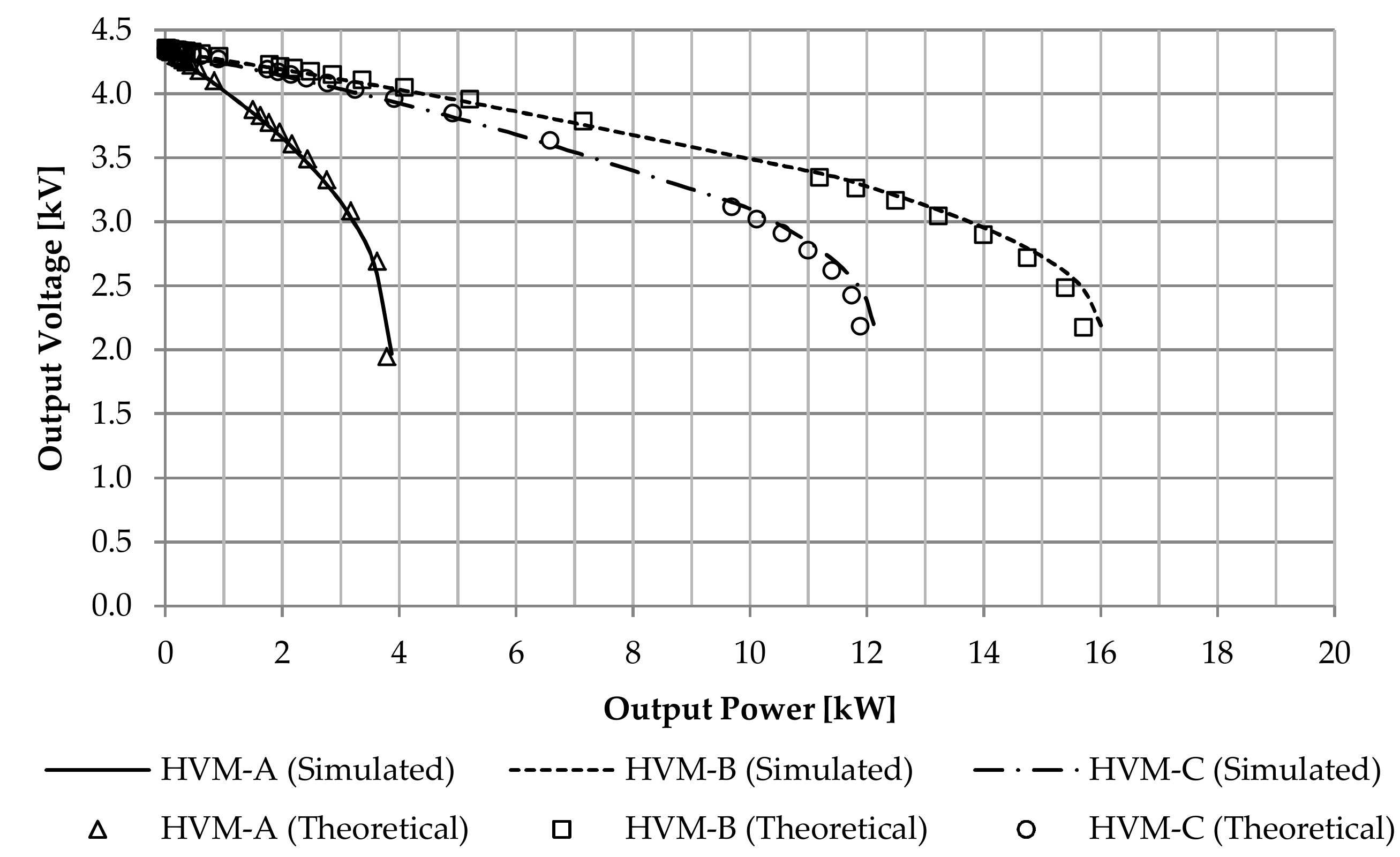

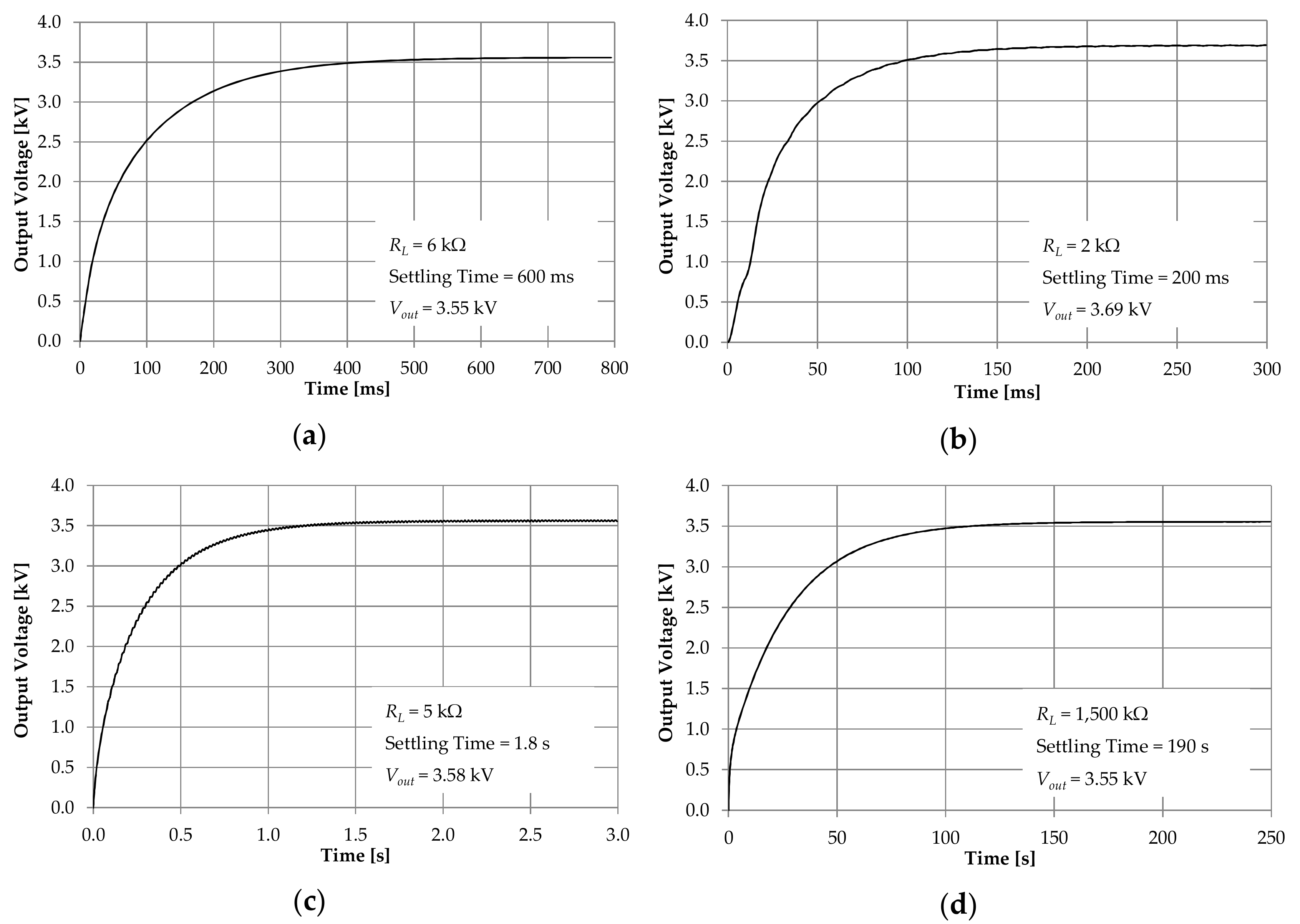

3. Theoretical Analysis

- (1)

- The dielectric loss is not considered.

- (2)

- The time constant of the proposed HVM-A is greater than the time period of clock pulses.

- (3)

- The input is a rectangular waveform.

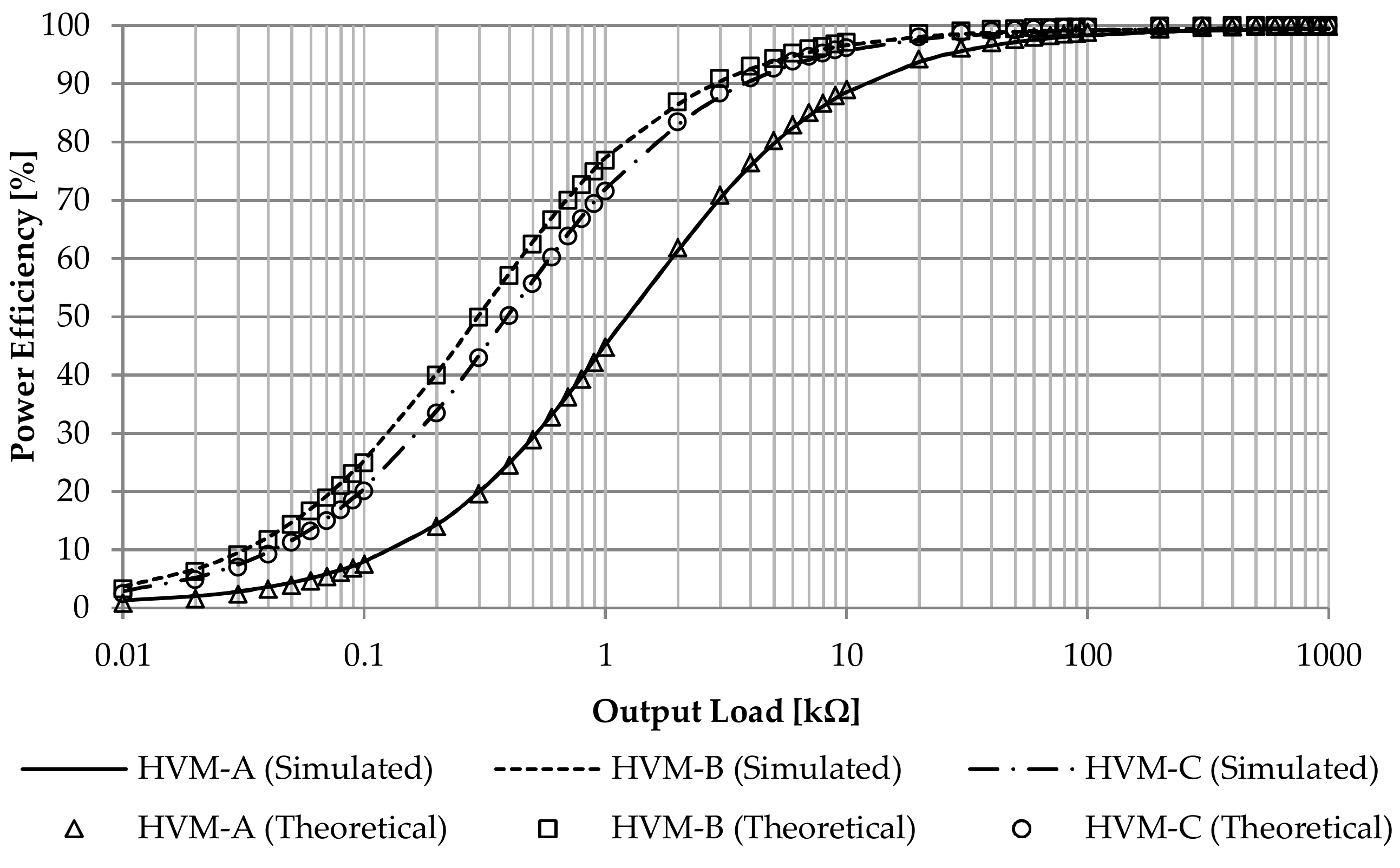

4. Simulation Results

5. Discussion and Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Zhang, C.H.; Namihira, T.; Kiyan, T.; Nakashima, K.; Katsuki, S.; Akiyama, H.; Ito, H.; Imaizumi, Y. Investigation of Shockwave Produced by Large Volume Pulsed Discharge under Water. In Proceedings of the IEEE Pulsed Power Conference, Monterey, CA, USA, 13–15 June 2005; pp. 1377–1380. [Google Scholar]

- Yamashita, Y.; Oda, A.; Maehara, H.; Watanabe, T.; Motamedi, M.; Itoh, S. The numerical analysis of food processing using shock wave. Int. J. Multiphysics 2009, 3, 337–346. [Google Scholar] [CrossRef]

- Shimojima1, K.; Miyafuji, Y.; Naha1, K.; Higa, O.; Matsubara, R.; Higa, K.; Higa, Y.; Matsui, T.; Takemoto, A.; Tanaka, S.; et al. Development of the rice-powder manufacturing system using underwater shock wave. Int. J. Multiphysics 2012, 6, 355–363. [Google Scholar] [CrossRef]

- Shinzato, S.; Higa, Y.; Tamaki, T.; Iyama, H.; Itoh, S. Computational simulation of underwater shockwave propagation using smoothed particle hydrodynamics. Mater. Sci. Forum 2013, 767, 86–91. [Google Scholar] [CrossRef]

- Matsui, T.; Higa, K.; Matsubara, R.; Hanashiro, S.; Higa, O.; Itoh, S. Measurement of discharged energy and pressure of underwater shockwave changing materials of contact switch in high voltage power supply. Mater. Sci. Forum 2013, 767, 250–255. [Google Scholar] [CrossRef]

- Higa, O.; Matsubara, R.; Higa, K.; Miyafuji, Y.; Gushi, T.; Omine, Y.; Naha, K.; Shimojima, K.; Fukuoka, H.; Maehara, H.; et al. Mechanism of the shock wave generation and energy efficiency by underwater discharge. Int. J. Multiphysics 2012, 6, 89–97. [Google Scholar] [CrossRef]

- Higa, K.; Matsui, T.; Hanashiro, S.; Higa, O.; Itoh, S. Evaluation of the contact switch materials in high voltage power supply for generate of underwater shockwave by electrical discharge. Int. J. Multiphysics 2014, 8, 359–366. [Google Scholar] [CrossRef]

- Higa, O.; Yasuda, A.; Higa, Y.; Shimojima, K.; Hokamoto, K.; Itoh, S. Optical Examination of shockwave propagation induced by an underwater wire explosion. Int. J. Multiphysics 2016, 10, 343–354. [Google Scholar]

- Zhou, H.; Zhang, Y.; Han, R.; Jing, Y.; Wu, J.; Liu, Q.; Ding, W.; Qiu, A. Signal analysis and waveform reconstruction of shock waves generated by underwater electrical wire explosions with piezoelectric pressure probes. Sensors 2016, 16, 573. [Google Scholar] [CrossRef]

- Eguchi, K.; Jaiwanglok, A.; Julsereewong, A.; Asadi, F.; Abe, H.; Oota, I. Design of a non-thermal food processing system utilizing wire discharge of dual electrodes in underwater. IJICIC 2018, 14, 847–860. [Google Scholar]

- Abe, H.; Do, W.; Eguchi, K. An Efficient Non-Thermal Food Processing System by Underwater Shockwaves Using Two Pairs of Restoration Electrodes. In Proceedings of the 5th International Conference on Engineering, Applied Sciences and Technology, Luang Prabang, LAOS, 2–5 July 2019; pp. 1–4. [Google Scholar]

- Abe, K.; Ogata, R.; Eguchi, K.; Smerpitak, K.; Pongswatd, S. Study on non-thermal food processing utilizing an underwater shockwave. Indian J. Sci.Technol. 2017, 10, 1–5. [Google Scholar] [CrossRef]

- Kuraya, E.; Nakada, S.; Touyama, A.; Itoh, S. Improving the antioxidant functionality of Citrus junos Tanaka (yuzu) fruit juice by underwater shockwave pretreatment. Food Chem. 2017, 216, 123–129. [Google Scholar] [CrossRef] [PubMed]

- Eguchi, K.; Terada, S.; Oota, I. Design of a digitally controlled inductor-less voltage multiplier for non-thermal food processing. IJIEE 2014, 4, 438–445. [Google Scholar]

- Lamantia, A.; Maranesi, P.; Radrizzani, L. The Dynamic of the Cockcroft-Walton Voltage Multiplier. In Proceedings of the 21st Annual IEEE Conference on Power Electronics Specialists, San Antonio, TX, USA, 11–14 June 1990; pp. 485–490. [Google Scholar]

- Lamantia, A.; Maranesi, P.G.; Radrizzani, L. Small-signal model of the Cockcroft–Walton voltage multiplier. IEEE Trans. Power Electron 1994, 9, 18–25. [Google Scholar] [CrossRef]

- Kobougias, I.C.; Tatakis, E.C. Optimal design of a half-wave Cockcroft–Walton voltage multiplier with minimum total capacitance. IEEE Trans. Power Electron 2010, 25, 2460–2468. [Google Scholar] [CrossRef]

- Katzir, L.; Shmilovitz, D. Effect of the capacitance distribution on the output impedance of the half-wave Cockcroft-Walton voltage multiplier. In Proceedings of the 2016 IEEE Applied Power Electronics Conference and Exposition, Long Beach, CA, USA, 20–24 March 2016; pp. 3655–3658. [Google Scholar]

- Tanzawa, T. Innovation of switched-capacitor voltage multiplier: Part 1: A brief history. IEEE Solid-State Circuits Mag. 2016, 8, 51–59. [Google Scholar] [CrossRef]

- Park, S.; Yang, J.; Rivas-Davila, J. A hybrid Cockcroft-Walton/Dickson multiplier for high voltage generation. IEEE Trans. Power Electron 2020, 35, 2714–2723. [Google Scholar] [CrossRef]

- Abe, K.; Sasaki, H.; Oota, I.; Eguchi, K. Improvement of an output voltage efficiency of a high voltage generator for non-thermal food processing systems. ICIC Express Lett. 2015, 9, 3087–3092. [Google Scholar]

- Young, C.M.; Chen, M.H.; Chang, T.A.; Ko, C.C.; Jen, K.K. Cascade Cockcroft–Walton voltage multiplier applied to transformerless high step- up DC–DC converter. IEEE Trans. Ind. Electron. 2013, 60, 523–537. [Google Scholar] [CrossRef]

- Razzak, M.A.; Chakraborty, S.; Tasneem, Z. Design of a multistage 0.1/12 kV DC-DC matrix converter using Cockcroft-Walton voltage multiplier topology. Proceeding of the 2015 IEEE International WIE Conference on Electrical and Computing Engineering, Dhaka, Bangladesh, 19–20 December 2015; pp. 309–312. [Google Scholar]

- Iqbal, S.; Besar, R. A bipolar Cockcroft-Walton voltage multipliers for gas lasers. Am. J. Appl. Sci. 2007, 4, 793–799. [Google Scholar] [CrossRef]

- Iqbal, S. A hybrid symmetrical voltage multiplier. IEEE Trans. Power Electr. 2014, 29, 6–12. [Google Scholar] [CrossRef]

- Eguchi, K.; Pongswatd, S.; Terada, S.; Oota, I. Parallel-connected high voltage multiplier with symmetrical structure. Appl. Mech. Mater. 2014, 619, 173–177. [Google Scholar] [CrossRef]

- Eguchi, K.; Abe, K.; Terada, S.; Oota, I. A parallel-connected high voltage multiplier for non-thermal food processing. In Proceedings of the 7th International Conference on Electrical, Electronics and Civil Engineering, Pattaya, Thailand, 17–18 June 2015; pp. 14–18. [Google Scholar]

- Eguchi, K.; Abe, K.; Fujisawa, H.; Oota, I. Design of a High Voltage Multiplier with Series-Connected Bipolar Topology. In Proceedings of the Third International Conference on Advances in Applied Science and Environmental Technology, Bangkok, Thailand, 28–29 December 2015; pp. 113–117. [Google Scholar]

- Eguchi, K.; Wongjan, A.; Julsereewong, A.; Do, W.; Oota, I. Design of a high-voltage multiplier combined with Cockcroft-Walton voltage multipliers and switched-capacitor AC-AC converters. IJICIC 2017, 13, 1007–1019. [Google Scholar]

- Tsubomi, K.; Terada, S.; Eguchi, K.; Oota, I. Improvement and analysis of equivalent circuit for switching converter by considering power loss. Trans. IEICE C 2014, 97, 365–375. [Google Scholar]

- Eguchi, K.; Junsing, T.; Julsereewong, A.; Do, W.; Oota, I. Design of a nesting-type switched-capacitor AC/DC converter using voltage equalizers. IJICIC 2017, 13, 1369–1384. [Google Scholar]

| Modified Scheme | Vpo | −Vno | Vout |

|---|---|---|---|

| HVM-A | Vpo = 10Vin − 11Vth | −Vno = 4Vin − 4Vth | Vout = 14Vin − 15Vth |

| HVM-B | Vpo = 10Vin − 11Vth | −Vno = 4Vin − 4Vth | Vout = 14Vin − 15Vth |

| HVM-C | Vpo = 10Vin − 6Vth | −Vno = 4Vin − 3Vth | Vout = 14Vin − 9Vth |

| Modified Scheme | Step-Up Gain | RSC |

|---|---|---|

| HVM-A | 14 | 114Rd + 1144Ron |

| HVM-B | 14 | 114Rd + 132Ron |

| HVM-C | 14 | 8Rd + 392Ron |

| Modified Scheme | 1st Multiple Block | 2nd Multiple Block |

|---|---|---|

| HVM-A | Positive FWR | Parallel-Connected Positive CWM |

| Positive VMB | Parallel-Connected Negative CWM | |

| HVM-B | Positive/Negative HWRs | Parallel-Connected Positive CWM |

| (AC-DC Rectifier) | Parallel-Connected Negative CWM | |

| HVM-C | Positive/Negative VMBs | Positive CWM |

| (SC AC-AC Converter) | Negative CWM |

| Modified Scheme | Diode | Capacitor | Switch | Total |

|---|---|---|---|---|

| HVM-A | 18 | 16 | 8 | 42 |

| HVM-B | 18 | 14 | 4 | 36 |

| HVM-C | 8 | 8 | 4 | 20 |

| Traditional CWM [16] | 14 | 14 | - | 28 |

| Modified Scheme | Size | Internal Resistance | Response Speed | Efficiency |

|---|---|---|---|---|

| HVM-A | 4 | 4 | 2 | 3 |

| HVM-B | 3 | 2 | 1 | 1 |

| HVM-C | 1 | 3 | 3 | 2 |

| Traditional CWM [16] | 2 | 1 | 4 | 4 |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Jaiwanglok, A.; Eguchi, K.; Smerpitak, K.; Julsereewong, A. Modification of Cockcroft–Walton-Based High-Voltage Multipliers with 220 V and 50 Hz Input for Non-Thermal Food Processing Apparatus. Sustainability 2020, 12, 6330. https://doi.org/10.3390/su12166330

Jaiwanglok A, Eguchi K, Smerpitak K, Julsereewong A. Modification of Cockcroft–Walton-Based High-Voltage Multipliers with 220 V and 50 Hz Input for Non-Thermal Food Processing Apparatus. Sustainability. 2020; 12(16):6330. https://doi.org/10.3390/su12166330

Chicago/Turabian StyleJaiwanglok, Anurak, Kei Eguchi, Krit Smerpitak, and Amphawan Julsereewong. 2020. "Modification of Cockcroft–Walton-Based High-Voltage Multipliers with 220 V and 50 Hz Input for Non-Thermal Food Processing Apparatus" Sustainability 12, no. 16: 6330. https://doi.org/10.3390/su12166330

APA StyleJaiwanglok, A., Eguchi, K., Smerpitak, K., & Julsereewong, A. (2020). Modification of Cockcroft–Walton-Based High-Voltage Multipliers with 220 V and 50 Hz Input for Non-Thermal Food Processing Apparatus. Sustainability, 12(16), 6330. https://doi.org/10.3390/su12166330