Experimental Verification of Fault Tolerant Operation Focusing on DC-Bus Battery Failure in Dual Inverter Motor Drive

Abstract

:1. Introduction

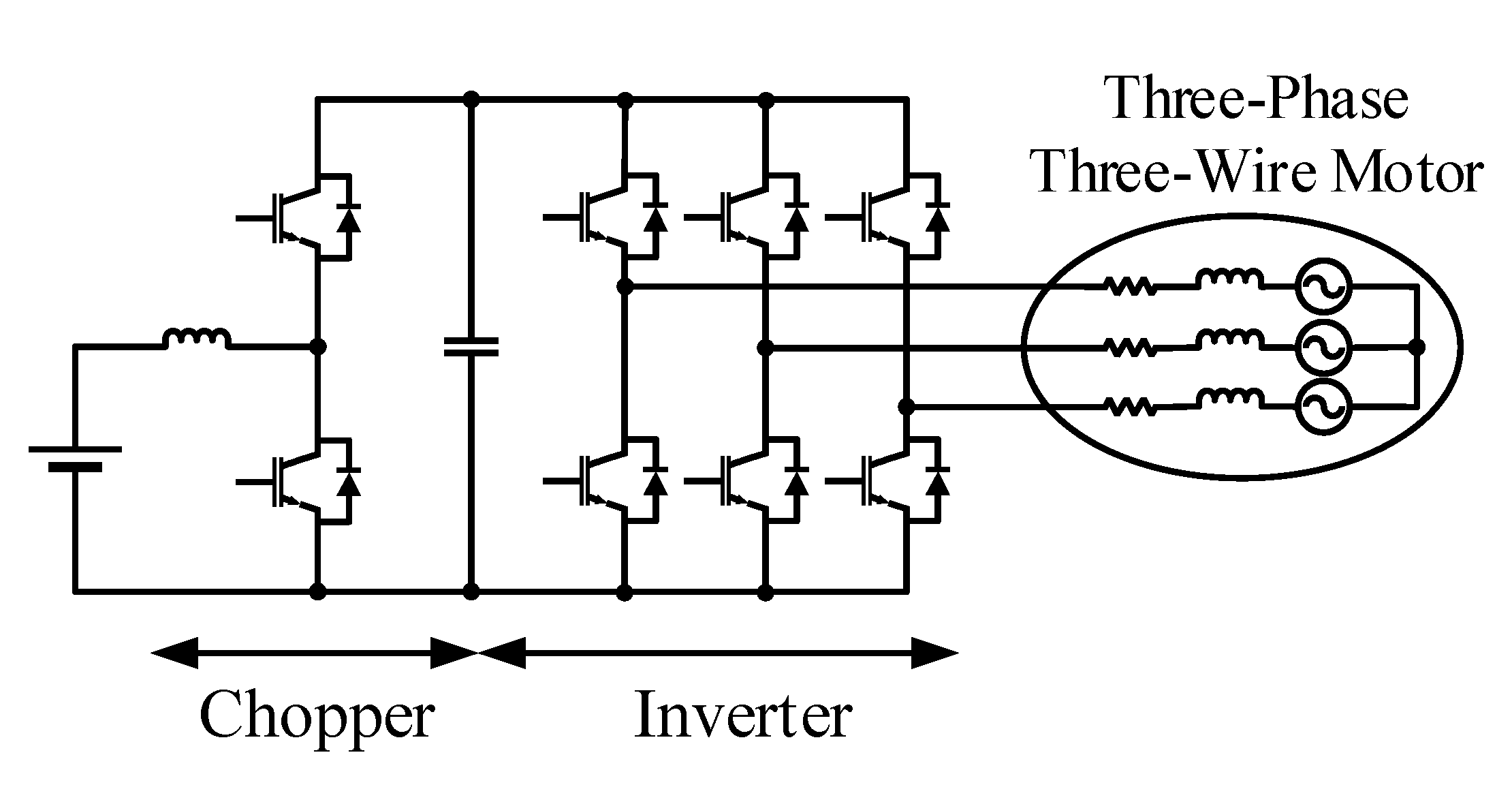

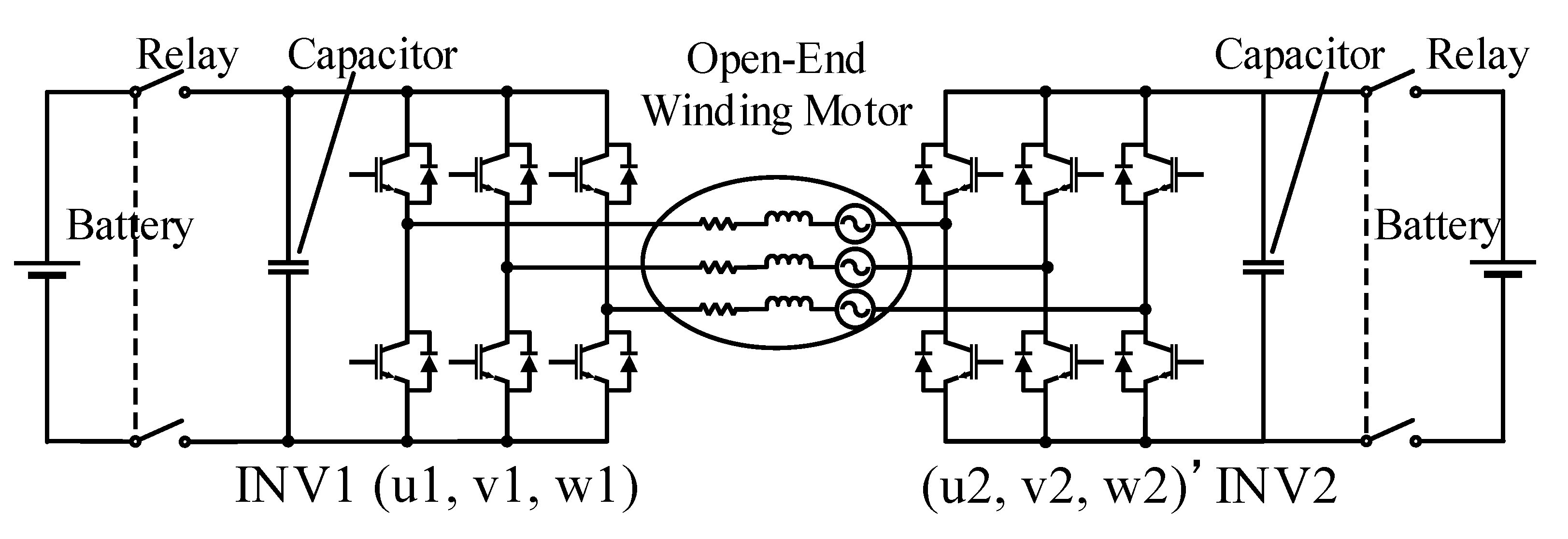

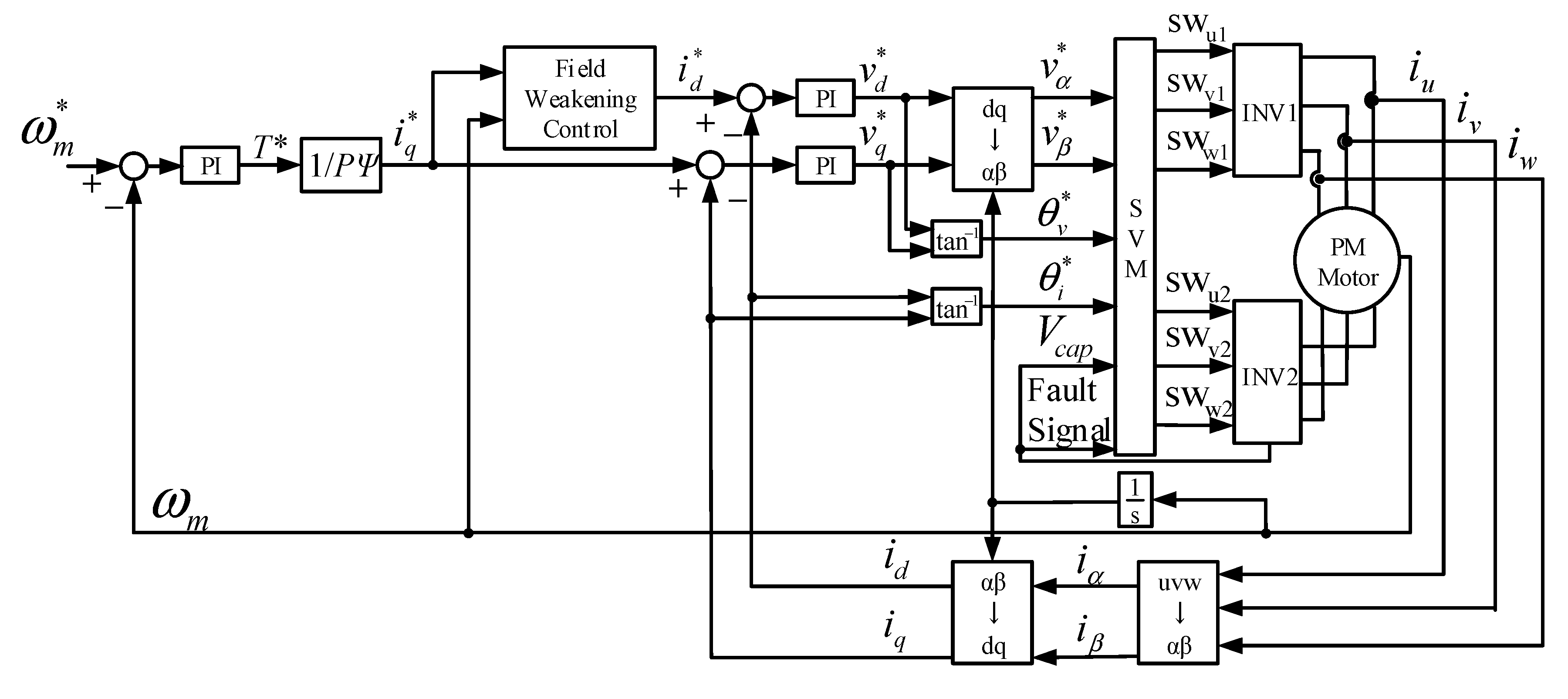

2. Dual Inverter Motor Drive

2.1. Circuit Configuration

2.2. Fault Tolerant Operation of DC-Bus Battery

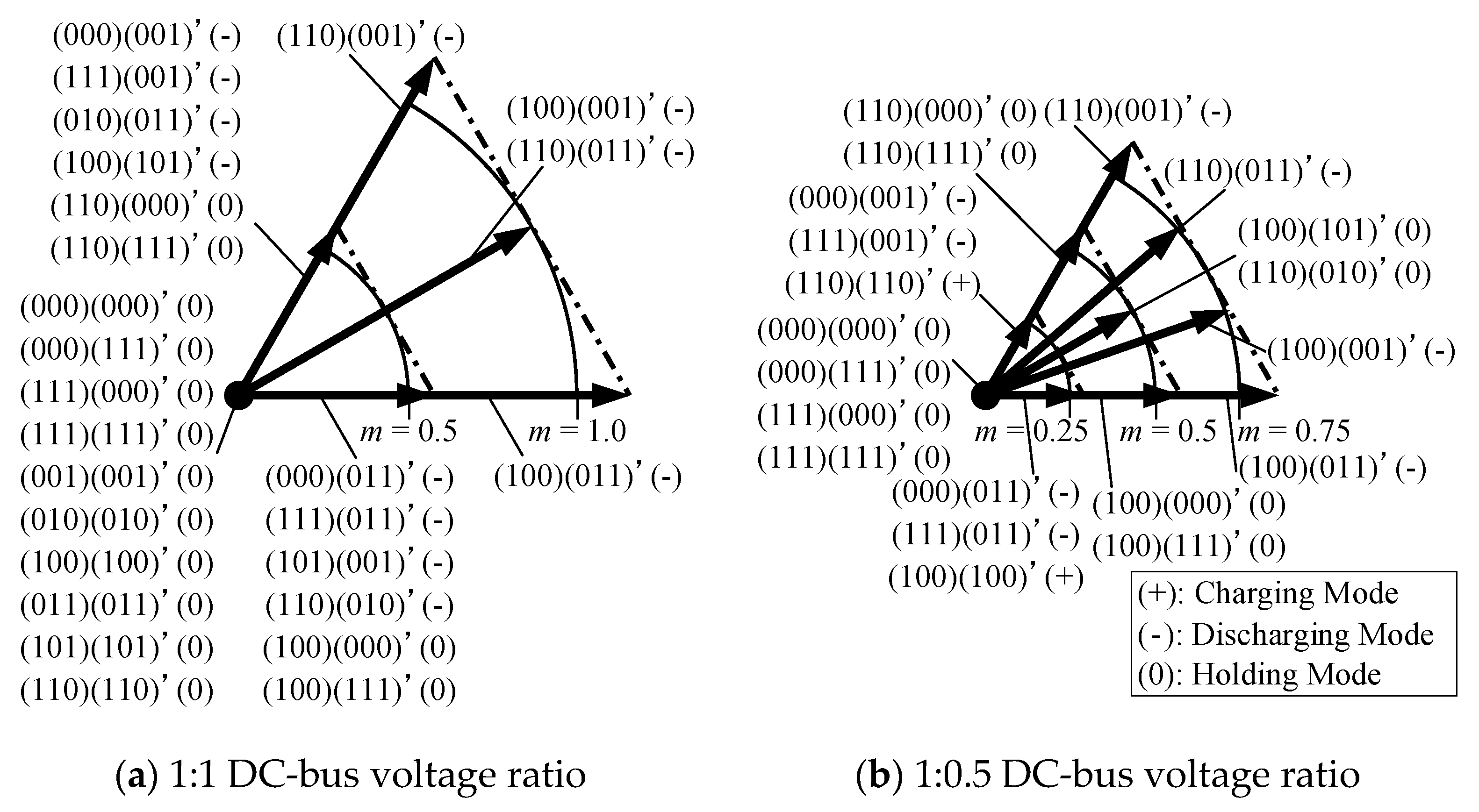

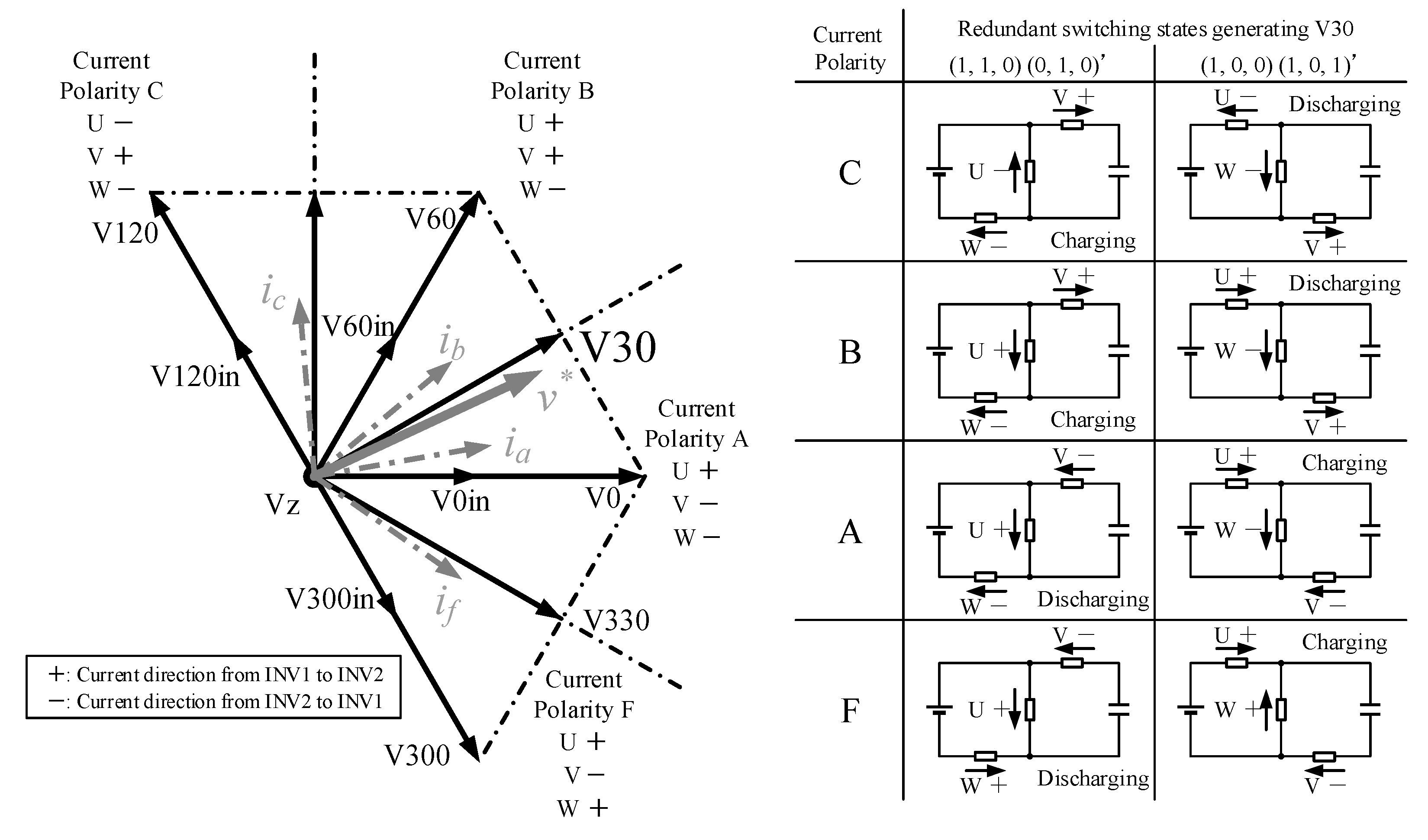

2.2.1. Operation Principle

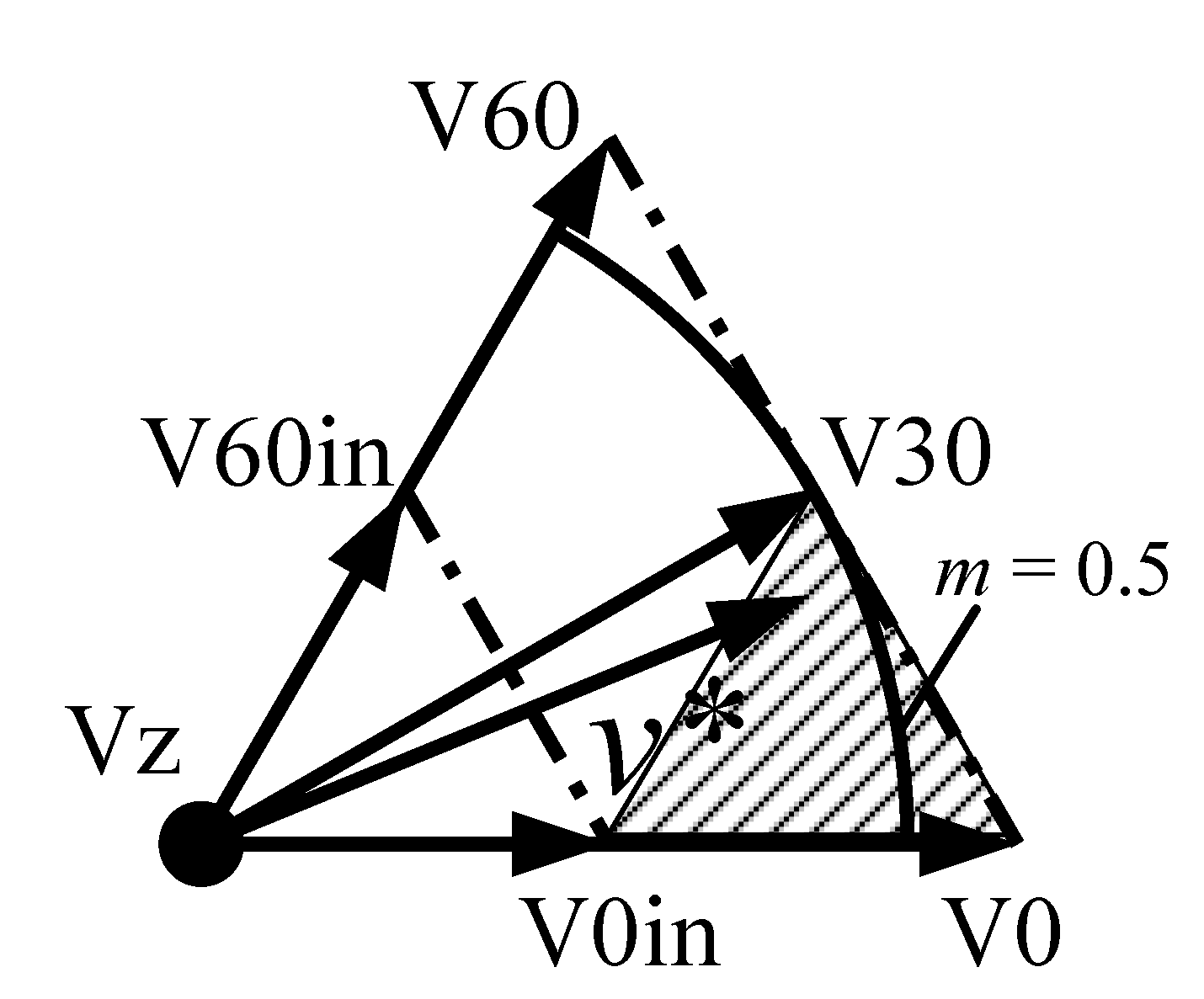

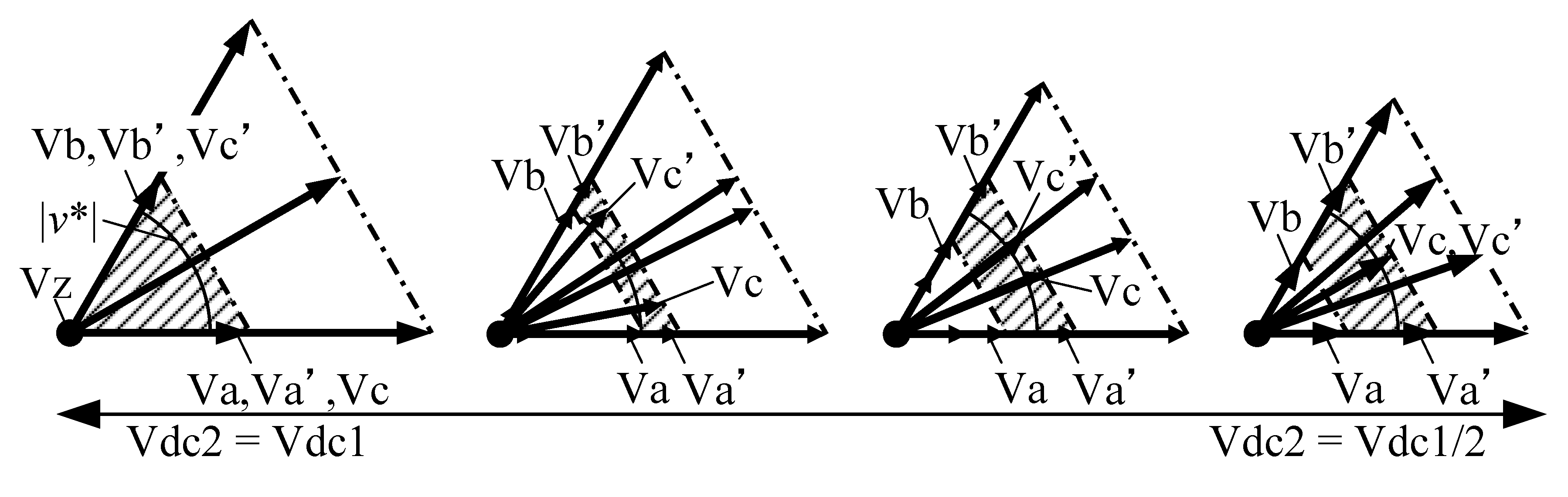

2.2.2. Capacitor Voltage Control with SVM

2.3. Switching Over Techniques for Fault Tolerant Operation of DC-Bus Battery

2.3.1. Switching Over Technique for Fault Tolerant Operation at Low-Modulation-Index

2.3.2. Switching Over Technique for Fault Tolerant Operation Employing Field-Weakening Control at High-Modulation-Index

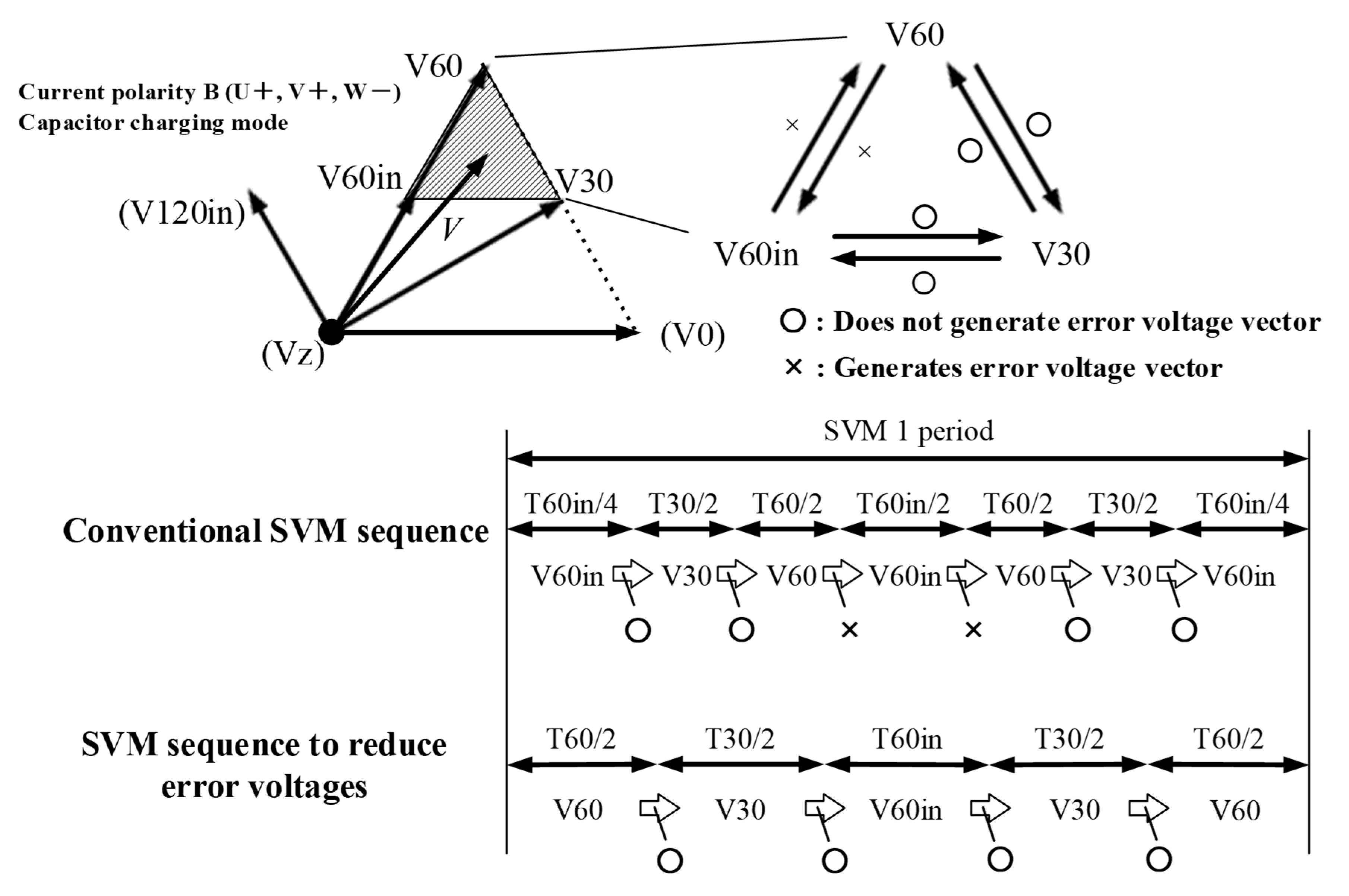

2.4. Impact of Dead Time in Dual Inverter Motor Drive

2.4.1. Error Voltage Vector During Dead Time

2.4.2. SVM Techniques to Reduce Error Voltages

3. Experimental Results and Discussion

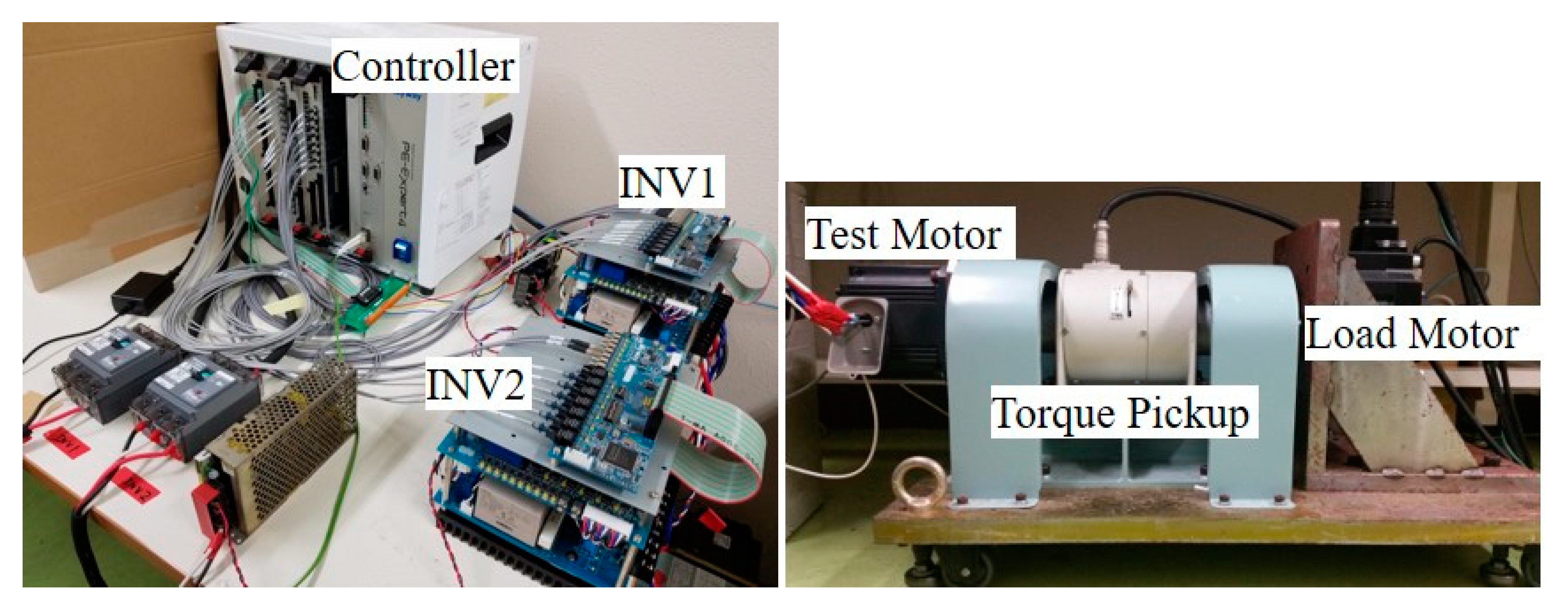

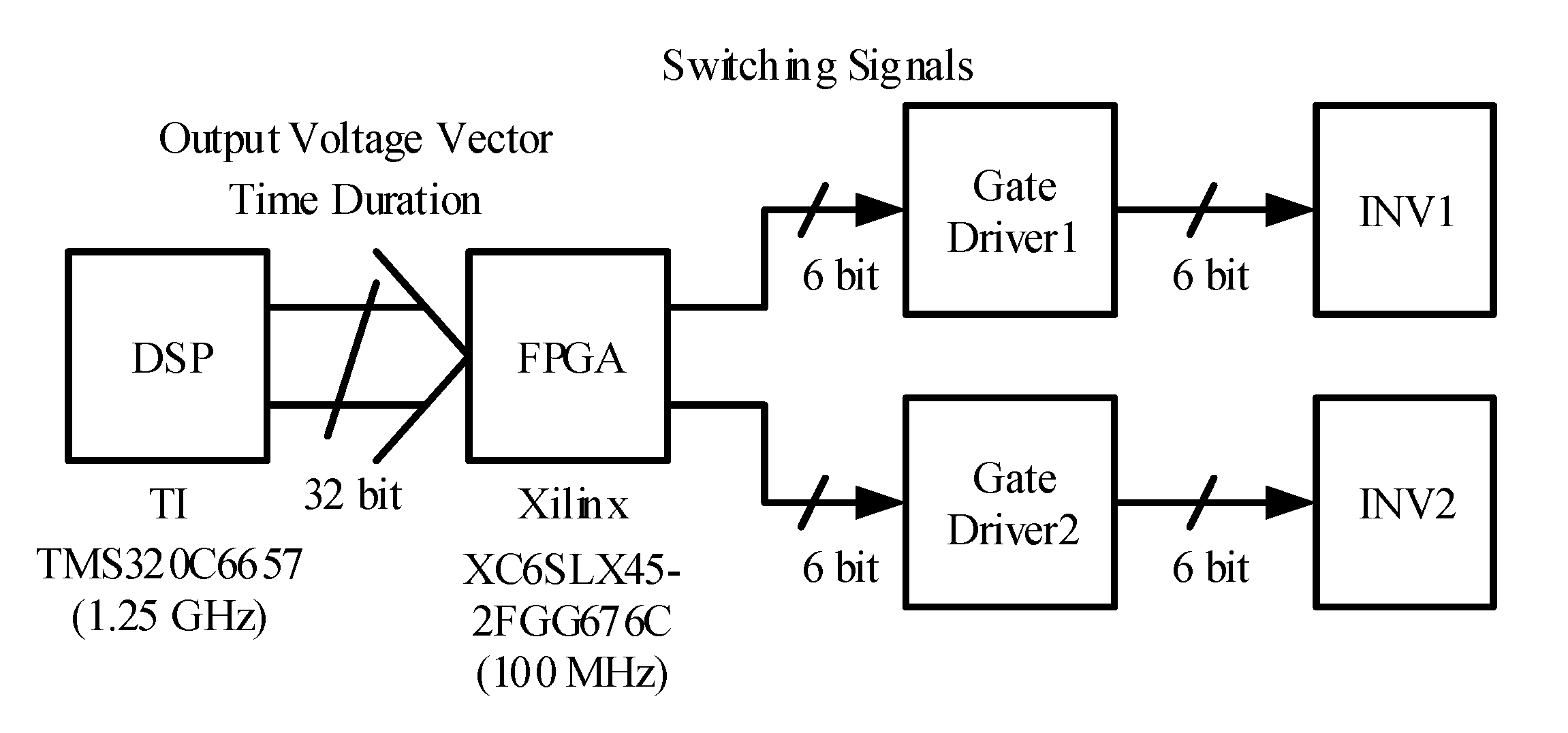

3.1. Experimental Setups

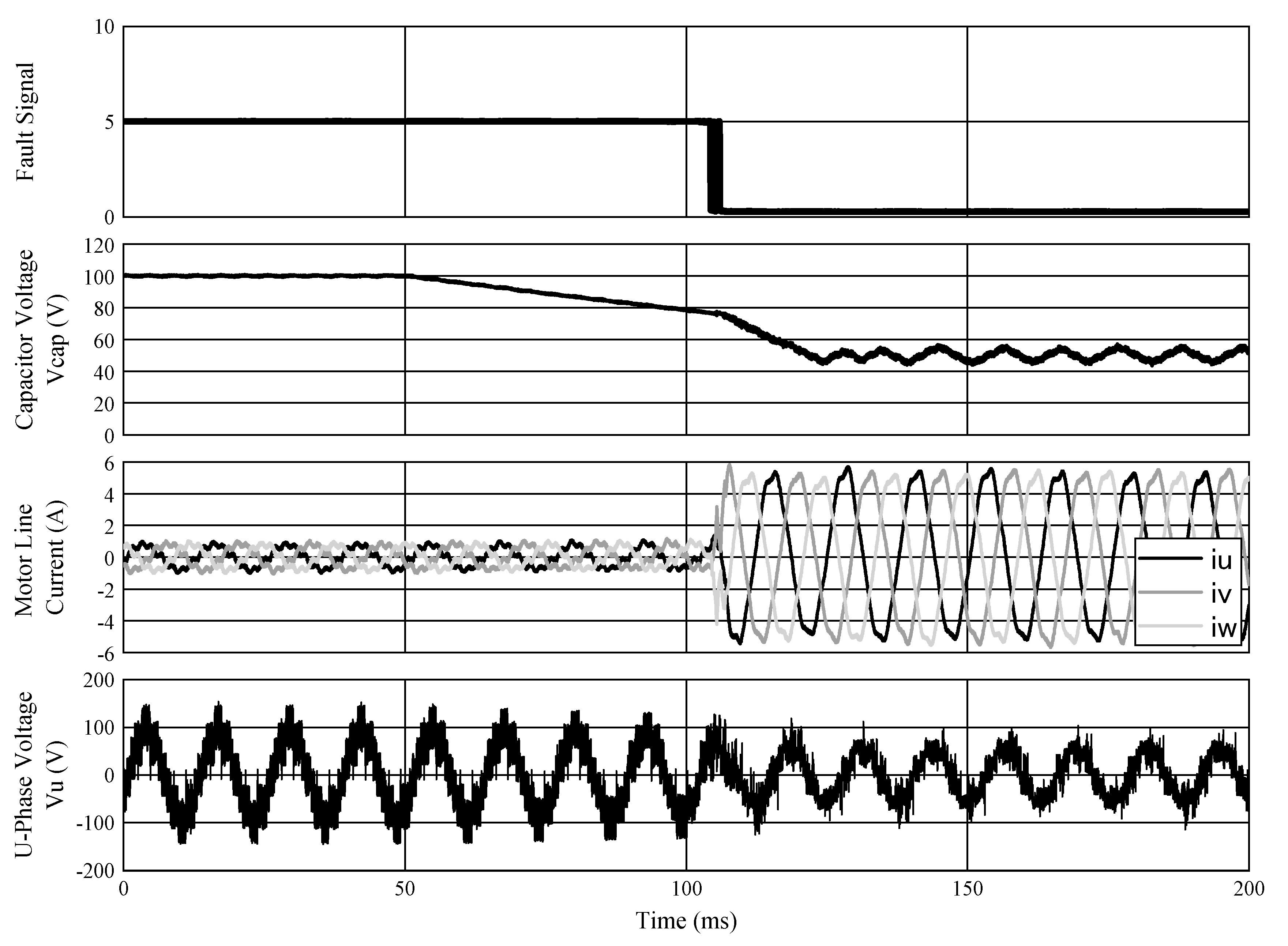

3.2. Experimental Results and Discussions

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Kiadehi, A.D.; Drissi, K.E.K.; Pasquier, C. Voltage THD Reduction for Dual-Inverter Fed Open-End Load with Isolated DC Sources. IEEE Trans. Ind. Electron. 2017, 64, 2102–2111. [Google Scholar] [CrossRef]

- Wu, D.; Wu, X.; Su, L.; Yuan, X.; Xu, J. A Dual Three-Level inverter -Based Open-End Winding Induction Motor Drive with Averaged Zero-Sequence Voltage Elimination and Neutral-Point Voltage Balance. IEEE Trans. Ind. Electron. 2016, 63, 4783–4795. [Google Scholar] [CrossRef]

- Somasekhar, V.T.; Srinivas, S.; Kumar, K.K. Effect of Zero-Vector Placement in a Dual -Inverter Fed Open-End Winding Induction-Motor Drive with a Decoupled Space-Vector PWM Strategy. IEEE Trans. Ind. Electron. 2008, 55, 2497–2505. [Google Scholar] [CrossRef]

- Umeshi, B.S.; Sivakumar, K. Dual-Inverter-Fed Pole-Phase Modulated Nine-Phase Induction Motor Drive with Improved Performance. IEEE Trans. Ind. Electron. 2016, 63, 5376–5383. [Google Scholar] [CrossRef]

- Somani, A.; Gupta, R.K.; Mohapatra, K.K.; Mohan, N. On the Causes of Circulating Currents in PWM Drives with Open-End Winding AC Machines. IEEE Trans. Ind. Electron. 2013, 60, 3670–3678. [Google Scholar] [CrossRef]

- Mitsudome, K.; Haga, H.; Kondo, S. Improvement of Output Voltage Waveform in Dual Inverter Having a Different DC Power Supply. In Proceedings of the IEEJ Technical Meeting on Semiconductor Power Converter and Motor Drive, Osaka, Japan, 23–24 January 2015; pp. 77–82. [Google Scholar]

- Ewanchuk, J.; Salmon, J.; Chapelsky, C. A Method for Supply Voltage Boosting in an Open-Ended Induction Machine Using a Dual Inverter System with a Floating Capacitor Bridge. IEEE Trans. Power Electron. 2013, 28, 1348–1357. [Google Scholar] [CrossRef]

- Machiya, H.; Haga, H.; Kondo, S. High Efficiency Drive Method of an Open-Winding Induction Machine Driven by Dual Inverter using Capacitor Across DC Bus. IEEJ Trans. Ind. Appl. 2015, 135, 10–18. [Google Scholar] [CrossRef]

- Corzine, K.A.; Wielevski, M.W.; Peng, F.Z.; Wang, J. Control of Cascaded Multi-Level Inverters. IEEE Trans. Power Electron. 2004, 19, 732–738. [Google Scholar] [CrossRef]

- Corzine, K.A.; Lu, S.; Fikse, T.H. Distributed Control of Hybrid Motor Drives. IEEE Trans. Power Electron. 2006, 21, 1374–1384. [Google Scholar] [CrossRef]

- Kim, J.; Jung, J.; Nam, K. Dual-Inverter Control Strategy for High-Speed Operation of EV Induction Motors. IEEE Trans. Ind. Electron. 2004, 51, 312–320. [Google Scholar] [CrossRef]

- Chowdhury, S.; Wheeler, P.W.; Gerada, C.; Patel, C. Model Predictive Control for a Dual-Active Bridge Inverter with a Floating Bridge. IEEE Trans. Ind. Electron. 2016, 63, 5558–5568. [Google Scholar] [CrossRef]

- Zhao, W.; Chen, Z.; Xu, D.; Ji, J.; Zhao, P. Unity Power Factor Fault-Tolerant Control of Linear Permanent-Magnet Vernier Motor Fed by a Floating Bridge Multilevel Inverter with Switch Fault. IEEE Trans. Ind. Electron. 2018, 65, 9113–9123. [Google Scholar] [CrossRef]

- Zhao, W.; Wu, B.; Chen, Q.; Zhu, J. Fault-Tolerant Direct Thrust Force Control for a Dual Inverter Fed Open-End Winding Linear Vernier Permanent-Magnet Motor Using Improved SVPWM. IEEE Trans. Ind. Electron. 2018, 65, 7458–7467. [Google Scholar] [CrossRef]

- Nallamekala, K.K.; Sivakumar, K. A Fault-Tolerant Dual Three-Level Inverter Configuration for Multipole Induction Motor Drive with Reduced Torque Ripple. IEEE Trans. Ind. Electron. 2016, 63, 1450–1457. [Google Scholar] [CrossRef]

- Gould, C.; Wang, J.; Stone, D.; Foster, M. EV/HEV Li-ion battery modelling and State-of-Function determination. In Proceedings of the International Symposium on Power Electronics, Electrical Drives, Automation and Motion, Sorrento, Italy, 20–22 June 2012. [Google Scholar]

- Burke, A.; Miller, M. Life cycle testing of lithium batteries for fast charging and second-use applications. In Proceedings of the World Electric Vehicle Symposium and Exhibition, Barcelona, Spain, 17–20 November 2013. [Google Scholar]

- Ohto, Y.; Noguchi, T.; Sasaya, T. Space Vector Modulation of Dual Inverter Taking Power Factor of Open-End Winding Motor. In Proceedings of the IEEJ Annual National Conference, Sendai, Japan, 16–18 March 2016; pp. 71–72. [Google Scholar]

- Oto, Y.; Noguchi, T. Fault-Tolerant Function of DC-Bus Power Source in A Dual Inverter Drive System and Its Operation Characteristics. IEEJ J. Ind. Appl. 2019, in press. [Google Scholar]

- Oto, Y.; Noguchi, T. Fault Tolerant Operation of Motor Drive Fed by Dual Inverter Focusing on DC-Bus Battery Failure. In Proceedings of the International Conference on Electrical Machines and Systems, Harbin, China, 11–14 August 2019. [Google Scholar]

- Mizukoshi, A.; Haga, H. Improvement of Output Voltage Waveform in Dual Inverter Having a Different DC Power Supply. In Proceedings of the IEEE Energy Conversion Congress and Expo, Portland, Oregon, 23–27 September 2018. [Google Scholar]

- Oto, Y.; Noguchi, T.; Sasaya, T.; Yamada, T.; Kazaoka, R. Space Vector Modulation of Dual Inverter System Focusing on Improvement of Multilevel Voltage Waveforms. In IEEE Transactions on Industrial Electronics; IEEE: Piscataway, NJ, USA, 2018. [Google Scholar]

- Noguchi, T.; Kumakiri, Y. On-line Parameter Identification of IPM Motor Using Instantaneous Reactive Power for Robust Maximum Torque Control. In Proceedings of the IEEE International Conference on Industrial Technology, Seville, Spain, 17–19 March 2015. [Google Scholar]

| State | INV1 | INV2 | Phase Voltage | ||

|---|---|---|---|---|---|

| p1 | n1 | p2 | n2 | ||

| #1 | 1 | 0 | 1 | 0 | Vdc1 − Vdc2 |

| #2 | 1 | 0 | 0 | 0 | Vdc1 − Vdc2 |

| #3 | 0 | 0 | 0 | 1 | 0 |

| #4 | 0 | 1 | 0 | 1 | 0 |

| Items | Values | |

|---|---|---|

| Switching frequency | 10 kHz | |

| DC-bus battery voltages in normal situation | 100 V | |

| Capacitor voltage command in fault situation | 50 ± 5 V | |

| Capacitance of capacitor across DC-bus | 1330 µF | |

| Motor rotating speed | 1180 r/min | |

| Dead time | 4 µs | |

| d-axis current command in normal situation | −0.14 A | |

| q-axis current command in normal situation | 0.99 A | |

| d-axis current command in fault situation | −6.33 A | |

| q-axis current command in fault situation | 0.99 A | |

| Motor parameters | Number of poles | 8 |

| Rated power | 1000 W | |

| Rated speed | 2000 r/min | |

| Rated torque | 4.78 Nm | |

| Rated current | 3.7 A | |

| Number of flux linkage | 0.174 Wb | |

| Armature resistance | 1.1 Ω | |

| d-axis inductance | 11.0 mH | |

| q-axis inductance | 25.0 mH | |

| THD of Vu [%] | irms [A] | Efficiencies [%] | |||

|---|---|---|---|---|---|

| INV1 | INV2 | Motor | |||

| Normal situation | 13.7 | 0.59 | 96.0 | 96.4 | 42.0 |

| Fault situation | 13.0 | 3.74 | 88.4 | No data 1 | 4.1 |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Oto, Y.; Noguchi, T.; Fauziah, M.B. Experimental Verification of Fault Tolerant Operation Focusing on DC-Bus Battery Failure in Dual Inverter Motor Drive. World Electr. Veh. J. 2019, 10, 65. https://doi.org/10.3390/wevj10040065

Oto Y, Noguchi T, Fauziah MB. Experimental Verification of Fault Tolerant Operation Focusing on DC-Bus Battery Failure in Dual Inverter Motor Drive. World Electric Vehicle Journal. 2019; 10(4):65. https://doi.org/10.3390/wevj10040065

Chicago/Turabian StyleOto, Yoshiaki, Toshihiko Noguchi, and Melinda Badriatul Fauziah. 2019. "Experimental Verification of Fault Tolerant Operation Focusing on DC-Bus Battery Failure in Dual Inverter Motor Drive" World Electric Vehicle Journal 10, no. 4: 65. https://doi.org/10.3390/wevj10040065

APA StyleOto, Y., Noguchi, T., & Fauziah, M. B. (2019). Experimental Verification of Fault Tolerant Operation Focusing on DC-Bus Battery Failure in Dual Inverter Motor Drive. World Electric Vehicle Journal, 10(4), 65. https://doi.org/10.3390/wevj10040065