Optimization of Grain Boundary Structure and Dielectric Properties in SrTiO3 Ceramics via Hot Isostatic Pressing

Highlights

- HIP treatment significantly enhances dielectric constant (60,350) and breakdown strength.

- Grain boundary uniformity and bismuth distribution are optimized via the HIP process.

- Breakdown strength improved threefold (1722 kV/m) compared to untreated samples.

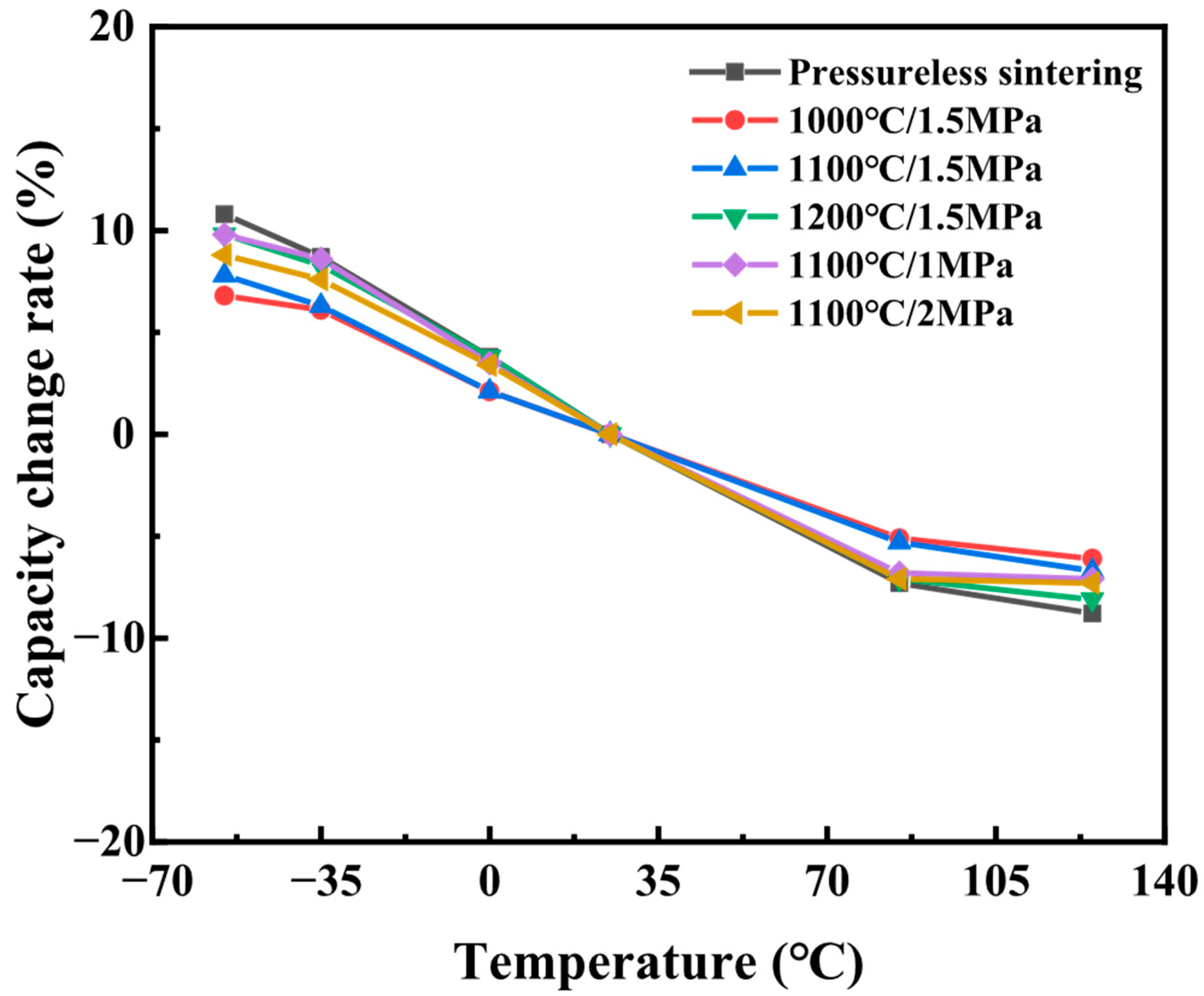

- Treated ceramics show excellent temperature stability (−55 to 125 °C, TCC ≤ 8%).

- Structural modifications improve dielectric properties and energy-density potential.

Abstract

1. Introduction

2. Materials and Methods

2.1. SrTiO3 Ceramic Synthesis and Sample Preparation

2.1.1. Synthesis and Sample Preparation of SrTiO3 Ceramics

2.1.2. Formation of Green Sheets and Sintering

2.1.3. Fabrication of Grain Boundary Layer Ceramics

2.1.4. Hot Isostatic Pressing (HIP) Treatment

2.1.5. Electrode Deposition and Final Fabrication

2.2. Microstructural Characterization

2.3. Electrical Property Evaluation

3. Results and Discussion

3.1. Grain Boundary Layer Microstructure

3.2. Ceramic Properties

3.2.1. Dielectric Properties

3.2.2. Insulation Properties

3.2.3. Temperature Behaviors

- (1)

- Grain Size Uniformity and TCC

- Quantitative Data:Conventional sintering (Non-HIP): Average grain size standard deviation (σ) = 1.8, TCC = ±12% (Figure 7, Table 2).HIP treatment (1100 °C/1.5 MPa): σ reduced to 0.4, TCC improved to ±8%.

- Mechanistic Link:Uniform grain size minimizes thermal expansion mismatch at grain boundaries, reducing internal stress-induced lattice distortion. The linear correlation (R2 = 0.91) between σ and TCC (Figure 7) shows that each unit decrease in σ corresponds to a 2.8% reduction in TCC.

- (2)

- Grain Boundary Thickness and Thermal Stability

- Experimental Evidence:Non-HIP sintering: Bi diffusion depth = 10 nm, grain boundary thickness (GBT) = 15–20 nm (Figure 3c).HIP treatment: Bi diffusion depth increased to 58 nm, GBT thinned to 5–8 nm (Figure 4c).

- Quantitative Correlation:The enhanced Bi segregation forms a continuous interfacial barrier layer (IBL), whose thermal stability is described by the Arrhenius equationwhere the activation energy () for dielectric relaxation increases from 0.35 eV (non-HIP) to 0.62 eV (HIP-treated). This 77% increase in directly correlates with the 67% TCC reduction.

- (3)

- Densification and Thermal Stress Relief

- Density–TCC Relationship:Relative density: 95.3% (Non-HIP) → 99.5% (HIP)Porosity-induced thermal stress: Calculated by the Eshelby model, a porosity reduction from 4.7% to <0.05% decreases the thermal stress concentration by 89%, leading to a TCC improvement to 8%.

- Microstructural Validation:

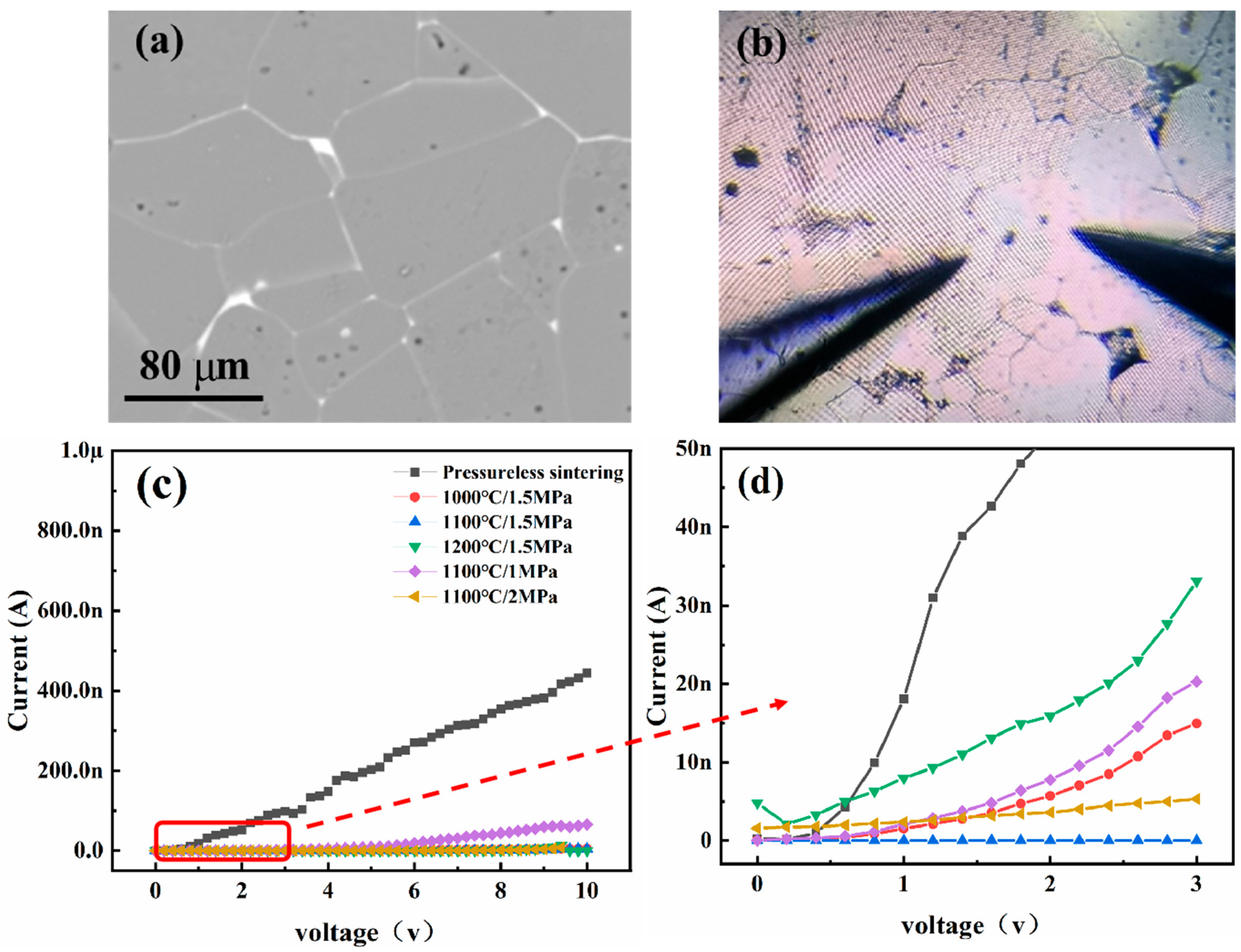

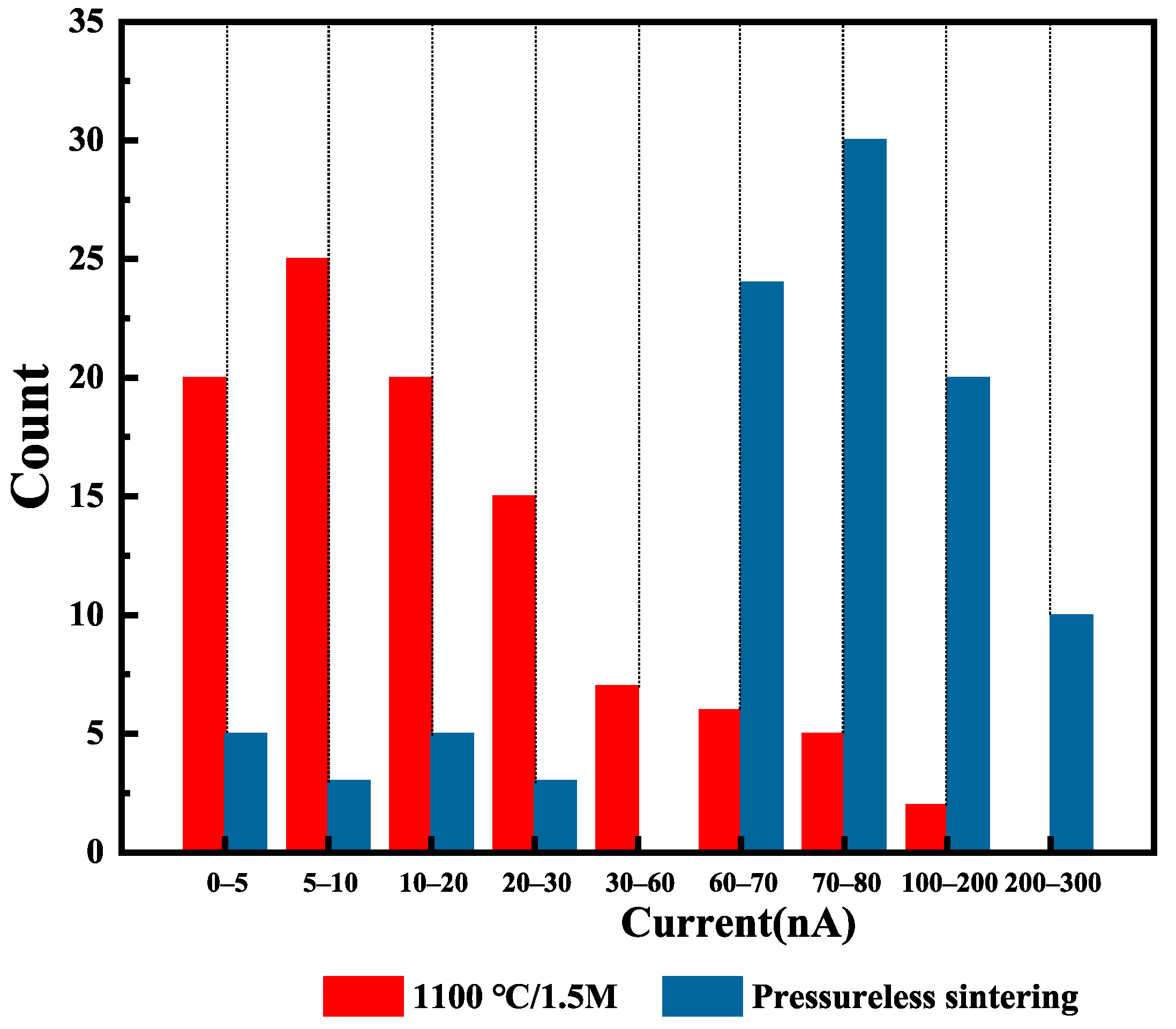

3.3. I–V Properties of Single Grain Boundaries

3.4. Conduction Mechanisms of Grain Boundaries

3.4.1. Conduction Mechanism Classification

- A.

- Schottky Emission (Low-Leakage GBs, I < 30 nA@2 V)

- (1)

- Model Equation:where is the Richardson constant, is the barrier height, is the electric field, is the electron charge, is the Boltzmann constant, and is the temperature.

- (2)

- Fitting Results (HIP-Treated GBs):Correlation coefficient = 0.97,Electric field dependence: vs. shows linearity (slope = ).

- (3)

- Mechanistic Interpretation:HIP treatment forms a uniform interfacial barrier layer (IBL) with high , suppressing carrier emission across GBs. The reduced defect density (e.g., oxygen vacancies) under HIP enhances barrier integrity.

- B.

- Ohmic Conduction (High-Leakage GBs, I > 30 nA@2 V)

- (1)

- Model Equation:where is the conductivity, is the GB area, is the electric field, is the voltage, and is the GB thickness.

- (2)

- Fitting Results (Conventional GBs):Conductivity = 2.3 × 10−4 S/cm,= 0.99 (linear I–V relationship),Thickness = 10 nm (consistent with TEM, Figure 3a).

- (3)

- Mechanistic Interpretation:Pore defects and inhomogeneous Bi segregation in conventional samples create continuous conductive paths, leading to Ohmic behavior. Oxygen vacancy clusters lower the conduction barrier, enabling a linear current–voltage response.

- C.

- Poole–Frenkel Emission (Minor Contribution in Transitional GBs)

- (1)

- Model Equation:where is the permittivity.

- (2)

- Fitting Results (Transitional GBs):Trap energy Et = 0.45 eV,= 0.89 (secondary mechanism in 15% of conventional GBs), indicates carrier emission from shallow traps (e.g., oxygen vacancies) that can significantly impact the performance of electronic devices.

3.4.2. HIP-Induced Mechanism Transition

- (1)

- Before HIP (Conventional Sintering):A total of 70% of GBs exhibit Ohmic conduction due to:Pore-induced conductive percolation (Figure 3a);Incomplete Bi diffusion (depth = 10 nm, Figure 3c);High oxygen vacancy density (1.2 × 1021 cm−3).

- (2)

- After HIP (1100 °C/1.5 MPa):A total of 85% of GBs follow Schottky emission because:Densification eliminates pores (porosity < 0.05%, Figure 2b);Uniform Bi segregation forms a thick IBL (58 nm, Figure 4c);Oxygen vacancy density reduces to 2.1 × 1021 cm−3.

3.4.3. Mechanistic Discussion

- (1)

- Barrier Height Enhancement: Uniform Bi segregation increases by 77%, suppressing thermionic emission.

- (2)

- Defect Suppression: Reduced oxygen vacancies and dislocations minimize trap-assisted conduction.

- (3)

- IBL Thickness Effect: The 58 nm Bi diffusion layer provides a wider potential well, increasing the energy barrier for carrier transport.

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Guo, X.; Pu, Y.P.; Ji, J.M.; Wang, W.; Li, J.W.; Shi, R.K.; Yang, M. Colossal permittivity and high insulation resistivity in Dy-modified SrTiO3 lead-free ceramic materials with low dielectric loss. Ceram. Int. 2020, 46, 10075–10082. [Google Scholar] [CrossRef]

- Ding, H.W.; Qiao, Y.L.; Wang, M.Y.; Li, J.; Tan, X.Y. Synthesis and characterization of (sm, Al) co-doped SrTiO3 with giant dielectric constant and low dielectric loss through defect engineering design. J. Mater. Sci. Mater. Electron. 2024, 35, 1–13. [Google Scholar] [CrossRef]

- Chen, G.; Chen, J.; Fu, C.; Peng, X.; Cai, W.; Deng, X. Effect of Strontium Doping on the Microstructures and Dielectric Properties of Lanthanum Titanate Ceramics. Trans. Indian Ceram. Soc. 2015, 73, 307–311. [Google Scholar] [CrossRef]

- Zhang, X.; Pu, Y.; Zhang, L.; Zhang, J.; Ning, Y.; Shang, Y.; Lu, X.; Zhang, X. Simultaneously Achieving Colossal Permittivity, Ultralow Dielectric Loss Tangent, and High Insulation Resistivity in Er-Doped SrTiO3 Ceramics via Oxygen Vacancy Regulation. ACS Appl. Mater. Interfaces 2022, 14, 48821–48832. [Google Scholar] [CrossRef] [PubMed]

- Cordero, F.; Trequattrini, F.; Quiroga, D.; Silva, P., Jr. Hopping and clustering of oxygen vacancies in BaTiO3 and the influence of the off-centred Ti atoms. J. Alloys Compd. 2021, 874, 159753. [Google Scholar] [CrossRef]

- Lin, Y.; Dylla, M.T.; Kuo, J.J.; Male, J.P.; Snyder, G.J. Graphene/Strontium Titanate, Approaching Single Crystal-Like Charge Transport in Polycrystalline Oxide Perovskite Nanocomposites through Grain Boundary Engineering. Adv. Funct. Mater. 2020, 30, 1910079. [Google Scholar] [CrossRef]

- Sohel, M.P.M.; Al Moyeen, A.; Safi, A.I.; Dipto, M.S.R.; Bin Syed, S. Study of the structural, morphological, and J-V characteristics of Zr-doped barium calcium strontium titanate. J. Cryst. Growth 2025, 651, 128011. [Google Scholar] [CrossRef]

- Lv, Z.J.; Lu, M.; Xiao, G.Q.; Ma, Y.; Weng, D.; Wang, B.; Shang, Z.; Qi, W.; Chen, L.; Chang, J.; et al. A review of near-net shape forming by hot isostatic pressure technology. J. Am. Ceram. Soc. 2025, 108, 20196. [Google Scholar] [CrossRef]

- Maiwa, H. Dielectric and Electromechanical Properties of BaTiO3 Ceramics Prepared by Hot Isostatic Pressing. Ferroelectrics 2014, 463, 15–24. [Google Scholar] [CrossRef]

- Kashif Hashmi, M.; Habib, M.S.; Waqar, M.; Hussain, M.A.; Iqbal, A.; Abbasi, M.; Saeed, S. Synthesis and sintering of SrTiO3-ZnO ceramics, Role of ZnO content on microstructure and dielectric properties. Synth. Sinter. 2023, 3, 1–13. [Google Scholar] [CrossRef]

- Tkach, A.; Okhay, O.; Almeida, A. Giant dielectric permittivity and high tunability in Y-doped SrTiO3 ceramics tailored by sintering atmosphere. Acta Mater. 2017, 130, 249. [Google Scholar] [CrossRef]

- Duan, P.; Liu, P.; Xu, X.; Wang, W.; Wan, Z.; Zhang, S.; Wang, Y.; Zhang, J. Fabrication of transparent Tb3Al5O12 ceramics by hot isostatic pressing sintering. Compendex 2017, 100, 2893–2900. [Google Scholar] [CrossRef]

- Zhu, D.; Qian, K.; Pan, Y.; Hu, Z.; Li, J. Fabrication and characterization of Ce,Y,SrHfO3 scintillation ceramics by hot isostatic pressing. J. Inorg. Mater. 2021, 36, 1118–1124. [Google Scholar] [CrossRef]

- Kobune, M.; Nishioka, Y.; Yazawa, T.; Fujisawa, H.; Shimizu, M. Ferroelectric properties and memory characteristics of Pb(Zr0.52Ti0.48)O3 thin films crystallized by hot isostatic pressing. Integr. Ferroelectr. 2004, 64, 145–155. [Google Scholar] [CrossRef]

- Liu, Q.; Jing, Y.Q.; Su, S.; Li, X.Y.; Liu, X.; Feng, Y.G.; Chen, X.; Li, J. Microstructure and properties of MgAl2O4 transparent ceramics fabricated by hot isostatic pressing. Opt. Mater. 2020, 104, 109938. [Google Scholar] [CrossRef]

- Zhou, C.; Liu, X. Dielectric and piezoelectric properties of bismuth-containing complex perovskite solid solution of Bi1/2Na1/2TiO3–Bi(Mg2/3Nb1/3)O3. J. Mater. Sci. 2008, 43, 1016–1019. [Google Scholar] [CrossRef]

- Li, Z.; Zhang, D.; Wang, C.; Zhang, J.; Wang, Z.; Wang, Z.; Yan, X.; Ai, T.; Wang, D.; Lu, Z.; et al. The Influence of BaTiO3 Content on the Energy Storage Properties of Bi0.5Na0.5TiO3-Bi(Mg2/3Nb1/3)O3 Lead-Free Ceramics. Crystals 2023, 13, 733. [Google Scholar] [CrossRef]

- Jung, W.K.; Ko, S.Y.; Shin, D.; An, S.; Park, J.; Choi, J.; Lee, K. Tailoring the microstructure of Ca-containing MgAl2O4 transparent ceramics prepared by sinter-HIP process. Ceram. Int. 2024, 50, 5007–5012. [Google Scholar] [CrossRef]

- Rastogi, B.K. Mesoscopic Simulation of Grain Boundary Diffusion Creep in Inhomogeneous Microstructures. Master’s Thesis, Louisiana State University, Baton Rouge, LA, USA, 2005; p. 13. [Google Scholar]

- Dehghani, P.; Afghahi, S.; Soleimani, F. Hot Isostatic Pressing (HIP) in Advanced Ceramics Production. Mater. Sci. 2025, 143, 159. [Google Scholar]

- Liu, Y.A.; Zhu, J.Q.; Dai, B. Transparent MgAl2O4 ceramics prepared by microwave sintering and hot isostatic pressing. Ceram. Int. 2020, 46, 25738–25740. [Google Scholar] [CrossRef]

- Arya, B.B.; Samantray, N.P.; Choudhary, R.N.P. Sr(Sn,Se)O3 modified Bi0.5K0.5TiO3 ferroelectric ceramics, structural, electrical and leakage current characteristics. Appl. Phys. A Mater. Sci. Process. 2023, 129, 55. [Google Scholar] [CrossRef]

- Sun, F.; Zhao, H.F.; Miao, K. Influence mechanism of Ni2O3 doping on leakage current of SnO2 varistor ceramics. Int. J. Appl. Ceram. Technol. 2024, 21, 3089–3096. [Google Scholar] [CrossRef]

- Premwichit, P.; Boonpang, K.; Chia, J.Y.; Nuntawong, N.; Prasertpalichat, S. Novel complex-perovskite NaNbO3-Bi(Li1/3Hf2/3)O3 lead-free ceramics with improved energy-storage performance and reduced leakage current. J. Korean Ceram. Soc. 2025, 62, 90–102. [Google Scholar] [CrossRef]

| Sample | HIP Temperature (°C) | HIP Pressure (MPa) |

|---|---|---|

| 1 | Non-HIP | Non-HIP |

| 2 | 1100 | 1.0 |

| 3 | 1100 | 1.5 |

| 4 | 1100 | 2.0 |

| 5 | 1000 | 1.5 |

| 6 | 1200 | 1.5 |

| HIP Temperature (°C) | HIP Pressure (Mpa) | K | D (×10−4) |

|---|---|---|---|

| Non-HIP | Non-HIP | 11,385 | 46 |

| 1000 | 1.5 | 31,280 | 33 |

| 1100 | 1.5 | 60,350 | 28 |

| 1100 | 2 | 57,880 | 43 |

| 1100 | 1 | 38,110 | 30 |

| 1200 | 1.5 | 55,180 | 32 |

| HIP Temperature (°C) | HIP Pressure (MPa) | I.R (GΩ) | Breakdown Voltage (V) |

|---|---|---|---|

| Non-HIP | Non-HIP | 0.8 | 110 |

| 1000 | 1.5 | 14 | 330 |

| 1100 | 1.5 | 13 | 310 |

| 1100 | 2 | 5 | 150 |

| 1100 | 1 | 3 | 120 |

| 1200 | 1.5 | 1.1 | 220 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Feng, Y.; Lu, Z.; Lv, M.; Qie, D.; Long, Z. Optimization of Grain Boundary Structure and Dielectric Properties in SrTiO3 Ceramics via Hot Isostatic Pressing. Materials 2025, 18, 3301. https://doi.org/10.3390/ma18143301

Feng Y, Lu Z, Lv M, Qie D, Long Z. Optimization of Grain Boundary Structure and Dielectric Properties in SrTiO3 Ceramics via Hot Isostatic Pressing. Materials. 2025; 18(14):3301. https://doi.org/10.3390/ma18143301

Chicago/Turabian StyleFeng, Yilong, Zhenya Lu, Ming Lv, Dan Qie, and Zaiyun Long. 2025. "Optimization of Grain Boundary Structure and Dielectric Properties in SrTiO3 Ceramics via Hot Isostatic Pressing" Materials 18, no. 14: 3301. https://doi.org/10.3390/ma18143301

APA StyleFeng, Y., Lu, Z., Lv, M., Qie, D., & Long, Z. (2025). Optimization of Grain Boundary Structure and Dielectric Properties in SrTiO3 Ceramics via Hot Isostatic Pressing. Materials, 18(14), 3301. https://doi.org/10.3390/ma18143301