Analog Resistive Switching and Artificial Synaptic Behavior of ITO/WOX/TaN Memristors

Abstract

1. Introduction

2. Materials and Methods

2.1. Preparation Method

2.2. Test and Characterization

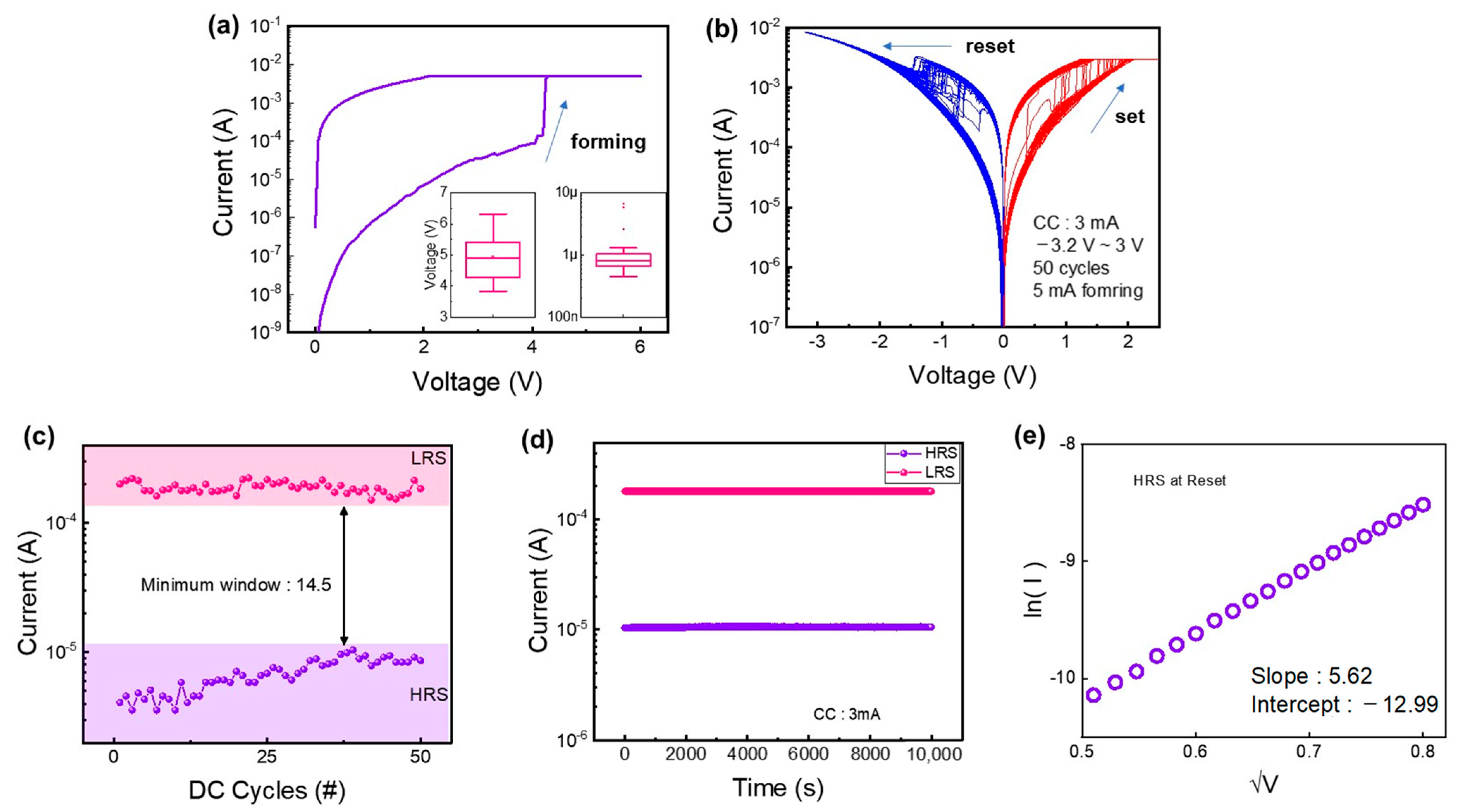

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Hung, J.M.; Li, X.; Wu, J.; Chang, M.F. Challenges and trends in developing nonvolatile memory-enabled computing chips for intelligent edge devices. IEEE Trans. Electron Devices 2020, 67, 1444–1453. [Google Scholar] [CrossRef]

- Kim, S.; Yong, S.; Kim, W.; Kang, S.; Park, H.; Yoon, K.; Sheen, D.; Lee, S.; Hwang, C. Review of semiconductor flash memory devices for material and process issues. Adv. Mater. 2022, 2022, 2200659. [Google Scholar] [CrossRef] [PubMed]

- Lee, G.; Hwang, S.; Yu, J.; Kim, H. Architecture and process integration overview of 3D NAND flash technologies. Appl. Sci. 2021, 11, 6703. [Google Scholar] [CrossRef]

- Luo, Z.-D.; Zhang, S.; Liu, Y.; Zhang, D.; Gan, X.; Seidel, J.; Liu, Y.; Han, G.; Alexe, M.; Hao, Y. Dual-Ferroelectric-Coupling-Engineered Two-Dimensional Transistors for Multifunctional In-Memory Computing. ACS Nano 2022, 16, 3362–3372. [Google Scholar] [CrossRef]

- Khan, A.I.; Keshavarzi, A.; Datta, S. The future of ferroelectric field-effect transistor technology. Nat. Electron. 2020, 3, 588–597. [Google Scholar] [CrossRef]

- Burr, G.W. Phase change memory technology. J. Vac. Sci. Technol. B 2010, 25, 223. [Google Scholar] [CrossRef]

- Ishdorj, B.; Kim, J.; Kim, J.H.; Na, T. A Timing-Based Split-Path Sensing Circuit for STT-MRAM. Micromachines 2022, 13, 1004. [Google Scholar] [CrossRef]

- Kwon, O.; Lee, Y.; Kang, M.; Kim, S. Synaptic plasticity features and neuromorphic system simulation in AlN-based memristor devices. J. Alloy. Compd. 2022, 911, 164870. [Google Scholar] [CrossRef]

- Dastgeer, G.; Afzal, A.M.; Aziz, J.; Hussain, S.; Jaffery, S.H.A.; Kim, D.; Imran, M.; Assiri, M.A. Flexible Memory Device Composed of Metal-Oxide and Two-Dimensional material (SnO2/WTe2) Exhibiting Stable Resistive Switching. Materials 2021, 14, 7535. [Google Scholar] [CrossRef]

- Huang, C.H.; Huang, J.S.; Lai, C.C.; Huang, H.W.; Lin, S.J.; Chueh, Y.L. Manipulated Transformation of Filamentary and Homogeneous Resistive Switching on ZnO Thin Film Memristor with Controllable Multistate. ACS Appl. Mater. Interfaces 2013, 5, 6017–6023. [Google Scholar] [CrossRef]

- Lee, S.H.; Zhu, X.; Lu, W.D. Nanoscale resistive switching devices for memory and computing applications. Nano Res. 2020, 13, 1228–1243. [Google Scholar] [CrossRef]

- Pan, C.H.; Chang, T.C.; Tsai, T.M.; Chang, K.C.; Chu, T.J.; Lin, W.Y.; Chen, M.C.; Sze, S.M. Confirmation of filament dissolution behavior by analyzing electrical field effect during reset process in oxide-based RRAM. Appl. Phys. Lett. 2016, 109, 133503. [Google Scholar] [CrossRef]

- Lee, S.R.; Kim, Y.B.; Chang, M.; Kim, K.M.; Lee, C.B.; Hur, J.H.; Park, G.S.; Lee, D.; Lee, M.J.; Kim, C.J.; et al. Multi-level switching of triple-layered TaOx RRAM with excellent reliability for storage class memory. In Proceedings of the 2012 Symposium on VLSI Technology (VLSIT), Honolulu, HI, USA, 12–14 June 2012; IEEE: Piscataway, NJ, USA, 2012; pp. 71–72. [Google Scholar] [CrossRef]

- Ielmini, D. Brain-inspired computing with resistive switching memory (RRAM): Devices, synapses and neural networks. Microelectron. Eng. 2018, 190, 44–53. [Google Scholar] [CrossRef]

- Prakash, A.; Jana, D.; Maikap, S. TaOx -based resistive switching memories: Prospective and challenges. Nanoscale Res. Lett. 2013, 8, 1–17. [Google Scholar] [CrossRef]

- Xia, L.; Gu, P.; Li, B.; Tang, T.; Yin, X.; Huangfu, W.; Yu, S.; Cao, Y.; Wang, Y.; Yang, H. Technological Exploration of RRAM Crossbar Array for Matrix-Vector Multiplication. J. Comput. Sci. Technol. 2016, 31, 3–19. [Google Scholar] [CrossRef]

- Zhang, L.; Cosemans, S.; Wouters, D.J.; Govereanu, B.; Groeseneken, G.; Jurczak, M. Analysis of vertical cross-point resistive memory (VRRAM) for 3D RRAM design. In Proceedings of the 2013 5th IEEE International Memory Workshop, Monterey, CA, USA, 26–29 May 2013; IEEE: Piscataway, NJ, USA, 2013; pp. 155–158. [Google Scholar] [CrossRef]

- Hong, X.L.; Loy, D.J.J.; Dananjaya, P.A.; Tan, F.; Ng, C.M.; Lew, W.S. Oxide-based RRAM materials for neuromorphic computing. J. Mater. Sci. 2018, 53, 8720–8746. [Google Scholar] [CrossRef]

- Sun, J.; Han, G.; Zeng, Z.; Wang, Y. Memristor-Based Neural Network Circuit of Full-Function Pavlov Associative Memory With Time Delay and Variable Learning Rate. IEEE Trans. Cybern. 2019, 50, 2935–2945. [Google Scholar] [CrossRef]

- Sun, J.; Wang, Y.; Liu, P.; Wen, S.; Wang, Y. Memristor-Based Neural Network Circuit With Multimode Generalization and Differentiation on Pavlov Associative Memory. IEEE Trans. Cybern. 2022, 1–12. [Google Scholar] [CrossRef]

- Ding, S.; Wang, N.; Bao, H.; Chen, B.; Wu, H.; Xu, Q. Memristor synapse-coupled piecewise-linear simplified Hopfield neural network: Dynamics analysis and circuit implementation. Chaos Solition Fract. 2023, 166, 112899. [Google Scholar] [CrossRef]

- Zokaee, F.; Zarandi, H.R.; Jiang, L.; Aligne, R. A Process-in-Memory Architecture for Short Read Alignment in ReRAMs. IEEE Comput. Archit. Lett. 2018, 17, 237–240. [Google Scholar] [CrossRef]

- Upadhyay, N.K.; Jiang, H.; Asapu, S.; Xia, Q.; Joshua, Y.J. Emerging Memory Devices for Neuromorphic Computing. Adv. Mater. Technol. 2019, 4, 1800589. [Google Scholar] [CrossRef]

- Giacomin, E.; Greenberg-Toledo, T.; Kvatinsky, S.; Gaillardon, P.E. A Robust Digital RRAM-Based Convolutional Block for Low-Power Image Processing and Learning Applications. IEEE Trans. Circuits Syst. I Regul. Pap. 2018, 66, 643–654. [Google Scholar] [CrossRef]

- Sawa, A. Resistive switching in transition metal oxides. Mater. Today 2008, 11, 28–36. [Google Scholar] [CrossRef]

- Sun, C.; Lu, S.M.; Jin, F.; Mo, W.Q.; Song, J.L.; Dong, K.F. The Resistive Switching Characteristics of TiN/HfO2/Ag RRAM Devices with Bidirectional Current Compliance. J. Electron. Mater. 2019, 48, 2992–2999. [Google Scholar] [CrossRef]

- Cheng, C.H.; Chin, A.; Yeh, F.S. Novel Ultra-low power RRAM with good endurance and retention. In Proceedings of the 2010 Symposium on VLSI Technology, Honolulu, Hawaii, 14–17 June 2010; IEEE: Piscataway, NJ, USA, 2010; pp. 85–86. [Google Scholar]

- Simanjunak, F.M.; Panda, D.; Wei, K.H.; Tseng, T.Y. Status and Prospects of ZnO-Based Resistive Switching Memory Devices. Nanoscale Res. Lett. 2016, 11, 368. [Google Scholar] [CrossRef]

- Wu, W.T.; Wu, J.J.; Chen, J.S. Resistive Switching Behavior and Multiple Transmittance States in Solution-Processed Tungsten Oxide. ACS Appl. Mater. Interfaces 2011, 3, 2616–2621. [Google Scholar] [CrossRef]

- Chein, W.C.; Chen, Y.C.; Chang, K.P.; Lai, E.K.; Yao, Y.D.; Lin, P.; Gong, J.; Tsai, S.C.; Hsieh, S.H.; Chen, C.F.; et al. Multi-Level Operation of Fully CMOS Compatible WOX Resistive Random Access Memory (RRAM). In Proceedings of the 2009 IEEE International Memory Workshop, Monterey, CA, USA, 10–14 May 2009; IEEE: Piscataway, NJ, USA, 2009; pp. 1–2. [Google Scholar] [CrossRef]

- Tsai, T.M.; Tan, Y.F.; Wu, C.H.; Yang, C.C.; Chen, W.C.; Lin, C.C.; Wu, P.Y.; Zhang, Y.C.; Chou, S.Y.; Chen, Z.Y.; et al. Impact of oxygen flow rate on performance of indium-tin-oxide-based RRAMs. J. Phys. Appl. Phys. 2021, 54, 295103. [Google Scholar] [CrossRef]

- Wang, H.; Yan, X. Overview of Resistive Random Access Memory (RRAM): Materials, Filament Mechanisms, Performance Optimization, and Prospects. Phys. Status Solidi RRL 2019, 13, 1900073. [Google Scholar] [CrossRef]

- Petzold, S.; Piros, E.; Eihardt, R.; Zintler, A.; Vogel, T.; Kaiser, N.; Radetinac, A.; Komissinskiy, P.; Jalaguier, E.; Nolot, E.; et al. Tailoring the Switching Dynamics in Yttrium Oxide-Based RRAM Devices by Oxygen Engineering: From Digital to Multi-Level Quantization toward Analog Switching. Adv. Electron. Mater. 2020, 6, 2000439. [Google Scholar] [CrossRef]

- Lien, S.Y. Characterization and optimization of ITO thin films for application in heterojunction silicon solar cells. Thin Solid Films 2010, 518, S10–S13. [Google Scholar] [CrossRef]

- Kim, J.; Park, J.; Kim, S. Bipolar Switching Characteristics of Transparent WOX-Based RRAM for Synaptic Application and Neuromorphic Engineering. Materials 2022, 15, 7185. [Google Scholar] [CrossRef]

- Kim, S.I.; Cho, S.H.; Choi, S.R.; Oh, M.C.; Jang, J.H.; Song, P.K. Crystallization and electrical properties of ITO:Ce thin films for flat panel display applications. Thin Solid Films 2009, 517, 4061–4064. [Google Scholar] [CrossRef]

- Luo, Q.; Xu, X.; Liu, H.; Lv, H.; Gong, T.; Long, S.; Liu, Q.; Sun, H.; Banerjee, W.; Li, L.; et al. Demonstration of 3D vertical RRAM with ultra low-leakage, high-selectivity and self-compliance memory cells. In Proceedings of the 2015 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015; IEEE: Piscataway, NJ, USA, 2015; pp. 10.2.1–10.2.4. [Google Scholar] [CrossRef]

- Ismail, M.; Mahata, C.; Kim, S. Electronic synaptic plasticity and analog switching characteristics in Pt/TiOx/AlOx/AlTaON/TaN multilayer RRAM for artificial synapses. Appl. Sur. Sci. 2022, 599, 153906. [Google Scholar] [CrossRef]

- Hsieh, W.K.; Lam, K.T.; Chang, S.J. Bipolar Ni/ZnO/HfO2/Ni RRAM with multilevel characteristic by different reset bias. Mater. Sci. Semicond. Process. 2015, 35, 30–33. [Google Scholar] [CrossRef]

- Shang, D.S.; Shi, L.; Sun, J.R.; Shen, B.G.; Zhunge, F.; Li, R.W.; Zhao, Y.G. Improvement of reproducible resistance switching in polycrystalline tungsten oxide films by in situ oxygen annealing. Appl. Phys. Lett. 2010, 96, 072103. [Google Scholar] [CrossRef]

- Hsu, C.C.; Chuang, H.; Jhang, W.C. Annealing effect on forming-free bipolar resistive switching characteristics of sol-gel WOx resistive memories with Al conductive bridges. J. Alloys Compd. 2021, 882, 160758. [Google Scholar] [CrossRef]

- Lai, E.K.; Chien, W.C.; Chen, Y.C.; Hong, T.J.; Lin, Y.Y.; Chang, K.P.; Yao, Y.D.; Lin, P.; Horng, S.F.; Gong, J. Tungsten Oxide Resistive Memory Using Rapid Thermal Oxidation of Tungsten Plugs. J. Appl. Phys. 2010, 49, 04DD17. [Google Scholar] [CrossRef]

| Device Structure | Process | Forming Voltage (V) | on/off Ratio | Endurance (#) | Retention (s) | Synaptic Properties | Ref. |

|---|---|---|---|---|---|---|---|

| Au/WO3/FTO | PLD | 2.6 | 102 | >104 | >104 | N/A | [40] |

| Al/WOX/ITO | Sol-gel | Forming-free | ~103 | >102 | N/A | N/A | [41] |

| TiN/WOX/W | RTO | 3.5 | >102 | >108 | N/A | N/A | [42] |

| Al/WOX/W | Plasma oxidation | 4 | 10 | >40 | >106 | N/A | [30] |

| ITO/WOX/ITO | Sputtering | Forming-free | ~5 | 300 | >104 | Potentiation/ Depression | [35] |

| ITO/WOX/TaN | Sputtering | 4.91 | >10 | >104 | >104 | Potentiation/ Depression | (This work) |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Cho, Y.; Kim, J.; Kang, M.; Kim, S. Analog Resistive Switching and Artificial Synaptic Behavior of ITO/WOX/TaN Memristors. Materials 2023, 16, 1687. https://doi.org/10.3390/ma16041687

Cho Y, Kim J, Kang M, Kim S. Analog Resistive Switching and Artificial Synaptic Behavior of ITO/WOX/TaN Memristors. Materials. 2023; 16(4):1687. https://doi.org/10.3390/ma16041687

Chicago/Turabian StyleCho, Youngboo, Jihyung Kim, Myounggon Kang, and Sungjun Kim. 2023. "Analog Resistive Switching and Artificial Synaptic Behavior of ITO/WOX/TaN Memristors" Materials 16, no. 4: 1687. https://doi.org/10.3390/ma16041687

APA StyleCho, Y., Kim, J., Kang, M., & Kim, S. (2023). Analog Resistive Switching and Artificial Synaptic Behavior of ITO/WOX/TaN Memristors. Materials, 16(4), 1687. https://doi.org/10.3390/ma16041687