Enhanced Short-Term Memory Plasticity of WOx-Based Memristors by Inserting AlOx Thin Layer

Abstract

1. Introduction

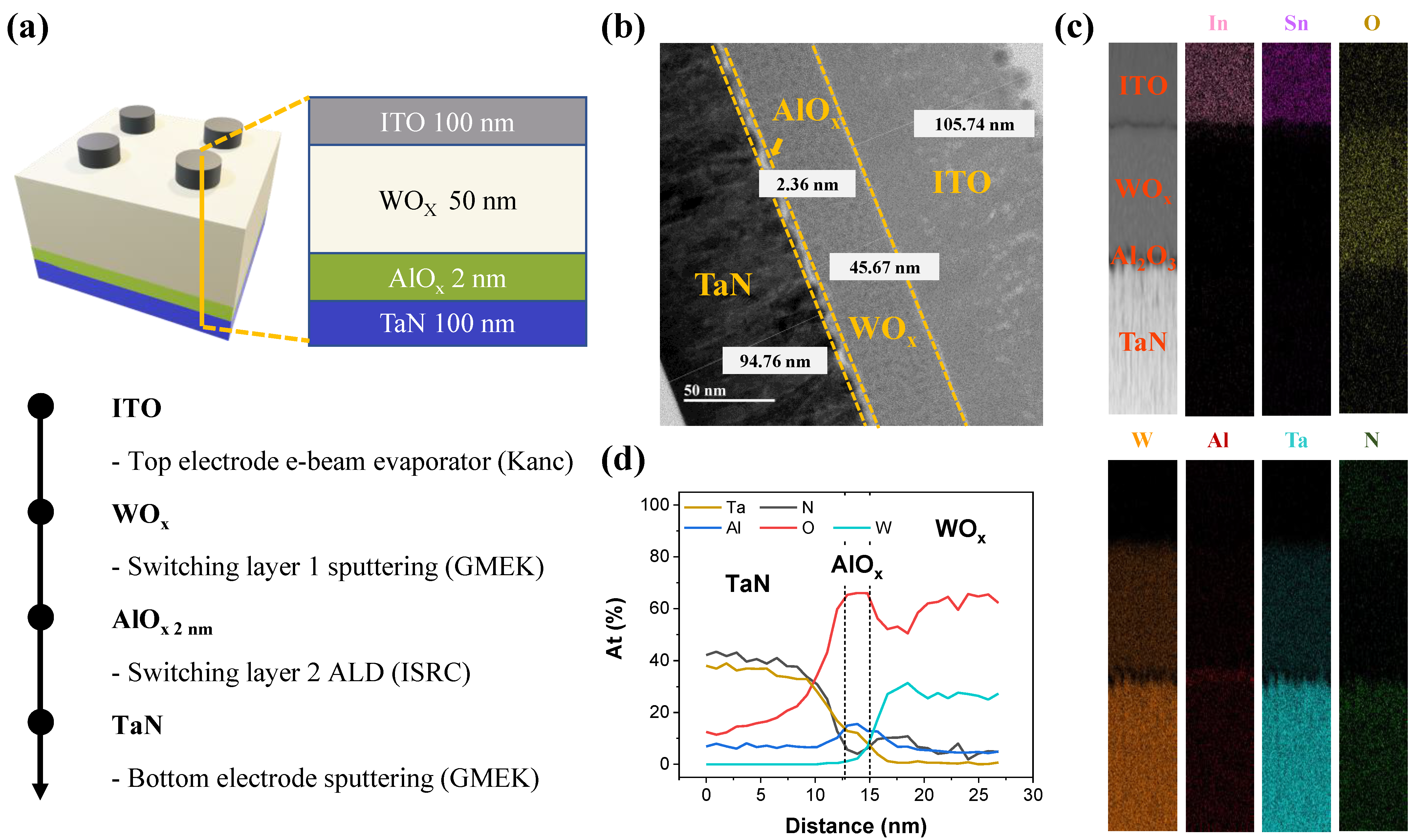

2. Materials and Methods

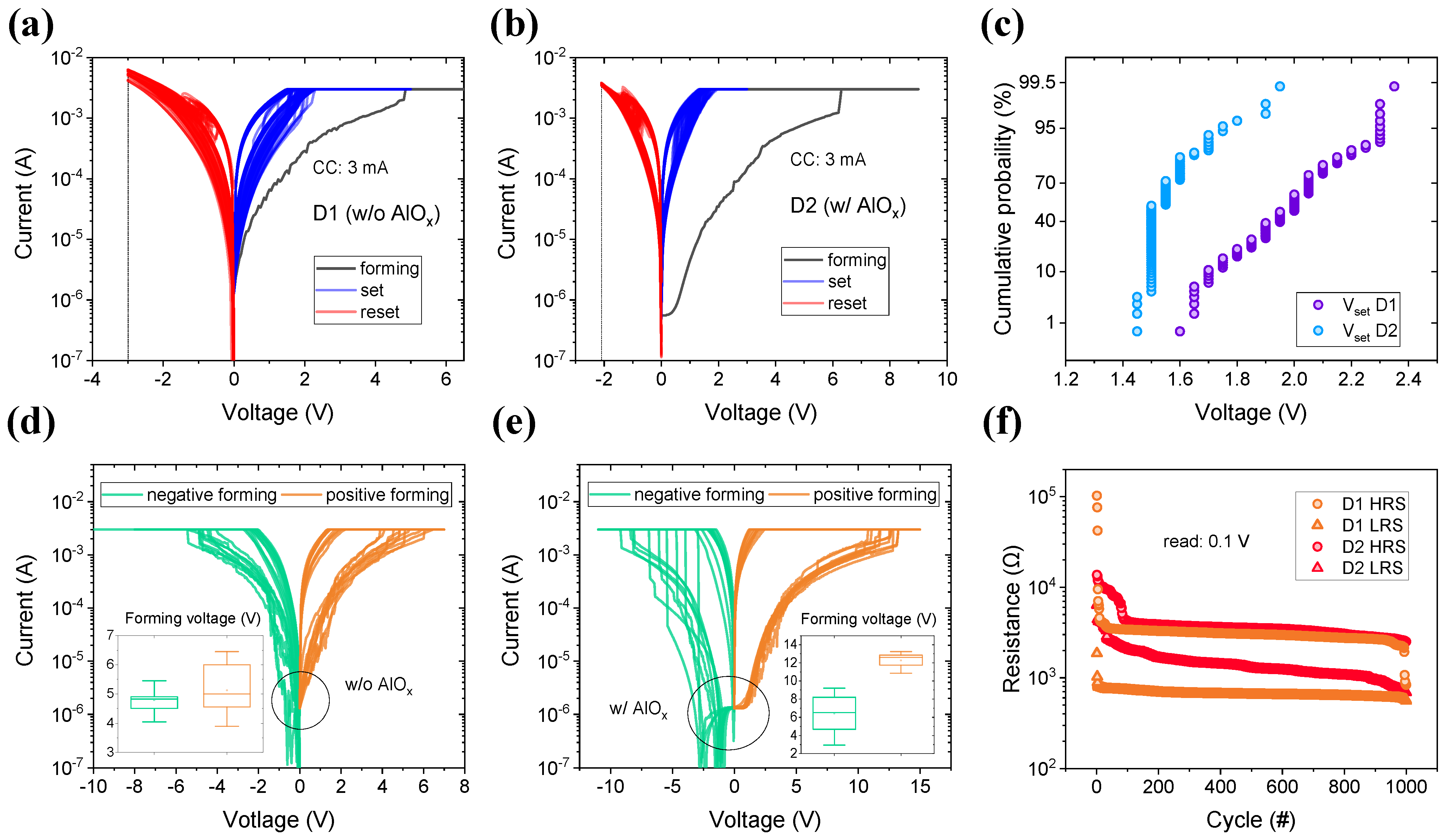

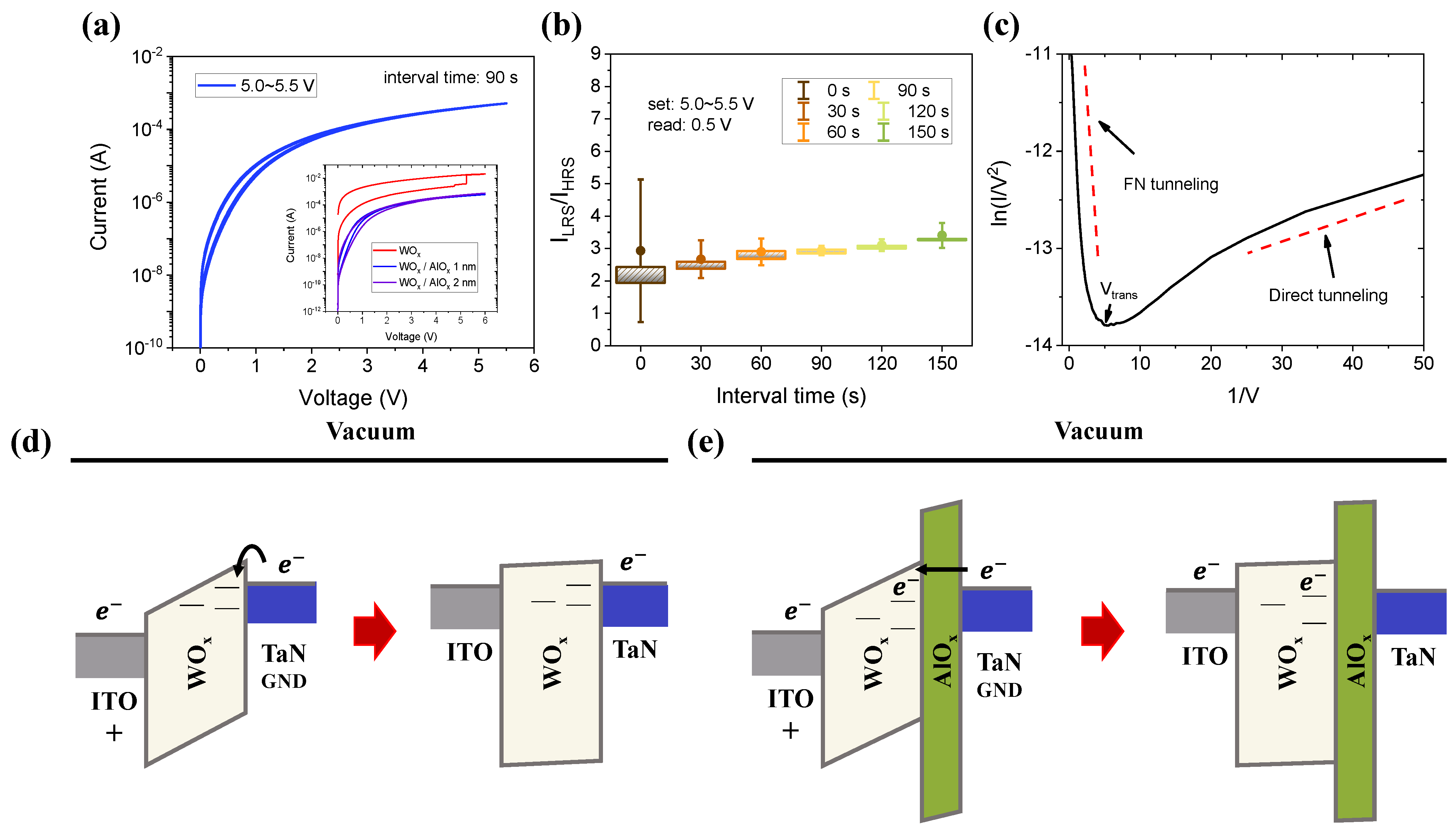

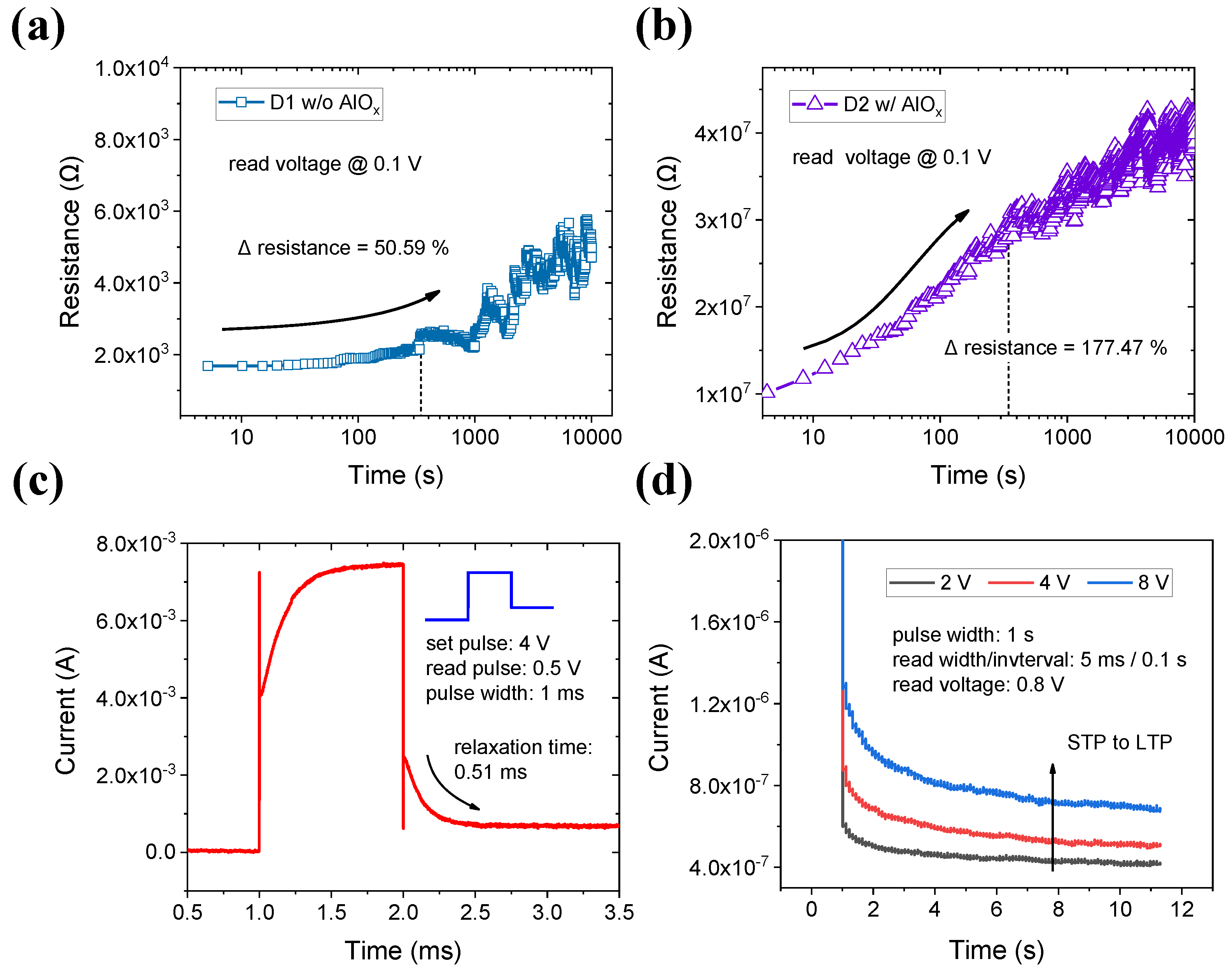

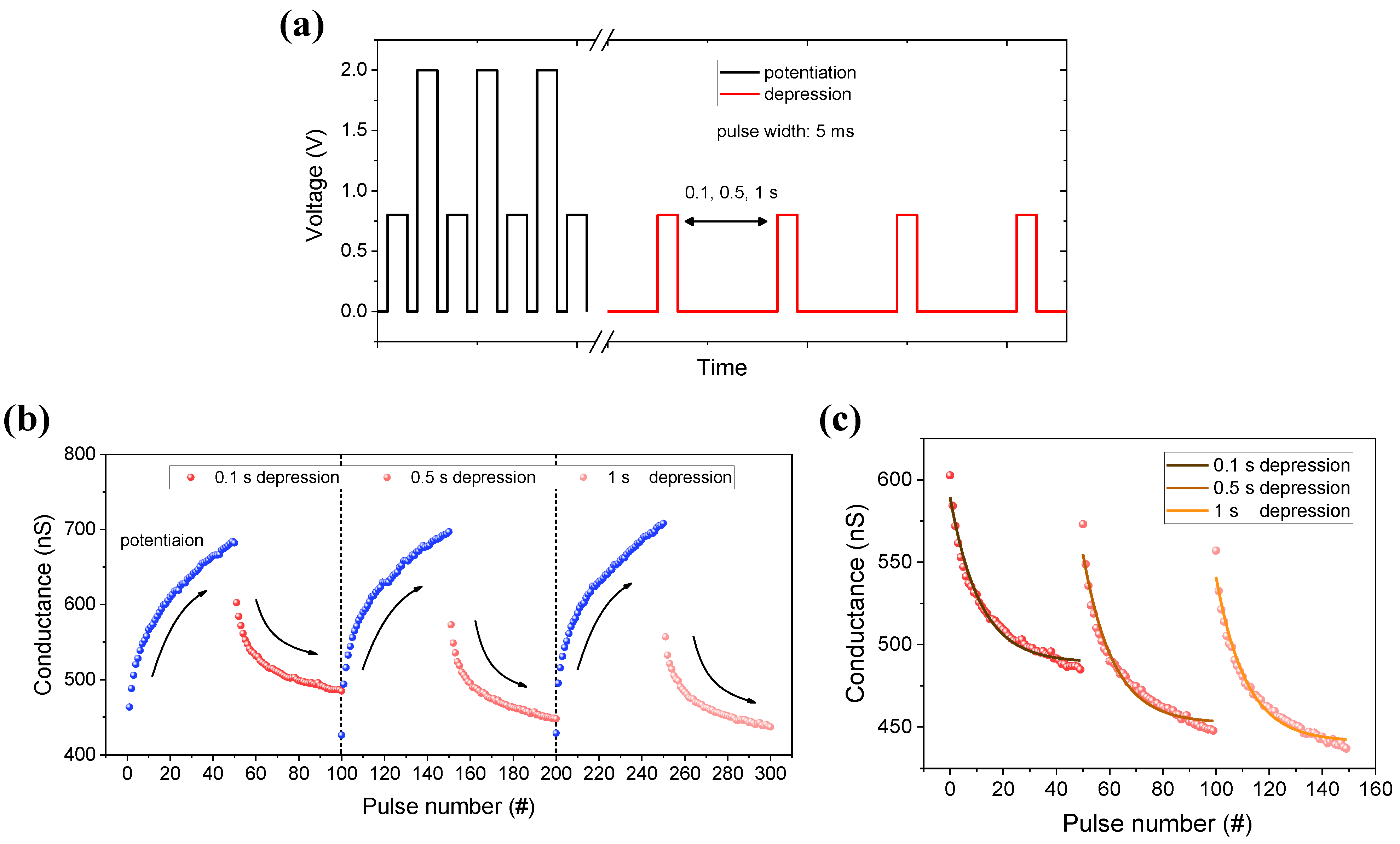

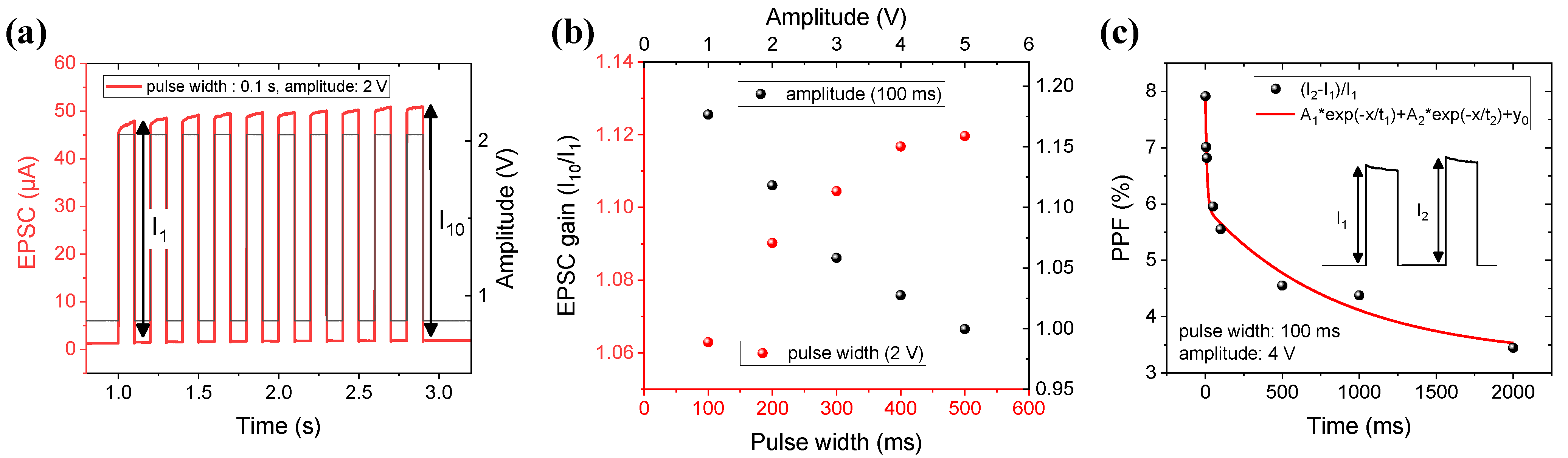

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Zhang, Z.; Wang, Z.; Shi, T.; Bi, C.; Rao, F.; Cai, Y.; Liu, Q.; Wu, H.; Zhou, P. Memory Materials and Devices: From Concept to Application. InfoMat 2020, 2, 261–290. [Google Scholar] [CrossRef]

- Atzori, L.; Iera, A.; Morabito, G. The Internet of Things: A Survey. Comput. Netw. 2010, 54, 2787–2805. [Google Scholar] [CrossRef]

- Zidan, M.A.; Strachan, J.P.; Lu, W.D. The Future of Electronics Based on Memristive Systems. Nat. Electron. 2018, 1, 22–29. [Google Scholar] [CrossRef]

- Kim, S.; Kim, H.; Hwang, S.; Kim, M.H.; Chang, Y.F.; Park, B.G. Analog Synaptic Behavior of a Silicon Nitride Memristor. ACS Appl. Mater. Interfaces 2017, 9, 40420–40427. [Google Scholar] [CrossRef] [PubMed]

- Chen, W.J.; Cheng, C.H.; Lin, P.E.; Tseng, Y.T.; Chang, T.C.; Chen, J.S. Analog Resistive Switching and Synaptic Functions in WOx/TaOxBilayer through Redox-Induced Trap-Controlled Conduction. ACS Appl. Electron. Mater. 2019, 1, 2422–2430. [Google Scholar] [CrossRef]

- Strukov, D.B.; Snider, G.S.; Stewart, D.R.; Williams, R.S. The Missing Memristor Found. Nature 2008, 453, 80–83. [Google Scholar] [CrossRef]

- Ryu, H.; Kim, S. Pseudo-Interface Switching of a Two-Terminal Taox/Hfo2 Synaptic Device for Neuromorphic Applications. Nanomaterials 2020, 10, 1550. [Google Scholar] [CrossRef]

- Shen, Z.; Zhao, C.; Qi, Y.; Xu, W.; Liu, Y.; Mitrovic, I.Z.; Yang, L.; Zhao, C. Advances of RRAM Devices: Resistive Switching Mechanisms, Materials and Bionic Synaptic Application. Nanomaterials 2020, 10, 1437. [Google Scholar] [CrossRef]

- Kim, K.H.; Gaba, S.; Wheeler, D.; Cruz-Albrecht, J.M.; Hussain, T.; Srinivasa, N.; Lu, W. A Functional Hybrid Memristor Crossbar-Array/CMOS System for Data Storage and Neuromorphic Applications. Nano Lett. 2012, 12, 389–395. [Google Scholar] [CrossRef]

- Jo, S.H.; Chang, T.; Ebong, I.; Bhadviya, B.B.; Mazumder, P.; Lu, W. Nanoscale Memristor Device as Synapse in Neuromorphic Systems. Nano Lett. 2010, 10, 1297–1301. [Google Scholar] [CrossRef]

- Burr, G.W.; Shelby, R.M.; Sebastian, A.; Kim, S.; Kim, S.; Sidler, S.; Virwani, K.; Ishii, M.; Narayanan, P.; Fumarola, A.; et al. Neuromorphic Computing Using Non-Volatile Memory. Adv Phys. X 2017, 2, 89–124. [Google Scholar] [CrossRef]

- Upadhyay, N.K.; Jiang, H.; Wang, Z.; Asapu, S.; Xia, Q.; Joshua Yang, J. Emerging Memory Devices for Neuromorphic Computing. Adv. Mater. Technol. 2019, 4, 1800589. [Google Scholar] [CrossRef]

- Kim, C.H.; Lim, S.; Woo, S.Y.; Kang, W.M.; Seo, Y.T.; Lee, S.T.; Lee, S.; Kwon, D.; Oh, S.; Noh, Y.; et al. Emerging Memory Technologies for Neuromorphic Computing. Nanotechnology 2019, 30, 032001. [Google Scholar] [CrossRef] [PubMed]

- Mikhaylov, A.; Pimashkin, A.; Pigareva, Y.; Gerasimova, S.; Gryaznov, E.; Shchanikov, S.; Zuev, A.; Talanov, M.; Lavrov, I.; Demin, V.; et al. Neurohybrid Memristive Cmos-Integrated Systems for Biosensors and Neuroprosthetics. Front. Neurosci. 2020, 14, 358. [Google Scholar] [CrossRef]

- Emelyanov, A.V.; Nikiruy, K.E.; Serenko, A.V.; Sitnikov, A.V.; Presnyakov, M.Y.; Rybka, R.B.; Sboev, A.G.; Rylkov, V.V.; Kashkarov, P.K.; Kovalchuk, M.V.; et al. Self-Adaptive STDP-Based Learning of a Spiking Neuron with Nanocomposite Memristive Weights. Nanotechnology 2019, 31, 045201. [Google Scholar] [CrossRef]

- Cho, H.; Kim, S. Emulation of Biological Synapse Characteristics from Cu/Aln/Tin Conductive Bridge Random Access Memory. Nanomaterials 2020, 10, 1709. [Google Scholar] [CrossRef]

- Meena, J.S.; Sze, S.M.; Chand, U.; Tseng, T.Y. Overview of Emerging Nonvolatile Memory Technologies. Nanoscale Res. Lett. 2014, 9, 526. [Google Scholar] [CrossRef]

- Xie, Y. Modeling, Architecture, and Applications for Emerging Memory Technologies. IEEE Des. Test Comput. 2011, 28, 44–51. [Google Scholar] [CrossRef]

- Wang, Z.; Wu, H.; Burr, G.W.; Hwang, C.S.; Wang, K.L.; Xia, Q.; Yang, J.J. Resistive Switching Materials for Information Processing. Nat. Rev. Mater. 2020, 5, 173–195. [Google Scholar] [CrossRef]

- Kim, S.; Jung, S.; Kim, M.H.; Cho, S.; Park, B.G. Resistive Switching Characteristics of Si3N4-Based Resistive-Switching Random-Access Memory Cell with Tunnel Barrier for High Density Integration and Low-Power Applications. Appl. Phys. Lett. 2015, 106, 212106. [Google Scholar] [CrossRef]

- Makarov, A.; Sverdlov, V.; Selberherr, S. Emerging Memory Technologies: Trends, Challenges, and Modeling Methods. Microelectron. Reliab. 2012, 52, 628–634. [Google Scholar] [CrossRef]

- Zhu, J.; Zhang, T.; Yang, Y.; Huang, R. A Comprehensive Review on Emerging Artificial Neuromorphic Devices. Appl. Phys. Rev. 2020, 7, 011312. [Google Scholar] [CrossRef]

- Kim, K.; Lee, S. Integration of Lead Zirconium Titanate Thin Films for High Density Ferroelectric Random Access Memory. J. Appl. Phys. 2006, 100, 051604. [Google Scholar] [CrossRef]

- Hong, X.L.; Loy, D.J.J.; Dananjaya, P.A.; Tan, F.; Ng, C.M.; Lew, W.S. Oxide-Based RRAM Materials for Neuromorphic Computing. J. Mater. Sci. 2018, 53, 8720–8746. [Google Scholar] [CrossRef]

- Zahoor, F.; Azni Zulkifli, T.Z.; Khanday, F.A. Resistive Random Access Memory (RRAM): An Overview of Materials, Switching Mechanism, Performance, Multilevel Cell (Mlc) Storage, Modeling, and Applications. Nanoscale Res. Lett. 2020, 15, 90. [Google Scholar] [CrossRef] [PubMed]

- Ohno, T.; Hasegawa, T.; Tsuruoka, T.; Terabe, K.; Gimzewski, J.K.; Aono, M. Short-Term Plasticity and Long-Term Potentiation Mimicked in Single Inorganic Synapses. Nat. Mater. 2011, 10, 591–595. [Google Scholar] [CrossRef] [PubMed]

- Mahata, C.; Lee, C.; An, Y.; Kim, M.H.; Bang, S.; Kim, C.S.; Ryu, J.H.; Kim, S.; Kim, H.; Park, B.G. Resistive Switching and Synaptic Behaviors of an HfO2/Al2O3 Stack on ITO for Neuromorphic Systems. J. Alloys Compd. 2020, 826, 154434. [Google Scholar] [CrossRef]

- Ryu, J.H.; Mahata, C.; Kim, S. Long-Term and Short-Term Plasticity of Ta2O5/HfO2 Memristor for Hardware Neuromorphic Application. J. Alloys Compd. 2021, 850, 156675. [Google Scholar] [CrossRef]

- Ryu, H.; Kim, S. Synaptic Characteristics from Homogeneous Resistive Switching in Pt/Al2O3 /TiN Stack. Nanomaterials 2020, 10, 2055. [Google Scholar] [CrossRef]

- Seo, Y.; Lee, S.; Baek, S.H.C.; Hwang, W.S.; Yu, H.Y.; Lee, S.H.; Cho, B.J. The Mechanism of Schottky Barrier Modulation of Tantalum Nitride/Ge Contacts. IEEE Electron. Device Lett. 2015, 36, 997–1000. [Google Scholar] [CrossRef]

- Oh, I.; Pyo, J.; Kim, S. Resistive Switching and Synaptic Characteristics in ZnO/TaON-Based RRAM for Neuromorphic System. Nanomaterials 2022, 12, 2185. [Google Scholar] [CrossRef] [PubMed]

- Mahata, C.; Kang, M.; Kim, S. Multi-Level Analog Resistive Switching Characteristics in Tri-Layer HfO2/Al2O3/HfO2 Based Memristor on Ito Electrode. Nanomaterials 2020, 10, 2069. [Google Scholar] [CrossRef] [PubMed]

- Kim, D.; Shin, J.; Kim, S. Implementation of Reservoir Computing Using Volatile WOx-Based Memristor. Appl. Surf. Sci. 2022, 599, 153876. [Google Scholar] [CrossRef]

- Mahata, C.; Kim, M.H.; Bang, S.; Kim, T.H.; Lee, D.K.; Choi, Y.J.; Kim, S.; Park, B.G. SiO2 Layer Effect on Atomic Layer Deposition Al2O3-Based Resistive Switching Memory. Appl. Phys. Lett. 2019, 114, 182102. [Google Scholar] [CrossRef]

- Liu, Z.Q.; Chim, W.K.; Chiam, S.Y.; Pan, J.S.; Ng, C.M. An Interface Dipole Predictive Model for High-k Dielectric/Semiconductor Heterostructures Using the Concept of the Dipole Neutrality Point. J. Mater. Chem. 2012, 22, 17887–17892. [Google Scholar] [CrossRef]

- Dao, V.A.; Trinh, T.T.; Kim, S.; van Ngoc, L.; Viet, T.D.; Thanh Giang, N.T.; Duong, D.L.; Thanh Nguyen, H.T.; Nam, N.D.; Yi, J.; et al. Carrier Transport Mechanisms of Reactively Direct Current Magnetron Sputtered Tungsten Oxide/n-Type Crystalline Silicon Heterojunction. J. Power Sources 2020, 472, 228460. [Google Scholar] [CrossRef]

- Ikuno, T.; Okamoto, H.; Sugiyama, Y.; Nakano, H.; Yamada, F.; Kamiya, I. Electron Transport Properties of Si Nanosheets: Transition from Direct Tunneling to Fowler-Nordheim Tunneling. Appl. Phys. Lett. 2011, 99, 023107. [Google Scholar] [CrossRef]

- Ryu, H.; Kim, S. Gradually Tunable Conductance in TiO2/Al2O3 Bilayer Resistors for Synaptic Device. Metals 2021, 11, 440. [Google Scholar] [CrossRef]

- Kim, S.; Park, B.G. Nonlinear and Multilevel Resistive Switching Memory in Ni/Si3N4/Al2O3/TiN Structures. Appl. Phys. Lett. 2016, 108, 212103. [Google Scholar] [CrossRef]

- Kopperberg, N.; Wiefels, S.; Liberda, S.; Waser, R.; Menzel, S. A Consistent Model for Short-Term Instability and Long-Term Retention in Filamentary Oxide-Based Memristive Devices. ACS Appl. Mater. Interfaces 2021, 13, 58066–58075. [Google Scholar] [CrossRef]

- Maiti, D.; Daza, Y.A.; Yung, M.M.; Kuhn, J.N.; Bhethanabotla, V.R. Oxygen Vacancy Formation Characteristics in the Bulk and across Different Surface Terminations of La(1-x)SrxFe(1-y)CoyO(3-δ) Perovskite Oxides for CO2 Conversion. J. Mater. Chem. A Mater 2016, 4, 5137–5148. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Pyo, J.; Ha, H.; Kim, S. Enhanced Short-Term Memory Plasticity of WOx-Based Memristors by Inserting AlOx Thin Layer. Materials 2022, 15, 9081. https://doi.org/10.3390/ma15249081

Pyo J, Ha H, Kim S. Enhanced Short-Term Memory Plasticity of WOx-Based Memristors by Inserting AlOx Thin Layer. Materials. 2022; 15(24):9081. https://doi.org/10.3390/ma15249081

Chicago/Turabian StylePyo, Juyeong, Hoesung Ha, and Sungjun Kim. 2022. "Enhanced Short-Term Memory Plasticity of WOx-Based Memristors by Inserting AlOx Thin Layer" Materials 15, no. 24: 9081. https://doi.org/10.3390/ma15249081

APA StylePyo, J., Ha, H., & Kim, S. (2022). Enhanced Short-Term Memory Plasticity of WOx-Based Memristors by Inserting AlOx Thin Layer. Materials, 15(24), 9081. https://doi.org/10.3390/ma15249081