Improved Ion/Ioff Current Ratio and Dynamic Resistance of a p-GaN High-Electron-Mobility Transistor Using an Al0.5GaN Etch-Stop Layer

Abstract

:1. Introduction

2. Device Structure

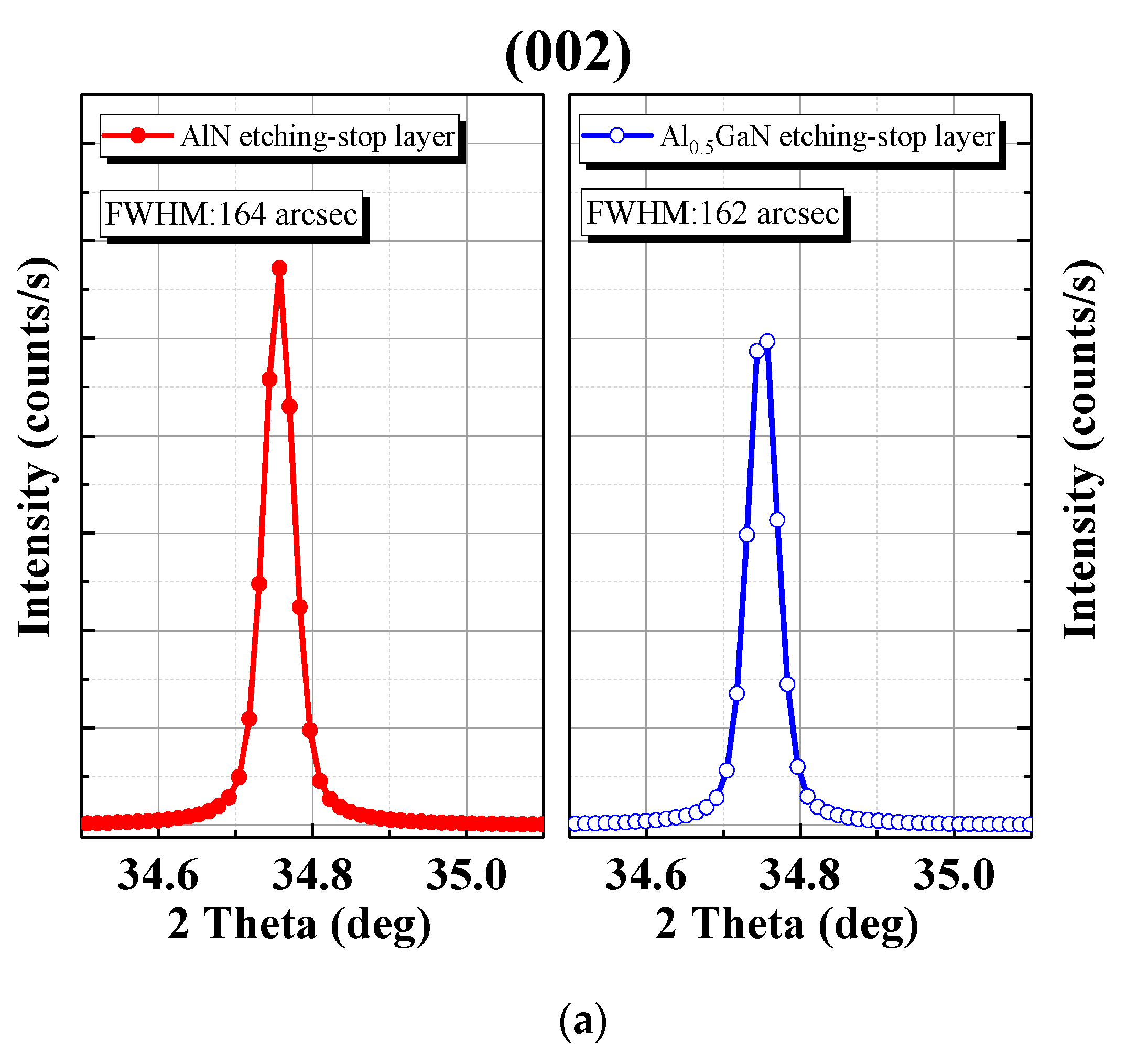

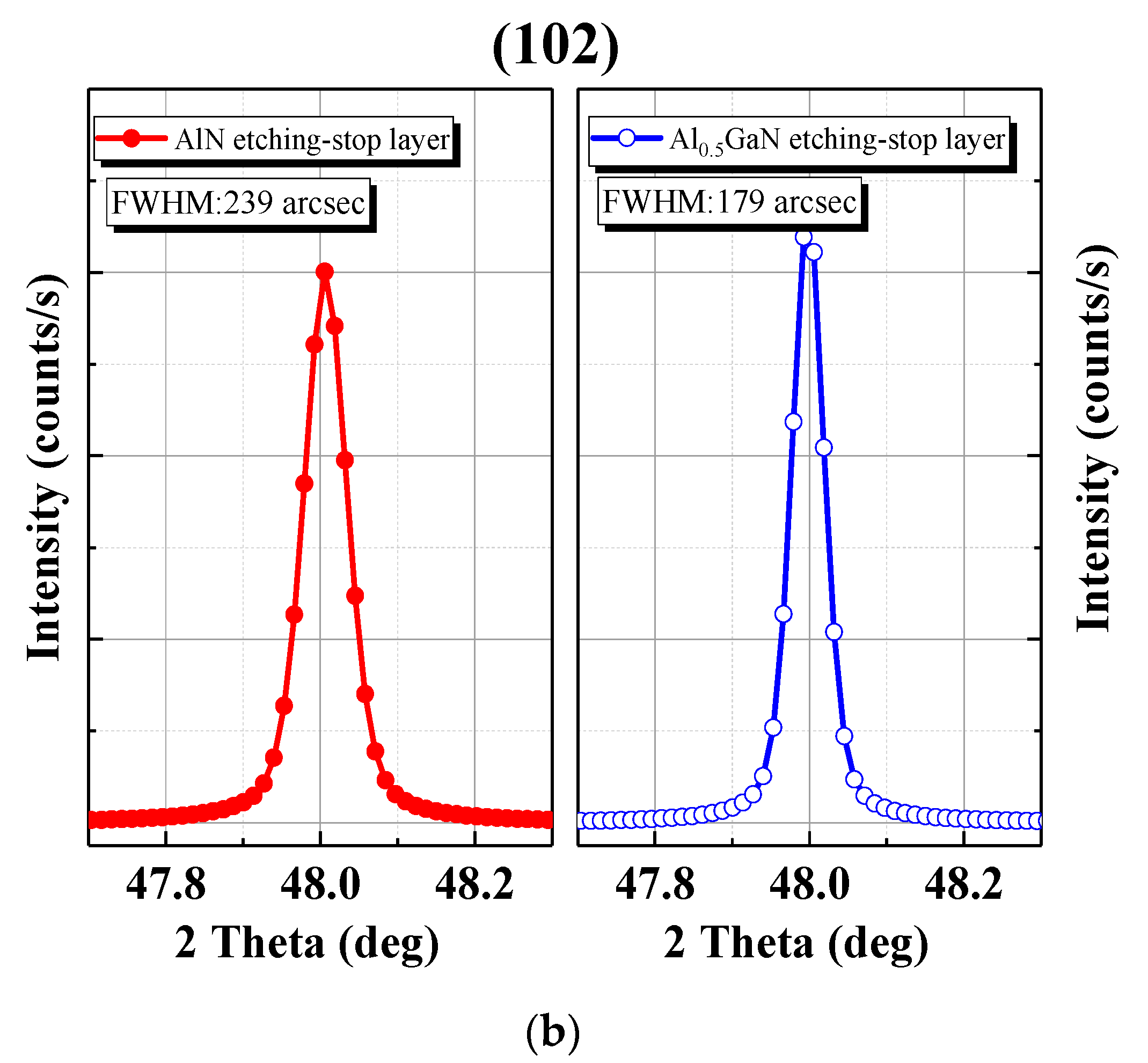

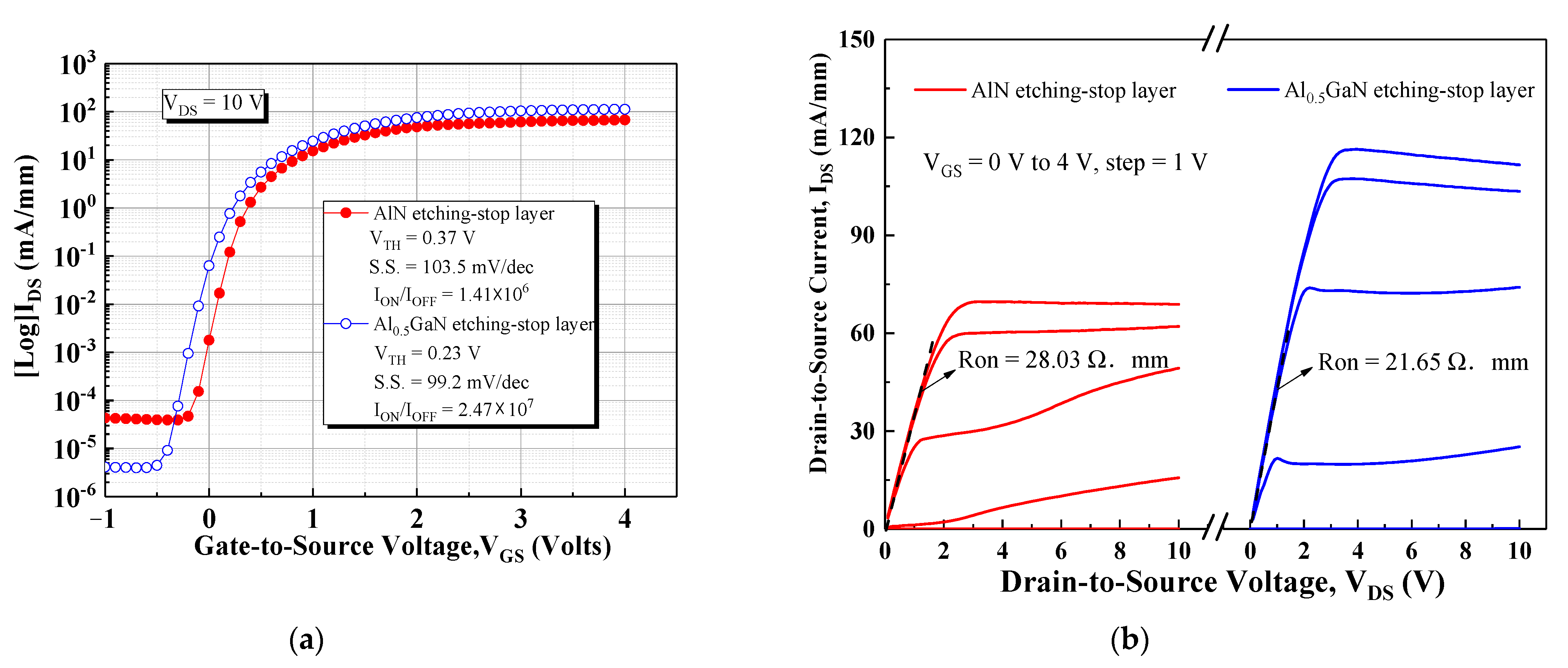

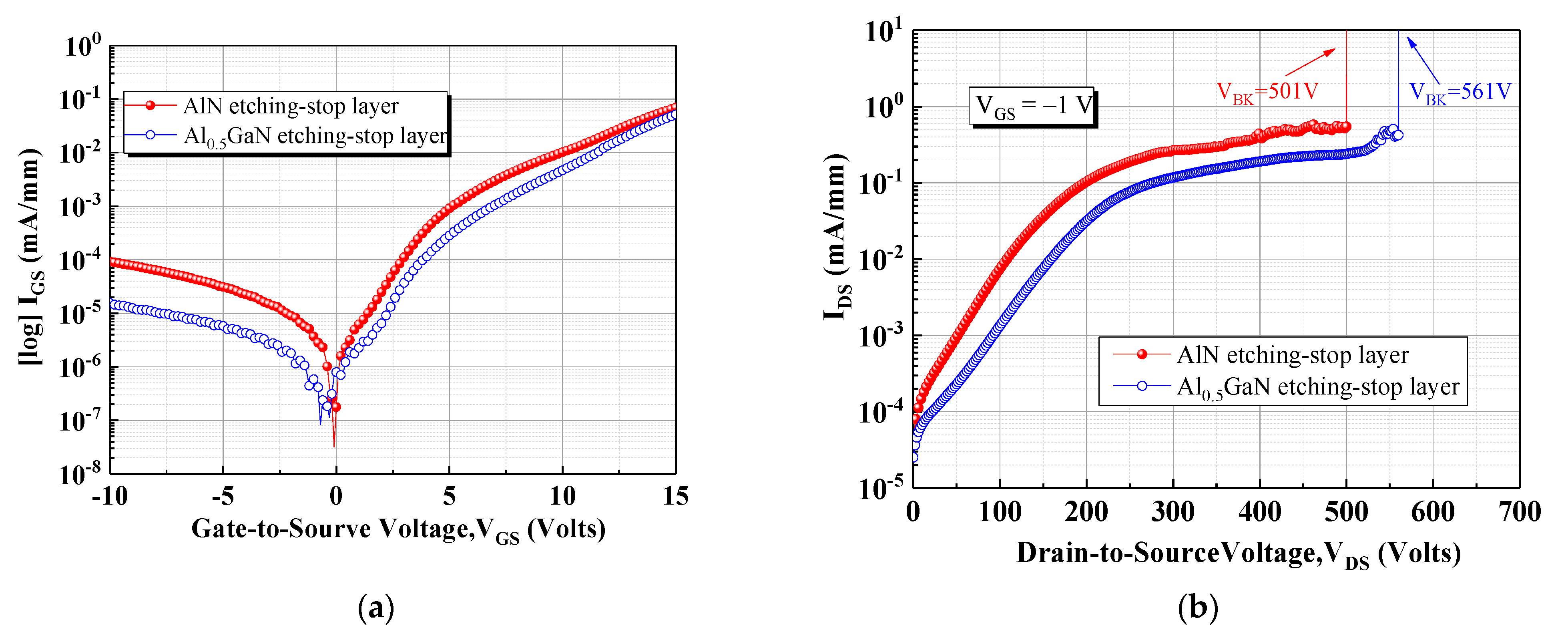

3. Experimental Results and Discussion

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Saito, W.; Takada, Y.; Kuraguchi, M.; Tsuda, K.; Omura, I.; Ogura, T.; Ohashi, H. High breakdown voltage AlGaN-GaN power-HEMT design and high current density switching behavior. IEEE Trans. Electron Devices 2003, 50, 2528–2531. [Google Scholar] [CrossRef]

- Nirmal, D.; Arivazhagan, L.; Fletcher, A.; Ajayan, J.; Prajoon, P. Current collapse modeling in AlGaN/GaN HEMT using small signal equivalent circuit for high power application. Superlattices Microstruct. 2018, 113, 810–820. [Google Scholar] [CrossRef]

- Matys, M.; Ishida, T.; Nam, K.P.; Sakurai, H.; Narita, T.; Uesugi, T.; Bockowski, M.; Suda, J.; Kachi, T. Mg-implanted bevel edge termination structure for GaN power device applications. Appl. Phys. Lett. 2021, 118, 093502. [Google Scholar] [CrossRef]

- Ohmaki, Y.; Tanimoto, M.; Akamatsu, S.; Mukai, T. Enhancement-Mode AlGaN/AlN/GaN High Electron Mobility Transistor with Low On-State Resistance and High Breakdown Voltage. Jpn. J. Appl. Phys. 2006, 45, L1168–L1170. [Google Scholar] [CrossRef]

- Oka, T.; Nozawa, T. AlGaN/GaN Recessed MIS-Gate HFET With High-Threshold-Voltage Normally-Off Operation for Power Electronics Applications. IEEE Electron Device Lett. 2008, 29, 668–670. [Google Scholar] [CrossRef]

- Kim, K.W.; Jung, S.D.; Kim, D.S.; Kang, H.S.; Im, K.S.; Oh, J.J.; Ha, J.B.; Shin, J.K.; Lee, J.H. Effects of TMAH treatment on device performance of normally off Al2O3/GaN MOSFET. IEEE Electron. Device Lett. 2011, 32, 1376–1378. [Google Scholar] [CrossRef]

- Chen, W.; Wong, K.Y.; Chen, K.J. Monolithic integration of lateral field-effect rectifier with normally-off HEMT for GaN-on-Si switch-mode power supply converters. In Proceedings of the 2008 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2008; pp. 1–4. [Google Scholar]

- Cai, Y.; Zhou, Y.; Chen, K.J.; Lau, K.M. High-performance enhancement-mode AlGaN/GaN HEMTs using fluoride-based plasma treatment. IEEE Electron Device Lett. 2005, 26, 435–437. [Google Scholar] [CrossRef]

- Tian, W.; Yan, W.Y.; Dai, J.N.; Li, S.L.; Tian, Y.; Hui, X.; Zhang, J.B.; Fang, Y.Y.; Wu, Z.H.; Chen, C.Q. Effect of growth temperature of an AlN intermediate layer on the growth mode of AlN grown by MOCVD. J. Phys. D Appl. Phys. 2013, 46, 65303. [Google Scholar] [CrossRef]

- Demir, I.; Li, H.; Robin, Y.; McClintock, R.; Elagoz, S.; Razeghi, M. Sandwich method to grow high quality AlN by MOCVD. J. Phys. D Appl. Phys. 2018, 51, 085104. [Google Scholar] [CrossRef]

- Buttari, D.; Chini, A.; Chakraborty, A.; McCarthy, L.; Xing, H.; Palacios, T.; Shen, L.; Keller, S.; Mishra, U.K. Selective dry etching of GaN over AlGaN in BCl3/SF6 mixtures. Int. J. High Speed Electron. Syst. 2004, 14, 756–761. [Google Scholar] [CrossRef]

- Yu, C.J.; Hsu, C.W.; Wu, M.C.; Hsu, W.C.; Chuang, C.Y.; Liu, J.Z. Improved DC and RF Performance of Novel MIS p-GaN-Gated HEMTs by Gate-All-Around Structure. IEEE Electron. Device Lett. 2020, 41, 673–676. [Google Scholar] [CrossRef]

- Lee, H.-P.; Perozek, J.; Rosario, L.D.; Bayram, C. Investigation of AlGaN/GaN high electron mobility transistor structures on 200-mm silicon (111) substrates employing different buffer layer configurations. Sci. Rep. 2016, 6, 37588. [Google Scholar] [CrossRef] [PubMed]

- Booker, I.; Khoshroo, L.R.; Woitok, J.F.; Kaganer, V.; Mauder, C.; Behmenburg, H.; Gruis, J.; Heuken, M.; Kalisch, H.; Jansen, R.H. Dislocation density assessment via X-ray GaN rocking curve scans. Phys. Status Solidi 2010, 7, 1787–1789. [Google Scholar] [CrossRef]

- Maity, N.; Thakur, R.; Maity, R.; Thapa, R.; Baishya, S. Analysis of Interface Charge Using Capacitance-Voltage Method for Ultra Thin HfO2 Gate Dielectric Based MOS Devices. Procedia Comput. Sci. 2015, 57, 757–760. [Google Scholar] [CrossRef] [Green Version]

- Shen, L.; Müller, S.; Cheng, X.; Zhang, D.; Zheng, L.; Xu, D.; Yu, Y.; Meissner, E.; Erlbacher, T. The GaN trench gate MOSFET with floating islands: High breakdown voltage and improved BFOM. Superlattices Microstruct. 2018, 114, 200–206. [Google Scholar] [CrossRef]

- Sun, W.; Joh, J.; Krishnan, S.; Pendharkar, S.; Jackson, C.M.; Ringel, S.A.; Arehart, A.R. Investigation of Trap-Induced Threshold Voltage Instability in GaN-on-Si MISHEMTs. IEEE Trans. Electron. Device 2019, 66, 890–895. [Google Scholar] [CrossRef]

- Liu, C.H.; Chiu, H.C.; Huang, C.R.; Chang, K.J.; Chen, C.T.; Hsueh, K.P. Low Gate Lag Normally-off p-GaN/AlGaN/GaN High Electron Mobility Transistor with Zirconium Gate Metal. Crystals 2020, 10, 25. [Google Scholar] [CrossRef] [Green Version]

- Tirado, J.M.; Sanchez-Rojas, J.L.; Izpura, J.I. Trapping Effects in the Transient Response of AlGaN/GaN HEMT Devices. IEEE Trans. Electron. Devices 2007, 54, 410–417. [Google Scholar] [CrossRef]

- Chiu, H.C.; Chang, Y.S.; Li, B.H.; Wang, H.C.; Kao, H.L.; Chien, F.T.; Hu, C.W.; Xuan, R. High Uniformity Normally-OFF p-GaN Gate HEMT Using Self-Terminated Digital Etching Technique. IEEE Trans. Electron. Devices 2018, 65, 4820–4825. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, H.-C.; Liu, C.-H.; Huang, C.-R.; Shih, M.-H.; Chiu, H.-C.; Kao, H.-L.; Liu, X. Improved Ion/Ioff Current Ratio and Dynamic Resistance of a p-GaN High-Electron-Mobility Transistor Using an Al0.5GaN Etch-Stop Layer. Materials 2022, 15, 3503. https://doi.org/10.3390/ma15103503

Wang H-C, Liu C-H, Huang C-R, Shih M-H, Chiu H-C, Kao H-L, Liu X. Improved Ion/Ioff Current Ratio and Dynamic Resistance of a p-GaN High-Electron-Mobility Transistor Using an Al0.5GaN Etch-Stop Layer. Materials. 2022; 15(10):3503. https://doi.org/10.3390/ma15103503

Chicago/Turabian StyleWang, Hsiang-Chun, Chia-Hao Liu, Chong-Rong Huang, Min-Hung Shih, Hsien-Chin Chiu, Hsuan-Ling Kao, and Xinke Liu. 2022. "Improved Ion/Ioff Current Ratio and Dynamic Resistance of a p-GaN High-Electron-Mobility Transistor Using an Al0.5GaN Etch-Stop Layer" Materials 15, no. 10: 3503. https://doi.org/10.3390/ma15103503

APA StyleWang, H.-C., Liu, C.-H., Huang, C.-R., Shih, M.-H., Chiu, H.-C., Kao, H.-L., & Liu, X. (2022). Improved Ion/Ioff Current Ratio and Dynamic Resistance of a p-GaN High-Electron-Mobility Transistor Using an Al0.5GaN Etch-Stop Layer. Materials, 15(10), 3503. https://doi.org/10.3390/ma15103503