In-Memory-Computing Realization with a Photodiode/Memristor Based Vision Sensor

Abstract

:1. Introduction

2. Silicon Nitride Memristor Devices as Analog Switches

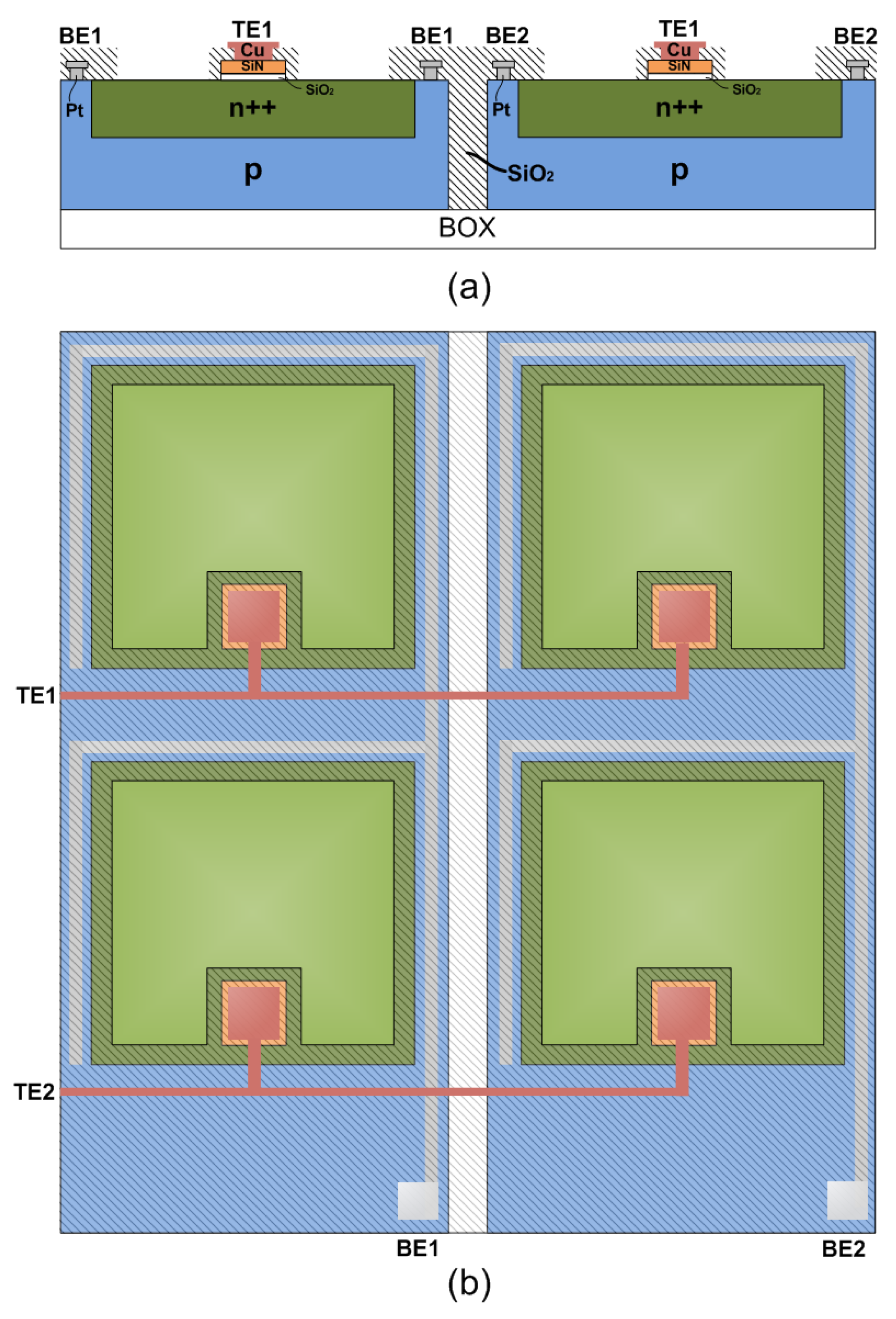

2.1. Device Fabrication

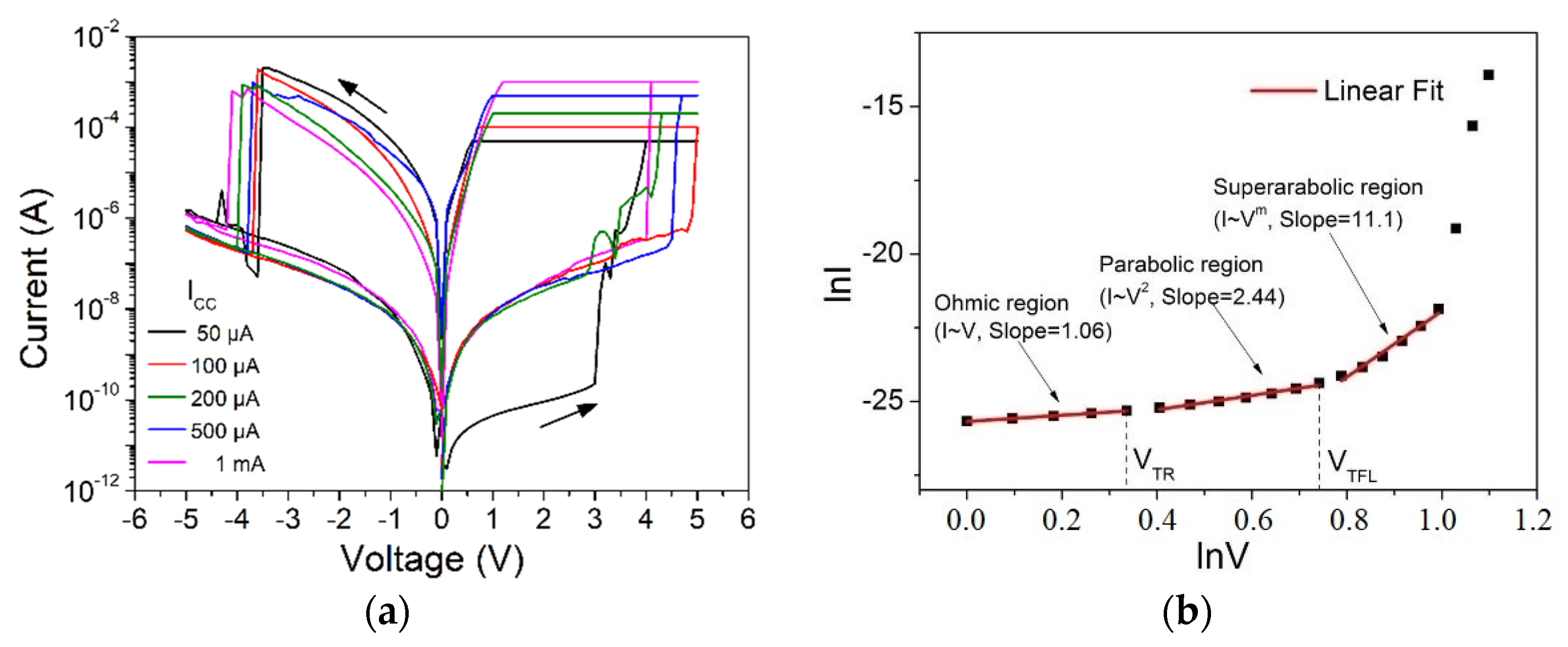

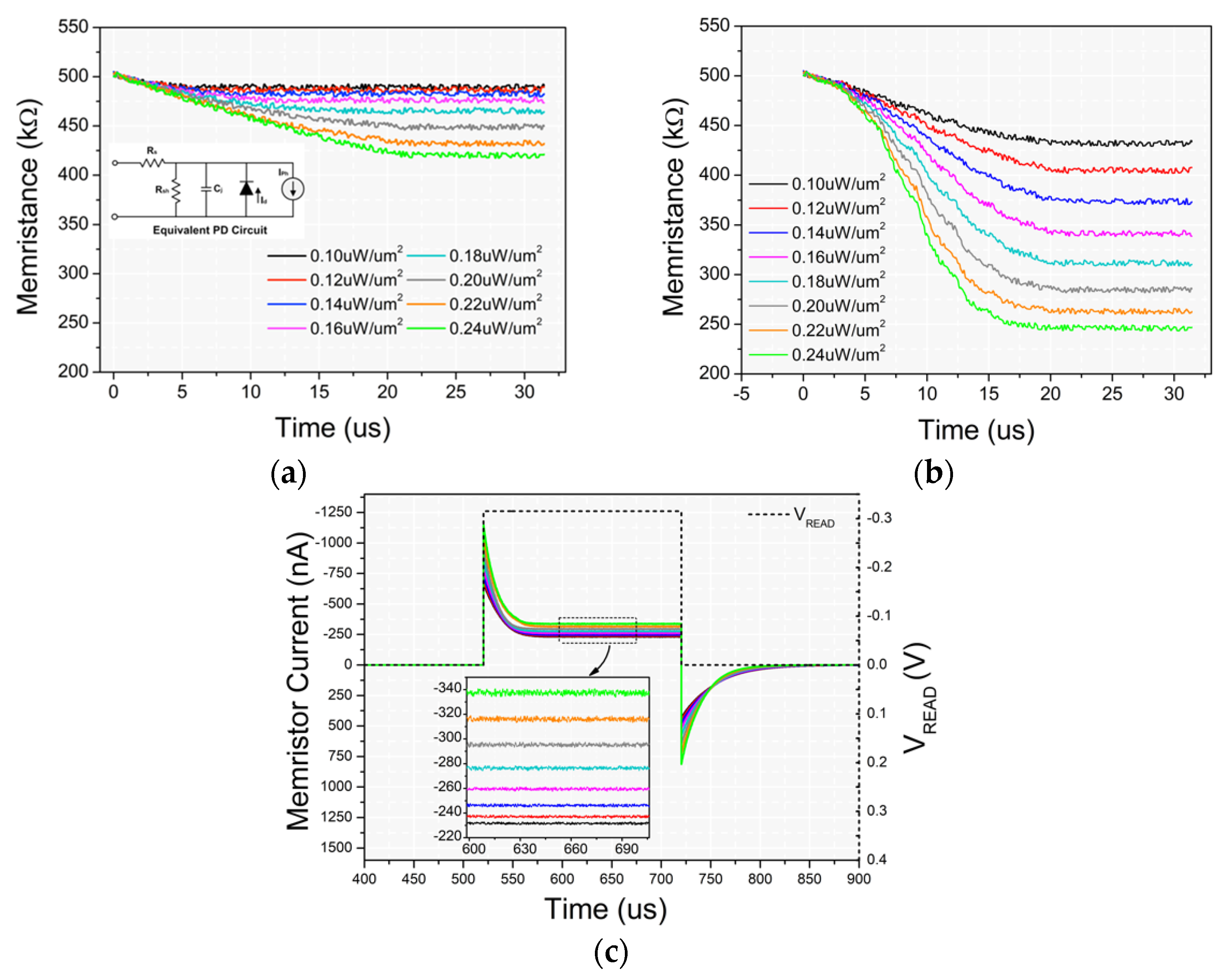

2.2. Analog Resistive Switching Characteristics

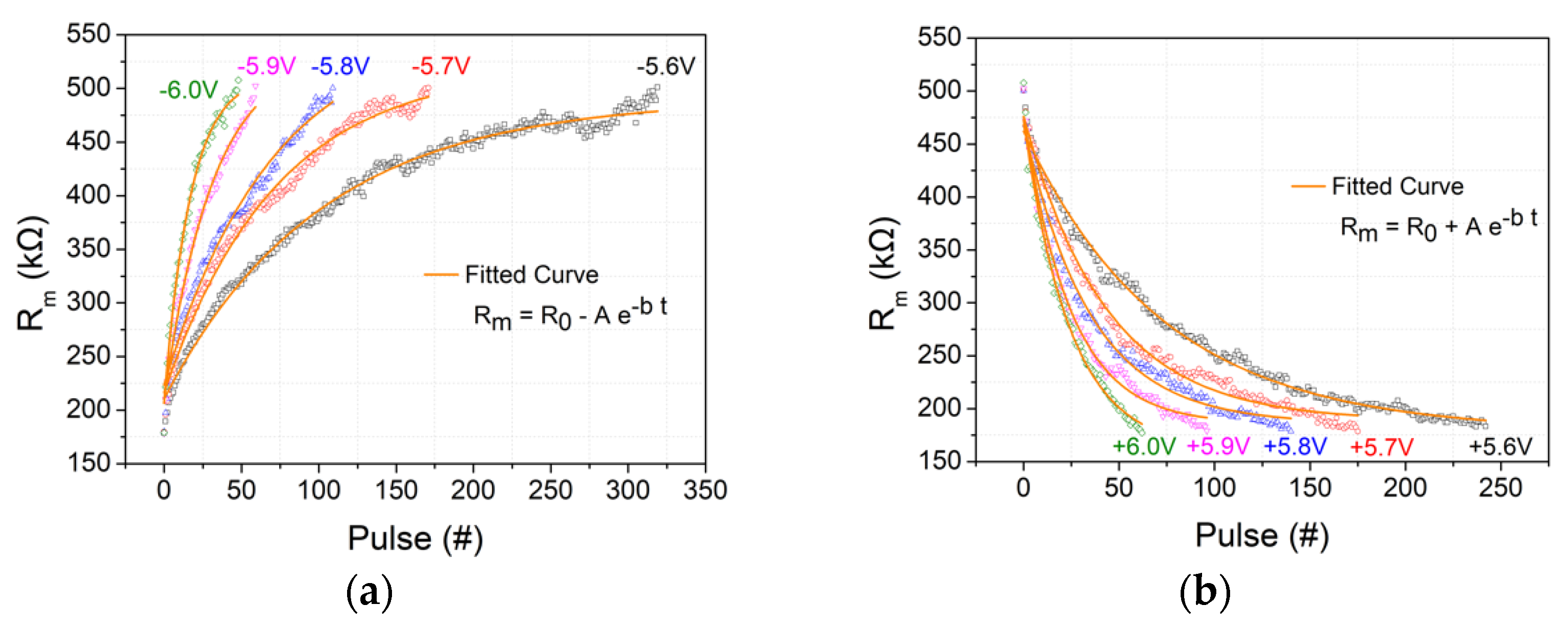

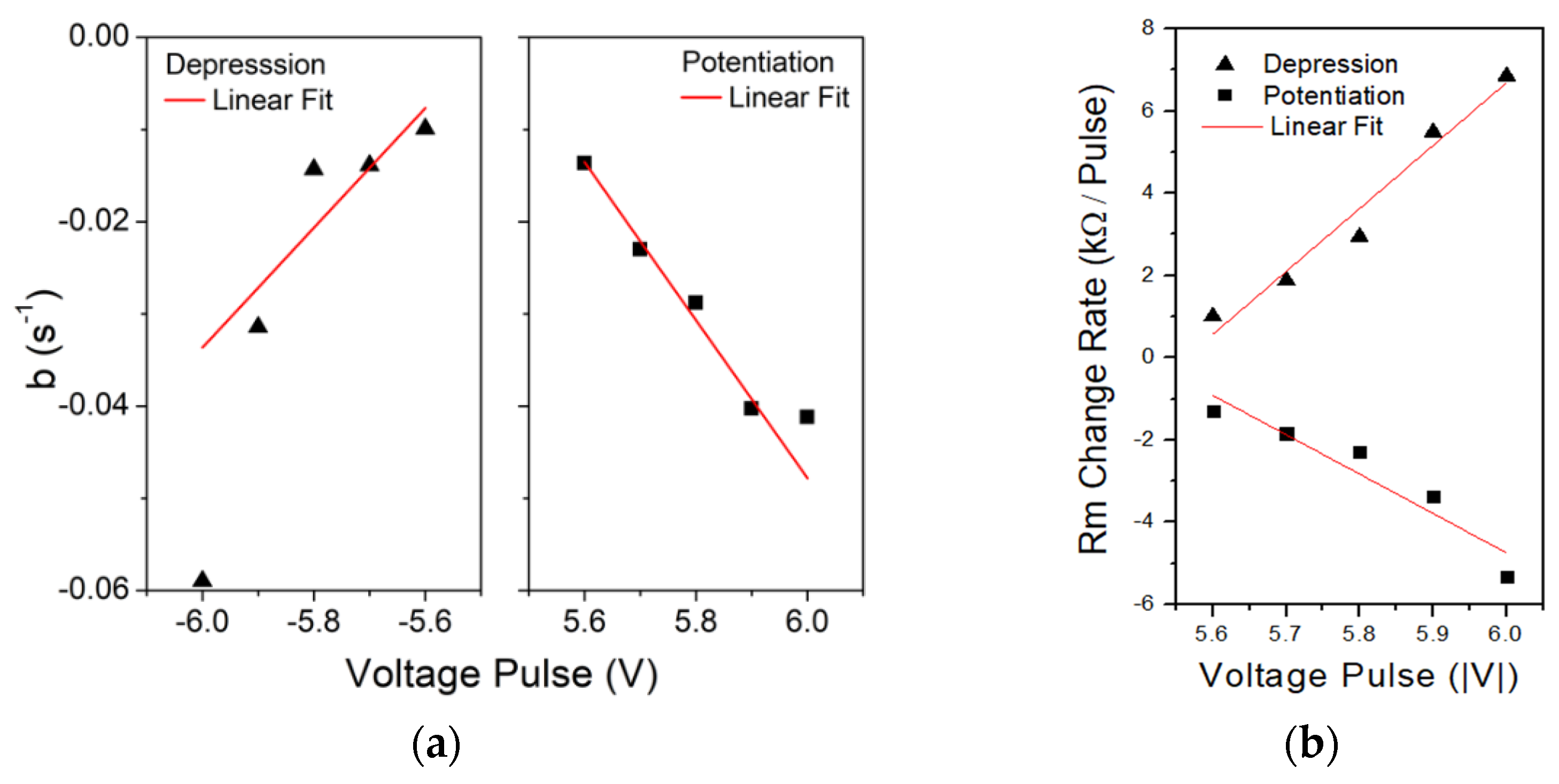

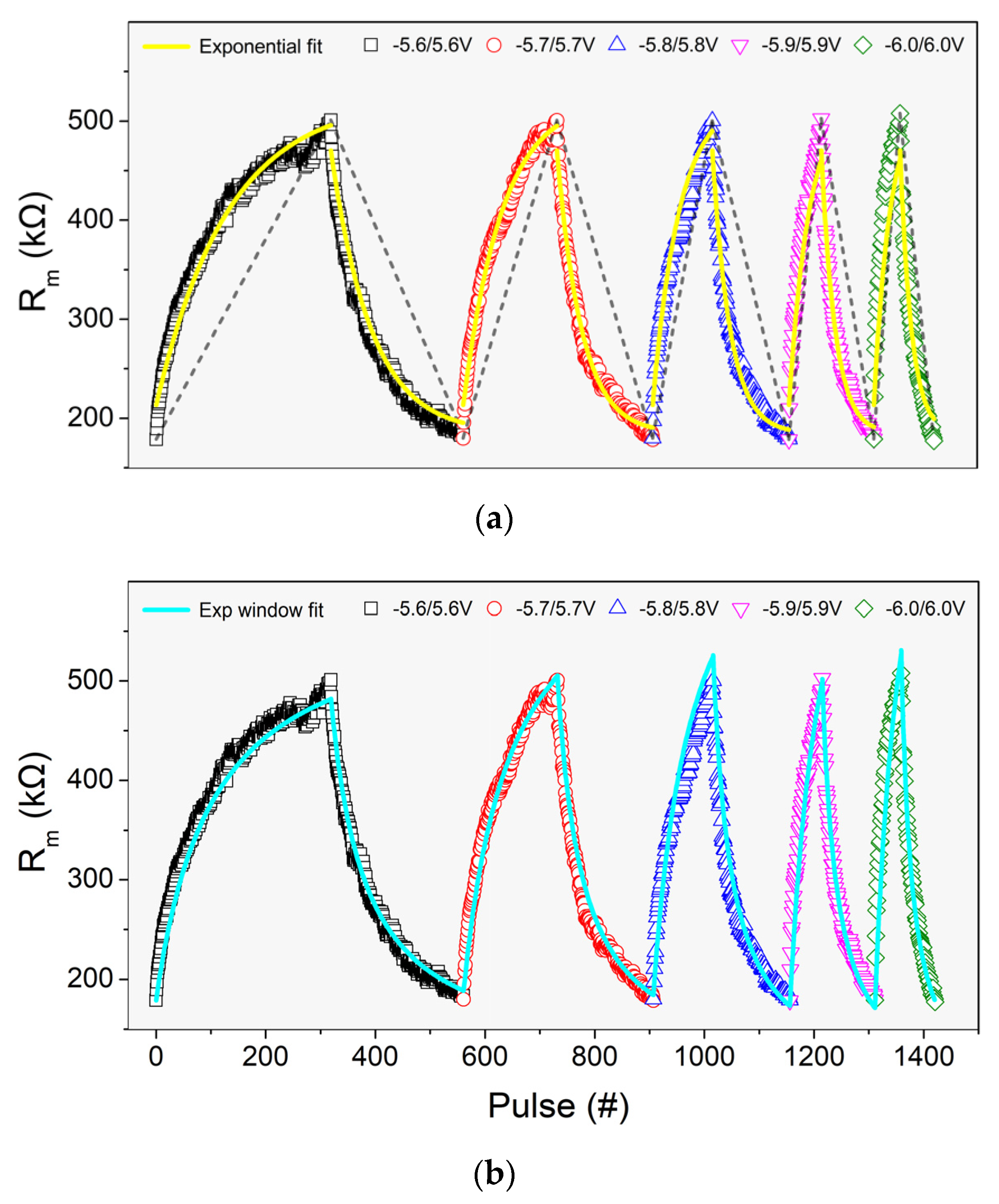

2.3. Analog Resistive Switching Behavioral Modeling

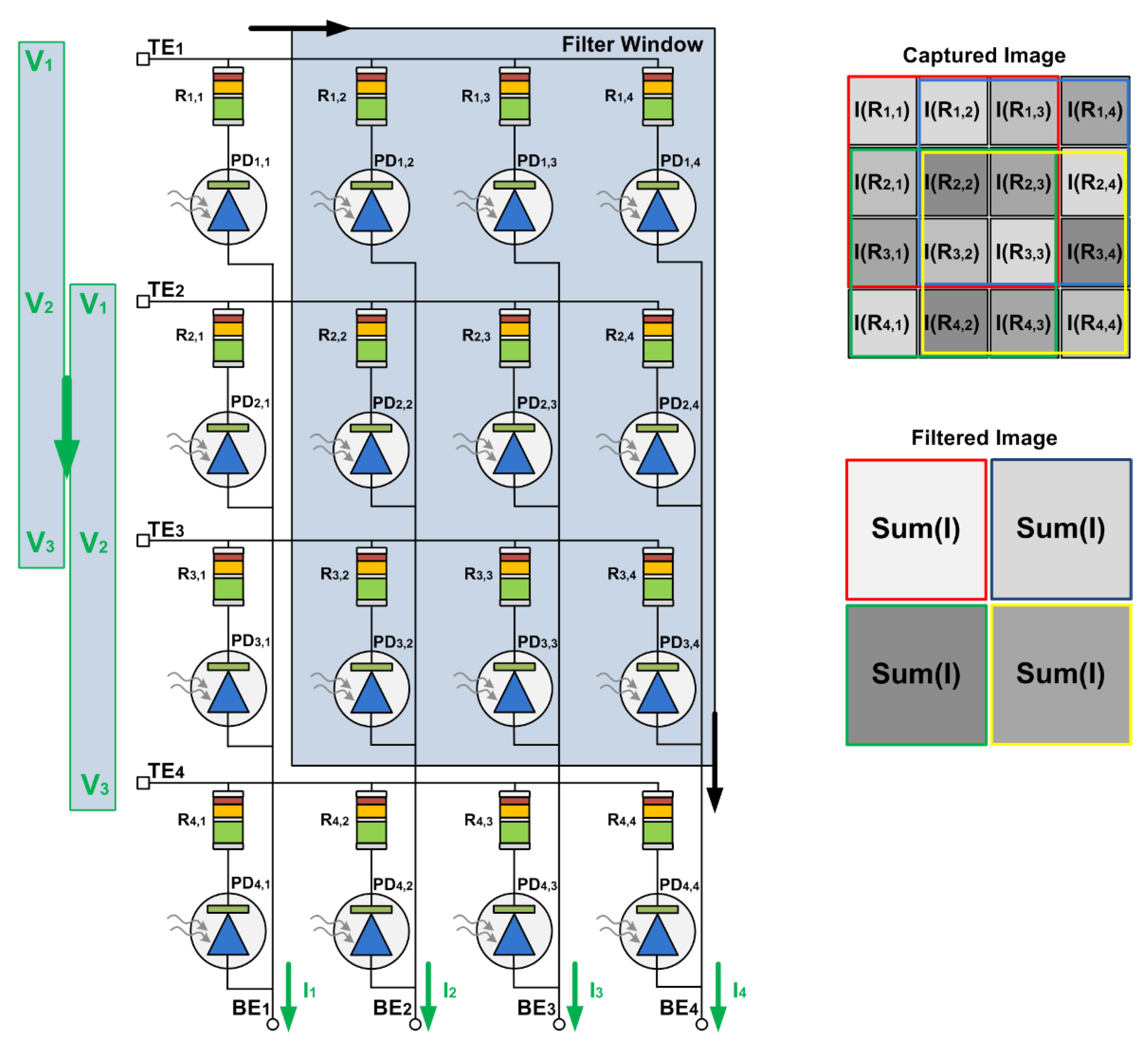

3. One Photodiode One Resistor (1D1M) Vision Sensor

3.1. Architectural Overview

3.2. Integration Perspectives

3.3. SPICE Simulated in-Memory-Computing Operations

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Satyanarayanan, M. The emergence of edge computing. Computer 2017, 50, 30–39. [Google Scholar] [CrossRef]

- Premsankar, G.; di Francesco, M.; Taleb, T. Edge computing for the internet of things: A case study. IEEE Internet Things J. 2018, 5, 1275–1284. [Google Scholar] [CrossRef] [Green Version]

- Gusev, M.; Dustdar, S. Going back to the roots—the evolution of edge computing, an iot perspective. IEEE Internet Comput. 2018, 22, 5–15. [Google Scholar] [CrossRef]

- Sheltami, T.R.; Shahra, E.Q.; Shakshuki, E.M. Fog computing: Data streaming services for mobile end-users. Procedia Comput. Sci. 2018, 134, 289–296. [Google Scholar] [CrossRef]

- Oyekanlu, E.; Scoles, K.; Oladele, P.O. Advanced Signal Processing for Communication Networks and Industrial IoT Machines Using Low-Cost Fixed-Point Digital Signal Processor. In 2018 10th International Conference on Advanced Infocomm Technology (ICAIT 2018); International Conference on Advanced Infocomm Technology, Ed.; IEEE: Piscataway, NJ, USA, 2018; pp. 93–101. [Google Scholar] [CrossRef]

- Mennel, L.; Symonowicz, J.; Wachter, S.; Polyushkin, D.K.; Molina-Mendoza, A.J.; Mueller, T. Ultrafast machine vision with 2d material neural network image sensors. Nature 2020, 579, 62–66. [Google Scholar] [CrossRef] [PubMed]

- Yakopcic, C.; Taha, T.M.; Subramanyam, G.; Rogers, S. Memristor-based unit cell for a detector readout circuit. In Unconventional Imaging, Wavefront Sensing, and Adaptive Coded Aperture Imaging and Non-Imaging Sensor Systems; Rogers, S., Casasent, D.P., Dolne, J.J., Karr, T.J., Gamiz, V.L., Eds.; International Society for Optics and Photonics: Bellingham, WA, USA, 2011; Volume 81651, p. 81651F. [Google Scholar]

- Olumodeji, O.A.; Bramanti, A.P.; Gottardi, M. A Memristive Pixel Architecture for Real-Time Tracking. IEEE Sens. J. 2016, 16, 7911–7918. [Google Scholar] [CrossRef]

- Eshraghian, K.; Cho, K.; Zheng, C.; Nam, M.; Iu, H.H.-C.; Lei, W.; Eshraghian, K. Neuromorphic vision hybrid RRAM-CMOS architecture. IEEE Trans. Very Large-Scale Integr. (VLSI) Syst. 2018, 26, 2816–2829. [Google Scholar] [CrossRef]

- Kumar, A.; Sarkar, M.; Suri, M. Oxram resistive switching for dr improvement. In Proceedings of the 2018 IEEE International Symposium on Circuits and Systems (ISCAS), Florence, Italy, 27–30 May 2018; pp. 1–5. [Google Scholar]

- Karakolis, P.; Normand, P.; Dimitrakis, P.; Ntinas, V.; Fyrigos, I.-A.; Karafyllidis, I.; Sirakoulis, G.C. Future and emergent materials and devices for resistive switching. In Proceedings of the 2018 IEEE 13th Nanotechnology Materials and Devices Conference (NMDC), Portland, OR, USA, 14–17 October 2018; pp. 1–5. [Google Scholar]

- Vasileiadis, N.; Karakolis, P.; Mandylas, P.; Ioannou-Sougleridis, V.; Normand, P.; Perego, M.; Komninou, P.; Ntinas, V.; Fyrigos, I.-A.; Karafyllidis, I.; et al. Understanding the Role of Defects in Silicon Nitride-Based Resistive Switching Memories Through Oxygen Doping. IEEE Trans. Nanotechnol. 2021, 20, 356–364. [Google Scholar] [CrossRef]

- Belyi, V.I.; Rastorguyev, A.A. A new view on the nature of electron levels in amorphous silicon nitride. Chem. Sust. Develop. 2000, 8, 13–20. [Google Scholar]

- Kaloyeros, A.E.; Jove, F.A.; Goff, J.; Arkles, B. Silicon nitride and silicon nitride-rich thin film technologies: Trends in deposition techniques and related applications. ECS J. Solid State Sci. Technol. 2017, 6, 691. [Google Scholar] [CrossRef]

- Sonoda, K.; Tsukuda, E.; Tanizawa, M.; Yamaguchi, Y. Electron trap level of hydrogen incorporated nitrogen vacancies in silicon nitride. J. Appl. Phys. 2015, 117, 104501. [Google Scholar] [CrossRef]

- Gismatulin, A.A.; Orlov, O.M.; Gritsenko, V.A.; Kruchinin, V.N.; Mizginov, D.S.; Krasnikov, G.Y. Charge transport mechanism in the metal–nitride–oxide–silicon forming-free memristor structure. Appl. Phys. Lett. 2020, 116, 203502. [Google Scholar]

- Tikhov, S.V.; Mikhaylov, A.N.; Belov, A.I.; Korolev, D.S.; Antonov, I.N.; Karzanov, V.V.; Gorshkov, O.N.; Tetelbaum, D.I.; Karakolis, P.; Dimitrakis, P. Role of highly doped Si substrate in bipolar resistive switching of silicon nitride MIS-capacitors. Microelectron. Eng. 2018, 187–188, 134–138. [Google Scholar] [CrossRef]

- Kim, S.; Chang, Y.F.; Park, B.G. Understanding rectifying and nonlinear bipolar resistive switching characteristics in Ni/SiNx/p-Si memory devices. RSC Adv. 2017, 7, 17882. [Google Scholar] [CrossRef] [Green Version]

- Vasileiadis, N.; Loukas, P.; Karakolis, P.; Ioannou-Sougleridis, V.; Normand, P.; Ntinas, V.; Fyrigos, I.-A.; Karafyllidis, I.; Sirakoulis, G.C.; Dimitrakis, P. Multi-level resistance switching and random telegraph noise analysis of nitride based memristors. arXiv 2021, arXiv:2103.09931. preprint. [Google Scholar]

- Vasileiadis, N.; Dimitrakis, P.; Ntinas, V.; Sirakoulis, G.C. True random number generator based on multi-state silicon nitride memristor entropy sources combination. In Proceedings of the 2021 International Conference on Electronics, Information, and Communication, Jeju Island, Korea, 31 January2021–3 February 2021. art. no. 9369817. [Google Scholar]

- Kim, S.; Jung, S.; Kim, M.-H.; Chen, Y.-C.; Chang, Y.-F.; Ryoo, K.-C.; Cho, S.; Lee, J.-H.; Park, B.-G. Scaling effect on silicon nitride memristor with highly doped si substrate. Small 2018, 14, 1704062. [Google Scholar] [CrossRef] [PubMed]

- Kim, S.; Kim, H.; Hwang, S.; Kim, M.-H.; Chang, Y.-F.; Park, B.-G. Analog synaptic behavior of a silicon nitride memristor. ACS Appl. Mater. Interfaces 2017, 9, 40420–40427. [Google Scholar] [CrossRef]

- Edwards, A.H.; Barnaby, H.J.; Campbell, K.A.; Kozicki, M.N.; Liu, W.; Marinella, M.J. Reconfigurable memristive device technologies. Proc. IEEE 2015, 103, 1004–1033. [Google Scholar] [CrossRef]

- Wang, Z.; Wu, H.; Burr, G.W.; Hwang, C.S.; Wang, K.L.; Xia, Q.; Yang, J.J. Resistive switching materials for information processing. Nat. Rev. Mater. 2020, 5, 173–195. [Google Scholar] [CrossRef]

- Zidan, M.A.; Strachan, J.P.; Lu, W.D. The future of electronics based on memristive systems. Nat. Electron. 2018, 1, 22–29. [Google Scholar] [CrossRef]

- Islam, R.; Li, H.; Chen, P.-Y.; Wan, W.; Chen, H.-Y.; Gao, B.; Wu, H.; Yu, S.; Saraswat, K.; Wong, H.-S.P. Device and materials requirements for neuromorphic computing. J. Phys. D: Appl. Phys. 2019, 52, 113001. [Google Scholar] [CrossRef]

- Karafyllidis, I.G.; Sirakoulis, G.C.; Dimitrakis, P. Memristive Quantum Computing Simulator. IEEE Trans. Nanotechnol. 2019, 18, 1015–1022. [Google Scholar] [CrossRef]

- Kim, S.; Cho, S.; Park, B.-G. Fully Si compatible SiN resistive switching memory with large self-rectification ratio. AIP Adv. 2016, 6, 015021. [Google Scholar] [CrossRef]

- Kim, S.; Chang, Y.-F.; Kim, M.-H.; Kim, T.-H.; Kim, Y.; Park, B.-G. Self-Compliant Bipolar Resistive Switching in SiN-Based Resistive Switching Memory. Materials 2017, 10, 459. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Jiang, X.; Ma, Z.; Xu, J.; Chen, K.; Xu, L.; Li, W.; Huang, X.; Feng, D. a-SiNx:H-based ultra-low power resistive random access memory with tunable Si dangling bond conduction paths. Sci. Rep. 2015, 5, 15762. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Kim, G.H.; Ju, H.; Yang, M.K.; Lee, D.K.; Choi, J.W.; Jang, J.H.; Lee, S.G.; Cha, I.S.; Park, B.K.; Han, J.H.; et al. Four-bits-per-cell operation in an HfO2-based resistive switching device. Small 2017, 13, 1701781. [Google Scholar] [CrossRef] [PubMed]

- Kim, S.; Park, B.-G. Power-and low-resistance-state-dependent, bipolar reset-switching transitions in sin-based resistive random-access memory. Nanoscale Res. Lett. 2016, 11, 1–8. [Google Scholar] [CrossRef] [Green Version]

- Yonai, T.; Kinoshita, H.; Yasuhara, R.; Takeuchi, K. 98% endurance error reduction by hard verify for 40 nm TaOx based ReRAM. In 2020 International Symposium on VLSI Technology, Systems and Applications (VLSI-TSA); IEEE Staff, Ed.; IEEE: Piscataway, NJ, USA, 2020; pp. 35–36. [Google Scholar]

- Messaris, I.; Serb, A.; Stathopoulos, S.; Khiat, A.; Nikolaidis, S.; Prodromakis, T. A data-driven Verilog-a ReRAM model. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2018, 37, 3151–3162. [Google Scholar] [CrossRef]

- Fatih, G.Ü.L. A Generic Circuit Model for Memristor Based One Diode-One Resistor Devices. Balk. J. Electr. Comput. Eng. 2019, 7, 15–19. [Google Scholar]

- Wang, S.; Wang, C.-Y.; Wang, P.; Wang, C.; Li, Z.-A.; Pan, C.; Dai, Y.; Gao, A.; Liu, C.; Liu, J.; et al. Networking retinomorphic sensor with memristive crossbar for brain-inspired visual perception. Natl. Sci. Rev. 2021, 8, nwaa172. [Google Scholar] [CrossRef]

- Jang, H.; Liu, C.; Hinton, H.; Lee, M.-H.; Kim, H.; Seol, M.; Shin, H.-J.; Park, S.; Ham, D. An atomically thin optoelectronic machine vision processor. Adv. Mater. 2020, 32, 2002431. [Google Scholar] [CrossRef]

- Chen, S.; Lou, Z.; Chen, D.; Shen, G. An Artificial Flexible Visual Memory System Based on an UV-Motivated Memristor. Adv. Mater. 2018, 30, 1705400. [Google Scholar] [CrossRef]

- Vasileiadis, N.; Ntinas, V.; Fyrigos, L.-A.; Karamani, R.-E.; Ioannou-Sougleridis, V.; Normand, P.; Karafyllidis, P.; Sirakoulis, G.C.; Dimitrakis, P. A new 1P1R Image Sensor with In-Memory Computing Properties based on Silicon Nitride Devices. In 2021 IEEE International Symposium on Circuits and Systems (ISCAS); IEEE Staff, Ed.; IEEE: Piscataway, NJ, USA, 2021. [Google Scholar]

| Potentiation–Positive Pulses | Depression–Negative Pulses | ||

|---|---|---|---|

| Technology [Reference] | NVH RRAM-CMOS Architecture [9] | Networking Retinomorphic Sensor [36] | UMV 2D Material Image Sensor [6] | ATO Machine Vision Processor [37] | AFV Memory System [38] | 1P1R Image Sensor [39] | This Work |

|---|---|---|---|---|---|---|---|

| Biological System emulation | Retinal bioarchitecture | Human Retina | No | Human vision system | Human visual memory | No | No |

| CMOS process compatibility | Only Pixel Array | Not compatible | Not compatible | Not compatible | Not compatible | All structure | All structure |

| Memristive structure | Hexagonal circuitry | 1T1R crossbar | 1PD-1FGT crossbar | MoS2 photo-FET crossbar | 1SMW-1R array | 1T1R crossbar | 1D1R crossbar |

| Memristive element | Pt-Hf-Ti VTEAM Model | Pt/Ta/HfO2/Ta | hBN-Au-Al2O3 (Floating gate memory) | FET PCC (1) | Ni-Al2O3-Au | SiNx Experimental data model | SiNx Experimental data model |

| Analog Resistive states | 2 levels On/Off | [0 mA, 4 mA]: [0 V, 0.4 V] discrete levels not mentioned | discrete levels not mentioned | 4 discrete levels | 2 levels On/Off | 16 discrete levels | 8 discrete levels |

| Photosensitive element | PN photodiode | WSe2/h-BN/Al2O3 phototransistor | WSe2 photodiode | MoS2 photo-FET | In2O3 SMW (4) | NPN-BJT phototransistor | PN photodiode |

| Development stage | IC Mask Layout design and sims | Fabricated | Fabricated | Fabricated | Fabricated | Simulation | Simulation |

| Estimated power consumption | 7.8 μW (2) | N/A | N/A | 1.65 μW (3) | N/A | N/A | N/A |

| Estimated IC pixel area size | N/A | N/A | 17 × 17 μm2 | 300 × 300 μm2 | 0.5 × 0.5 cm2 | 10 × 10 μm2 | 10 × 10 μm2 |

| Sensor size investigated | 128 × 128 PDs 16 × 16 RRAMs arrays | N/A | 27× 3 × 3 Pixel (PD + FGT) array | 32 × 32 photo-FET array | 10 × 10 (SMW + RRAM) array | 32 × 32 (PD + RRAM) array | 28 × 28 (PD + RRAM) array |

| In-memory computing application Demo | Retinal Line spread function approximation | Edge enhancement, stylization and recognition | ANN classifier | Edge Detection, Embossing, Blur and Visual recognition | N/A | Mean Filtering And Edge Detection | Mean Filtering |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Vasileiadis, N.; Ntinas, V.; Sirakoulis, G.C.; Dimitrakis, P. In-Memory-Computing Realization with a Photodiode/Memristor Based Vision Sensor. Materials 2021, 14, 5223. https://doi.org/10.3390/ma14185223

Vasileiadis N, Ntinas V, Sirakoulis GC, Dimitrakis P. In-Memory-Computing Realization with a Photodiode/Memristor Based Vision Sensor. Materials. 2021; 14(18):5223. https://doi.org/10.3390/ma14185223

Chicago/Turabian StyleVasileiadis, Nikolaos, Vasileios Ntinas, Georgios Ch. Sirakoulis, and Panagiotis Dimitrakis. 2021. "In-Memory-Computing Realization with a Photodiode/Memristor Based Vision Sensor" Materials 14, no. 18: 5223. https://doi.org/10.3390/ma14185223

APA StyleVasileiadis, N., Ntinas, V., Sirakoulis, G. C., & Dimitrakis, P. (2021). In-Memory-Computing Realization with a Photodiode/Memristor Based Vision Sensor. Materials, 14(18), 5223. https://doi.org/10.3390/ma14185223