Standard Deviation Quantitative Characterization and Process Optimization of the Pyramidal Texture of Monocrystalline Silicon Cells

Abstract

1. Introduction

2. Texture Growth and Characterization

2.1. Texture Growth Process on the Surface of the Wafers

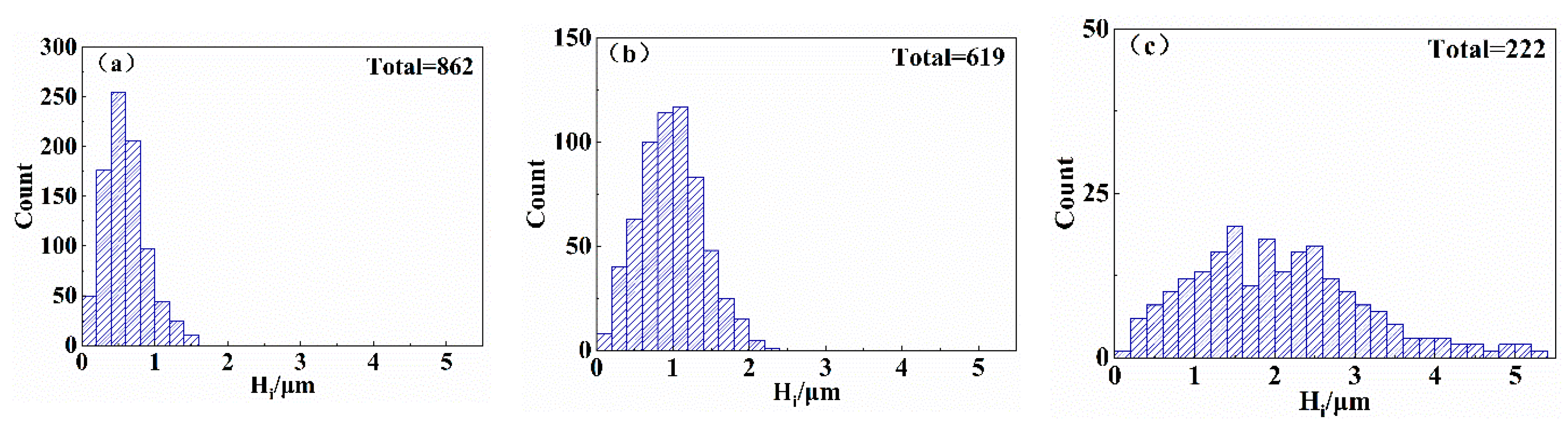

2.2. Quantitative Characterization of Pyramidal Texture

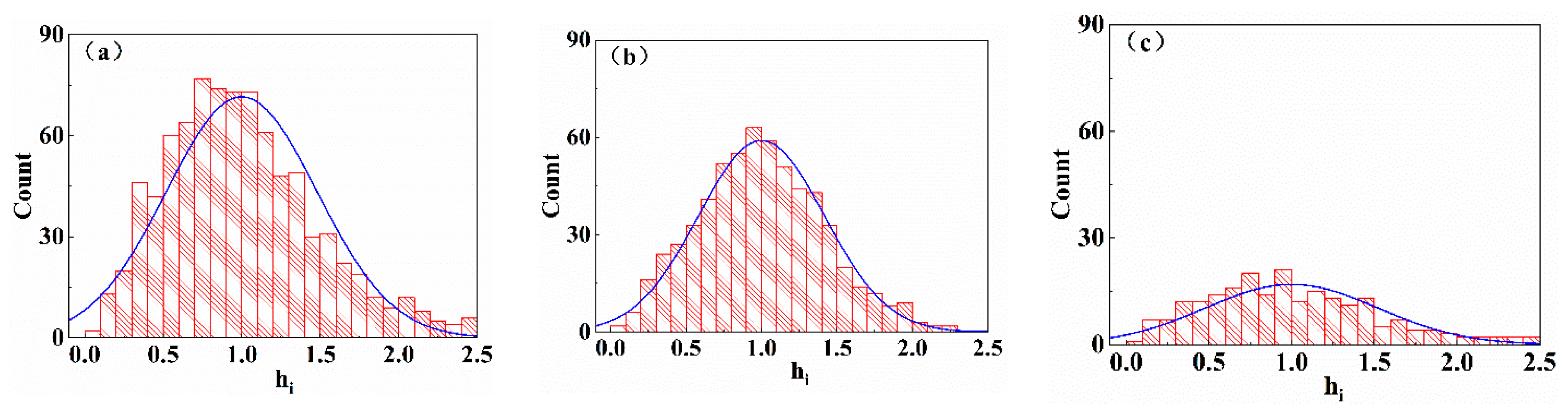

2.3. Calculation of Relative Standard Deviation

3. Materials and Methods

4. Results and Discussion

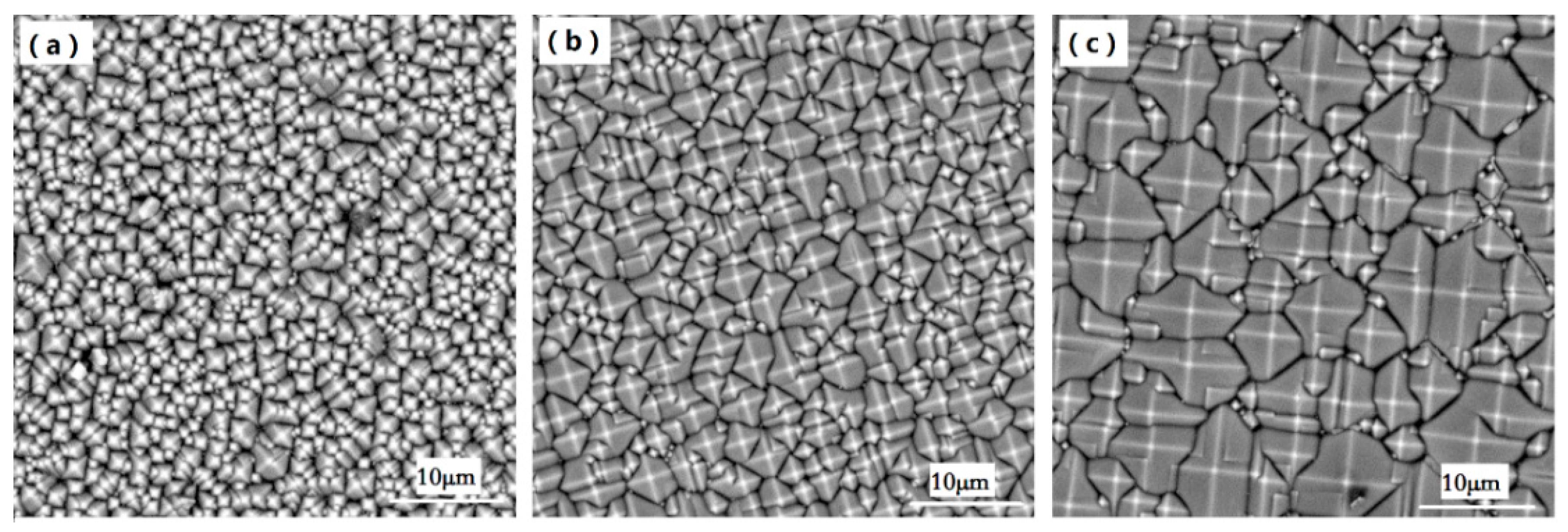

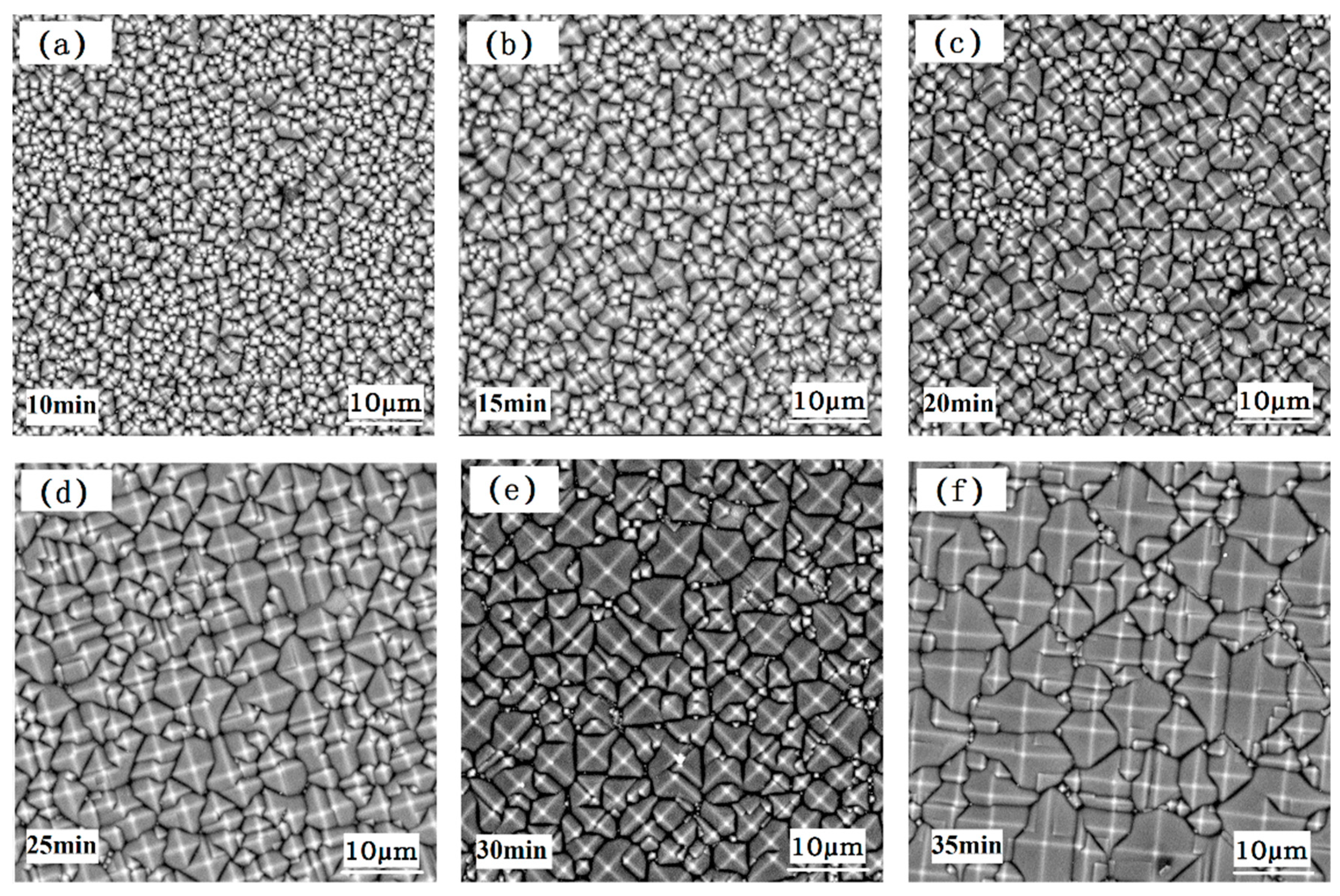

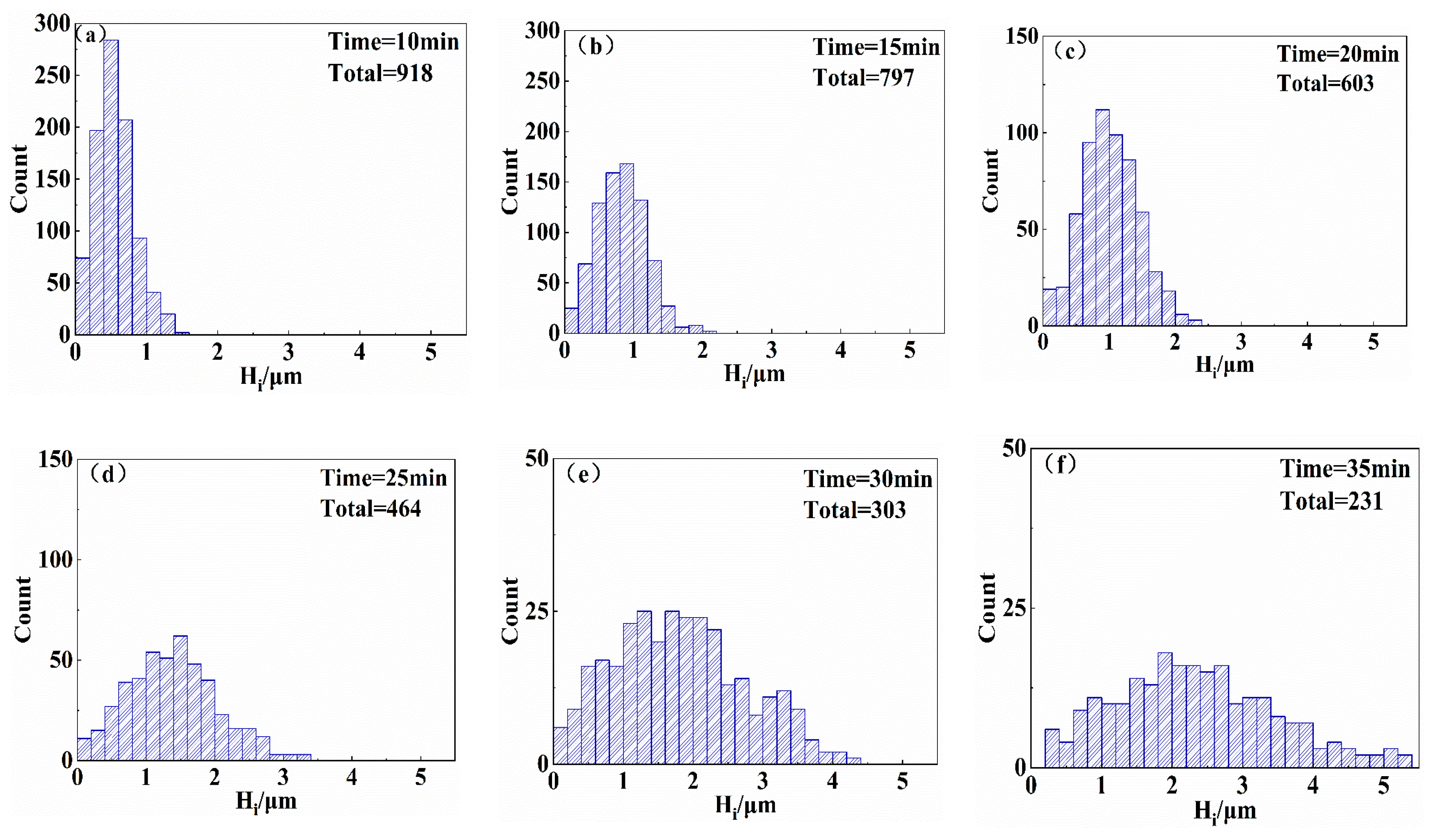

4.1. Surface Morphology of the Wafers

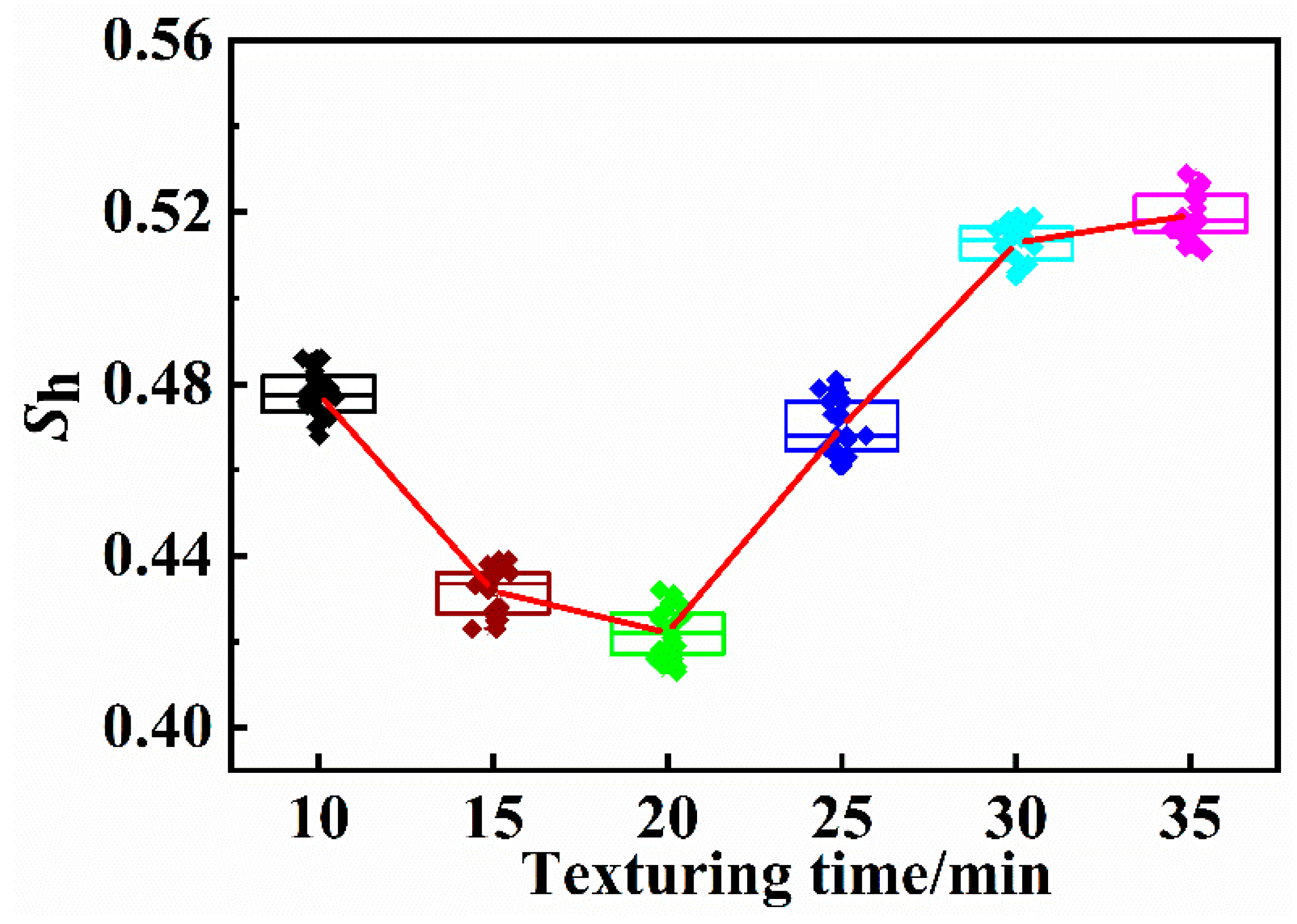

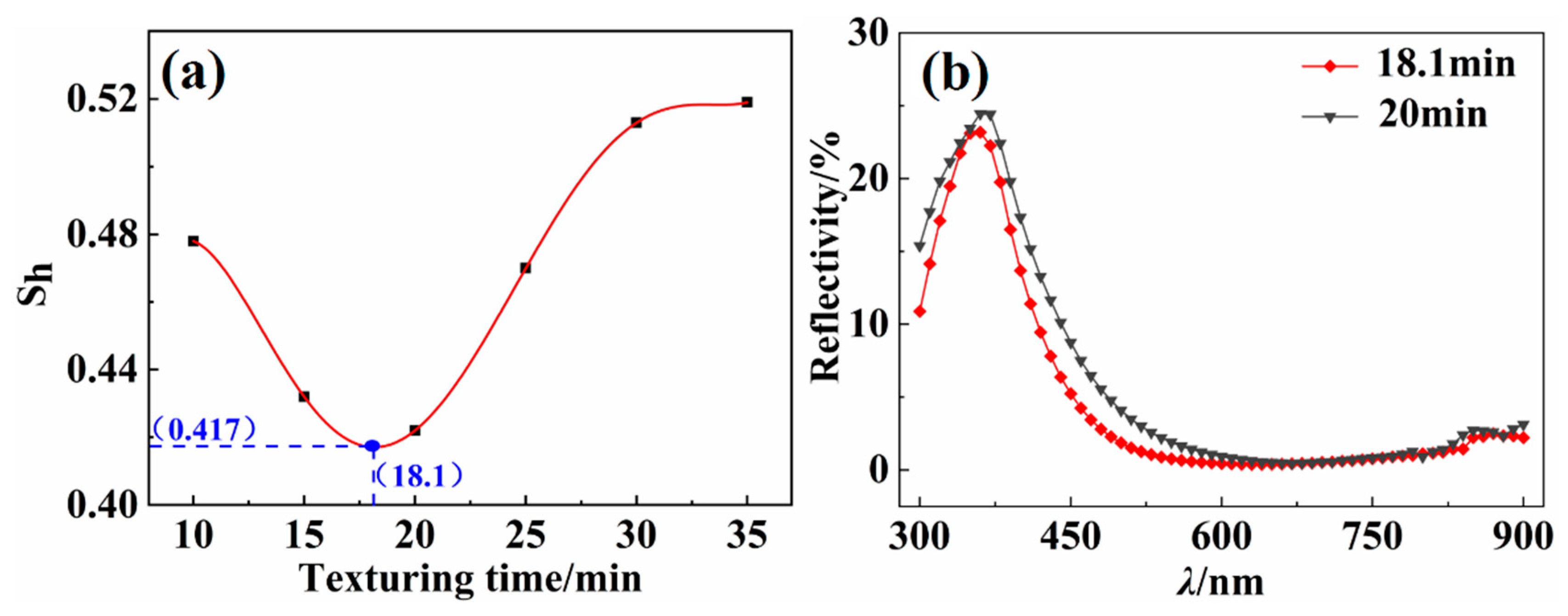

4.2. Relative Standard deviation (Sh) of the Pyramidal Texture

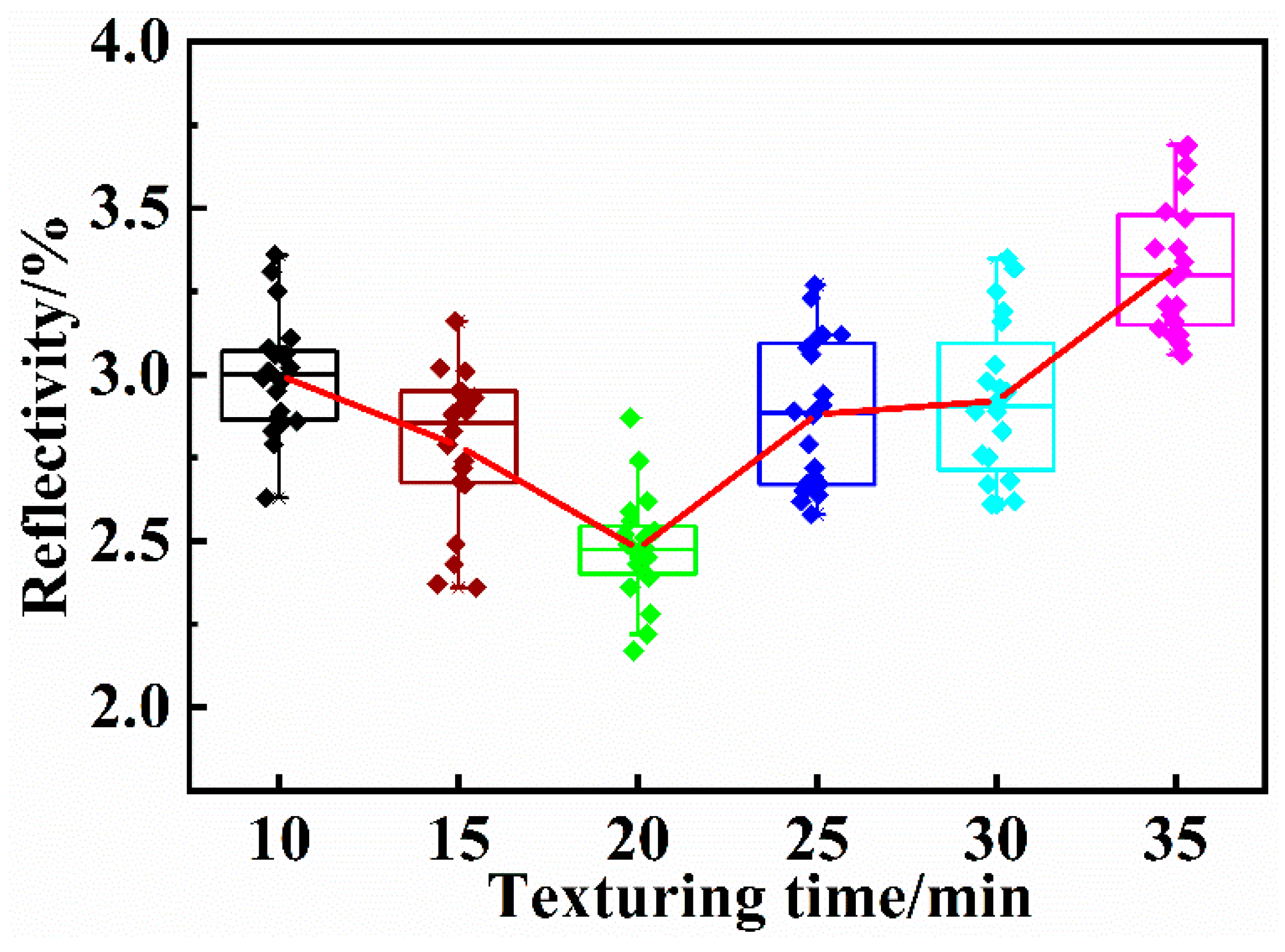

4.3. Reflectivity of the Wafers

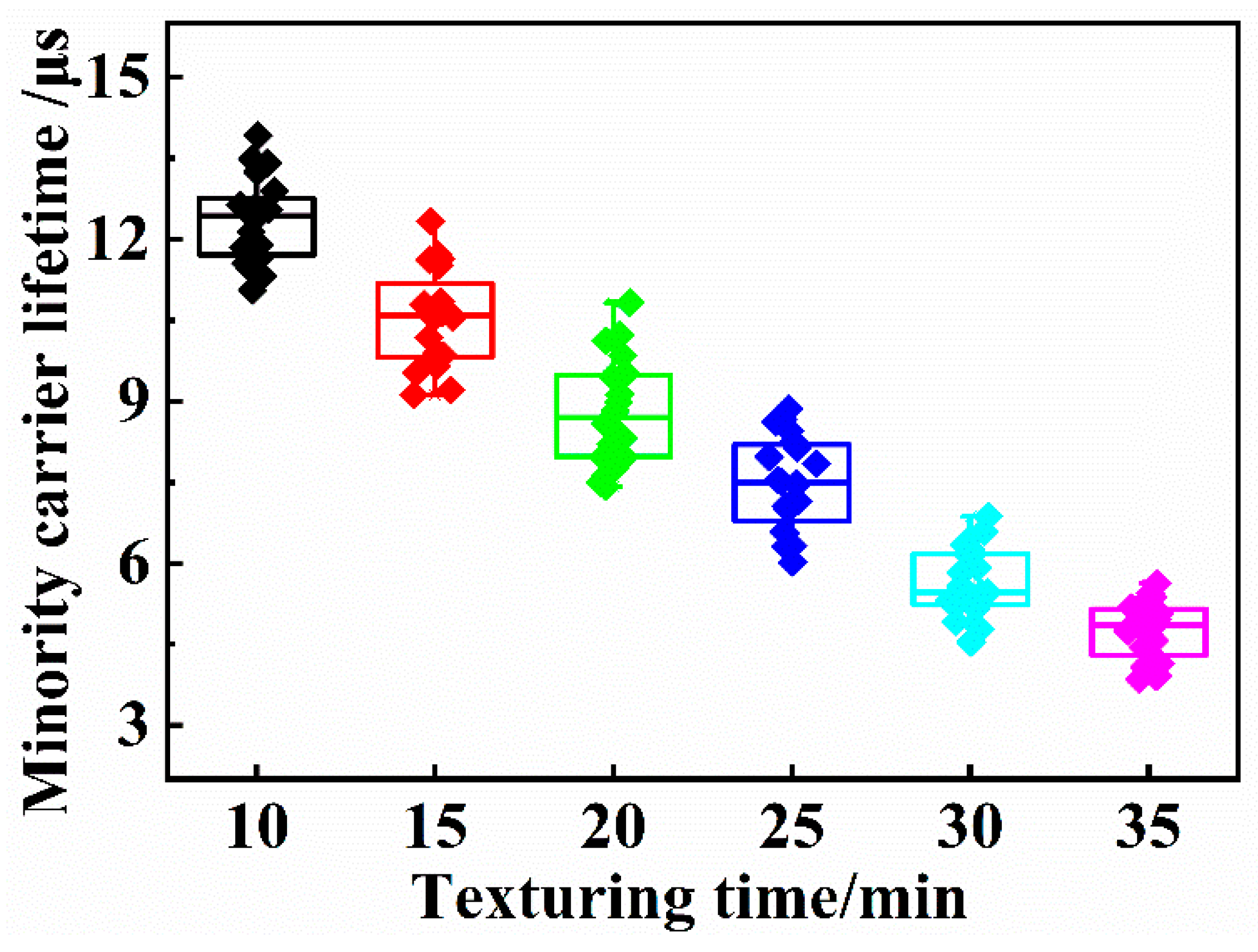

4.4. Minority Carrier Lifetime of the Wafers

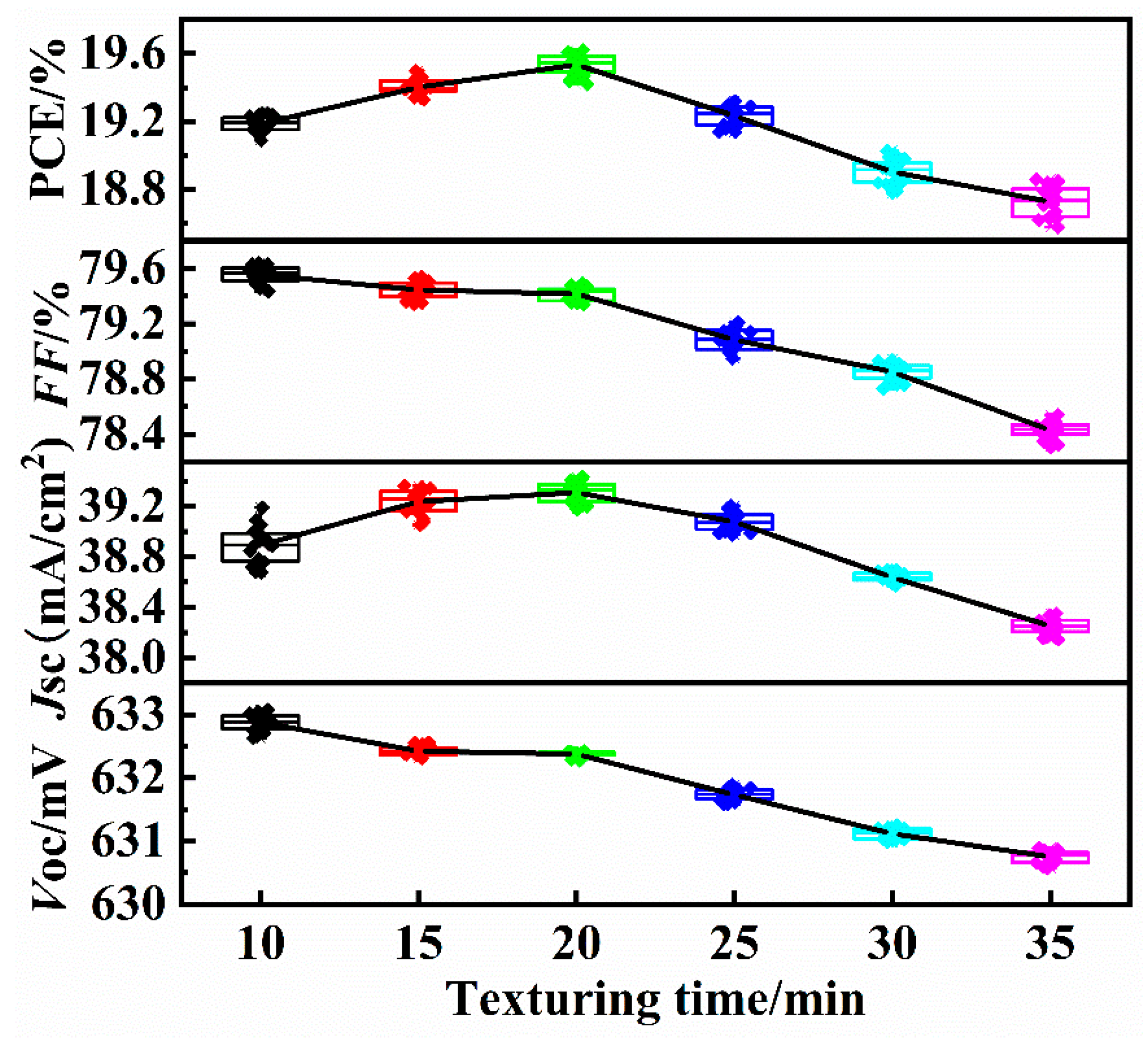

4.5. Electrical Properties of the Silicon Cells

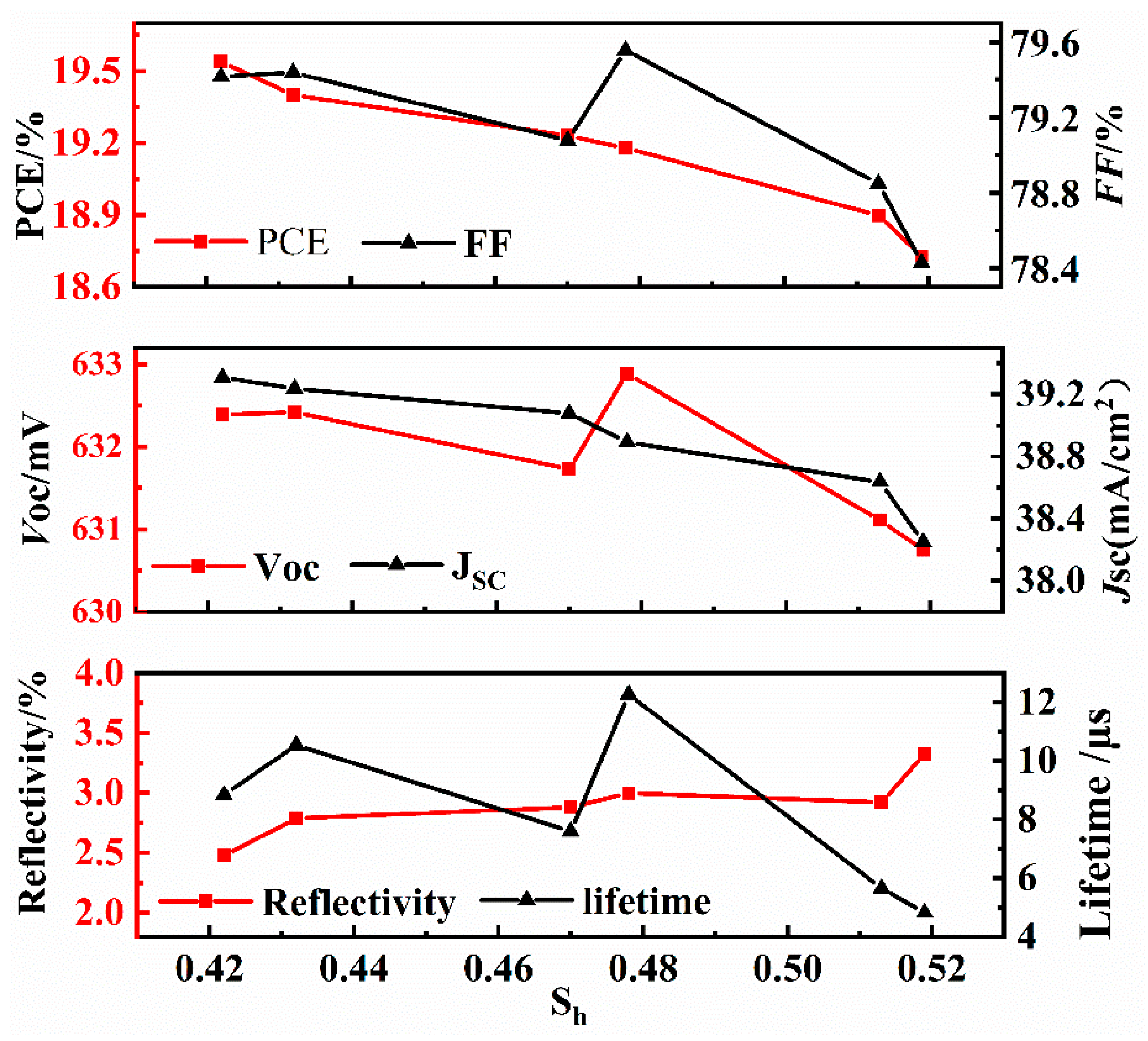

4.6. Relations between the Relative Standard Deviation and Photoelectric Characteristics

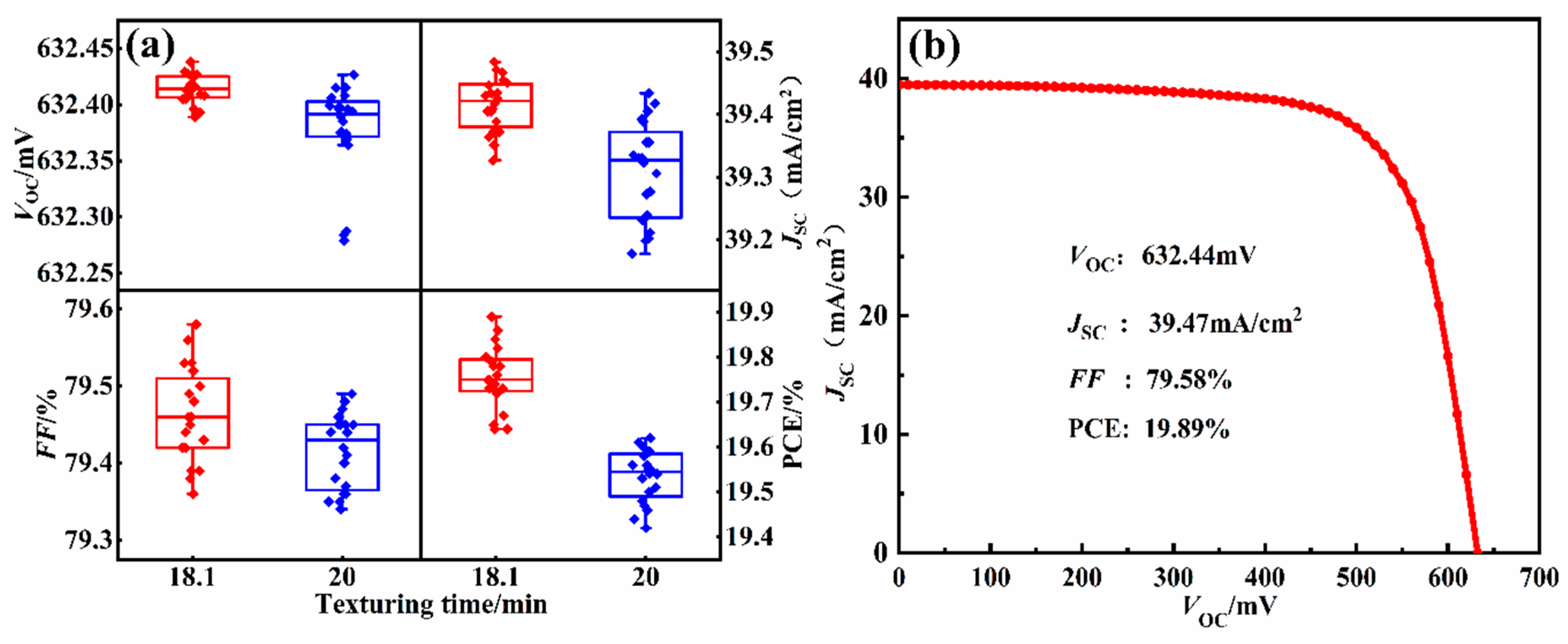

4.7. Optimization of Process Parameters

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Abdullah, M.F.; Alghoul, M.A.; Naser, H.; Asim, N.; Ahmadi, S.; Yatim, B.; Sopian, K. Research and development efforts on texturization to reduce the optical losses at front surface of silicon solar cell. Renew. Sustain. Energy Rev. 2016, 66, 380–398. [Google Scholar] [CrossRef]

- Green, M.A.; Dunlop, E.D.; Levi, D.H.; Hohl-Ebinger, J.; Yoshita, M.; Ho-Baillie, A.W.Y. Solar cell efficiency tables (version 54). Prog. Photovolt. Res. Appl. 2019, 27, 565–575. [Google Scholar] [CrossRef]

- Rahman, A.; Ashraf, A.; Xin, H.; Tong, X.; Sutter, P.; Eisaman, M.D.; Black, C.T. Sub-50-nm self-assembled nanotextures for enhanced broadband antireflection in silicon solar cells. Nat. Commun. 2015, 6, 5963. [Google Scholar] [CrossRef] [PubMed]

- Souren, F.M.M.; Rentsch, J.; van de Sanden, M.C.M. Relation between light trapping and surface topography of plasma textured crystalline silicon wafers. Prog. Photovolt. Res. Appl. 2015, 23, 352–366. [Google Scholar] [CrossRef]

- Escarré, J.; Söderström, K.; Despeisse, M.; Nicolay, S.; Battaglia, C.; Bugnon, G.; Ding, L.; Meillaud, F.; Haug, F.-J.; Ballif, C. Geometric light trapping for high efficiency thin film silicon solar cells. Sol. Energy Mater. Sol. Cells 2012, 98, 185–190. [Google Scholar] [CrossRef]

- Wang, F.; Zhang, Y.; Yang, M.; Sui, Y.; Sun, Y.; Yang, L.; Yang, J.; Zhang, X. Insights into nucleation engineering in Si pyramidal texturing for high performance heterojunction solar cells applications. J. Alloys Compd. 2018, 752, 53–60. [Google Scholar] [CrossRef]

- Stapf, A.; Honeit, F.; Gondek, C.; Kroke, E. Texturing of monocrystalline silicon wafers by HF-HCl-H2O2 mixtures: Generation of random inverted pyramids and simulation of light trapping in PERC solar cells. Sol. Energy Mater. Sol. Cells 2017, 159, 112–120. [Google Scholar] [CrossRef]

- Moroz, V.; Huang, J.; Wijekoon, K.; Tanner, D. Experimental and theoretical analysis of the optical behavior of textured silicon wafers. In Proceedings of the IEEE Photovoltaic Specialists Conference, Seattle, WA, USA, 19–24 June 2011; pp. 2900–2905. [Google Scholar] [CrossRef]

- Kim, H.; Park, S.; Kim, S.M.; Kim, S.; Kim, Y.D.; Tark, S.J.; Kim, D. Influence of surface texturing conditions on crystalline silicon solar cell performance. Curr. Appl. Phys. 2013, 13, S34–S40. [Google Scholar] [CrossRef]

- Dai, X.; Chen, T.; Cai, H.; Wen, H.; Sun, Y. Improving Performance of Organic-Silicon Heterojunction Solar Cells Based on Textured Surface via Acid Processing. ACS Appl. Mater. Interfaces 2016, 8, 14572–14577. [Google Scholar] [CrossRef]

- Khanna, A.; Basu, P.K.; Filipovic, A.; Shanmugam, V.; Schmiga, C.; Aberle, A.G.; Mueller, T. Influence of random pyramid surface texture on silver screen-printed contact formation for monocrystalline silicon wafer solar cells. Sol. Energy Mater. Sol. Cells 2015, 132, 589–596. [Google Scholar] [CrossRef]

- Chen, K.; Liu, Y.; Wang, X.; Zhang, L.; Su, X. Novel texturing process for diamond-wire-sawn single-crystalline silicon solar cell. Sol. Energy Mater. Sol. Cells 2015, 133, 148–155. [Google Scholar] [CrossRef]

- Wang, L.; Wang, F.; Zhang, X.; Wang, N.; Jiang, Y.; Hao, Q.; Zhao, Y. Improving efficiency of silicon heterojunction solar cells by surface texturing of silicon wafers using tetramethylammonium hydroxide. J. Power Sources 2014, 268, 619–624. [Google Scholar] [CrossRef]

- Huang, B.-R.; Yang, Y.-K.; Yang, W.-L. Key technique for texturing a uniform pyramid structure with a layer of silicon nitride on monocrystalline silicon wafer. Appl. Surf. Sci. 2013, 266, 245–249. [Google Scholar] [CrossRef]

- Park, H.; Kwon, S.; Lee, J.S.; Lim, H.J.; Yoon, S.; Kim, D. Improvement on surface texturing of single crystalline silicon for solar cells by saw-damage etching using an acidic solution. Sol. Energy Mater. Sol. Cells 2009, 93, 1773–1778. [Google Scholar] [CrossRef]

- Basu, P.K.; Sarangi, D.; Shetty, K.D.; Boreland, M.B. Liquid silicate additive for alkaline texturing of mono-Si wafers to improve process bath lifetime and reduce IPA consumption. Sol. Energy Mater. Sol. Cells 2013, 113, 37–43. [Google Scholar] [CrossRef]

- Wu, G.; Liu, Y.; Liu, M.; Zhang, Y.; Zhu, P.; Wang, M.; Zheng, G.; Wang, G.; Wang, D. High-Efficiency p-Type Si Solar Cell Fabricated by Using Firing-Through Aluminum Paste on the Cell Back Side. Materials 2019, 12, 3388. [Google Scholar] [CrossRef]

- Basu, P.K.; Khanna, A.; Hameiri, Z. The effect of front pyramid heights on the efficiency of homogeneously textured inline-diffused screen-printed monocrystalline silicon wafer solar cells. Renew. Energy 2015, 78, 590–598. [Google Scholar] [CrossRef]

- Ju, M.; Balaji, N.; Park, C.; Thanh Nguyen, H.T.; Cui, J.; Oh, D.; Jeon, M.; Kang, J.; Shim, G.; Yi, J. The effect of small pyramid texturing on the enhanced passivation and efficiency of single c-Si solar cells. RSC Adv. 2016, 6, 49831–49838. [Google Scholar] [CrossRef]

- Basu, P.K.; Dhasmana, H.; Udayakumar, N.; Khan, F.; Thakur, D.K. Regulated low cost pre-treatment step for surface texturization of large area industrial single crystalline silicon solar cell. Sol. Energy Mater. Sol. Cells 2010, 94, 1049–1054. [Google Scholar] [CrossRef]

- Basu, P.K.; Sarangi, D.; Boreland, M.B. Single-Component Damage-Etch Process for Improved Texturization of Monocrystalline Silicon Wafer Solar Cells. IEEE J. Photovolt. 2013, 3, 1222–1228. [Google Scholar] [CrossRef]

- Ju, M.; Mallem, K.; Dutta, S.; Balaji, N.; Oh, D.; Cho, E.-C.; Cho, Y.H.; Kim, Y.; Yi, J. Influence of small size pyramid texturing on contact shading loss and performance analysis of Ag-screen printed mono crystalline silicon solar cells. Mater. Sci. Semicond. Process. 2018, 85, 68–75. [Google Scholar] [CrossRef]

- Akila, B.S.; Vaithinathan, K.; Balaganapathi, T.; Vinoth, S.; Thilakan, P. Investigations on the correlation between surface texturing histogram and the spectral reflectance of (100) Crystalline Silicon Substrate textured using anisotropic etching. Sens. Actuators A Phys. 2017. [Google Scholar] [CrossRef]

- Kegel, J.; Angermann, H.; Stürzebecher, U.; Conrad, E.; Mews, M.; Korte, L.; Stegemann, B. Over 20% conversion efficiency on silicon heterojunction solar cells by IPA-free substrate texturization. Appl. Surf. Sci. 2014, 301, 56–62. [Google Scholar] [CrossRef]

- Lien, S.-Y.; Yang, C.-H.; Hsu, C.-H.; Lin, Y.-S.; Wang, C.-C.; Wuu, D.-S. Optimization of textured structure on crystalline silicon wafer for heterojunction solar cell. Mater. Chem. Phys. 2012, 133, 63–68. [Google Scholar] [CrossRef]

- Wefringhaus, E.; Kesnar, C.; Löhmann, M. Statistical Approach to the Description of Random Pyramid Surfaces using 3D Surface Profiles. Energy Procedia 2011, 8, 135–140. [Google Scholar] [CrossRef][Green Version]

- Kim, J.; Inns, D.; Fogel, K.; Sadana, D.K. Surface texturing of single-crystalline silicon solar cells using low density SiO2 films as an anisotropic etch mask. Sol. Energy Mater. Sol. Cells 2010, 94, 2091–2093. [Google Scholar] [CrossRef]

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Fang, Z.; Xu, Z.; Jang, T.; Zhou, F.; Huang, S. Standard Deviation Quantitative Characterization and Process Optimization of the Pyramidal Texture of Monocrystalline Silicon Cells. Materials 2020, 13, 564. https://doi.org/10.3390/ma13030564

Fang Z, Xu Z, Jang T, Zhou F, Huang S. Standard Deviation Quantitative Characterization and Process Optimization of the Pyramidal Texture of Monocrystalline Silicon Cells. Materials. 2020; 13(3):564. https://doi.org/10.3390/ma13030564

Chicago/Turabian StyleFang, Zheng, Zhilong Xu, Tao Jang, Fei Zhou, and Shixiang Huang. 2020. "Standard Deviation Quantitative Characterization and Process Optimization of the Pyramidal Texture of Monocrystalline Silicon Cells" Materials 13, no. 3: 564. https://doi.org/10.3390/ma13030564

APA StyleFang, Z., Xu, Z., Jang, T., Zhou, F., & Huang, S. (2020). Standard Deviation Quantitative Characterization and Process Optimization of the Pyramidal Texture of Monocrystalline Silicon Cells. Materials, 13(3), 564. https://doi.org/10.3390/ma13030564