Low-Temperature In-Induced Holes Formation in Native-SiOx/Si(111) Substrates for Self-Catalyzed MBE Growth of GaAs Nanowires

Abstract

1. Introduction

2. Materials and Methods

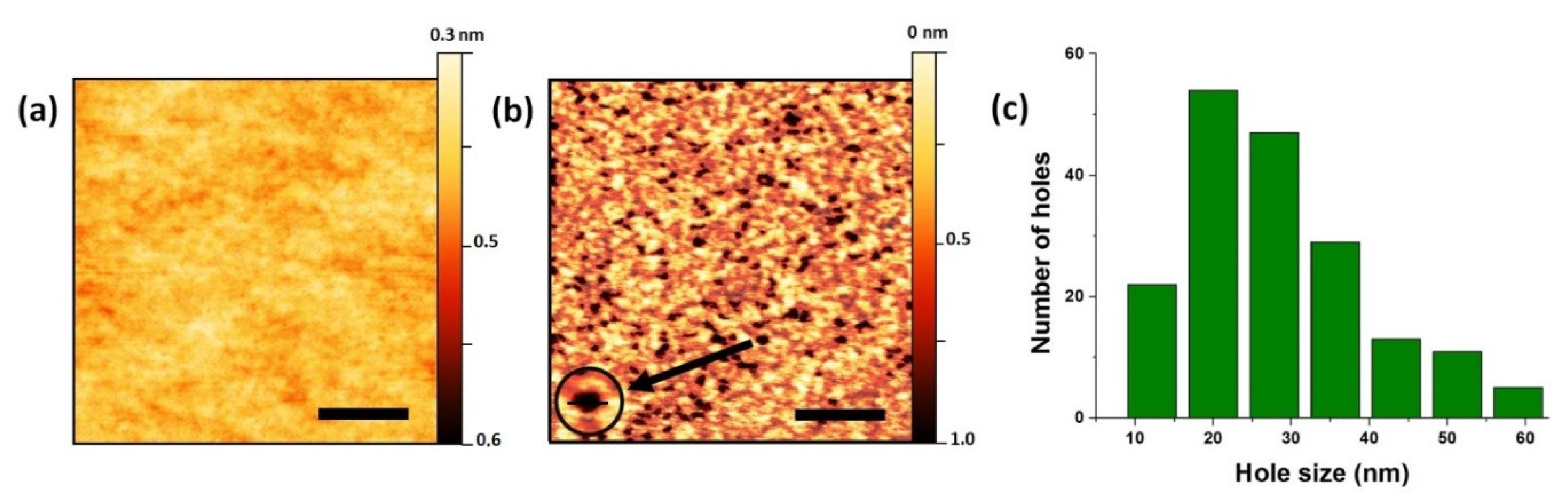

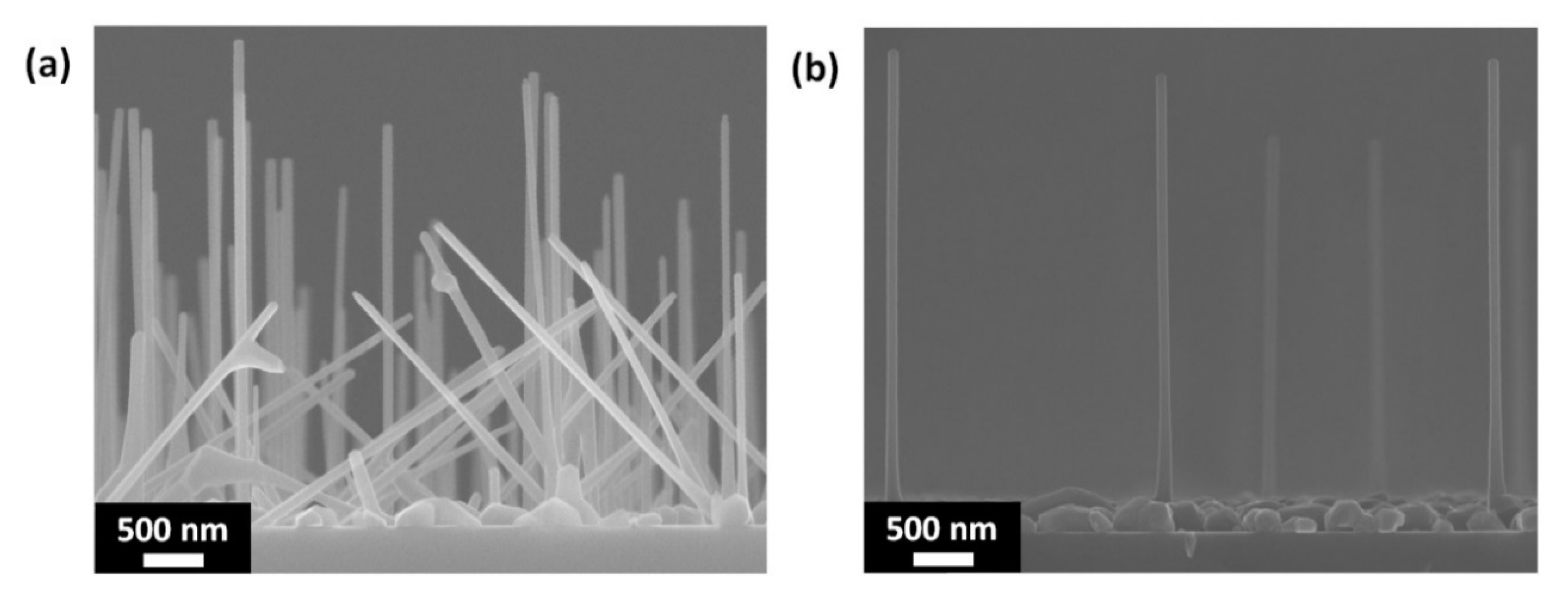

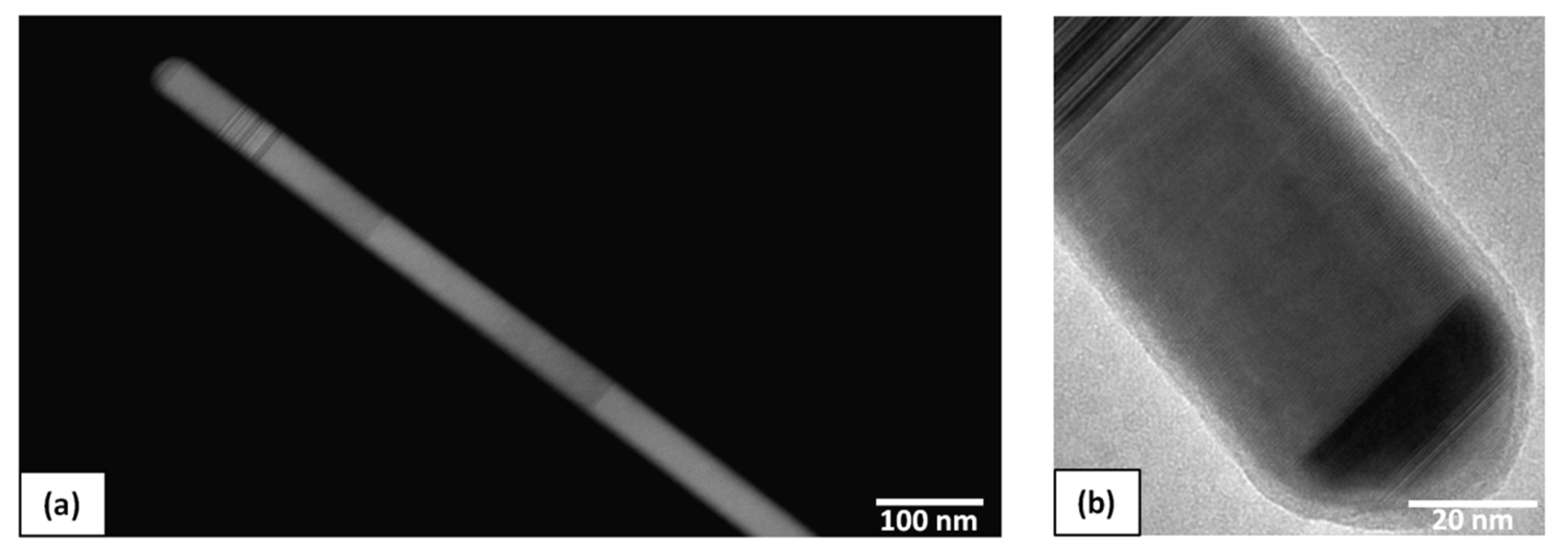

3. Results and Discussion

Author Contributions

Funding

Conflicts of Interest

References

- Wong-Leung, J.; Yang, I.; Li, Z.; Karuturi, S.K.; Fu, L.; Tan, H.H.; Jagadish, C. Engineering III–V Semiconductor Nanowires for Device Applications. Adv. Mater. 2019, 32, e1904359. [Google Scholar] [CrossRef] [PubMed]

- Gudiksen, M.S.; Lauhon, L.J.; Wang, J.; Smith, D.C.; Lieber, C.M. Growth of nanowire superlattice structures for nanoscale photonics and electronics. Nature 2002, 415, 617–620. [Google Scholar] [CrossRef]

- Patolsky, F.; Zheng, G.; Hayden, O.; Lakadamyali, M.; Zhuang, X.; Lieber, C.M. Electrical detection of single viruses. Proc. Natl. Acad. Sci. USA 2004, 101, 14017–14022. [Google Scholar] [CrossRef]

- Сибирев, Н.; Kotlyar, K.; Koryakin, A.A.; Shtrom, I.V.; Ubiivovk, E.V.; Soshnikov, I.P.; Reznik, R.R.; Bouravleuv, A.D.; Cirlin, G. Solar Cell Based on Core/Shell Nanowires. Semiconductors 2018, 52, 1568–1572. [Google Scholar] [CrossRef]

- Glas, F. Critical dimensions for the plastic relaxation of strained axial heterostructures in free-standing nanowires. Phys. Rev. B 2006, 74, 121302. [Google Scholar] [CrossRef]

- Chuang, L.C.; Moewe, M.; Chase, C.; Kobayashi, N.P.; Chang-Hasnain, C.; Crankshaw, S. Critical diameter for III-V nanowires grown on lattice-mismatched substrates. Appl. Phys. Lett. 2007, 90, 43115. [Google Scholar] [CrossRef]

- Moewe, M.; Chuang, L.C.; Dubrovskii, V.G.; Chang-Hasnain, C. Growth mechanisms and crystallographic structure of InP nanowires on lattice-mismatched substrates. J. Appl. Phys. 2008, 104, 44313. [Google Scholar] [CrossRef]

- Wagner, R.S.; Ellis, W.C. Vapor-liquid-solid mechanism of single crystal growth. Appl. Phys. Lett. 1964, 4, 89. [Google Scholar] [CrossRef]

- Dubrovskii, V.G.; Cirlin, G.; Ustinov, V.M. Semiconductor nanowhiskers: Synthesis, properties, and applications. Semiconductors 2009, 43, 1539–1584. [Google Scholar] [CrossRef]

- Bullis, W. Properties of gold in silicon. Solid State Electron. 1966, 9, 143–168. [Google Scholar] [CrossRef]

- Perea, D.E.; Allen, J.E.; May, S.J.; Wessels, B.W.; Seidman, D.N.; Lauhon, L.J. Three-Dimensional Nanoscale Composition Mapping of Semiconductor Nanowires. Nano Lett. 2006, 6, 181–185. [Google Scholar] [CrossRef] [PubMed]

- Bar Sadan, M.; Barthel, J.; Shtrikman, H.; Houben, L. Direct Imaging of Single Au Atoms Within GaAs Nanowires. Nano Lett. 2012, 12, 2352–2356. [Google Scholar] [CrossRef]

- Cirlin, G.; Dubrovskii, V.G.; Samsonenko, Y.B.; Bouravleuv, A.D.; DuRose, K.; Proskuryakov, Y.Y.; Mendes, B.; Bowen, L.; Kaliteevski, M.A.; A Abram, R.; et al. Self-catalyzed, pure zincblende GaAs nanowires grown on Si(111) by molecular beam epitaxy. Phys. Rev. B 2010, 82, 035302. [Google Scholar] [CrossRef]

- Colombo, C.; Spirkoska, D.; Frimmer, M.; Abstreiter, G.; I Morral, A.F. Ga-assisted catalyst-free growth mechanism of GaAs nanowires by molecular beam epitaxy. Phys. Rev. B 2008, 77, 155326. [Google Scholar] [CrossRef]

- Jabeen, F.; Grillo, V.; Rubini, S.; Martelli, F. Self-catalyzed growth of GaAs nanowires on cleaved Si by molecular beam epitaxy. Nanotechnology 2008, 19, 275711. [Google Scholar] [CrossRef] [PubMed]

- Plissard, S.R.; Dick, K.A.; Larrieu, G.; Godey, S.; Addad, A.; Wallart, X.; Caroff, P. Gold-free growth of GaAs nanowires on silicon: Arrays and polytypism. Nanotechnology 2010, 21, 385602. [Google Scholar] [CrossRef] [PubMed]

- Reznik, R.R.; Kotlyar, K.P.; I Khrebtov, A.; Samsonenko, Y.B.; Soshnikov, I.P.; Dyakonov, V.; Zadiranov, U.M.; Tankelevskaya, E.M.; A Kudryashov, D.; Shevchuk, D.S.; et al. Development of methods for orderly growth of nanowires. J. Phys. Conf. Ser. 2015, 661, 012053. [Google Scholar] [CrossRef]

- I Morral, A.F.; Colombo, C.; Abstreiter, G.; Arbiol, J.; Morante, J.R. Nucleation mechanism of gallium-assisted molecular beam epitaxy growth of gallium arsenide nanowires. Appl. Phys. Lett. 2008, 92, 063112. [Google Scholar] [CrossRef]

- Küpers, H.; Bastiman, F.; Luna, E.; Somaschini, C.; Geelhaar, L. Ga predeposition for the Ga-assisted growth of GaAs nanowire ensembles with low number density and homogeneous length. J. Cryst. Growth 2017, 459, 43–49. [Google Scholar] [CrossRef]

- Tauchnitz, T.; Nurmamytov, T.; Hübner, R.; Engler, M.; Facsko, S.; Schneider, H.; Helm, M.; Dimakis, E. Decoupling the Two Roles of Ga Droplets in the Self-Catalyzed Growth of GaAs Nanowires on SiOx/Si(111) Substrates. Cryst. Growth Des. 2017, 17, 5276–5282. [Google Scholar] [CrossRef]

- Koivusalo, E.; Hakkarainen, T.V.; Guina, M.D.; Dubrovskii, V.G. Sub-Poissonian Narrowing of Length Distributions Realized in Ga-Catalyzed GaAs Nanowires. Nano Lett. 2017, 17, 5350–5355. [Google Scholar] [CrossRef] [PubMed]

- Schmidt, V.; Wittemann, J.V.; Senz, S.; Gösele, U. Silicon Nanowires: A Review on Aspects of their Growth and their Electrical Properties. Adv. Mater. 2009, 21, 2681–2702. [Google Scholar] [CrossRef]

- Egorov, A.; Kovsh, A.; Ustinov, V.; Zhukov, A.; Maksimov, M.; Cirlin, G.; Ledentsov, N.; Bimberg, D.; Werner, P.; Alferov, Z. Self-organized InAs quantum dots in a silicon matrix. J. Cryst. Growth 1999, 201, 1202–1204. [Google Scholar] [CrossRef]

- Zakharov, N.; Werner, P.; Gösele, U.; Heitz, R.; Bimberg, D.; Ledentsov, N.N.; Ustinov, V.M.; Volovik, B.V.; Alferov, Z.I.; Polyakov, N.K.; et al. Structure and optical properties of Si/InAs/Si layers grown by molecular beam epitaxy on Si substrate. Appl. Phys. Lett. 2000, 76, 2677–2679. [Google Scholar] [CrossRef]

- Cirlin, G.E.; Polyakov, N.K.; Petrov, V.N.; Egorov, V.A.; Samsonenko, Y.B.; Denisov, D.V.; Busov, V.M.; Volovik, B.V.; Ustinov, V.M.; Alferov, Z.I.; et al. Effect of growth conditions on InAs nanoislands formation on Si(100) surface. Czechoslov. J. Phys. 1999, 49, 1547–1552. [Google Scholar] [CrossRef]

- Fouquat, L.; Vettori, M.; Botella, C.; Benamrouche, A.; Penuelas, J.; Grenet, G. Early Stages of GaAs Nanowires VLS Self-Catalyzed Growth on Silica-terminated Silicon Substrate: A Photoemission Study; Cornell University: Ithaca, NY, USA, 2019. [Google Scholar]

- Sutter, E.; Sutter, P. Enhanced oxidation of nanoscale In particles at the interface with a Si nanowire. Appl. Phys. Lett. 2012, 100, 231602. [Google Scholar] [CrossRef]

- Ow-Yang, C.W.; Shigesato, Y.; Paine, D.C. Interfacial stability of an indium tin oxide thin film deposited on Si and Si0.85Ge0.15. J. Appl. Phys. 2000, 88, 3717–3724. [Google Scholar] [CrossRef]

- Kolluri, S.; Chandorkar, A. Effect of annealing on the surface and interface properties of indium oxide-silicon structures. Thin Solid Films 1993, 230, 39–44. [Google Scholar] [CrossRef]

- Koryakin, A.A.; Kukushkin, S.A.; Kotlyar, K.P.; Ubyivovk, E.; Reznik, R.R.; Cirlin, G. A new insight into the mechanism of low-temperature Au-assisted growth of InAs nanowires. CrystEngComm 2019, 21, 4707–4717. [Google Scholar] [CrossRef]

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

R. Reznik, R.; P. Kotlyar, K.; O. Gridchin, V.; V. Ubyivovk, E.; V. Federov, V.; I. Khrebtov, A.; S. Shevchuk, D.; E. Cirlin, G. Low-Temperature In-Induced Holes Formation in Native-SiOx/Si(111) Substrates for Self-Catalyzed MBE Growth of GaAs Nanowires. Materials 2020, 13, 3449. https://doi.org/10.3390/ma13163449

R. Reznik R, P. Kotlyar K, O. Gridchin V, V. Ubyivovk E, V. Federov V, I. Khrebtov A, S. Shevchuk D, E. Cirlin G. Low-Temperature In-Induced Holes Formation in Native-SiOx/Si(111) Substrates for Self-Catalyzed MBE Growth of GaAs Nanowires. Materials. 2020; 13(16):3449. https://doi.org/10.3390/ma13163449

Chicago/Turabian StyleR. Reznik, Rodion, Konstantin P. Kotlyar, Vladislav O. Gridchin, Evgeniy V. Ubyivovk, Vladimir V. Federov, Artem I. Khrebtov, Dmitrii S. Shevchuk, and George E. Cirlin. 2020. "Low-Temperature In-Induced Holes Formation in Native-SiOx/Si(111) Substrates for Self-Catalyzed MBE Growth of GaAs Nanowires" Materials 13, no. 16: 3449. https://doi.org/10.3390/ma13163449

APA StyleR. Reznik, R., P. Kotlyar, K., O. Gridchin, V., V. Ubyivovk, E., V. Federov, V., I. Khrebtov, A., S. Shevchuk, D., & E. Cirlin, G. (2020). Low-Temperature In-Induced Holes Formation in Native-SiOx/Si(111) Substrates for Self-Catalyzed MBE Growth of GaAs Nanowires. Materials, 13(16), 3449. https://doi.org/10.3390/ma13163449