1. Introduction

Silicon carbide (SiC) is an attractive material for semiconductor devices operating under extreme conditions. This is because of its extraordinary physical properties, such as high electrical break down field, high thermal conductivity, and high electron saturation velocity [

1,

2,

3]. Among the many kinds of SiC devices, specific interest has been focused on the 4H-SiC gate turn-off thyristor (4H-SiC GTO) for pulsed-power applications because of its advantages in high voltage, high-current, and high temperature applications over silicon-based equivalent devices [

4,

5]. The conductivity modulated drift region of the GTO allows high voltages and high current densities while maintaining a low forward voltage [

6]. This conductivity modulation effect reduces the resistance of the thick, lowly-doped drift region that is required for blocking high voltages. This is achieved by the injection of carriers from adjacent device regions. However, the degree of conductivity modulation is heavily dependent on the carrier recombination from the point defects and extended defects in the SiC material, as such increasing the resistance of the drift region and hence the overall on-state power losses of the device. Therefore, it is of key importance to have a good knowledge of defects generation in the SiC material, which plays a crucial role in the well-known bipolar degradation in bipolar devices.

Although continuous improvement has been made in SiC epitaxial growth, such as the high uniformity in doping concentration and remarkable reduction of epi-defects (trianglar 3C inclusion and carrot defect) [

7,

8], the density of extended defects in SiC epi-wafer is still on the order of 10

2–10

4 cm

−2. The size and performance of SiC devices, especially for high-voltage bipolar devices, are still severely hindered by the extended defects, surface defects, and interfacial dislocations of SiC substrate and its epitaxial layers. In addition, the generation and propagation of defects in the process of device preparation, such as stacking faults, basal plane dislocations and point defects, are considered to degrade the electrical characteristics of power devices and their reliability. The influence of surface pit shape on 4H-SiC double implanted metal-oxide-semiconductor field-effect transistor (MOSFETs) reliability under a high temperature drain bias test has been investigated by Uchida. et al. [

9] in 2015, and the failure was revealed to be an oxide breakdown above the pit generated at the threading mixed dislocation in both pit shapes. Bonyadi. et al published the impact of a trianglar 3C inclusion on fabricated 4H-SiC PiN diodes, and they found that the existence of 3C triangular inclusions limit the active area of the devices and create a short path through the drift region which increases the leakage current almost 10

8 times higher than the devices fabricated on epitaxial layer with low defect density [

10].

In this work, an abnormal star-like defect was found after metal removal and KOH etching at 450 °C on the failed SiC GTO devices, which consists of several penetrating dislocations and exhibits the consistent orientation with the six-fold symmetry of silicon carbide. Its formation mechanisms and influence on the forward and blocking characteristic of SiC GTOs are investigated.

2. Materials and Methods

Figure 1 shows the schematic cross-section view of a 1.0 cm

2 SiC GTO. The conventional asymmetric blocking p

+np

−pn structure is used for the 4H-SiC GTO device. The five epitaxial layers were grown on an 4°-off n-type 4H-SiC wafer from Ascatron AB, Inc., Kista, Sweden. A 60 µm thick drift layer was then grown on the substrate, with a doping concentration of about 2 × 10

14 cm

−3. The highly doped anode layer (p

+∼2 × 10

19 cm

−3) is 2 µm and the gate layer (n

+∼2.3 × 10

17 cm

−3) is 2 µm thick. The top p

+ epilayer was first etched down to the base region. Nitrogen atoms were then implanted to form gate contact, followed by the creation of an n-type single zone junction termination extension (JTE) region by nitrogen implantation and activation anneal. Finally, the ohmic contacts to the anode, gate, and the substrate of the devices were formed by rapid thermal anneal and metal deposition.

Figure 1 shows the schematic cross-section view of a 1.0 cm

2 SiC GTO. The GTO has a 60 µm drift layer thickness.

The forward blocking and on-state characteristics for 1.0 cm2 GTOs were measured by a Keysight B1505 Semiconductor Parameter Analyzer (Keysight, CA, America) at room temperature. The negative voltage was applied to the cathode, while the anode is grounded. The applied trigger current on the gate was −100 mA. For forward blocking characterization, the applied voltages on the cathode was ranging from −3 KV to 0 V, which in this case was limited by the capability of our present B1505 Semiconductor Parameter Analyzer.

As some of the SiC GTOs exhibit lower breakdown voltage, the destructive physical analysis is then performed. Before the preferential etching of defects in the anode and gate layer, the Ni, Ni/Ti/Al alloy, and silicon dioxide passivation layer on the surface of anode and gate layer need to be eliminated. Thus, the GTO samples were repeatedly immersed in analytical reagent (AR) grade hydrochloric acid and 10% hydrofluoric acid solution, followed by ultrasonic cleaning in acetone, ethanol, and deionized water, each for 5−10 min, until the silicon carbide surface was exposed. Then, the preferential etching was carried out in the following process. A Ni-crucible filled with KOH granules of >85% purity (for the analysis) was used and heated in air to 450 °C within 2 h to evaporate the water. Then, the samples were fixed in a Ni-wire cage and were suspended into the melt for 15 min after preheating. The surface morphology of silicon carbide single crystal and dislocation etch pits were observed with the help of a LEXT OLS4000 3D laser confocal microscope and scanning electron microscope (HITACHI, Tokyo, Japan). The LEXT OLS4000 3D laser confocal microscope was manufactured by Olympus, Inc., Tokyo, Japan. A 405 nm laser was used as the source with a laser power of 6 mW. The vertical and transverse resolutions were 0.01 µm and 0.12 µm, respectively. The visible light mode and laser mode were used to obtain the surface morphology and 3D shape of the etch pits, respectively.

3. Results and Discussion

3.1. An Abnormal Star-Like Defect

The forward blocking and on-state characteristics for 1.0 cm2 GTOs were measured by a Keysight B1505 Semiconductor Parameter Analyzer. Most GTO devices have a breakdown voltage of more than 3 KV. However, a few GTO devices have a breakdown voltage of lower than 3 KV, and even close to zero. The number of the 1.0 cm2 SiC GTOs on a 4-inch 4H-SiC wafer is 54, and voltage failure GTO devices are scattered throughout the 4-inch 4H-SiC wafer. Therefore, the effect of the device preparation process, such as ion implantation and annealing, on the electrical properties of the device is excluded. A KLA Tencor Candela CS920 (Candela, Los Angeles, America) was used to identify and locate surface defects (triangle defects, carrot defects, and particles) of 4H-SiC epilayers before 1.0 cm2 GTOs preparation. Nevertheless, no correlation can be established between device voltage failure and surface defects. In order to study the reasons behind the low breakdown voltage, the defect exposure and characterization of the failure devices were carried out.

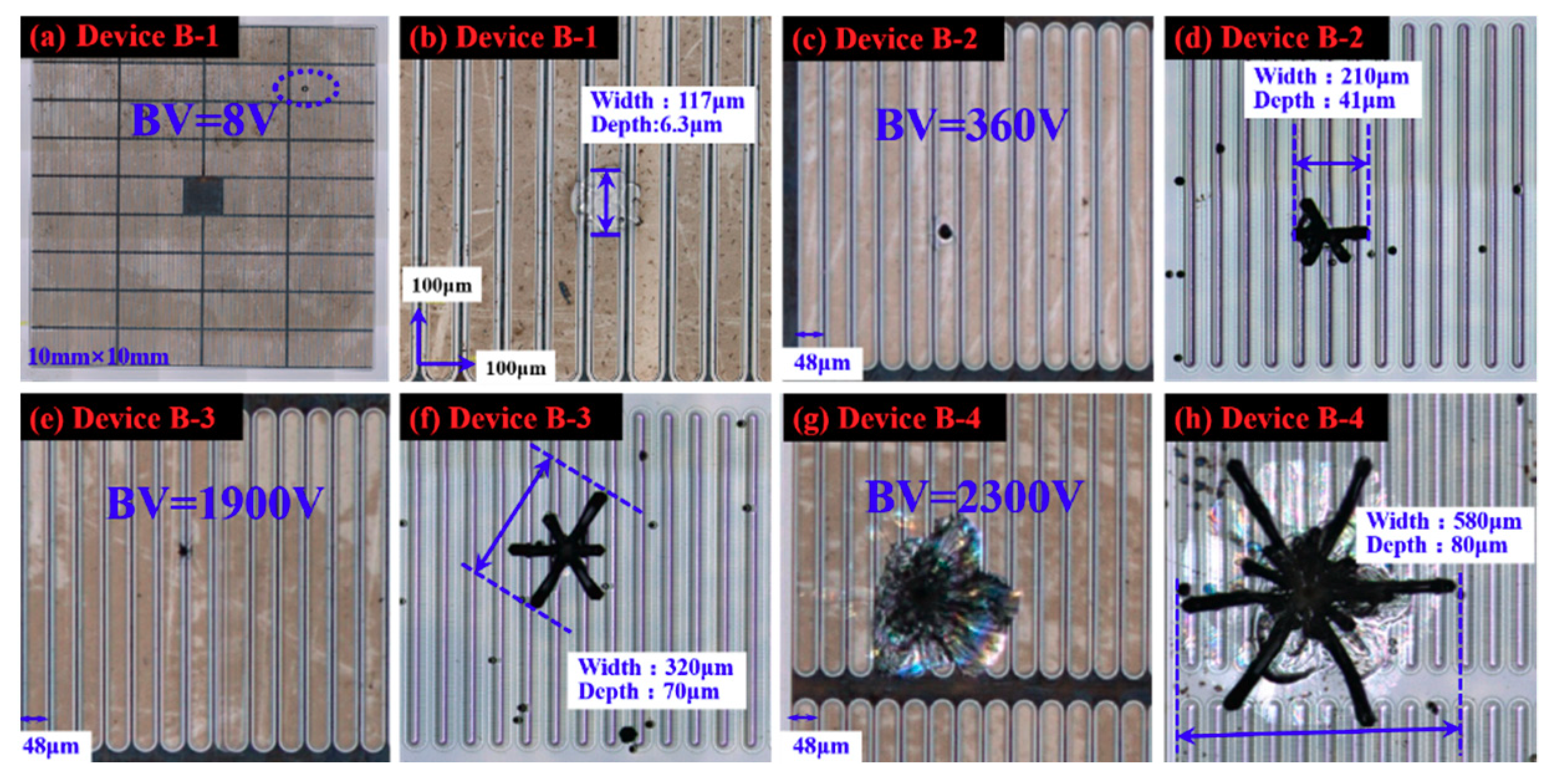

Morphology diagrams after metal removal at room temperature and KOH etching at 450 °C for device B1–B4 referral to

Table 1 are shown in

Figure 2. The Anode/Gate design of 1.0 mm

2 SiC GTO thyristors fabricated on the same wafer is a fine raster and the width of a single anode is 48 µm, which can be clearly seen in

Figure 2b. After metal removal, a large pit on the GTO device exists, which has a breakdown voltage lower than 3 KV. The big pit may be at the anode region, gate region, or across several anode regions from

Figure 2b,c,e,g. However, there are no big pits on devices with breakdown voltage higher than 3 KV. For device B-1, the pit on it after metal removal is 117 µm in width and 6.3 µm in depth, as shown in

Figure 2b, and it is noteworthy that the big pit runs through three anodes and two gates of a 1.0 cm

2 SiC GTO. After KOH etching at 450 °C, these big pits observed after metal removal developed into a hexagonal symmetric star-like etch pit with 210–580 µm in width and 41–80 µm in depth, as shown in

Figure 2d,f,h. The star-like etch pits run through 4–12 strip anodes of a 1.0 cm

2 SiC GTO, and one line of a star-like defect is perpendicular to the anode raster. In addition, the angle between the three dislocation lines of the star-like defect is almost 60° and the orientation of the three dislocation lines is consistent with the six-fold symmetry of silicon carbide.

Subcircular and hexagonal etching pits with depths of 2 to 7 µm appeared on the Si-face, which correspond to penetrating dislocations in 4H-SiC, as shown in

Figure 3b. It has been reported that large hexagonal etch pits without bottoms represent micropipes, middle-sized hexagonal etch pits with bottoms represent screw dislocations, while small hexagonal etch pits with bottoms represent threading edge dislocations [

11]. Amazingly, in

Figure 3a, the hexagonal symmetric star-like etch pit is much larger than the etch pit of a penetrating dislocation. Furthermore, as for the depth of the star-like etch pits being 41–80 µm and the GTO having a 60 µm drift layer thickness, as shown in

Figure 3c and

Figure 1, a star-like defect across the drift layer is found and almost extends into the 4H-SiC substrate.

3.2. Morphology and Structure of the Star-Like Defect

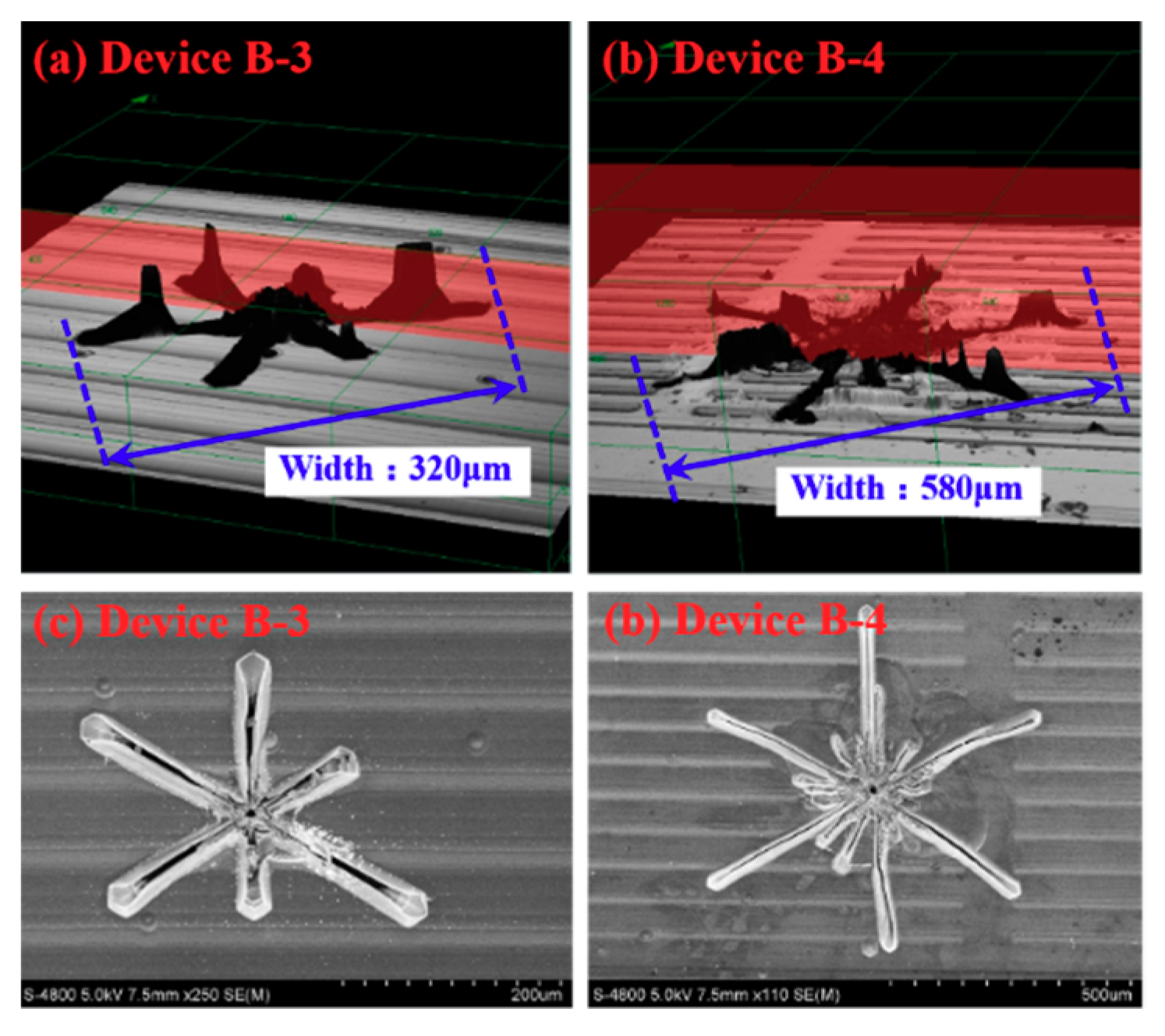

Then, the 3D-shape of the abnormal hexagonal symmetric star-like etch pits shown in

Figure 2f,h was measured by a LEXT OLS4000 3D laser confocal microscope and scanning electron microscope (SEM), and the results are shown in

Figure 4. From

Figure 4a,b, it can be found that the hexagonal symmetric star-like defect contains six to seven deep etch pits with a ladder cone shape section. These etch pits are located at the edge as well as the intersections of the three etch lines. According to the typical sectional view of etch pits, the hexagonal etch pits that have a ladder cone shape section correspond to a mixed dislocation with a Burgers vector of

+, where

and

(n = 1, 2, 3……; m = 1, 2, 3) [

12]. That is to say, the star-like defect consists of several mixed dislocations. In addition, the morphology obtained by SEM is shown in

Figure 4c,d, which is consistent with that obtained by the laser confocal microscope. Wu et al. [

13,

14] reported that they found a new stacking fault in 4H-SiC wafers through synchrotron white-beam x-ray topography. This fault has the shape of a six-pointed star, comprising faults with three different fault vectors of Shockley type. A micropipe is located in the center of the star stacking fault. However, the star-like defect found in our work after KOH etching at 450 °C consists of several mixed dislocations, not stacking faults.

3.3. The Influence of the Star-Like Defect on the Forward and Blocking Characteristic of SiC GTOs

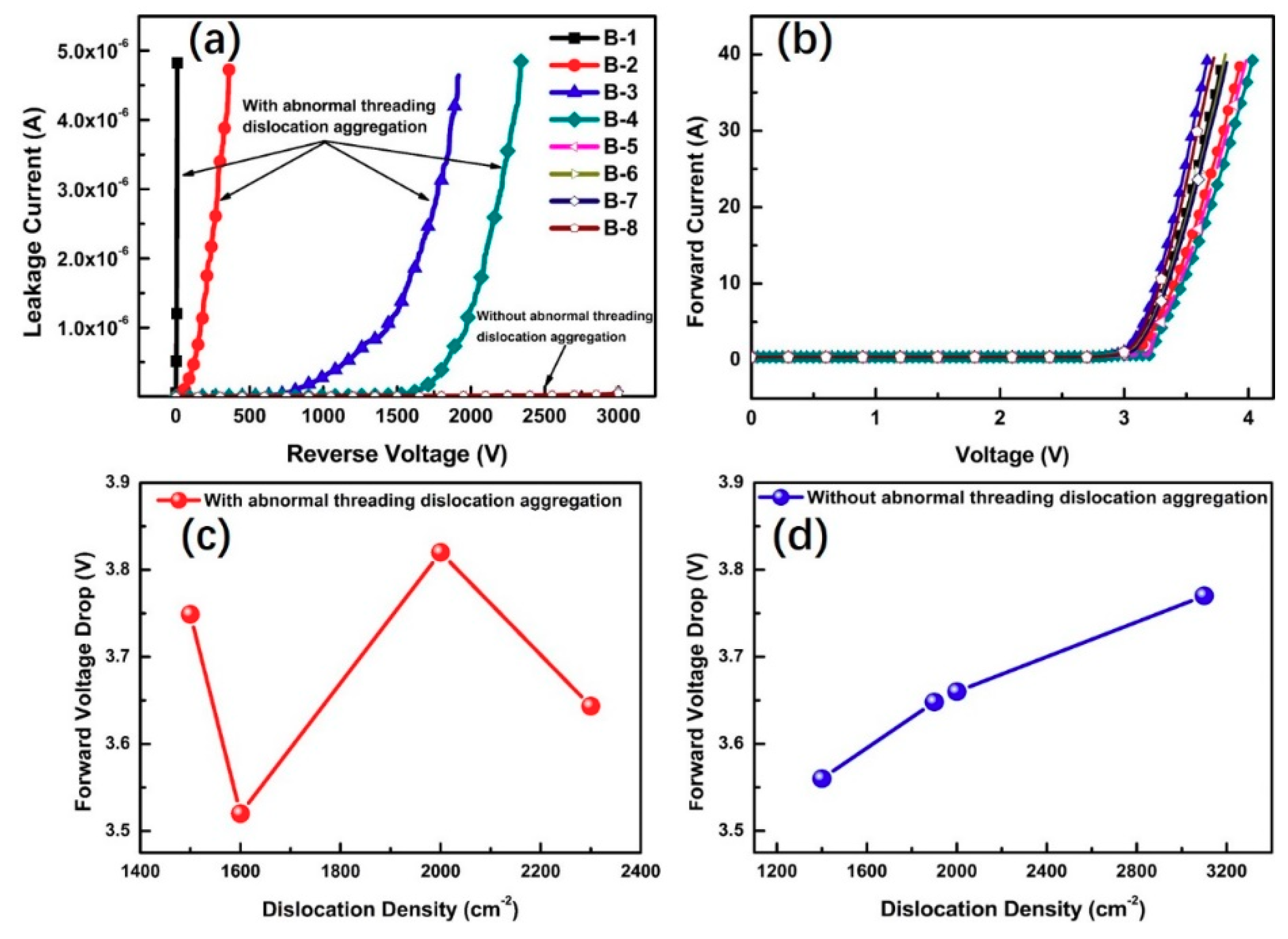

Reverse I–V and the forward characteristics of anode-gate GTOs for device B1–B8 were measured, and the result is shown in

Figure 5. The leakage current is on the order of 10

−6 A for devices B1–B4 before voltage failure, while it is about 10

−8 A for devices B5–B8. The leakage current value of the GTOs with abnormal threading dislocation aggregation is two orders of magnitude higher than the GTOs without abnormal threading dislocation aggregation. In addition, a summary of the breakdown voltage and dislocation density in devices B1–B8 is given in

Table 1. Herein, dislocation density was obtained by an average of nine points across the 1.0 mm

2 GTO [

15]. From

Table 1, it can be seen that the breakdown voltage shows no essential correlation with the dislocation density. Therefore, it can be inferred that these abnormal star-like etch defects from dislocation aggregation lead to the failure of blocking characteristics, rather than the isolated dislocations. It has been reported that inverted cone-shaped nano-scale pits with a diameter of approximately 200 nm, a depth of approximately 45 nm, were observed at the Schottky junction interface, and it was found that leakage current increases in these diodes due to the concentration of electric fields at the peaks of the pits [

16]. This is in a good agreement with the deteriorated blocking characteristics of current GTOs with large abnormal star-like defects.

Figure 5b shows the forward characteristics of anode-gate GTOs with and without abnormal threading dislocation aggregation. There is no essential difference between GTOs with and without abnormal dislocation aggregation. However, the abnormal dislocation aggregation can affect the relationship between voltage drop and dislocation density as shown in

Figure 5c,d, which is an interesting phenomenon. For GTOs without abnormal etch pits, a regular increase of forward voltage drop at 100 A/cm

2 was observed with the increase of threading dislocations density, which can be ascribed to the well-known carrier modulation degradation from enhanced carrier recombination at dislocations, while this correlation disappears in the presence of abnormal etch pits as shown in

Figure 4c, which plays a predominant role over dislocations in the blocking characteristics.

In single crystals, a penetrating dislocation occurs due to lattice distortions. As a result, these areas have higher strain energies than perfect single crystal regions. Due to the higher chemical potential, strained areas of single crystals are more liable to chemical attack than non-strained areas. The elastic strain energy of threading screw dislocations (TSDs) is greater than that of threading edge dislocations (TEDs) by a factor of 3 [

17]. The exposure and growth of the star-like defect after KOH etching means that the strain energy around the star-like defect is higher than that of the perfect single crystal regions. In addition, the higher stress and strain may be introduced by blocking characteristics measurements. From the above discussion and based on our current understanding of penetrating dislocations in 4H-SiC, we infer that the close penetrating dislocations will aggregate and merge under stress concentration, leading to forming star-like defects and releasing partial stress. Since stress concentration leads to the formation of the abnormal star-like defect after KOH etching, we deduce that the electrical stress also gives rise to the voltage concentration at the defect in the same way, which induces the close penetrating dislocations merge to form star-like defects, and in turn to reduce the breakdown voltage. Similar results have been reported that the breakdown voltages of the diodes with threading screw dislocations and threading edge dislocations were reduced by 15.5% and 6.5%, compared with those of a diode without defects [

18].

Based on the above discussion, forward voltage drop induced by an abnormal threading dislocation aggregation in 4H-SiC GTO devices is elucidated. Improving the quality of single crystals and reducing the connection of penetrating dislocations under mechanical or electrical stress are the keys to improving the reliability of SiC GTOs.

4. Conclusions

An abnormal star-like defect was found after both metal removal and KOH etching at 450 °C on the failed SiC GTO devices with lower breakdown voltage. It consists of several penetrating dislocations and its orientation is consistent with the six-fold symmetry of silicon carbide. The forward blocking characteristic of 1.0 cm2 GTOs is severely deteriorated by this abnormal star-like defect rather than the dislocation in much higher density. As for the forward characteristics, it is found that the influence of dislocation density on the forward voltage drop is affected by the presence of star-like defects from threading dislocation aggregation. The forward voltage drop at 100 A/cm2 for GTOs without abnormal etch pits shows a regular increase with the increasing of dislocation density, while this correlation disappears in the presence of abnormal etch pits. In a word, this abnormal star-like defect is a killing defect for both forward and blocking characteristics of SiC GTOs.

Author Contributions

Conceptualization, Y.C. and P.D.; Methodology, Y.C.; Software, L.L.; Validation, Y.C., Z.C. and J.L.; Formal Analysis, Z.L.; Investigation, Y.C.; Resources, Z.L.; Data Curation, J.L.; Writing—Original Draft Preparation, Y.C.; Writing—Review and Editing, P.D.

Funding

This research was funded by the Science Challenge Project, Grant No. TZ2018003-1.

Conflicts of Interest

The authors declare no conflict of interest.

References

- Morkoc, H.; Strite, S.; Gao, G.B.; Lin, M.E.; Sverdlov, B.; Burns, M. Large-band-gap SiC, III-V nitride, and II-VI ZnSe-based semiconductor device technologies. J. Appl. Phys. 1994, 76, 1363–1398. [Google Scholar] [CrossRef]

- Sriram, S.; Siergiej, R.R.; Clarke, R.C.; Agarwal, A.K.; Brandt, C.D. SiC for Microwave-Power Transistors. Phys. Status Solidi A 1997, 162, 441–457. [Google Scholar] [CrossRef]

- Barrett, D.L.; Seidensticker, R.G.; Gaida, W.; Hopkins, R.H.; Choyke, W.J. SiC boule growth by sublimation vapor transport. J. Cryst. Growth 1991, 109, 17–23. [Google Scholar] [CrossRef]

- Sugawara, Y. Advances in SiC GTO development and its applications. Mater. Sci. Forum 2006, 527, 1391–1396. [Google Scholar] [CrossRef]

- Li, Z.Q.; Zhou, K.; Zhang, L.; Xu, X.L.; Li, L.H.; Li, J.T.; Dai, G. A simple multistep etched termination technique for 4H-SiC GTO thyristors. Solid State Electron. 2019, 151, 1–5. [Google Scholar] [CrossRef]

- Zeng, C.; Deng, L.F.; Li, Z.J.; Wang, J. Experimental comparison of SiC GTO and ETO for pulse power applications. J. Semicond. 2018, 39, 124017. [Google Scholar] [CrossRef]

- Zeghbroeck, B.V.; Robinson, H.; Brow, R.R. Hot Filament CVD Growth of 4H-SiC Epitaxial Layers. Mater. Sci. Forum 2018, 924, 120–123. [Google Scholar] [CrossRef]

- Li, Y.; Zhao, Z.F.; Yu, L.; Wang, Y.; Zhou, P.; Niu, Y.X.; Li, Z.H.; Chen, Y.F.; Han, P. Reduction of morphological defects in 4H-SiC epitaxial layers. J. Cryst. Growth 2019, 506, 108–113. [Google Scholar] [CrossRef]

- Uchida, K.; Hiyoshi, T.; Nishigchi, T.; Yamamoto, H.; Matsukawa, S.; Furumai, M.; Mikamura, Y. The Influence of Surface Pit Shape on 4H-SiC MOSFETs Reliability under High Temperature Bias Tests. Mater. Sci. Forum 2016, 858, 840–843. [Google Scholar] [CrossRef]

- Schoeck, J.; Schlichting, H.; Kallinger, B.; Erlbacher, T.; Rommel, M.; Bauer, A.J. Influence of Triangular Defects on the Electrical Characteristics of 4H-SiC Devices. Mater. Sci. Forum 2018, 924, 164–167. [Google Scholar] [CrossRef]

- Yakimova, R.; Hylen, A.L.; Tuominen, M.; Syvajarvi, M.; Janzen, E. Preferential Etching of SiC Crystals. Diam. Relat. Mater. 1997, 6, 1456–1458. [Google Scholar] [CrossRef]

- Cui, Y.X.; Hu, X.B.; Xie, X.J.; Xu, X.G. Threading dislocation classification for 4H-SiC substrates using the KOH etching method. CrystEngComm 2018, 20, 978–982. [Google Scholar] [CrossRef]

- Wu, F.; Wang, H.; Byrappa, S.; Raghothamachar, B.; Dudley, M.; Wu, P.; Xu, X.; Zwieback, I. Characterization and formation mechanism of six pointed star-type stacking faults in 4H-SiC. J. Electron. Mater. 2013, 42, 787–793. [Google Scholar] [CrossRef]

- Defect Characterization in 4H Silicon Carbide Bulk Crystals and Epilayers. Available online: https://pdfs.semanticscholar.org/e11d/f9fec42f5db505fbcd9e19dad04c4baca4f9.pdf (accessed on 25 October 2019).

- Cui, Y.X.; Hu, X.B.; Xie, X.J.; Wang, R.K.; Xu, X.G. Spatial variation of lattice plane bending of 4H-SiC substrates. CrystEngComm 2017, 19, 3844–3849. [Google Scholar] [CrossRef]

- Fujiwara, H.; Naruoka, H.; Konishi, M.; Hamada, K.; Katsuno, T.; Ishikawa, T.; Watanabe, Y.; Endo, T. Relationship between threading dislocation, leakage current in 4H-SiC diodes. Appl. Phys. Lett. 2012, 100, 242102. [Google Scholar] [CrossRef]

- Berechman, R.A.; Skowronski, M.; Soloviev, S.; Sandvik, P. Electrical characterization of 4H–SiC avalanche photodiodes containing threading edge, screw dislocations. J. Appl. Phys. 2010, 107, 114504. [Google Scholar] [CrossRef]

- Yun, S.B.; Bahng, W.; Kang, I.H. Correlation between Reverse Characteristics and Structural Defects in 4H-SiC PiN Diode. J. Korean Phys. Soc. 2013, 63, 1819–1823. [Google Scholar] [CrossRef]

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).