Oxide Thin-Film Transistor-Based Vertically Stacked Complementary Inverter for Logic and Photo-Sensor Operations

Abstract

1. Introduction

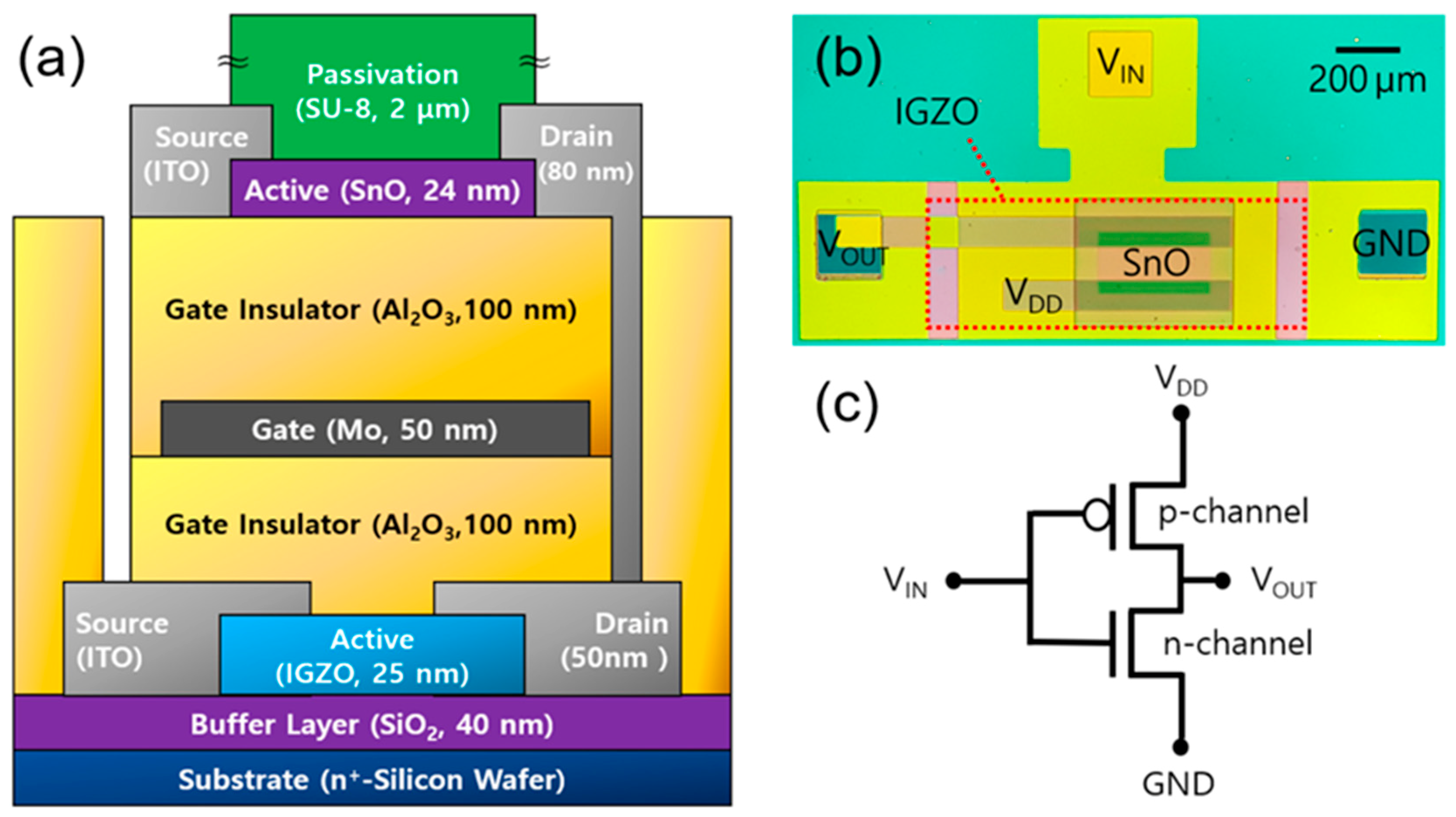

2. Experimental Procedure

3. Results and Discussion

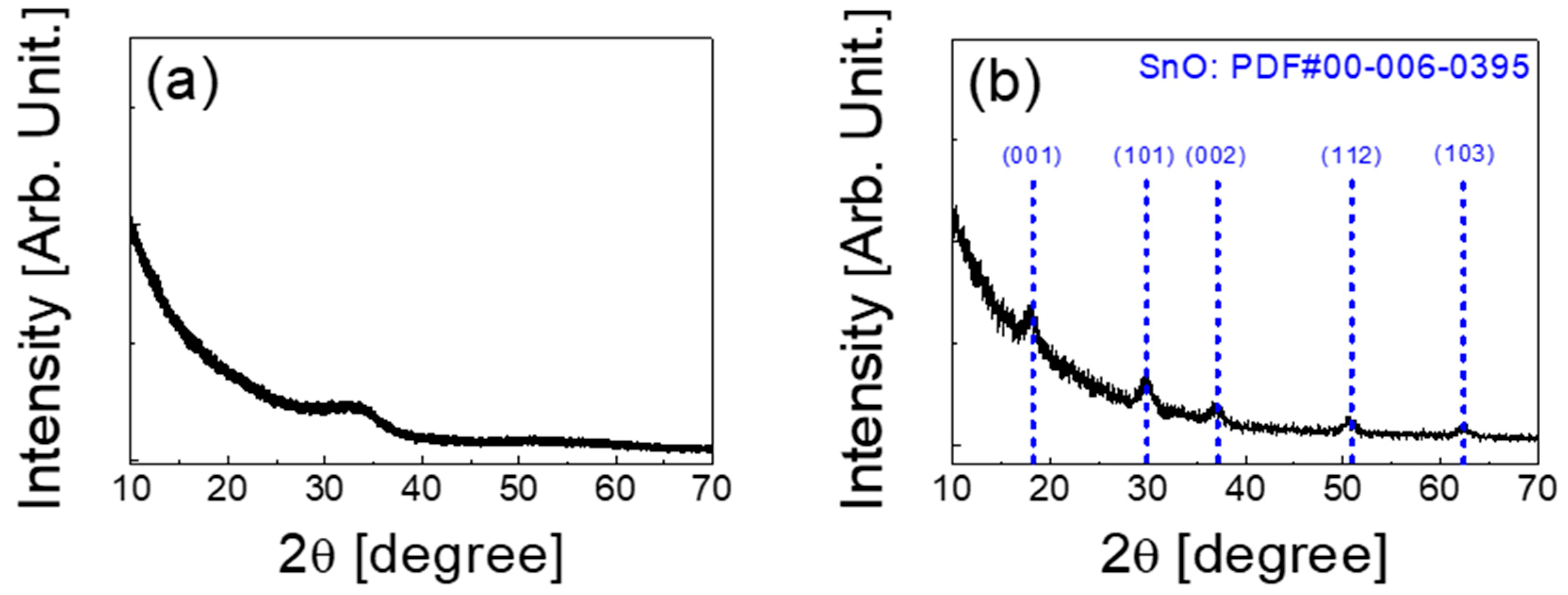

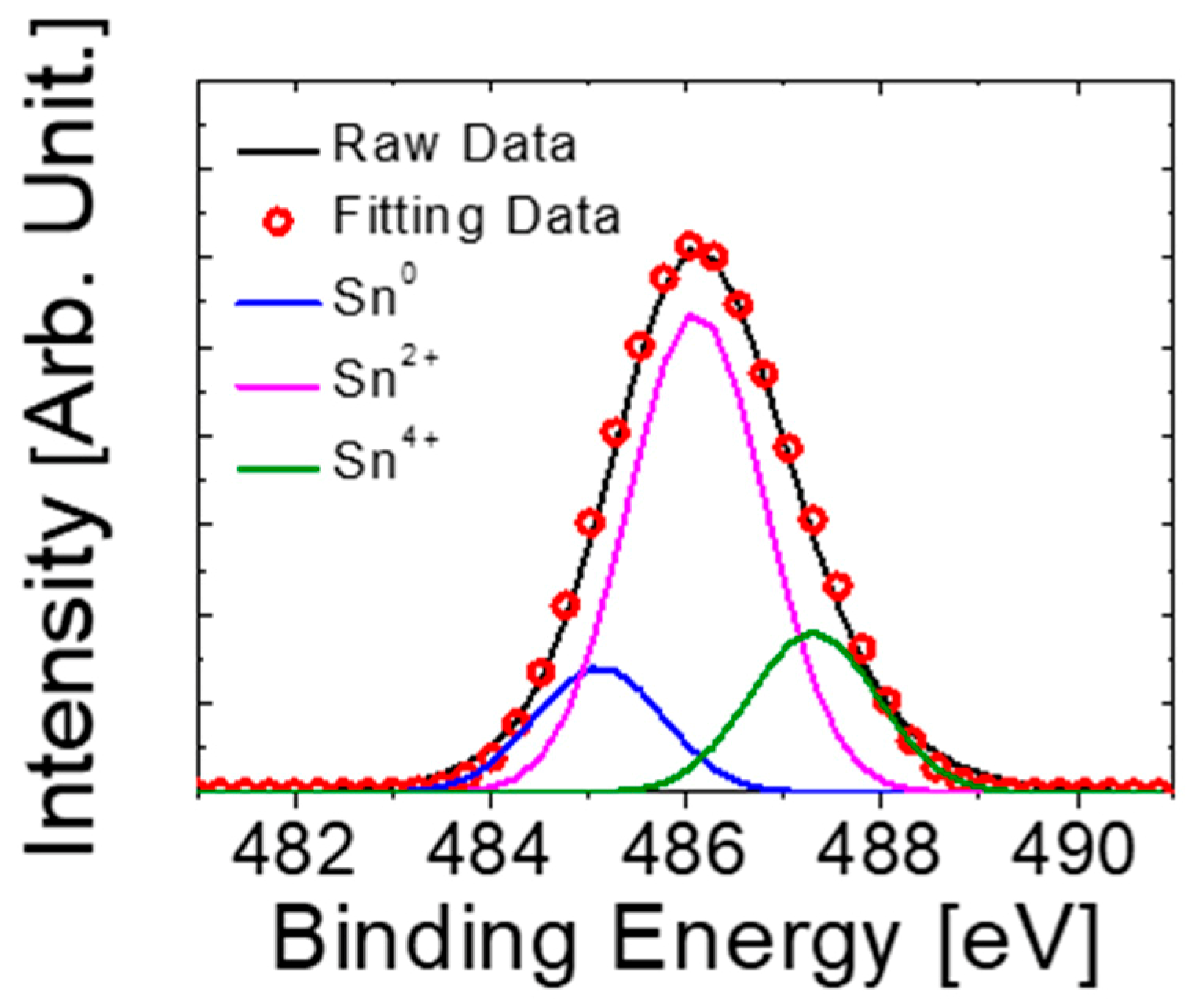

3.1. Thin Film Characterization

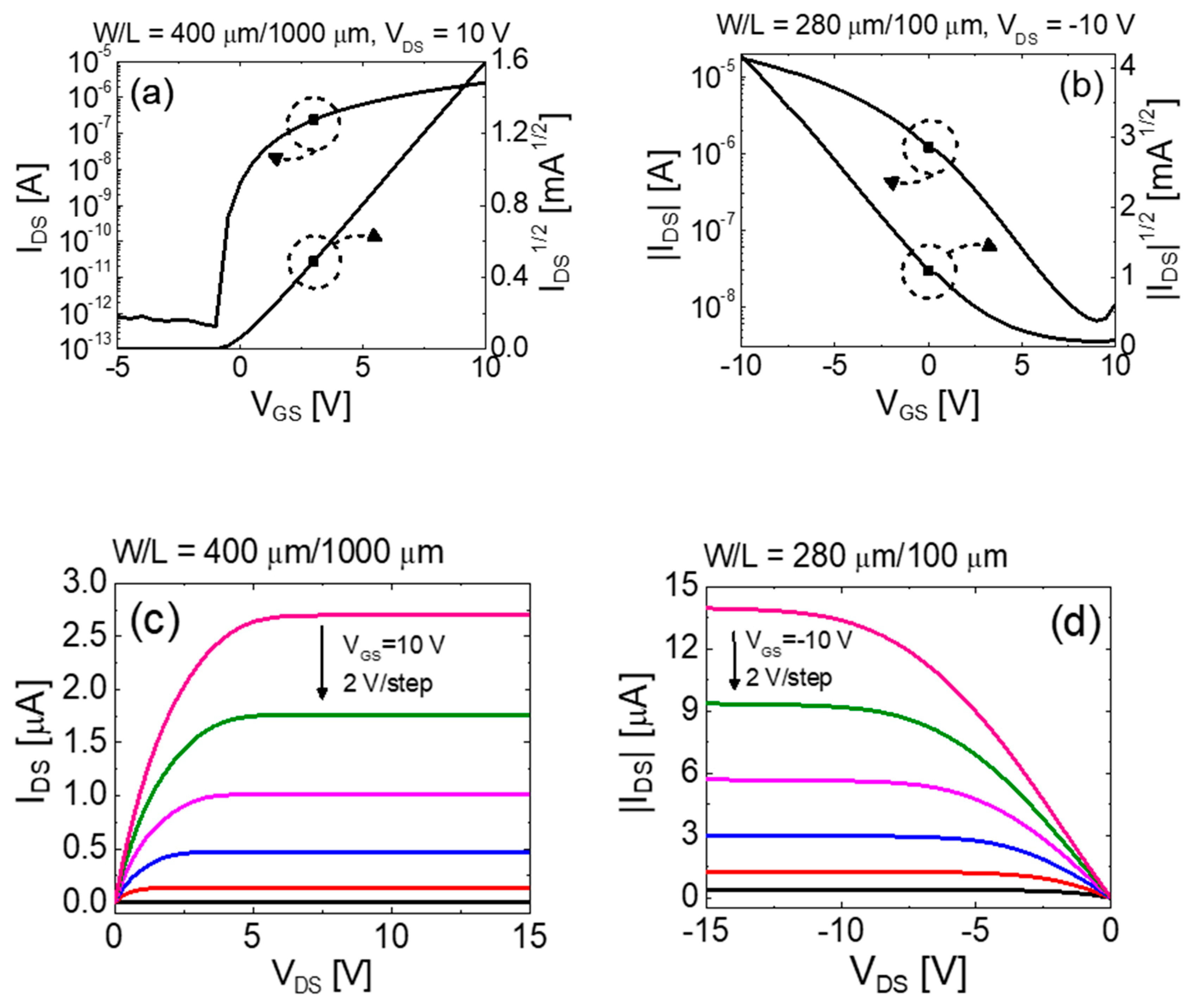

3.2. Electrical Characteristics of N-Channel IGZO and P-Channel SnO TFTs

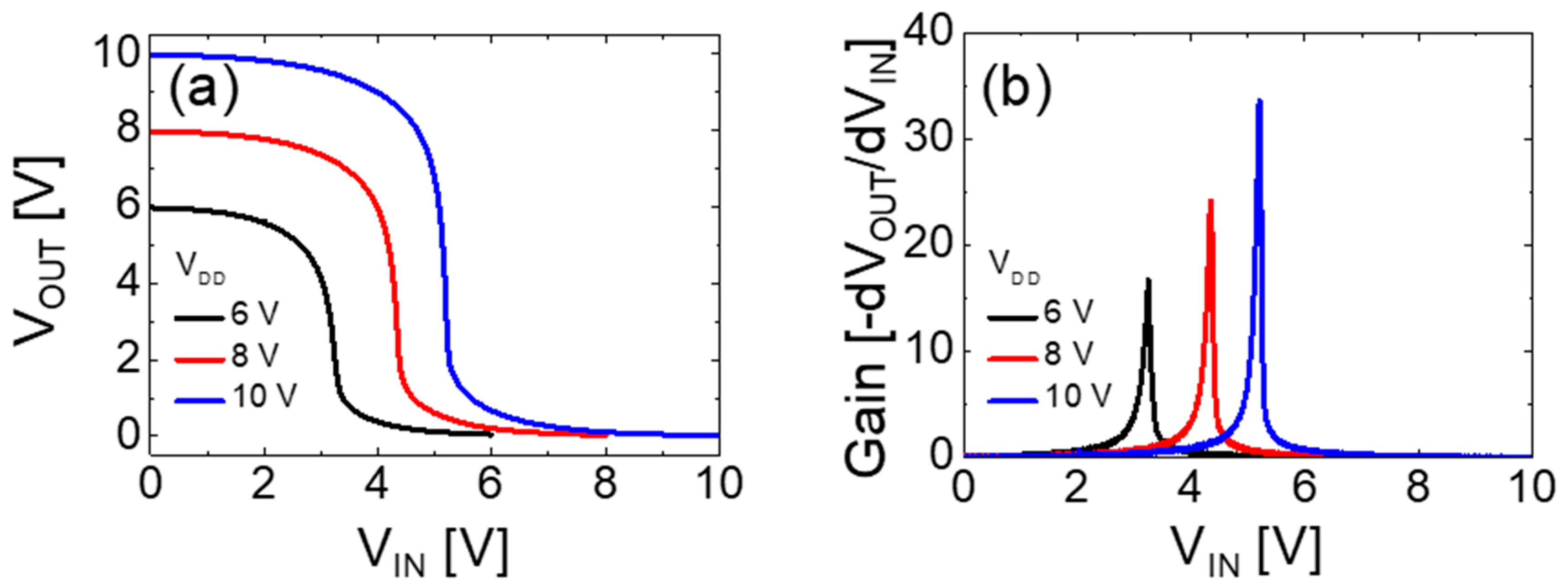

3.3. Static Performance of Vertically Stacked Complementary Inverter

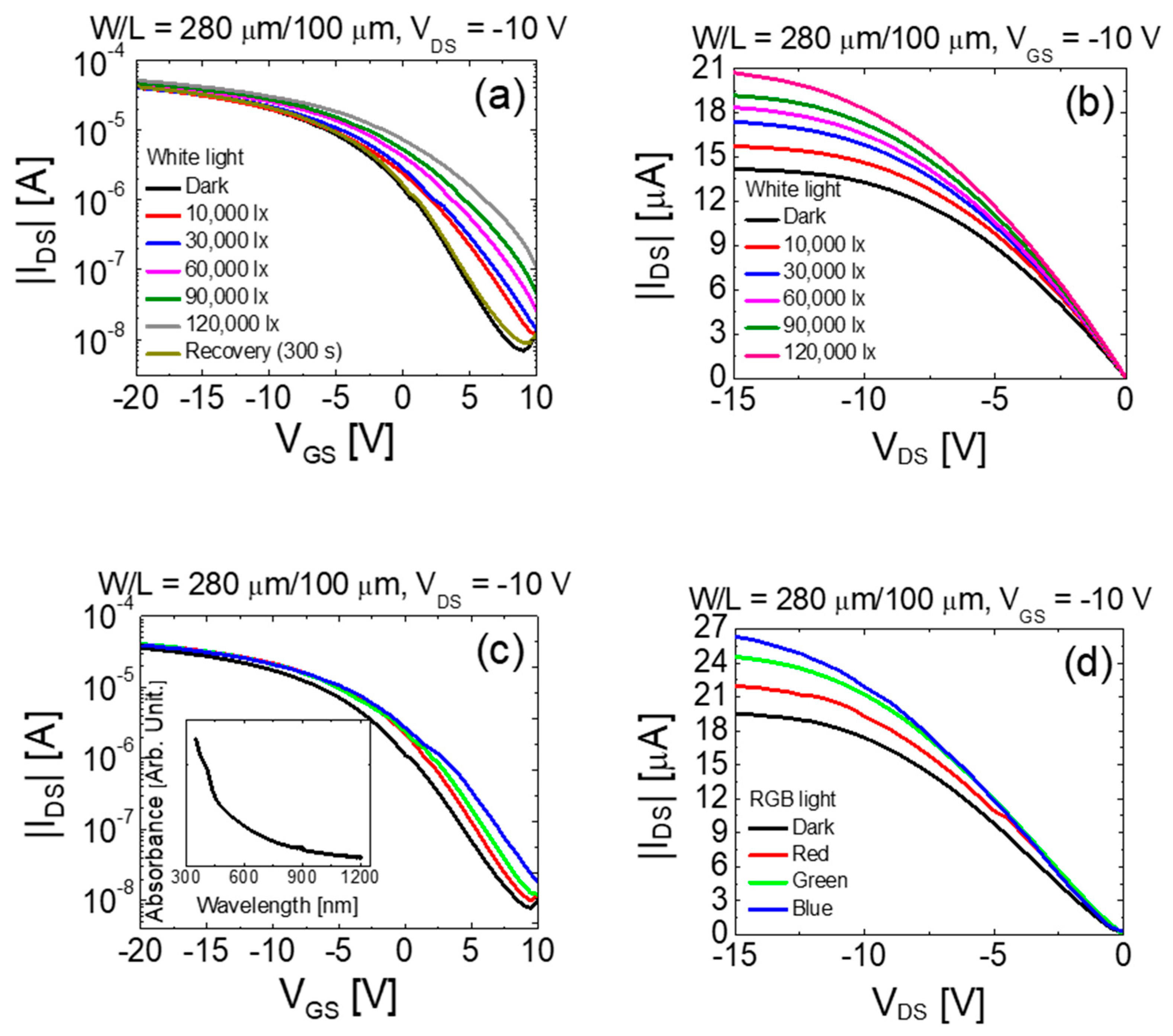

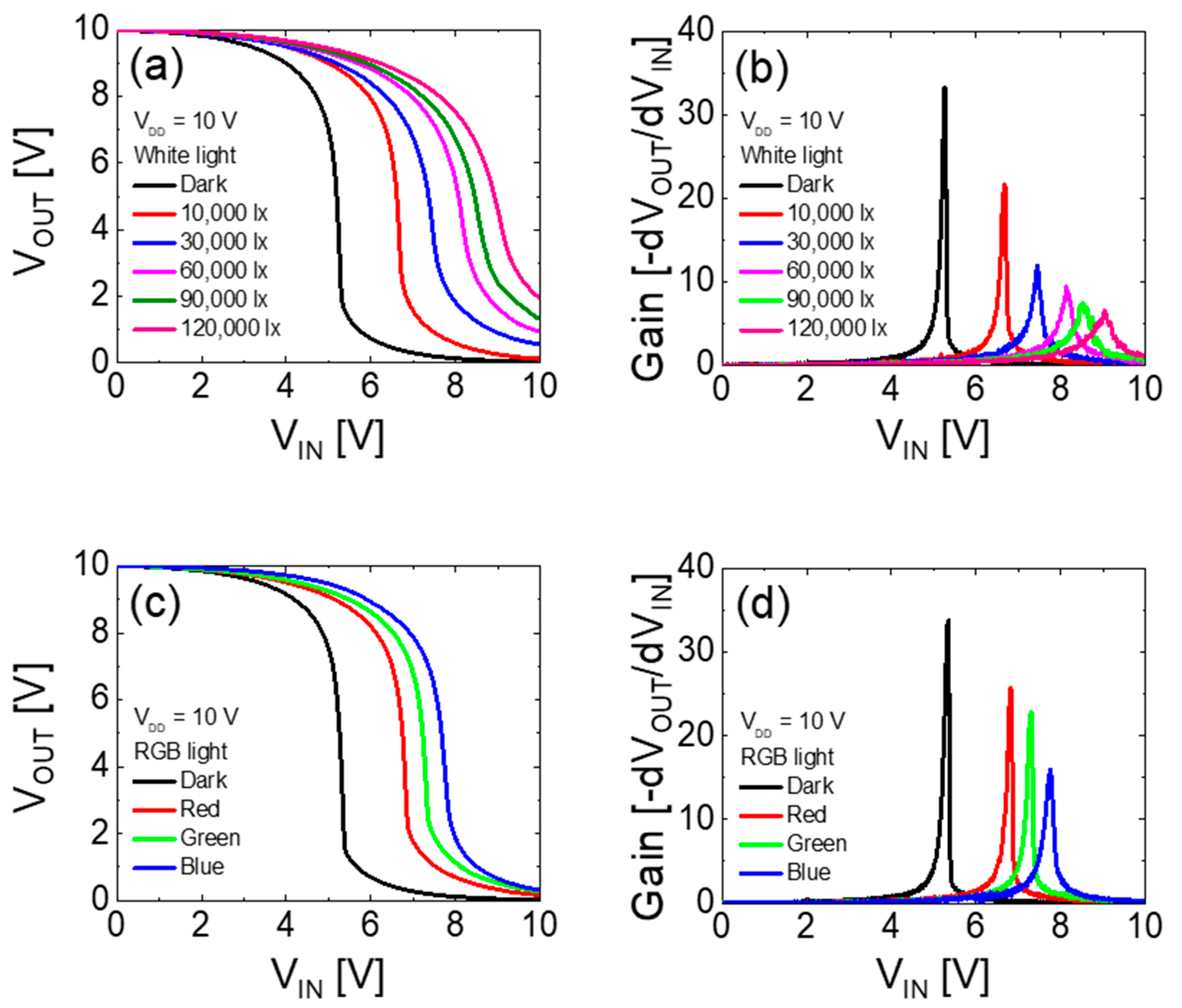

3.4. Visible Light Photoresponse of Vertically Stacked Complementary Inverter for Optoelectronic Applications

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Nomura, K.; Ohta, H.; Takagi, A.; Kamiya, T.; Hirano, M.; Hosono, H. Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors. Nature 2004, 432, 488–492. [Google Scholar] [CrossRef]

- Fortunato, E.; Barquinha, P.; Martins, R. Oxide semiconductor thin-film transistors: A review of recent advances. Adv. Mater. 2012, 24, 2945–2986. [Google Scholar] [CrossRef] [PubMed]

- Wang, Z.; Nayak, P.K.; Caraveo-Frescas, J.A.; Alshareef, H.N. Recent developments in p-type oxide semiconductor materials and devices. Adv. Mater. 2016, 28, 3831–3892. [Google Scholar] [CrossRef] [PubMed]

- Kamiya, T.; Nomura, K.; Hosono, H. Present status of amorphous In–Ga–Zn–O thin-film transistors. Sci. Technol. Adv. Mater. 2010, 11, 044305:1–044305:23. [Google Scholar] [CrossRef]

- Avis, C.; Kim, Y.; Jang, J. Amorphous tin oxide applied to solution processed thin-film transistors. Materials 2019, 12, 3341. [Google Scholar] [CrossRef]

- Yang, J.; Wang, Y.; Li, Y.; Yuan, Y.; Hu, Z.; Ma, P.; Zhou, L.; Wang, Q.; Song, A.; Xin, Q. Highly optimized complementary inverters based on p-SnO and n-InGaZnO with high uniformity. IEEE Electron Device Lett. 2018, 39, 516–519. [Google Scholar] [CrossRef]

- Li, Y.; Yang, J.; Wang, Y.; Ma, P.; Yuan, Y.; Zhang, J.; Lin, Z.; Zhou, L.; Xin, Q.; Song, A. Complementary integrated circuits based on p-type SnO and n-type IGZO thin-film transistors. IEEE Electron Device Lett. 2017, 39, 208–211. [Google Scholar] [CrossRef]

- Nayak, P.K.; Caraveo-Frescas, J.A.; Wang, Z.; Hedhili, M.N.; Wang, Q.X.; Alshareef, H.N. Thin film complementary metal oxide semiconductor (CMOS) device using a single-step deposition of the channel layer. Sci. Rep. 2014, 4, 4672. [Google Scholar] [CrossRef]

- Wang, Z.; Al-Jawhari, H.A.; Nayak, P.K.; Caraveo-Frescas, J.A.; Wei, N.; Hedhili, M.N.; Alshareef, H.N. Low temperature processed complementary metal oxide semiconductor (CMOS) device by oxidation effect from capping layer. Sci. Rep. 2015, 5, 9617. [Google Scholar] [CrossRef]

- Chiu, I.C.; Yun-Shiuan, L.; Min-Sheng, T.; Cheng, I.C. Complementary oxide-semiconductor-based circuits with n-channel ZnO and p-channel SnO thin-film transistors. IEEE Electron Device Lett. 2014, 35, 1263–1265. [Google Scholar] [CrossRef]

- Li, Y.-S.; He, J.-C.; Hsu, S.-M.; Lee, C.-C.; Su, D.-Y.; Tsai, F.-Y.; Cheng, I.C. Flexible complementary oxide-semiconductor-based circuits employing n-channel ZnO and p-channel SnO thin-film transistors. IEEE Electron Device Lett. 2016, 37, 46–49. [Google Scholar] [CrossRef]

- Zhang, J.; Yang, J.; Li, Y.; Wilson, J.; Ma, X.; Xin, Q.; Song, A. High performance complementary circuits based on p-SnO and n-IGZO thin-film transistors. Materials 2017, 10, 319. [Google Scholar] [CrossRef] [PubMed]

- Dhananjay; Chu, C.-W.; Ou, C.-W.; Wu, M.-C.; Ho, Z.-Y.; Ho, K.-C.; Lee, S.-W. Complementary inverter circuits based on p-SnO2 and n-In2O3 thin film transistors. Appl. Phys. Lett. 2008, 92, 232103. [Google Scholar] [CrossRef]

- Lee, C.T.; Chen, C.C.; Lee, H.Y. Three dimensional-stacked complementary thin-film transistors using n-type Al: ZnO and p-type NiO thin-film transistors. Sci. Rep. 2018, 8, 3968. [Google Scholar] [CrossRef]

- Dindar, A.; Kim, J.B.; Fuentes-Hernandez, C.; Kippelen, B. Metal-oxide complementary inverters with a vertical geometry fabricated on flexible substrates. Appl. Phys. Lett. 2011, 99, 172104. [Google Scholar] [CrossRef]

- Baek, C.; Seo, S.M. Vertical organic inverter with stacked pentacene thin film transistors. Appl. Phys. Lett. 2009, 94, 107. [Google Scholar] [CrossRef]

- Kim, J.B.; Fuentes-Hernandez, C.; Hwang, D.K.; Potscavage, W.J., Jr.; Cheun, H.; Kippelen, B. Vertically stacked hybrid organic–inorganic complementary inverters with low operating voltage on flexible substrates. Org. Electron. 2011, 12, 45–50. [Google Scholar] [CrossRef]

- Lin, X.; Zhang, S.; Wu, X.; Chan, M. Local clustering 3-D stacked CMOS technology for interconnect loading reduction. IEEE Trans. Electron Devices 2006, 53, 1405–1410. [Google Scholar] [CrossRef]

- Nomura, K.; Aoki, T.; Nakamura, K.; Kamiya, T.; Nakanishi, T.; Hasegawa, T.; Kimura, M.; Kawase, T.; Hirano, M.; Hosono, H. Three-dimensionally stacked flexible integrated circuit: Amorphous oxide/polymer hybrid complementary inverter using n-type a-In–Ga–Zn–O and p-type poly-(9, 9-dioctylfluorene-co-bithiophene) thin-film transistors. Appl. Phys. Lett. 2010, 96, 263509. [Google Scholar] [CrossRef]

- Kim, J.B.; Fuentes-Hernandez, C.; Hwang, D.K.; Tiwari, S.P.; Potscavage, W.J., Jr.; Kippelen, B. Vertically stacked complementary inverters with solution-processed organic semiconductors. Org. Electron. 2011, 12, 1132–1136. [Google Scholar] [CrossRef]

- Goutaland, F.; Marin, E.; Michalon, J.Y.; Boukenter, A. Growth of silver nanoparticles of variable and controlled diameter in silica-based and soda-lime glasses by simultaneous continuous ultraviolet irradiation and heat treatment. Appl. Phys. Lett. 2009, 94, 181108. [Google Scholar] [CrossRef]

- Tak, Y.J.; Du Ahn, B.; Park, S.P.; Kim, S.J.; Song, A.R.; Chung, K.B.; Kim, H.J. Activation of sputter-processed indium–gallium–zinc oxide films by simultaneous ultraviolet and thermal treatments. Sci. Rep. 2016, 6, 21869. [Google Scholar] [CrossRef] [PubMed]

- Tak, Y.J.; Yoon, D.H.; Yoon, S.; Choi, U.H.; Sabri, M.M.; Ahn, B.D.; Kim, H.J. Enhanced electrical characteristics and stability via simultaneous ultraviolet and thermal treatment of passivated amorphous In–Ga–Zn–O thin-film transistors. ACS Appl. Mater. Interfaces 2014, 6, 6399–6405. [Google Scholar] [CrossRef]

- Su, B.Y.; Chu, S.Y.; Juang, Y.D.; Chen, H.C. High-performance low-temperature solution-processed InGaZnO thin-film transistors via ultraviolet-ozone photo-annealing. Appl. Phys. Lett. 2013, 102, 192101. [Google Scholar] [CrossRef]

- Han, Y.J.; Choi, Y.J.; Cho, I.T.; Jin, S.H.; Lee, J.H.; Kwon, H.I. Improvement of long-term durability and bias stress stability in p-type SnO thin-film transistors using a SU-8 passivation layer. IEEE Electron Device Lett. 2014, 35, 1260–1262. [Google Scholar] [CrossRef]

- Li, Y.; Liu, Z.; Jiang, K.; Hu, X. H2 annealing effect on the structural and electrical properties of amorphous InGaZnO films for thin film transistors. J. Non-Cryst. Solids 2013, 378, 50–54. [Google Scholar] [CrossRef]

- Ogo, Y.; Hiramatsu, H.; Nomura, K.; Yanagi, H.; Kamiya, T.; Hirano, M.; Hosono, H. p-channel thin-film transistor using p-type oxide semiconductor, SnO. Appl. Phys. Lett. 2008, 93, 032113. [Google Scholar] [CrossRef]

- Fortunato, E.; Barros, R.; Barquinha, P.; Figueiredo, V.; Park, S.H.K.; Hwang, C.S.; Martins, R. Transparent p-type SnO x thin film transistors produced by reactive rf magnetron sputtering followed by low temperature annealing. Appl. Phys. Lett. 2010, 97, 052105. [Google Scholar] [CrossRef]

- Patterson, A.L. The Scherrer formula for X-ray particle size determination. Phys. Rev. 1939, 56, 978. [Google Scholar] [CrossRef]

- Szuber, J.; Czempik, G.; Larciprete, R.; Koziej, D.; Adamowicz, B. XPS study of the L-CVD deposited SnO2 thin films exposed to oxygen and hydrogen. Thin Solid Films 2001, 391, 198–203. [Google Scholar] [CrossRef]

- Ok, K.C.; Oh, S.; Jeong, H.J.; Bae, J.U.; Park, J.S. Effect of alumina buffers on the stability of top-gate amorphous InGaZnO thin-film transistors on flexible substrates. IEEE Electron Device Lett. 2015, 36, 917–919. [Google Scholar] [CrossRef]

- Luo, H.; Liang, L.Y.; Liu, Q.; Cao, H.T. Magnetron-sputtered SnO thin films for p-type and ambipolar TFT applications. ECS J. Solid State Sci. Technol. 2014, 3, Q3091–Q3094. [Google Scholar] [CrossRef]

- Sedra, A.S.; Smith, K.C. Microelectronic Circuits; Oxford University Press: New York, NY, USA, 1998. [Google Scholar]

- Parida, O.P.; Bhat, N. Characterization of optical properties of SU-8 and fabrication of optical components. In Proceedings of the International Conference on Optics and Photonics, Chandigarh, India, 30 October–1 November 2009. [Google Scholar]

- Kimura, M.; Kamada, Y.; Fujita, S.; Hiramatsu, T.; Matsuda, T.; Furuta, M.; Hirao, T. Mechanism analysis of photoleakage current in ZnO thin-film transistors using device simulation. Appl. Phys. Lett. 2010, 97, 163503. [Google Scholar] [CrossRef]

- Lee, J.H.; Choi, Y.J.; Jeong, C.Y.; Jung, D.K.; Ham, S.; Kwon, H.I. Electrical instability of p-channel SnO thin-film transistors under light illumination. IEEE Electron Device Lett. 2016, 37, 295–298. [Google Scholar] [CrossRef]

- Oh, M.S.; Choi, W.; Lee, K.; Hwang, D.K.; Im, S. Flexible high gain complementary inverter using n-Zn O and p-pentacene channels on polyethersulfone substrate. Appl. Phys. Lett. 2008, 93, 033510-1–033510-3. [Google Scholar] [CrossRef]

- Fujisaki, Y.; Nakajima, Y.; Kumaki, D.; Yamamoto, T.; Tokito, S.; Kono, T.; Nishida, J.; Yamashita, Y. Air-stable n-type organic thin-film transistor array and high gain complementary inverter on flexible substrate. Appl. Phys. Lett. 2010, 97, 209, 133303-1–133303-3. [Google Scholar] [CrossRef]

| VDD [V] | VM [V] | AV [V] | NML [V] | NMH [V] |

|---|---|---|---|---|

| 6 | 3.15 | 16.7 | 1.72 | 1.70 |

| 8 | 4.26 | 24.1 | 2.55 | 2.30 |

| 10 | 5.18 | 33.6 | 3.16 | 3.13 |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Joo, H.-J.; Shin, M.-G.; Jung, H.-S.; Cha, H.-S.; Nam, D.; Kwon, H.-I. Oxide Thin-Film Transistor-Based Vertically Stacked Complementary Inverter for Logic and Photo-Sensor Operations. Materials 2019, 12, 3815. https://doi.org/10.3390/ma12233815

Joo H-J, Shin M-G, Jung H-S, Cha H-S, Nam D, Kwon H-I. Oxide Thin-Film Transistor-Based Vertically Stacked Complementary Inverter for Logic and Photo-Sensor Operations. Materials. 2019; 12(23):3815. https://doi.org/10.3390/ma12233815

Chicago/Turabian StyleJoo, Hyo-Jun, Min-Gyu Shin, Hwan-Seok Jung, Hyun-Seok Cha, Donguk Nam, and Hyuck-In Kwon. 2019. "Oxide Thin-Film Transistor-Based Vertically Stacked Complementary Inverter for Logic and Photo-Sensor Operations" Materials 12, no. 23: 3815. https://doi.org/10.3390/ma12233815

APA StyleJoo, H.-J., Shin, M.-G., Jung, H.-S., Cha, H.-S., Nam, D., & Kwon, H.-I. (2019). Oxide Thin-Film Transistor-Based Vertically Stacked Complementary Inverter for Logic and Photo-Sensor Operations. Materials, 12(23), 3815. https://doi.org/10.3390/ma12233815