Study of Resistive-Type Superconducting Fault Current Limiters for a Hybrid High Voltage Direct Current System

Abstract

:1. Introduction

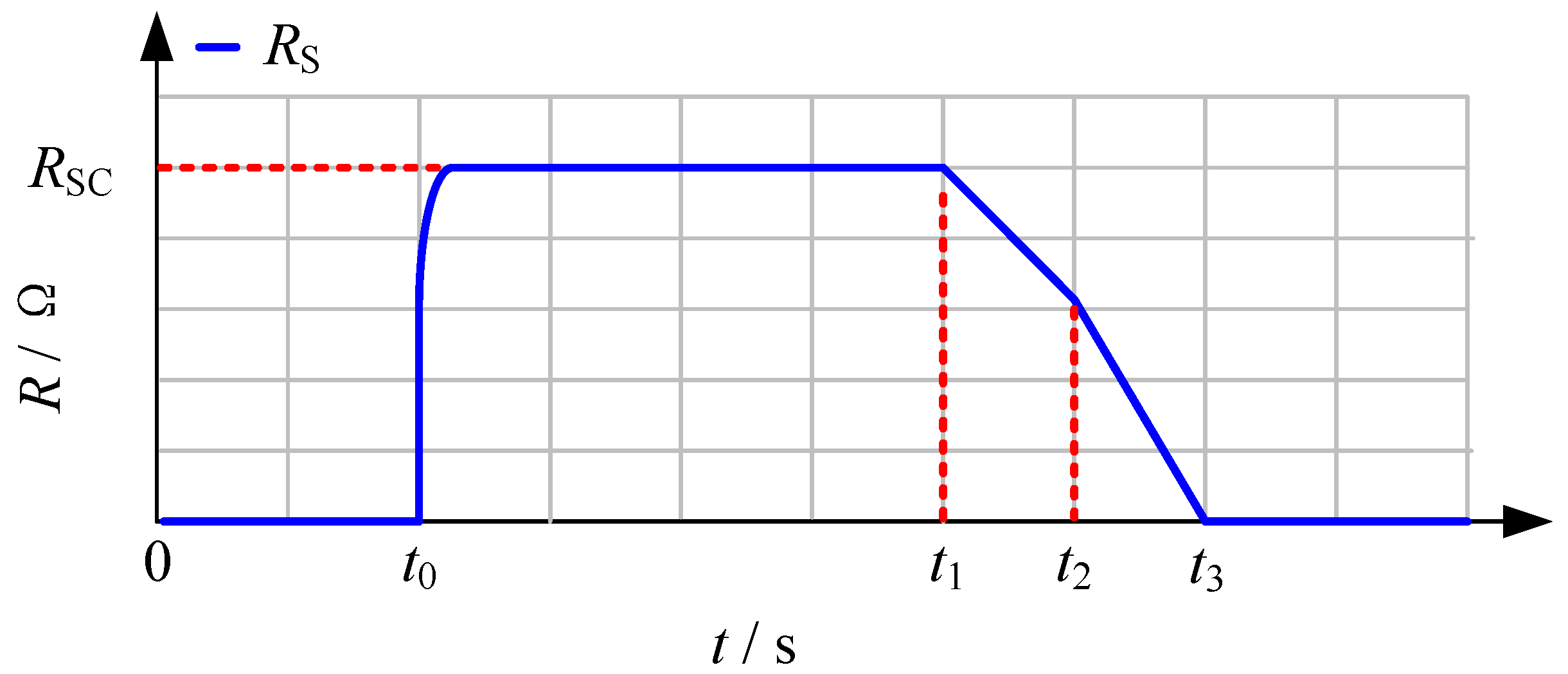

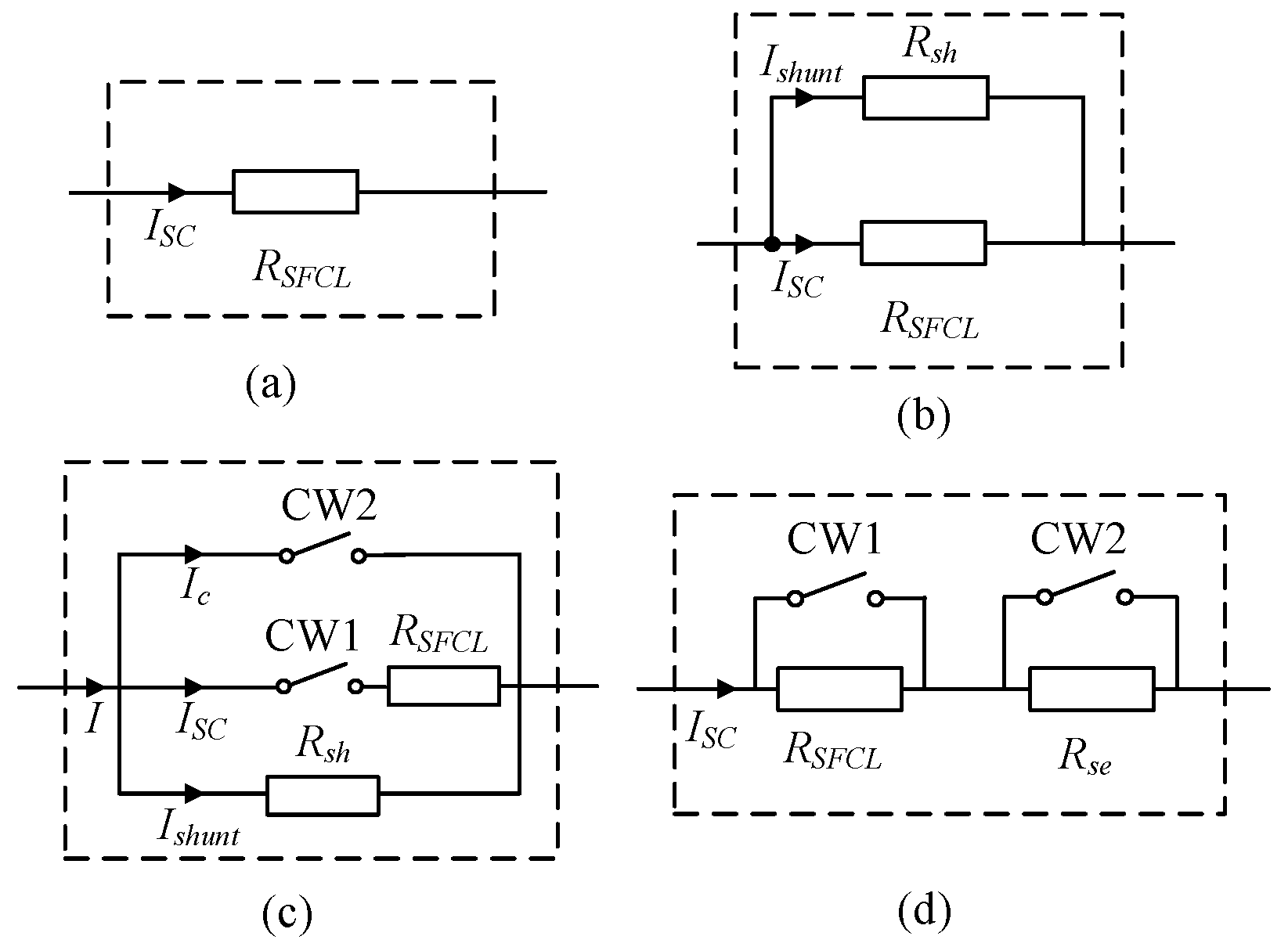

2. Theoretical Analysis

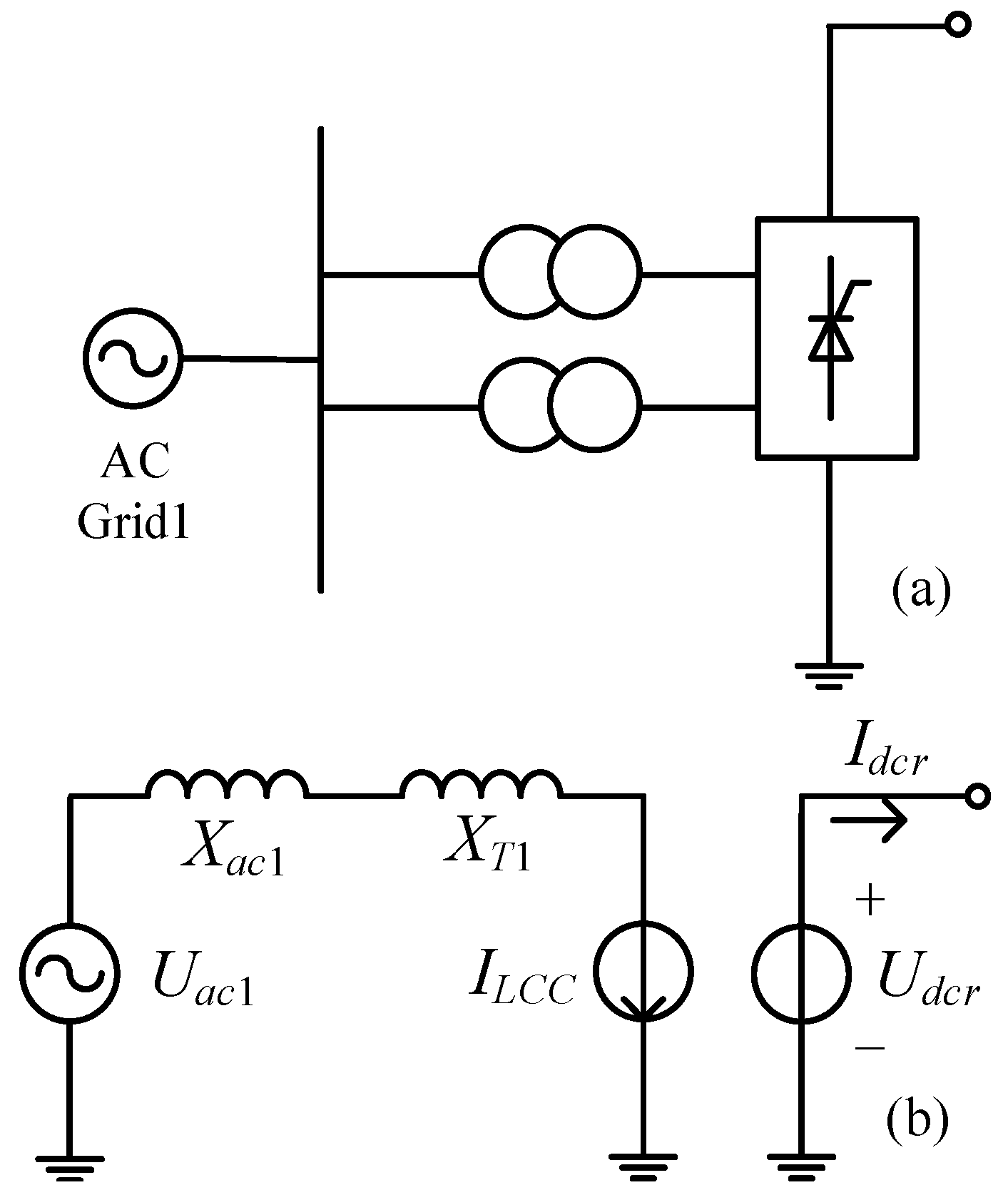

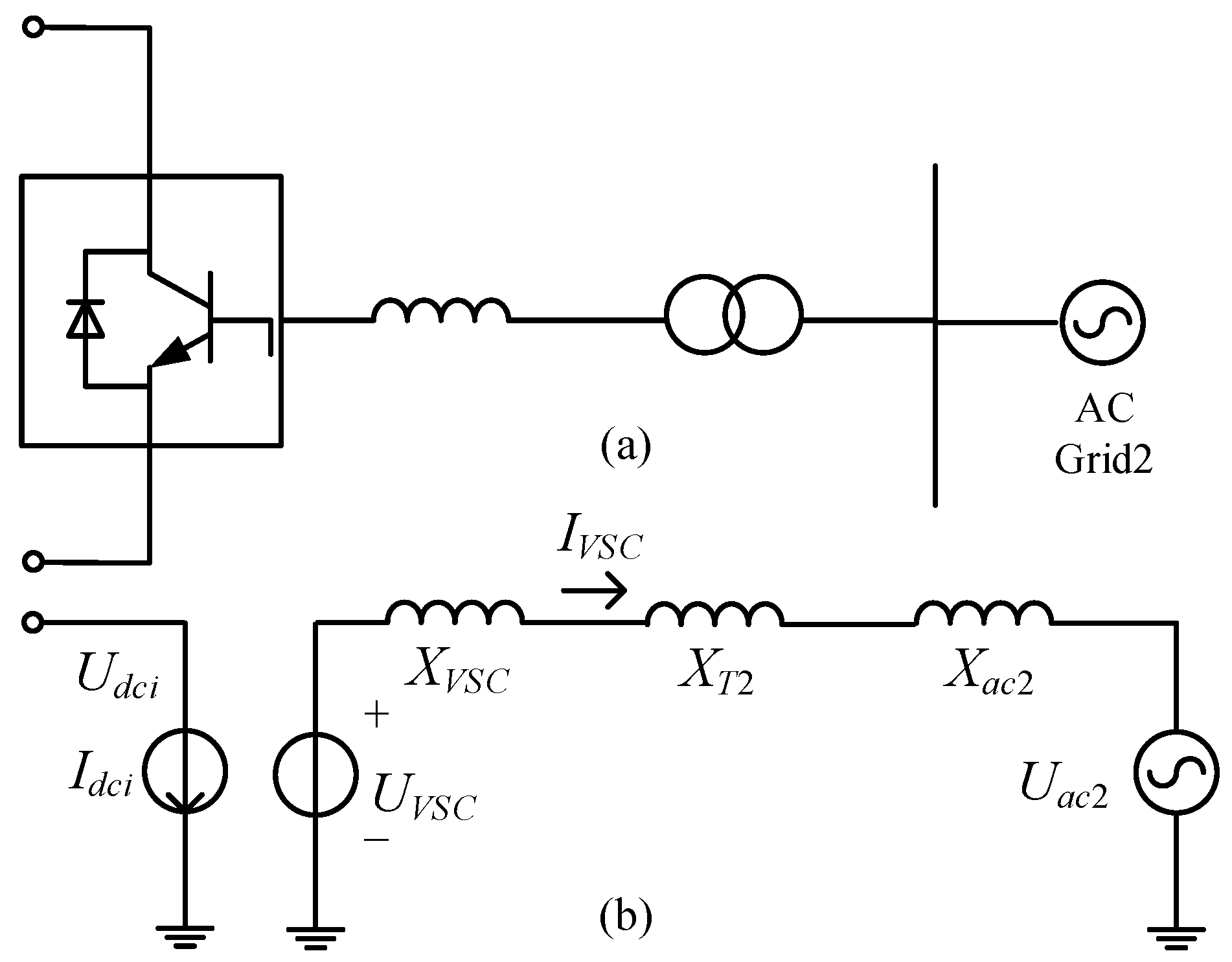

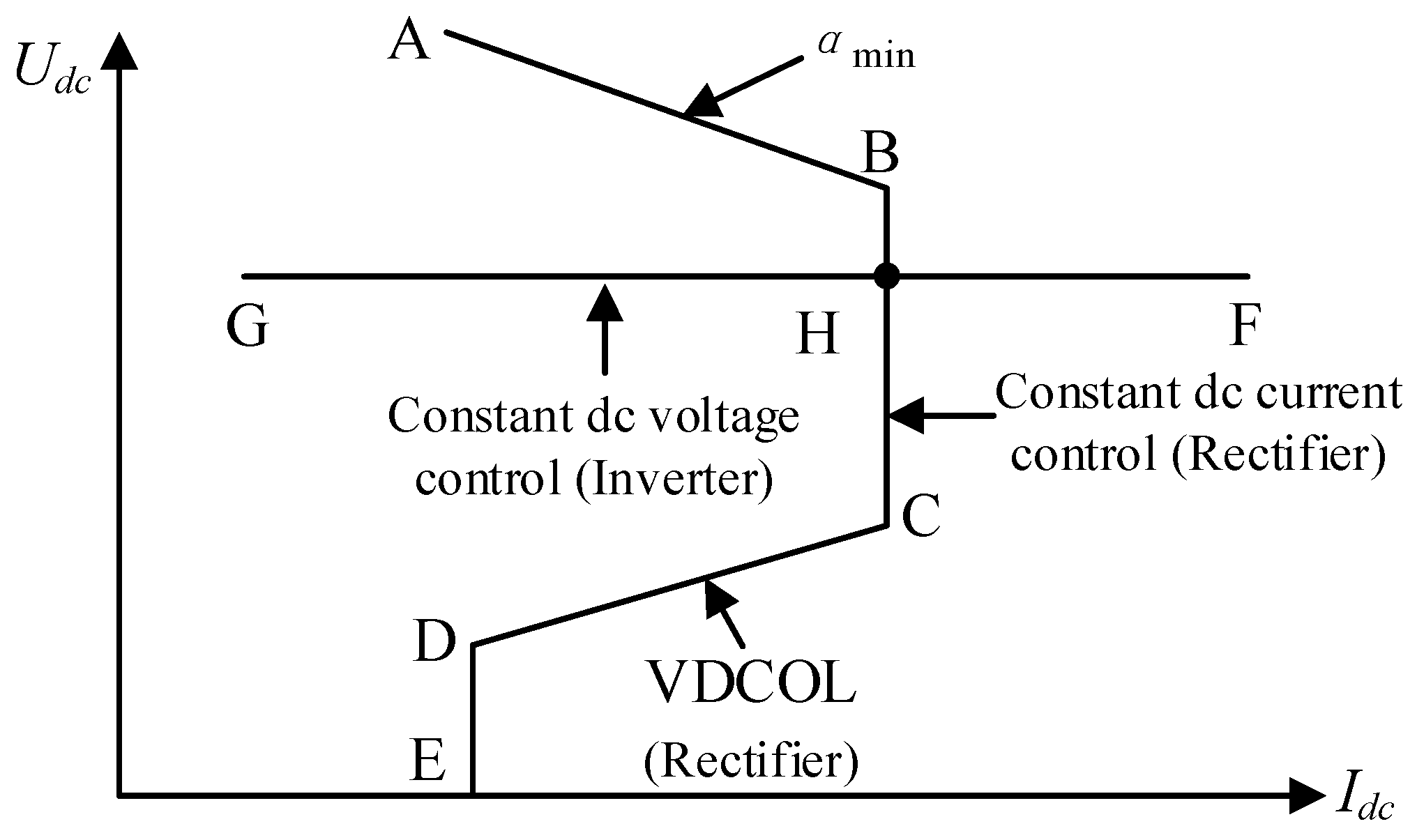

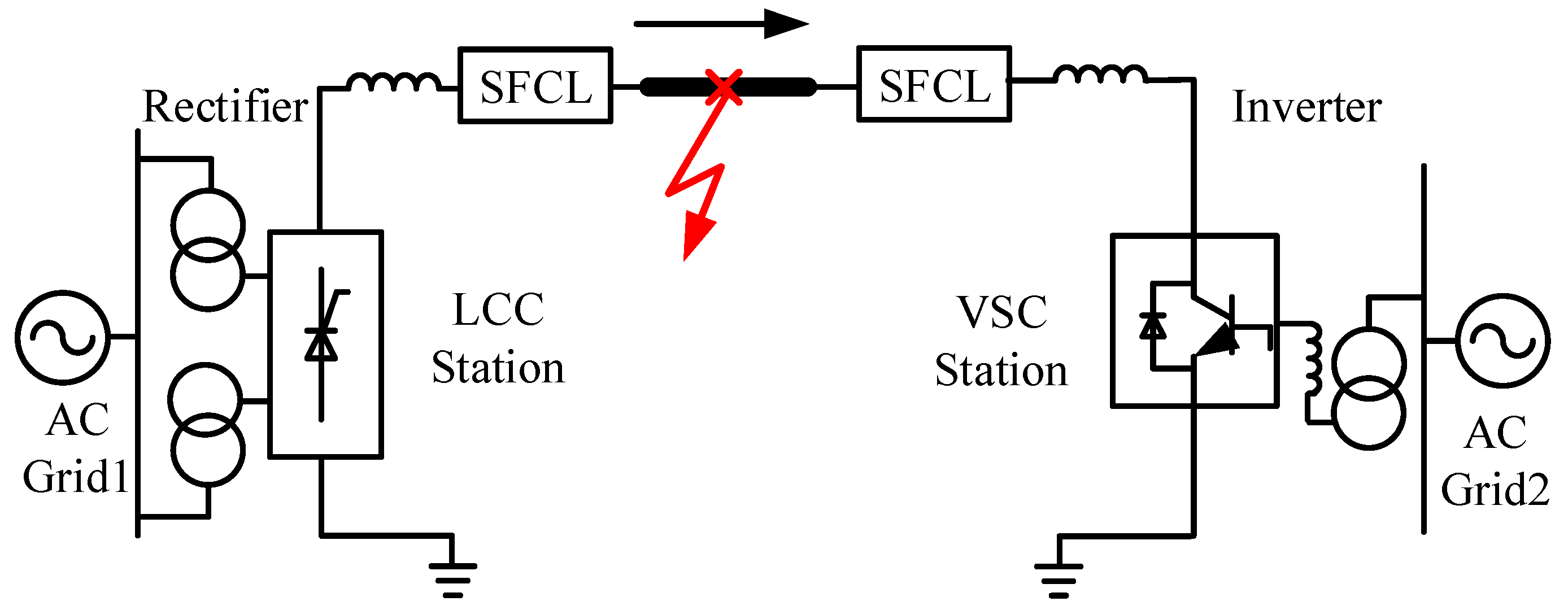

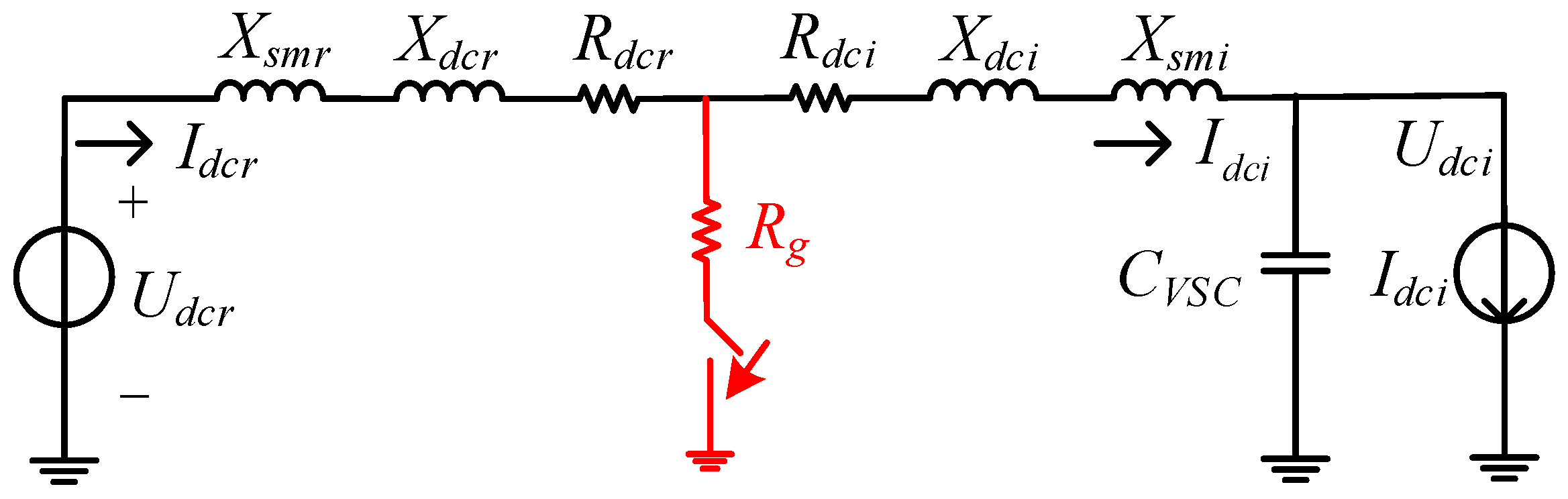

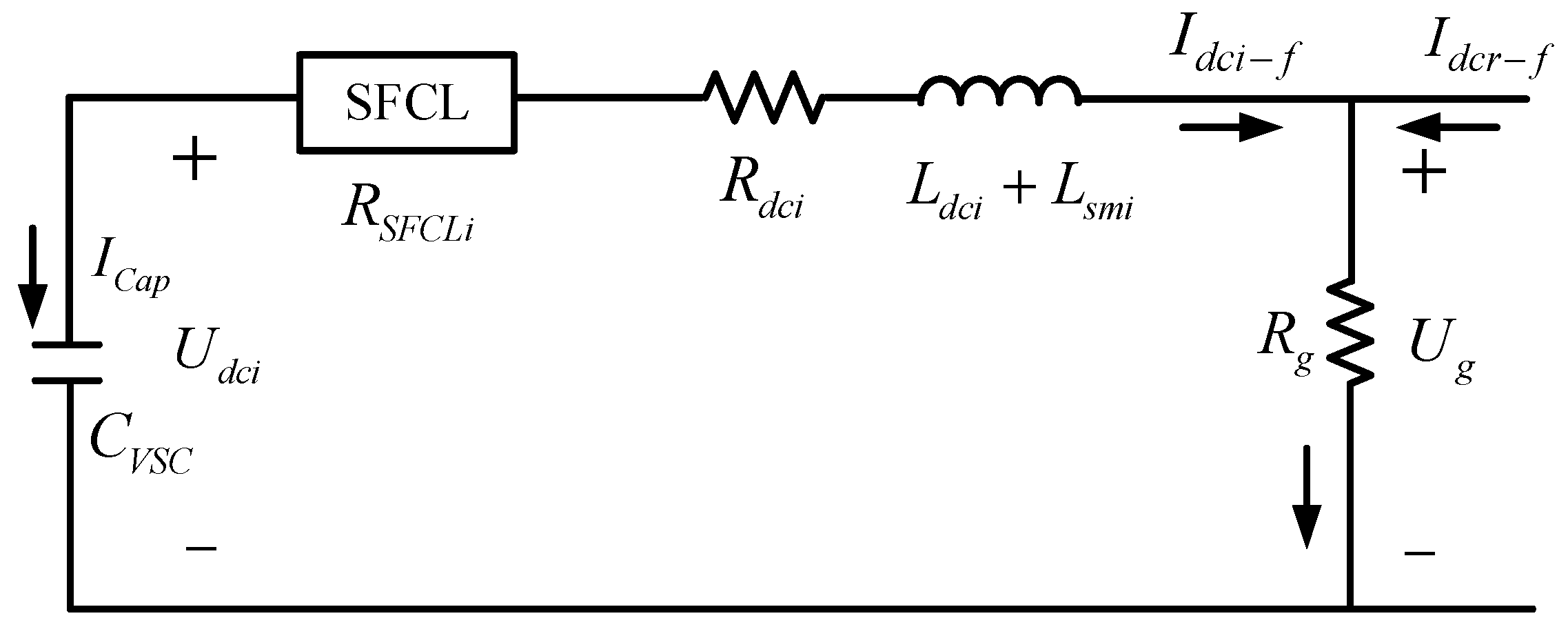

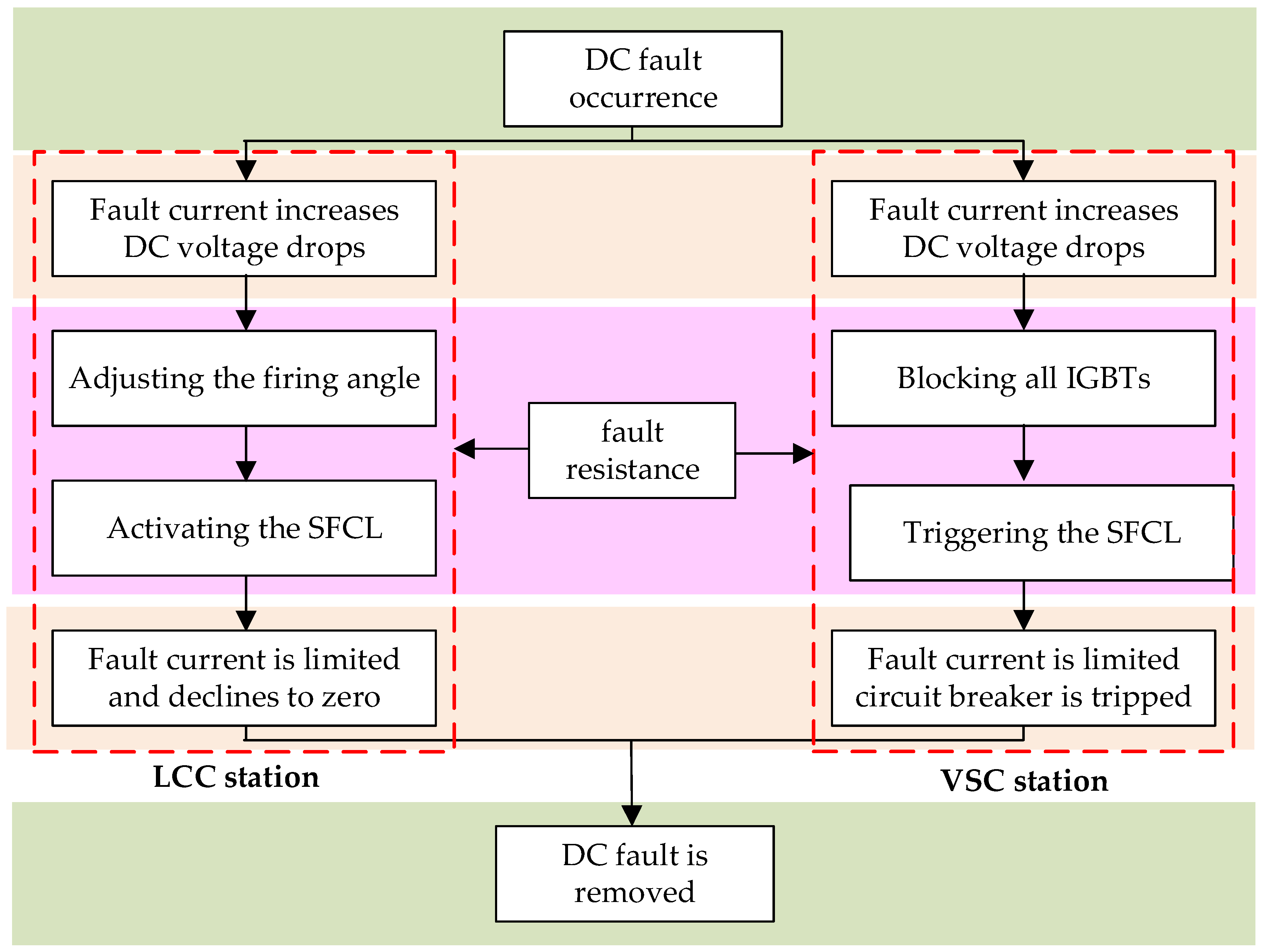

2.1. Analytical Model of the Hybrid HVDC Including the SFCLs

2.2. Impacts of the SFCLs on the DC Fault Currents

3. Simulation Study

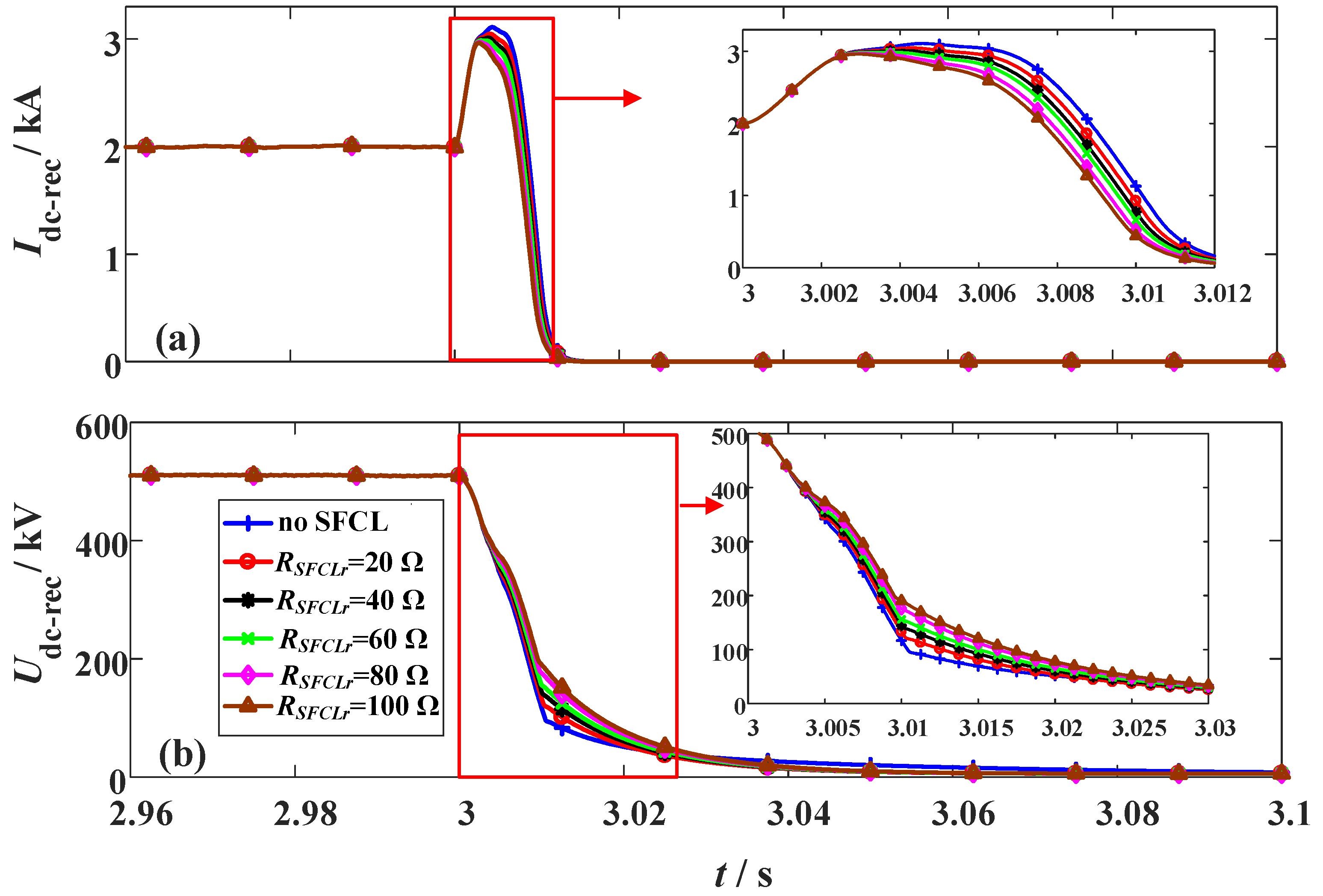

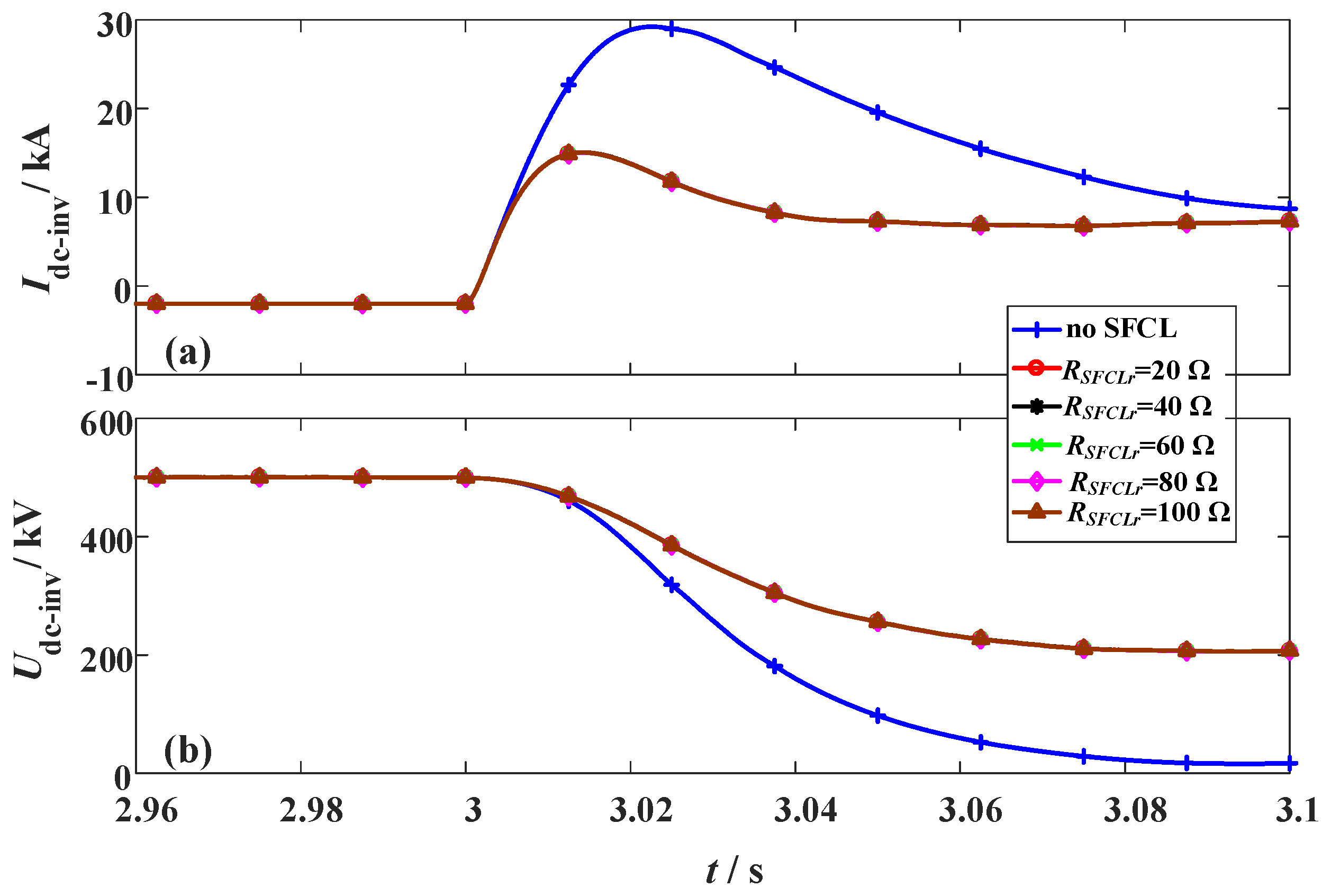

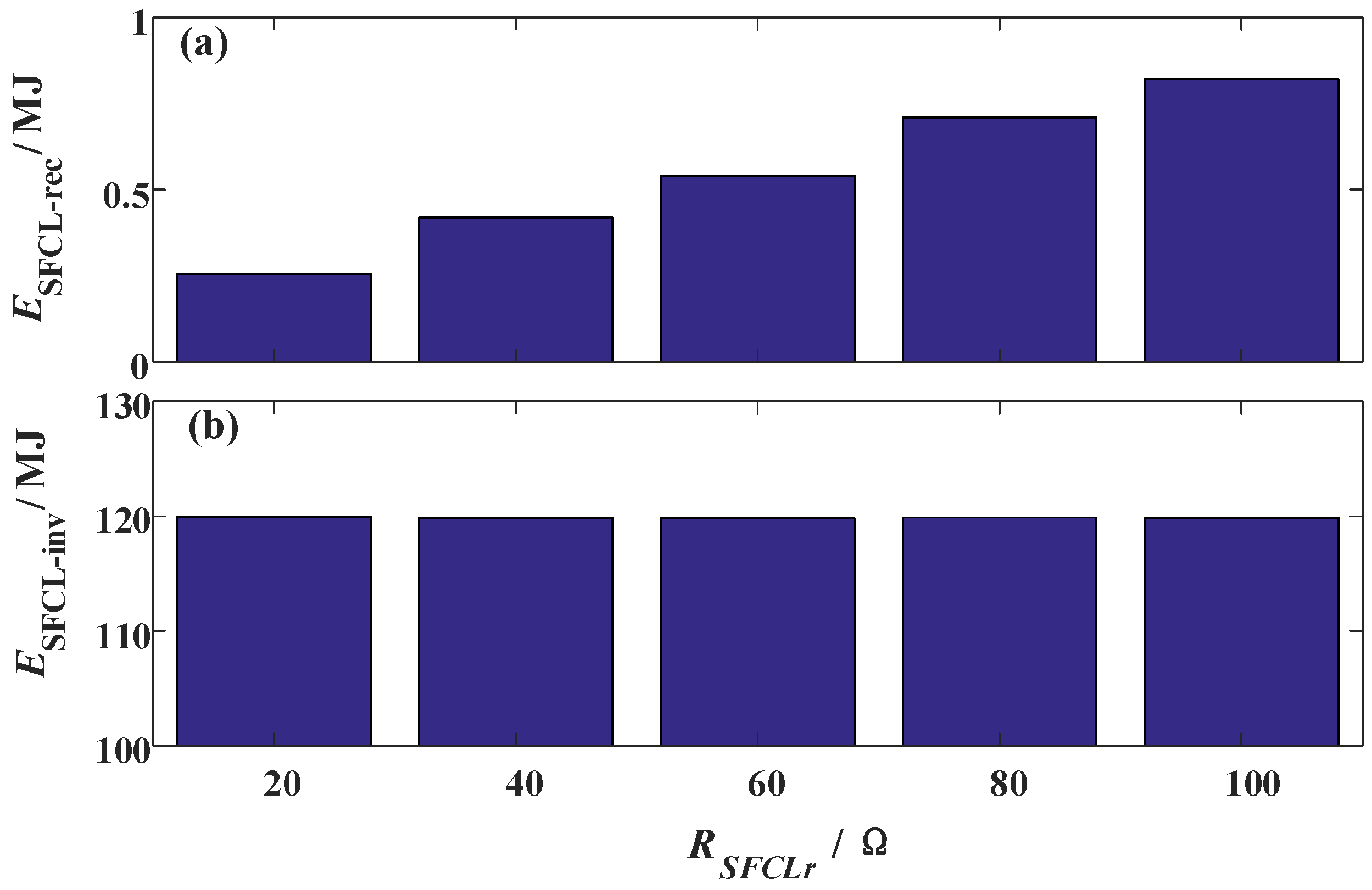

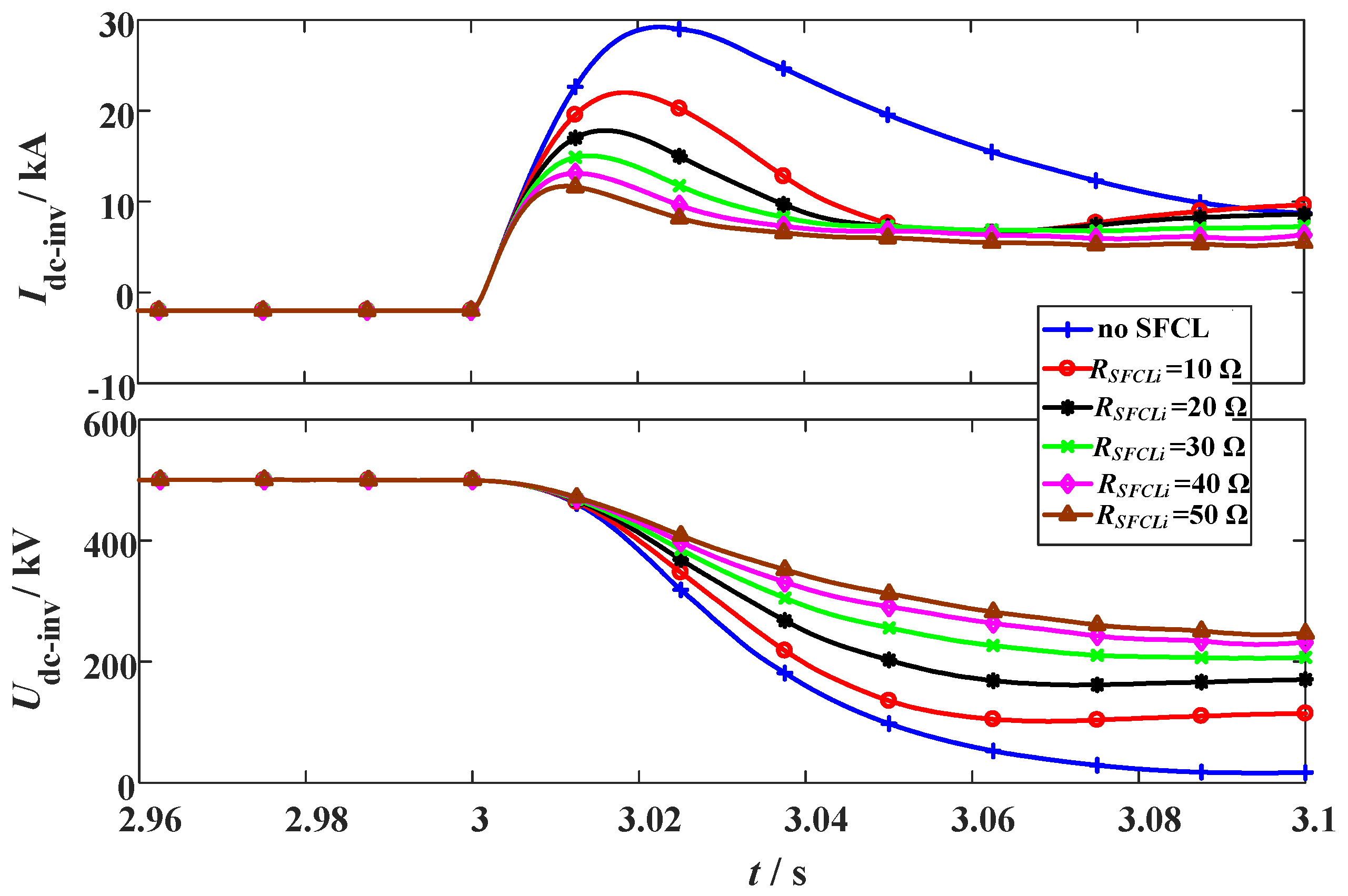

3.1. Changing the SFCL Resistance in the LCC Station

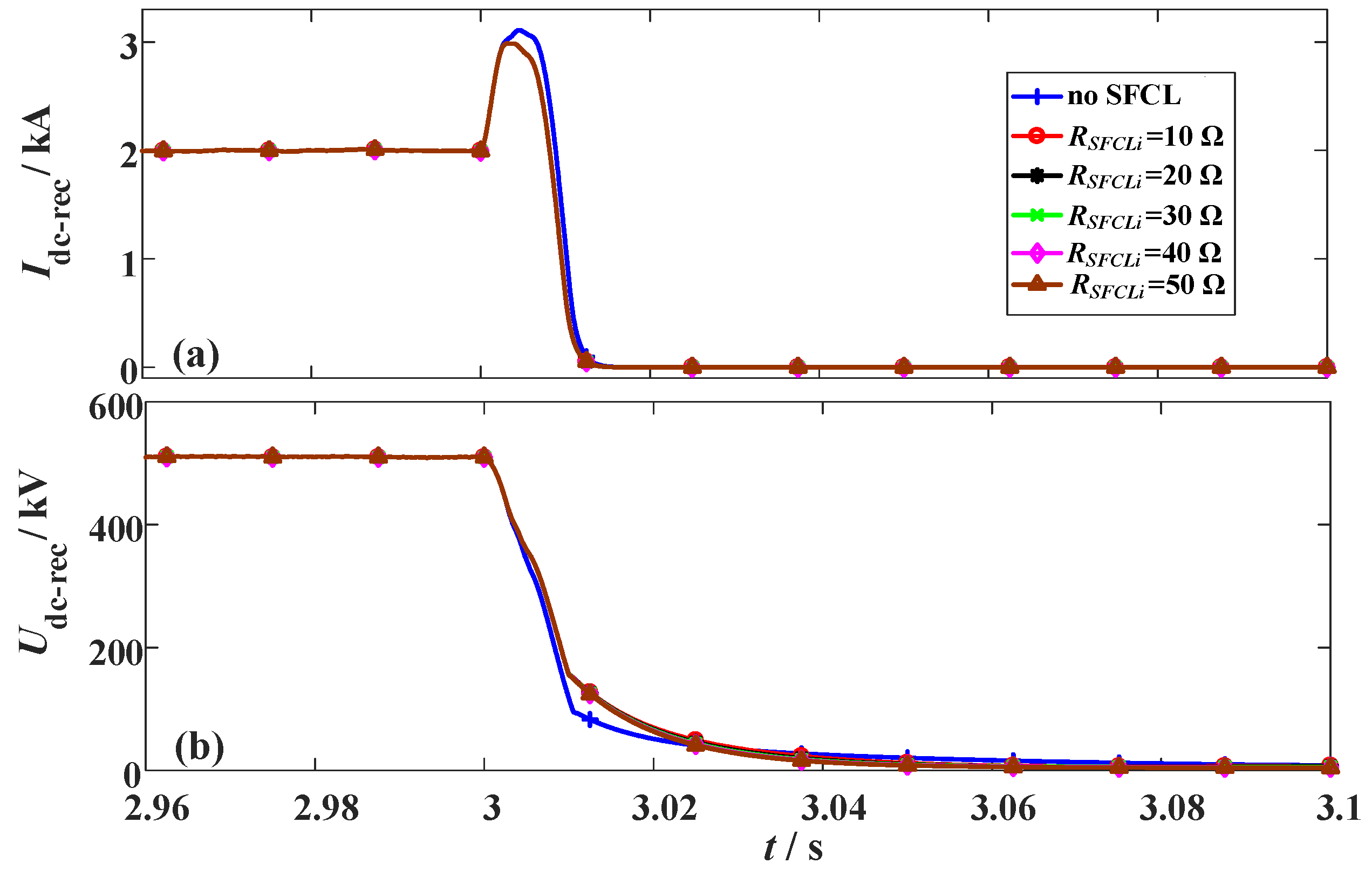

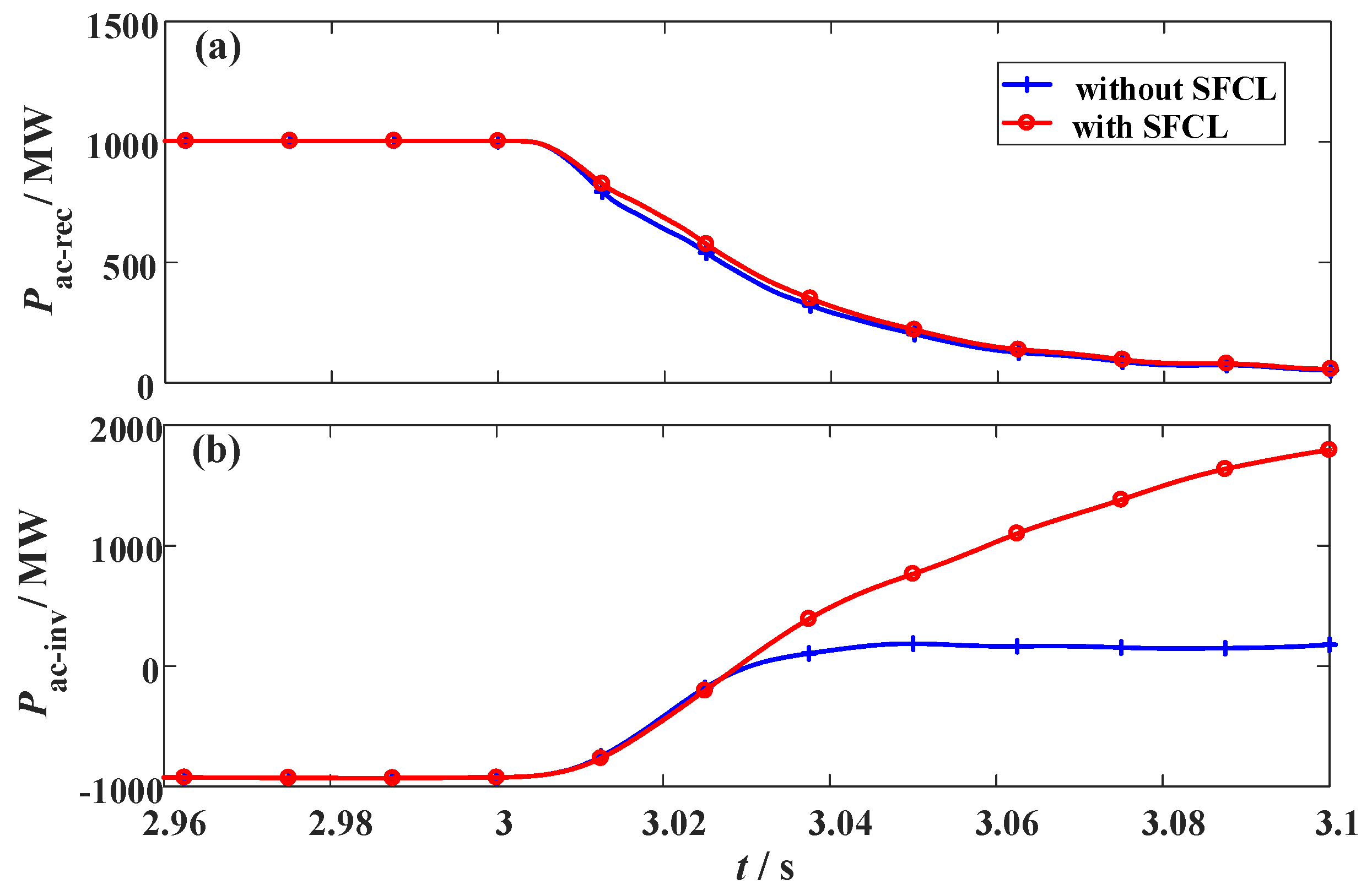

3.2. Changing the SFCL Resistance in the VSC Station

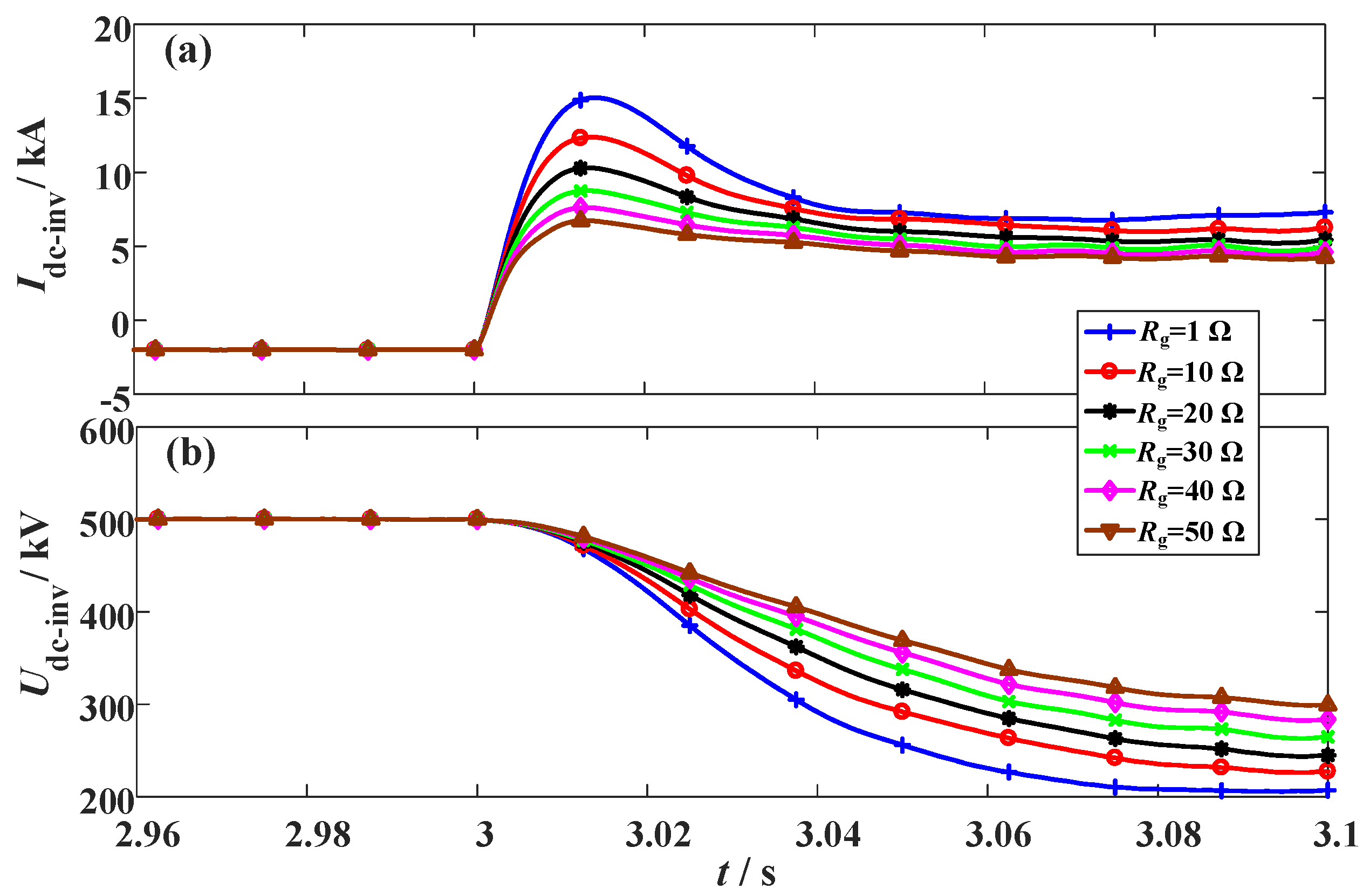

3.3. Changing the Fault Resistance of the Hybrid HVDC

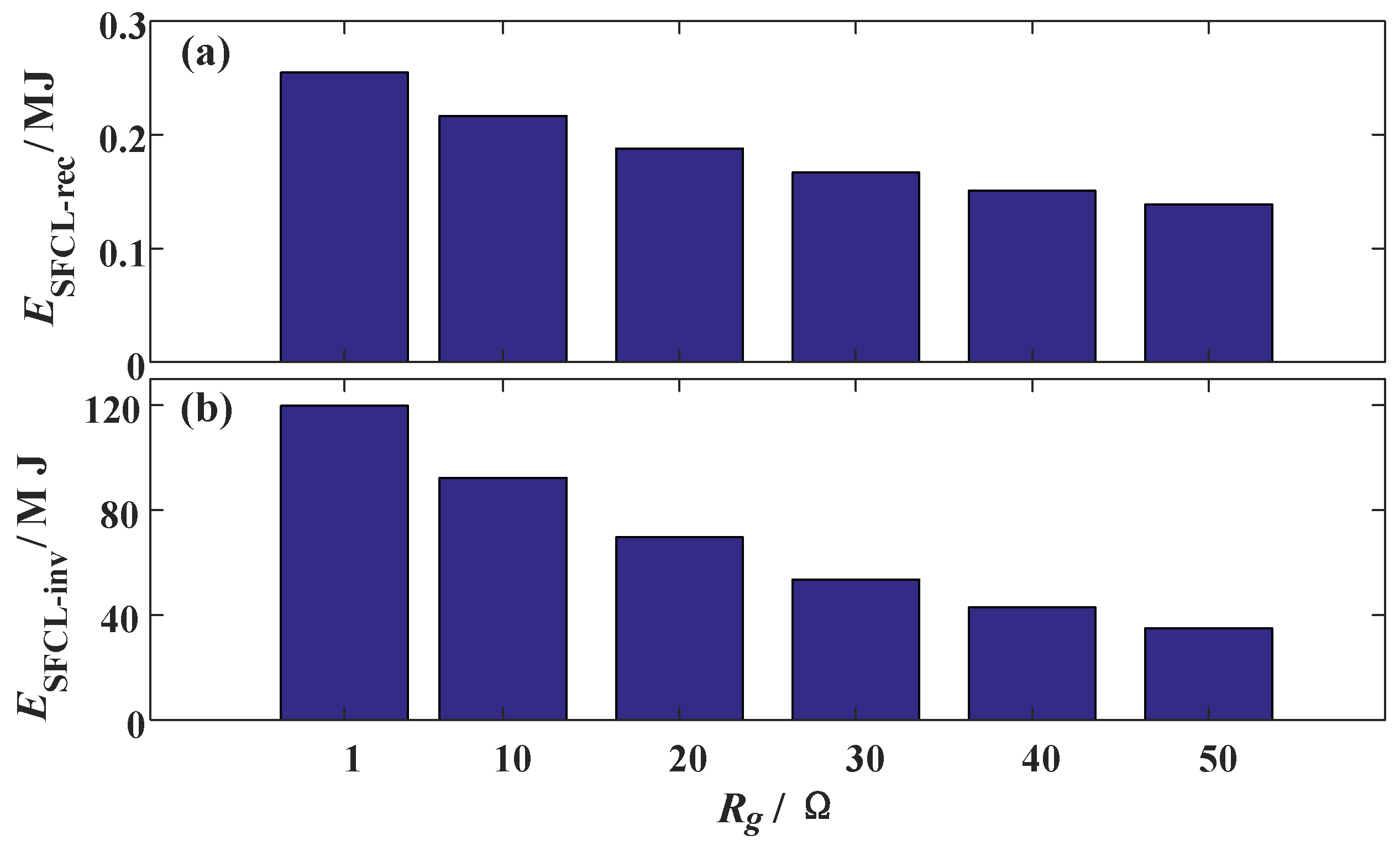

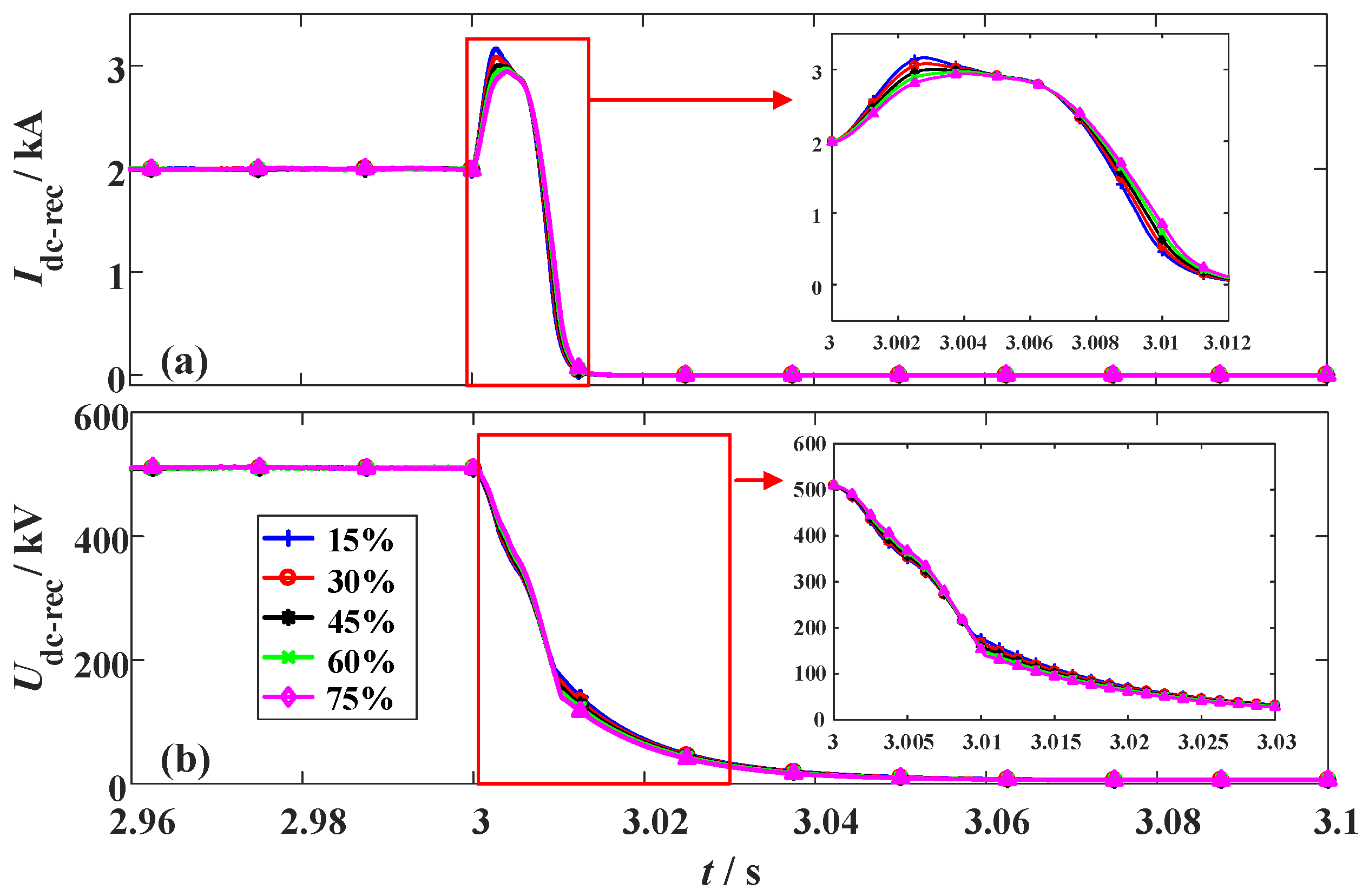

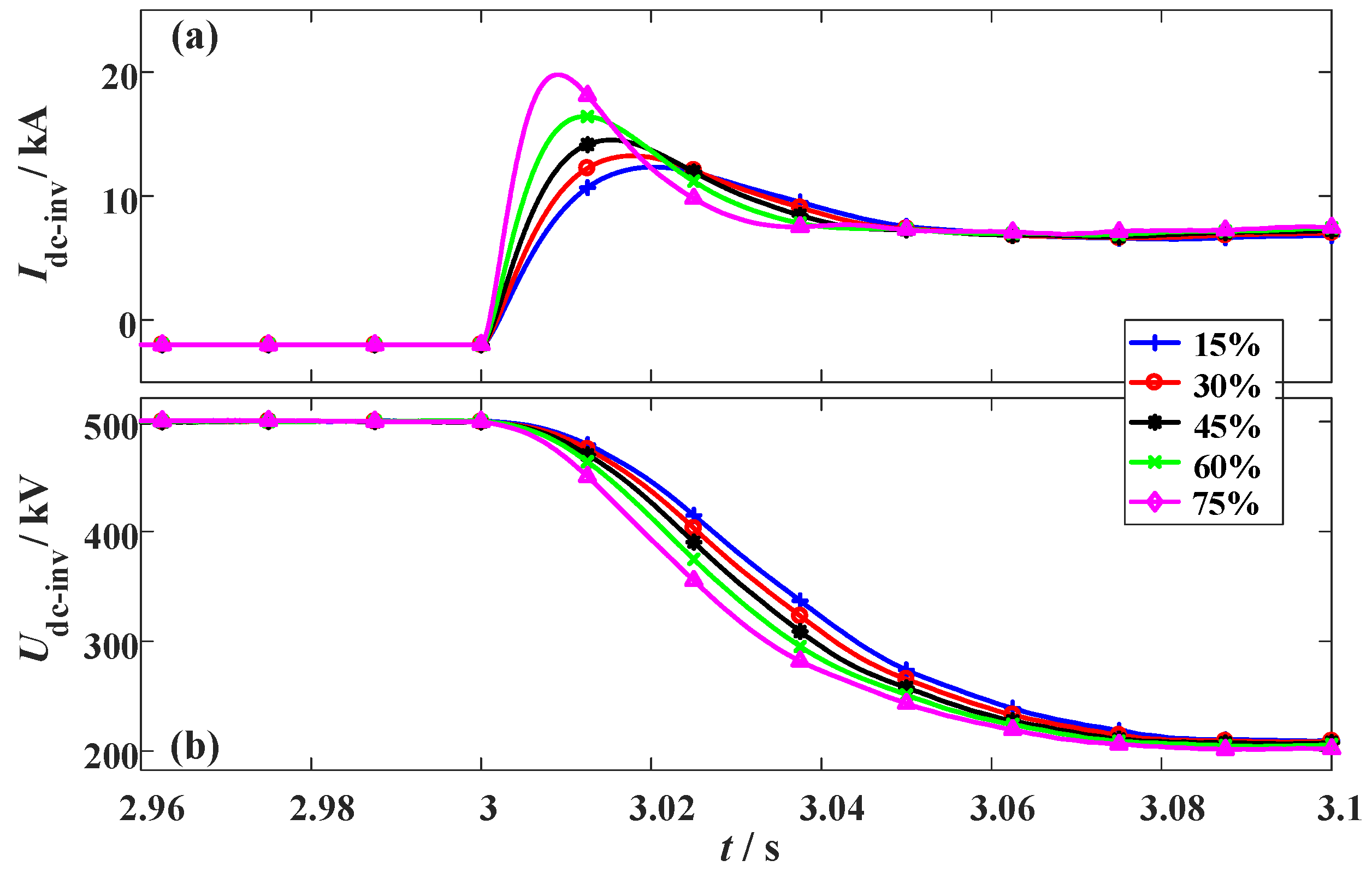

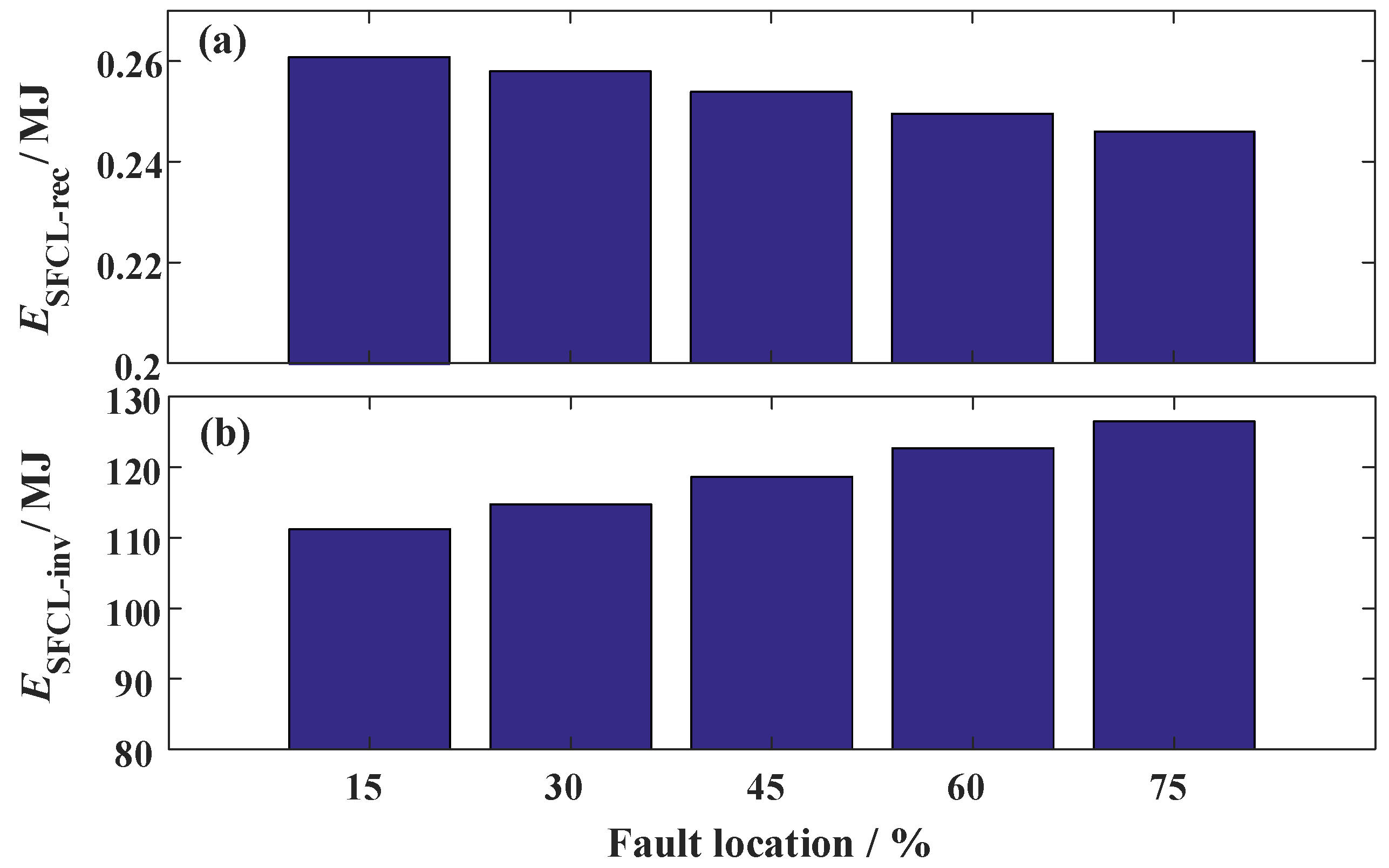

3.4. Changing the Fault Location of the Hybrid HVDC

4. Scheme Design

5. Conclusions

- The superconducting fault current limiter at the voltage source converter station enables to very efficiently mitigate the fault transients, and owns an enhanced current-limiting ability for handling the short-line faults. A moderate increase of the current-limiting resistance can bring better contributions, but an excessive increase may make the current-limiting ratio come up to the saturated level.

- The superconducting fault current limiter at the line commutated converter station is able to mildly limit the fault current and alleviate the voltage drop, and its working performance has a low sensitivity to the fault location. As for the primary and secondary factors, the firing angle controller and the superconducting fault current limiter will combinedly handle the fault transients.

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

Nomenclature

| LCC | Line commutated converter |

| VSC | Voltage source converter |

| RMS | Root mean square |

| FRT | Fault ride-through |

| HVDC | High voltage direct current |

| SFCL | Superconducting fault current limiter |

| YBCO | Yttrium barium copper oxide |

| VOCOL | Voltage-dependent current order limiter |

Symbols

| I | Current [A] | R | Resistance [Ω] |

| X | Reactance [Ω] | U | Voltage [V] |

| P | Power [W] | α | Firing angle [Degree] |

| M | Modulation ratio [-] | L | Inductance [H] |

| C | Capacitance [F] |

Subscripts

| c | Commutation | f | Fault |

| T | Transformer | r | Rectifier side |

| i | Inverter side | g | Ground |

| ac | Alternating current | dc | Direct current |

| sm | Smoothing reactor | min | Minimum |

Appendix A

Appendix A.1. LCC Station Modeling

Appendix A.2. VSC Station Modeling

Appendix A.3. Control Modeling

Appendix A.4. The solution of the DC Fault Current in the VSC Station

References

- Guo, C.; Zhao, C. Supply of an entirely passive ac network through a double-infeed HVdc system. IEEE Trans. Power Electron. 2010, 25, 2835–2841. [Google Scholar]

- Xu, F.; Xuan, X.; Lu, Y.; Qiu, P.; Huang, X.; Yu, H.; Jiang, D. Control Strategies for LCC-MMC Hybrid DC System Connected to Passive Networks. Autom. Electr. Power Syst. 2017, 41, 129–134. [Google Scholar]

- Guo, C.; Yin, Z.; Zhao, C.; Iravani, R. Small-signal dynamics of hybrid LCC-VSC HVDC systems. Int. J. Electr. Power Energy Syst. 2018, 98, 362–372. [Google Scholar] [CrossRef]

- Ni, X.; Gole, A.; Zhao, C.; Guo, C. An Improved Measure of AC System Strength for Performance Analysis of Multi-Infeed HVdc Systems Including VSC and LCC Converters. IEEE Trans. Power Deliv. 2018, 33, 169–178. [Google Scholar] [CrossRef]

- Chen, L.; Chen, H.; Shu, Z.; Zhang, G.; Xia, T.; Ren, L. Comparison of Inductive and Resistive SFCL to Robustness Improvement of a VSC-HVDC System with Wind Plants Against DC Fault. IEEE Trans. Appl. Supercond. 2016, 26, 5603508. [Google Scholar] [CrossRef]

- Chen, L.; Chen, H.; Yang, J.; Jun, Y.; He, H.; Liu, X.; Yu, Y.; Xu, Y.; Wang, Z.; Ren, L. Conceptual Design and Performance Evaluation of a 35-kV/500-A Flux-Coupling-Type SFCL for Protection of a DFIG-Based Wind Farm. IEEE Trans. Appl. Supercond. 2018, 28, 5200607. [Google Scholar] [CrossRef]

- Liang, S.; Tang, Y.; Ren, L.; Xu, Y.; Xia, Z.; Wang, Z.; Guo, S. Tests and Analysis of a Small-Scale Hybrid-Type DC SFCL Prototype. IEEE Trans. Appl. Supercond. 2018, 28, 5602106. [Google Scholar] [CrossRef]

- Rusiński, J. Impact of superconducting fault current limiter on the distributed energy source work. IET Gener. Transm. Distrib. 2018, 12, 310–317. [Google Scholar] [CrossRef]

- Chen, L.; Chen, H.; Li, G.; Tian, X.; Xu, Y.; Ren, L.; Li, Y.; Zhu, L.; Tang, Y. Coordination of SMES, SFCL and Distributed Generation Units for Micro-Grid Stability Enhancement via Wireless Communications. IEEE Access 2018, 6, 36699–36710. [Google Scholar] [CrossRef]

- Li, B.; Wang, C.; Wei, Z.; Xin, Y.; Li, B.; He, J. Technical Requirements of the DC Superconducting Fault Current Limiter. IEEE Trans. Appl. Supercond. 2018, 28, 5602805. [Google Scholar] [CrossRef]

- Chen, L.; Pan, H.; Deng, C.; Zheng, F.; Li, Z.; Guo, F. Study on the application of a flux-coupling-type superconducting fault current limiter for decreasing HVdc commutation failure. Can. J. Electr. Comput. Eng. 2015, 38, 10–19. [Google Scholar] [CrossRef]

- Lee, J.; Khan, U.; Lee, H.; Lim, S.; Lee, B. Mitigation of commutation failures in LCC–HVDC systems based on superconducting fault current limiters. Physica C 2016, 530, 160–163. [Google Scholar] [CrossRef]

- Zhu, J.; Li, Y.; Duan, X. Application of SFCLs to Inhibit Commutation Failure in HVdc Systems: Position Comparison and Resistance Recommendation. Can. J. Electr. Comput. Eng. 2017, 40, 31–40. [Google Scholar]

- Zhang, L.; Shi, J.; Wang, Z.; Tang, Y.; Yang, Z.; Ren, L.; Yan, S.; Liao, Y. Application of a Novel Superconducting Fault Current Limiter in a VSC-HVDC System. IEEE Trans. Appl. Supercond. 2017, 27, 5600706. [Google Scholar] [CrossRef]

- Garcia, W.; Tixador, P.; Raison, B.; Bertinato, A.; Luscan, B.; Creusot, C. Technical and Economic Analysis of the R-Type SFCL for HVDC Grids Protection. IEEE Trans. Appl. Supercond. 2017, 27, 5602009. [Google Scholar]

- Lee, H.; Asif, M.; Park, K.; Lee, B. Feasible Application Study of Several Types of Superconducting Fault Current Limiters in HVDC Grids. IEEE Trans. Appl. Supercond. 2018, 28, 5601205. [Google Scholar] [CrossRef]

- Li, B.; Jing, F.; Li, B.; Chen, X.; Jia, J. Study of the Application of Active Saturated Iron-Core Superconductive Fault Current Limiters in the VSC-HVDC System. IEEE Trans. Appl. Supercond. 2018, 28, 5602906. [Google Scholar] [CrossRef]

- Zhang, Z.; Guo, T.; Yang, J.; Qi, Q.; Xiao, L.; Zhang, G.; Lin, L. Resistance varying characteristics of DC superconducting fault current limiter in MTDC system. Cryogenics 2017, 81, 1–7. [Google Scholar] [CrossRef]

- Sanusi, W.; Hosani, M.; Moursi, M. A Novel DC Fault Ride-Through Scheme for MTDC Networks Connecting Large-Scale Wind Parks. IEEE Trans. Sustain. Energy 2017, 8, 1086–1095. [Google Scholar] [CrossRef]

- Arrillaga, J. High Voltage Direct Current Transmission; The Institution of Electrical Engineers: London, UK, 2008. [Google Scholar]

- Yang, X.; Chen, H.; Miao, Y.; Wang, L.; Hu, W.; Yang, R. A Method of PI Parameters Tuning for VSC-HVDC Control System. Mod. Electr. Power 2015, 32, 68–73. [Google Scholar]

- Chen, L.; Chen, H.; Yang, J.; Zhu, L.; Tang, Y.; Koh, L.; Xu, Y.; Zhang, C.; Liao, Y.; Ren, L. Comparison of Superconducting Fault Current Limiter and Dynamic Voltage Restorer for LVRT Improvement of High Penetration Microgrid. IEEE Trans. Appl. Supercond. 2017, 27, 3800607. [Google Scholar] [CrossRef]

- Kar, S.; Rao, V. Comparative study on the fastest effective fault limitation for stabilized and stabilizer-free high Tc superconductors. Physica C 2017, 541, 50–54. [Google Scholar] [CrossRef]

- Yang, J.; Fletcher, J.; O’Reilly, J. Short-circuit and ground fault analyses and location in VSC-based dc network cables. IEEE Trans. Ind. Electron. 2012, 59, 3827–3837. [Google Scholar] [CrossRef]

- Liu, J.; Tai, N.; Fan, C.; Chen, S. A Hybrid Current-Limiting Circuit for DC Line Fault in Multiterminal VSC-HVDC System. IEEE Trans. Ind. Electron. 2017, 64, 5595–5607. [Google Scholar] [CrossRef]

- Li, B.; Jing, F.; Jia, J.; Li, B. Research on Saturated Iron-Core Superconductive Fault Current Limiters Applied in VSC-HVDC Systems. IEEE Trans. Appl. Supercond. 2016, 26, 5603805. [Google Scholar] [CrossRef]

- Li, B.; He, J. DC Fault Analysis and Current Limiting Technique for VSC-based DC Distribution System. Proc. CSEE 2015, 35, 3026–3036. [Google Scholar]

- Li, B.; He, J. Research on the DC Fault Isolating Technique in Multi-terminal DC System. Proc. CSEE 2016, 36, 87–95. [Google Scholar]

- Ngamroo, I.; Karaipoom, T. Cooperative Control of SFCL and SMES for Enhancing Fault Ride Through Capability and Smoothing Power Fluctuation of DFIG Wind Farm. IEEE Trans. Appl. Supercond. 2014, 24, 5400304. [Google Scholar] [CrossRef]

- Lee, J.; Joo, S. Economic Assessment Method for Superconducting Fault Current Limiter (SFCL) in Fault Current-Constrained Power System Operation. IEEE Trans. Appl. Supercond. 2013, 23, 5601104. [Google Scholar]

- Xin, Y. Review on Superconducting Fault Current Limiters. South. Power Syst. Technol. 2015, 9, 1–9. [Google Scholar]

- Kalsi, S.S. Applications of High Temperature Superconductors to Electric Power Equipment; John Wiley & Sons: Hoboken, NJ, USA, 2011; pp. 185–188. [Google Scholar]

- Chen, L.; Li, G.; Chen, H.; Tao, Y.; Tian, X.; Liu, X.; Xu, Y.; Ren, L.; Tang, Y. Combined Use of a Resistive SFCL and DC-link Regulation of a SMES for FRT Enhancement of a DFIG Wind Turbine Under Different Faults. IEEE Trans. Appl. Supercond. 2019, 29, 5600408. [Google Scholar] [CrossRef]

- Xiao, L.; Dai, S.; Lin, L.; Zhang, Z.; Zhang, J. HTS Power Technology for Future DC Power Grid. IEEE Trans. Appl. Supercond. 2013, 23, 5401506. [Google Scholar] [CrossRef]

- Majka, M.; Kozak, J.; Kozak, S. HTS Tapes Selection for Superconducting Current Limiters. IEEE Trans. Appl. Supercond. 2017, 27, 5601405. [Google Scholar] [CrossRef]

| Type of SFCL | Type of HVDC | Voltage Class | Research Object | EvaluationMethod | Country, Report Year |

|---|---|---|---|---|---|

| Flux-coupling-type | LCC HVDC | 230 kV | Commutation failure and fault recovery | MATLAB Simulation | China, 2015 [11] |

| Resistive type | LCC HVDC | 180 kV [12] 500 kV [13] | Commutation failure and position analysis | PSCAD Simulation | Korea, 2016 [12] China, 2017 [13] |

| Hybrid-type | VSC HVDC | 160 kV | Principle verification and scheme design | MATLAB Simulation | China, 2017 [14] |

| Resistive type | VSC HVDC | 320 kV [15,19] 100 kV [16] 200 kV [18] | Techno-economic evolution and resistance varying behaviors | PSCAD [15,19] MATLAB [16,18] | France, 2017 [15] Korea, 2018 [16] China, 2017 [18] UAE, 2017 [19] |

| Inductive type | VSC HVDC | 100 kV | Current limitation and recovery | MATLAB Simulation | Korea, 2018 [16] |

| Saturated iron-core-type | VSC HVDC | 100 kV | Modeling, voltage analysis and energy dissipation | MATLAB Simulation | Korea, 2018 [16] China, 2018 [17] |

| Superconducting Fault Current Limiters | |

|---|---|

| Superconducting coil Rsc at the LCC/VSC | 20 Ω–100 Ω/10 Ω–50 Ω |

| LCC Station | |

| Rated voltage/frequency | 380 kV/50 Hz |

| Short-circuit ratio | 3.076 |

| DC current controller | K pIdc = 1, KiIdc = 90 |

| DC Link | |

| Rated voltage/current | 500kV/2 kA |

| Length of DC transmission line | 500 km |

| Smoothing reactor of LCC/VSC | 0.3 H/0.01 H |

| VSC Station | |

| Rated voltage/frequency | 220 kV/50 Hz |

| Short-circuit ratio | 3.34 |

| AC current controller (KpVac, KiVac) | KpVac = 0.6, KiVac = 10 |

| DC voltage controller (KpVdc, KiVdc) | KpVac = 8, KiVac = 20 |

| Items | Effects of the SFCL on the VSC Station | |

|---|---|---|

| DC Fault Current/Current-Limiting Ratio | DC Voltage/Calculated Drop Rate | |

| RSFCLi = 10 Ω | 22.1 kA/24.7% | 101.5 kV/79.7% |

| RSFCLi = 20 Ω | 17.8 kA/39% | 160.1 kV/67.9% |

| RSFCLi = 30 Ω | 15.1 kA/48.5% | 196.9 kV/60.6% |

| RSFCLi = 40 Ω | 13.2 kA/55.1% | 223.8 kV/55.2% |

| RSFCLi = 50 Ω | 11.7 kA/59.9% | 241.3 kV/51.7% |

| Items | DC Fault Current | DC Voltage | ||

|---|---|---|---|---|

| No SFCL | With SFCL/Current-Limiting Ratio | No SFCL | With SFCL | |

| Rg = 10 Ω | 21.2 kA | 12.4 kA/41.7% | 99.1 kV | 222.2 kV |

| Rg = 20 Ω | 16.1 kA | 10.3 kA/36.1% | 159.1 kV | 239.8 kV |

| Rg = 30 Ω | 12.8 kA | 8.76 kA/31.7% | 196.9 kV | 252.1 kV |

| Rg = 40 Ω | 10.6 kA | 7.62 kA/28.3 % | 221.5 kV | 261.8 kV |

| Rg = 50 Ω | 9.03 kA | 6.74 kA/25.4% | 239.9 kV | 271.9 kV |

| Fault Location Ratio | Energy Dissipation | |

|---|---|---|

| SFCL at the LCC Station | SFCL at the VSC Station | |

| 15% | 0.265 MJ | 111.2 MJ |

| 30% | 0.258 MJ | 114.8 MJ |

| 45% | 0.252 MJ | 118.7 MJ |

| 60% | 0.247 MJ | 122.7 MJ |

| 75% | 0.243 MJ | 126.5 MJ |

| Parameter | Value |

|---|---|

| Length of YBCO tape (m) | 54 |

| Inner diameter (mm) | 200 |

| Outer diameter (mm) | 870 |

| Interturn gap (mm) | 5 |

| Resistance (Ω) | 1.28 Ω @ 100 K |

| Resistance (Ω) | 2.98 Ω @ 300 K |

| N Value (μV/cm) | 38.6 |

| Rated voltage (kV) | 3 |

| Break-down voltage (kV) | 15 |

| Rated current (A) | 200 |

| Peak current (A, with a duration of 100 ms) | 900 |

| Safety temperature limit (K) | 300 |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chen, L.; He, H.; Li, G.; Chen, H.; Wang, L.; Chen, X.; Tian, X.; Xu, Y.; Ren, L.; Tang, Y. Study of Resistive-Type Superconducting Fault Current Limiters for a Hybrid High Voltage Direct Current System. Materials 2019, 12, 26. https://doi.org/10.3390/ma12010026

Chen L, He H, Li G, Chen H, Wang L, Chen X, Tian X, Xu Y, Ren L, Tang Y. Study of Resistive-Type Superconducting Fault Current Limiters for a Hybrid High Voltage Direct Current System. Materials. 2019; 12(1):26. https://doi.org/10.3390/ma12010026

Chicago/Turabian StyleChen, Lei, Huiwen He, Guocheng Li, Hongkun Chen, Lei Wang, Xiaoyuan Chen, Xin Tian, Ying Xu, Li Ren, and Yuejin Tang. 2019. "Study of Resistive-Type Superconducting Fault Current Limiters for a Hybrid High Voltage Direct Current System" Materials 12, no. 1: 26. https://doi.org/10.3390/ma12010026

APA StyleChen, L., He, H., Li, G., Chen, H., Wang, L., Chen, X., Tian, X., Xu, Y., Ren, L., & Tang, Y. (2019). Study of Resistive-Type Superconducting Fault Current Limiters for a Hybrid High Voltage Direct Current System. Materials, 12(1), 26. https://doi.org/10.3390/ma12010026