A P-Q Arc Suppression Method Based on DC-Link Voltage Stability for Hybrid Multifunctional Arc Suppression Devices

Abstract

1. Introduction

Literature Review

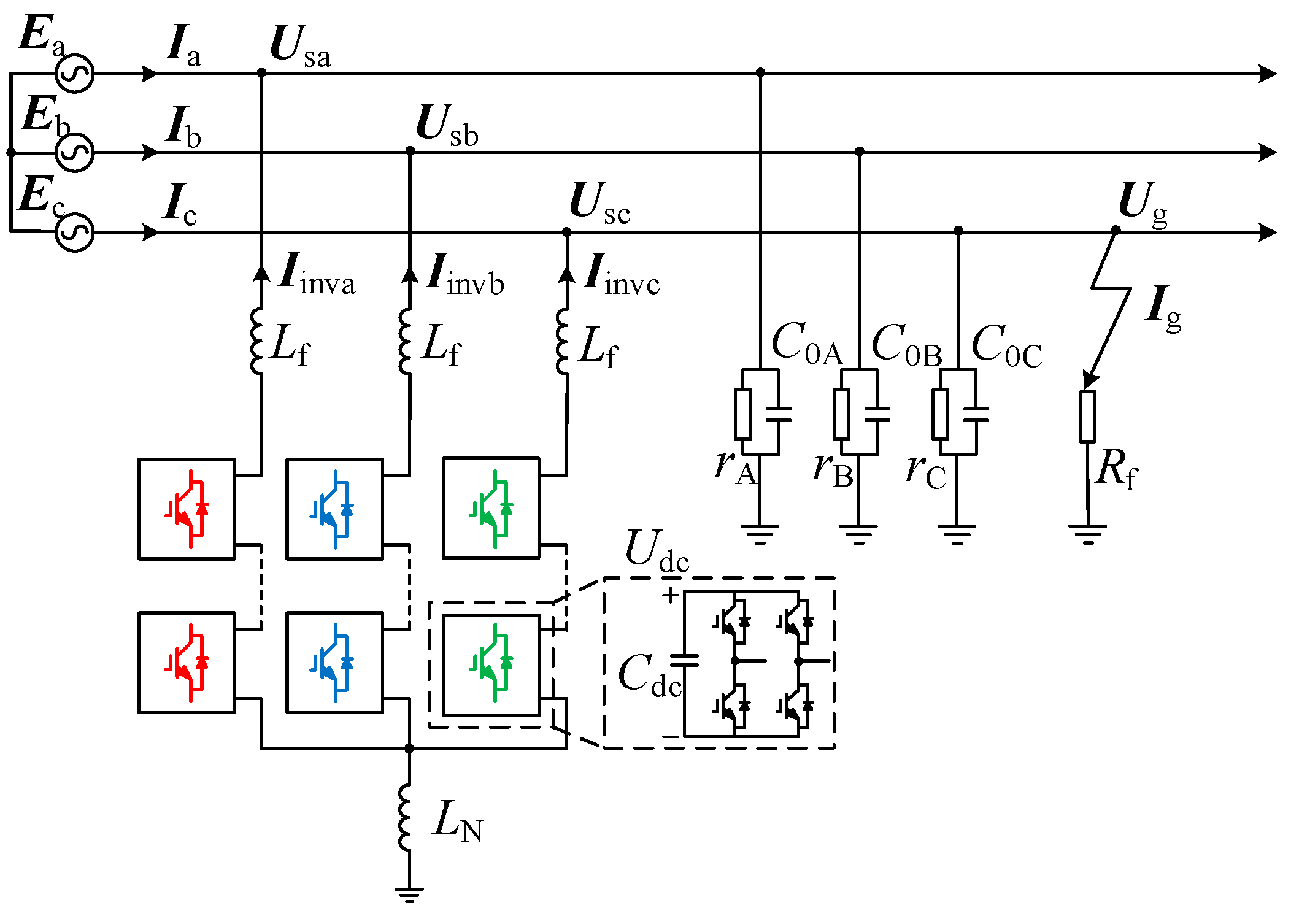

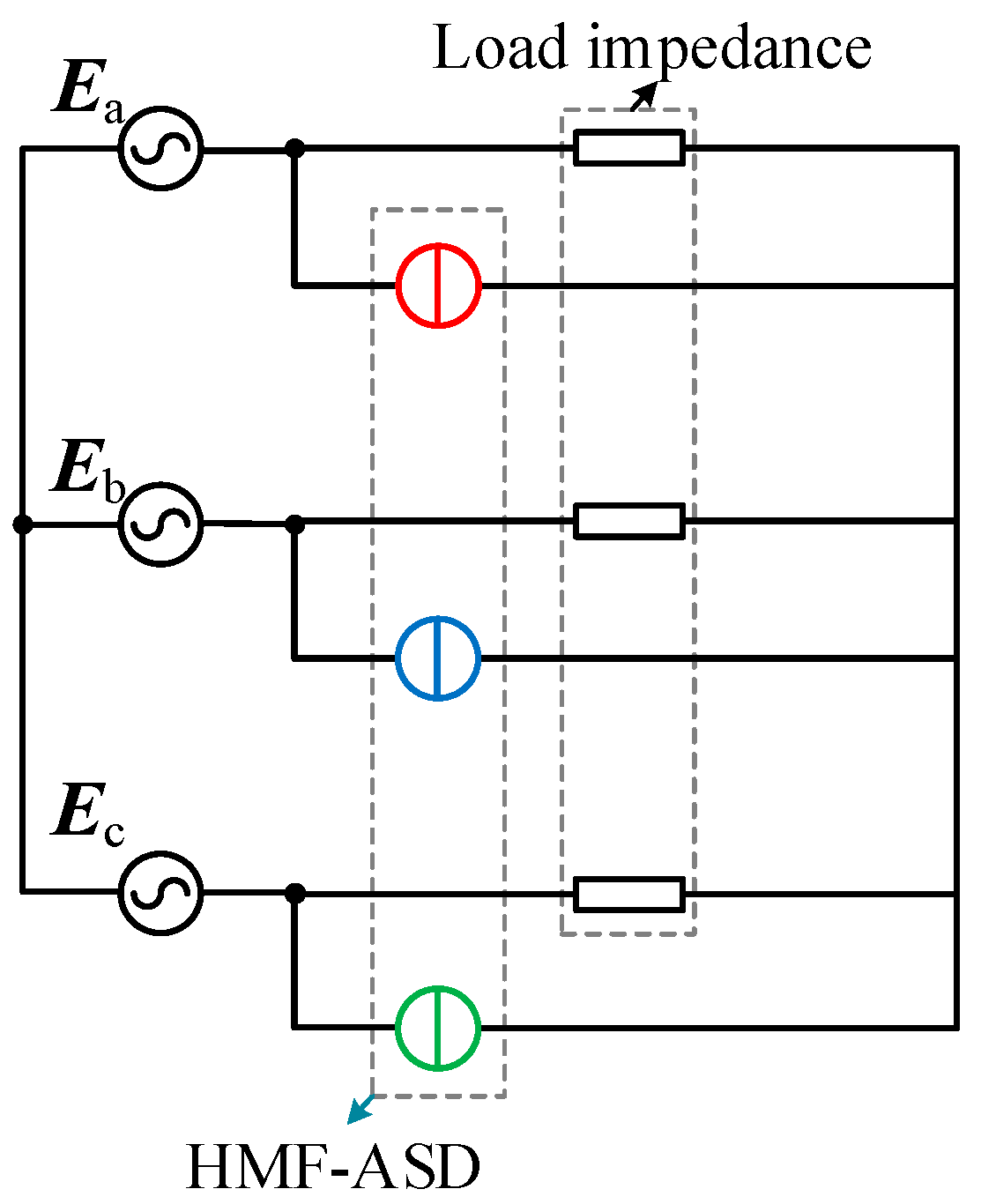

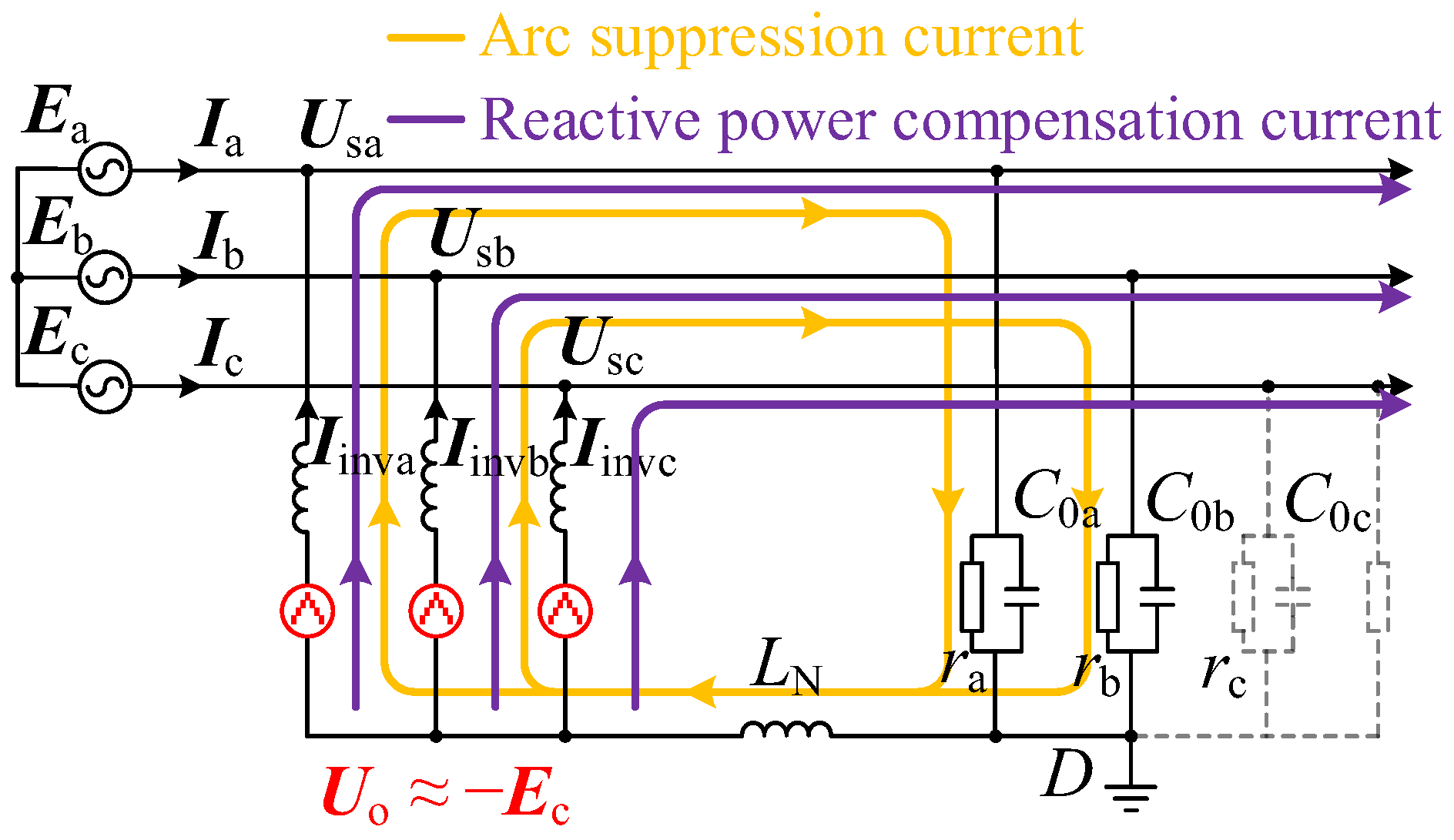

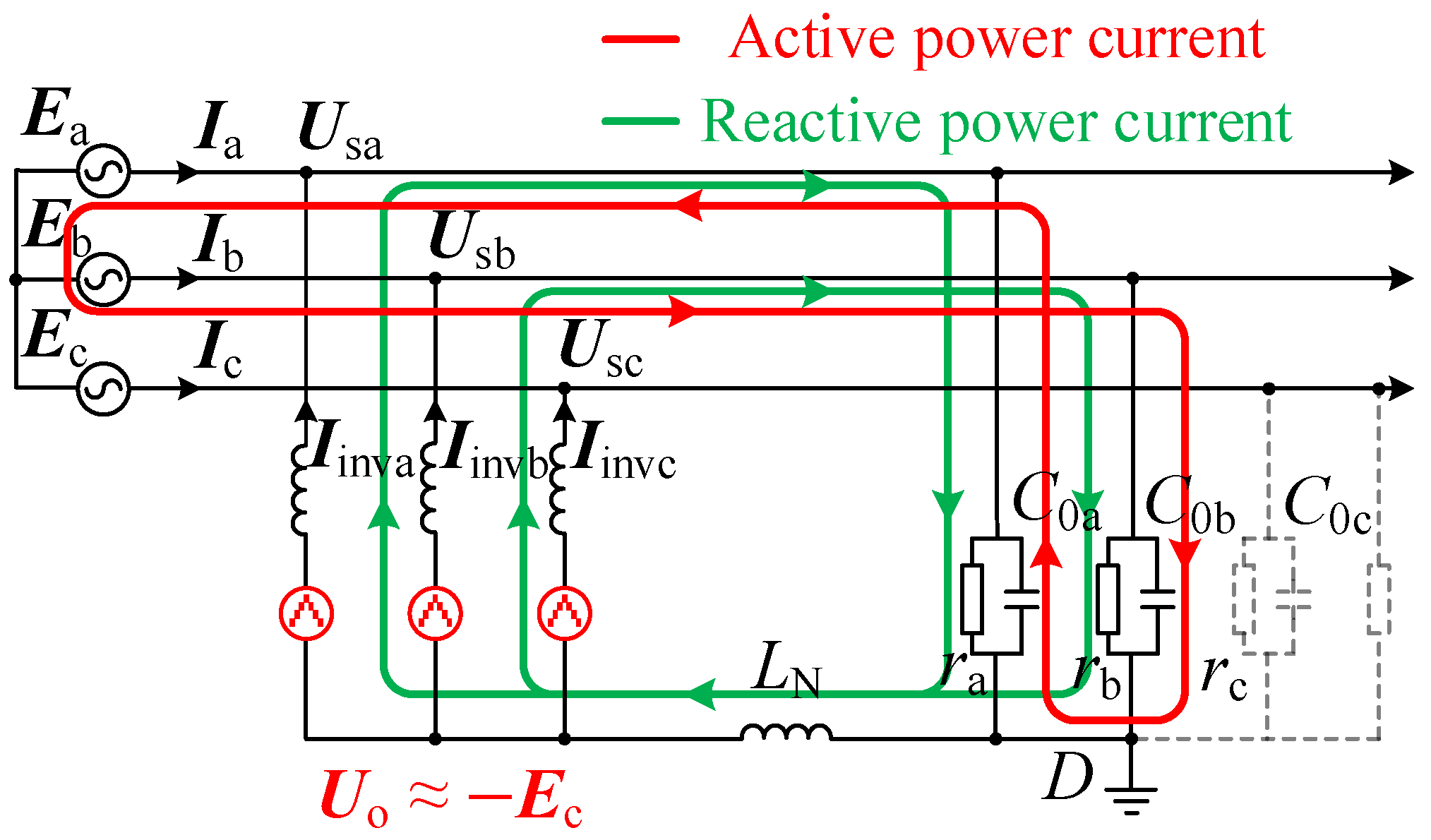

2. Topology and Working Principle of HMF-ASD

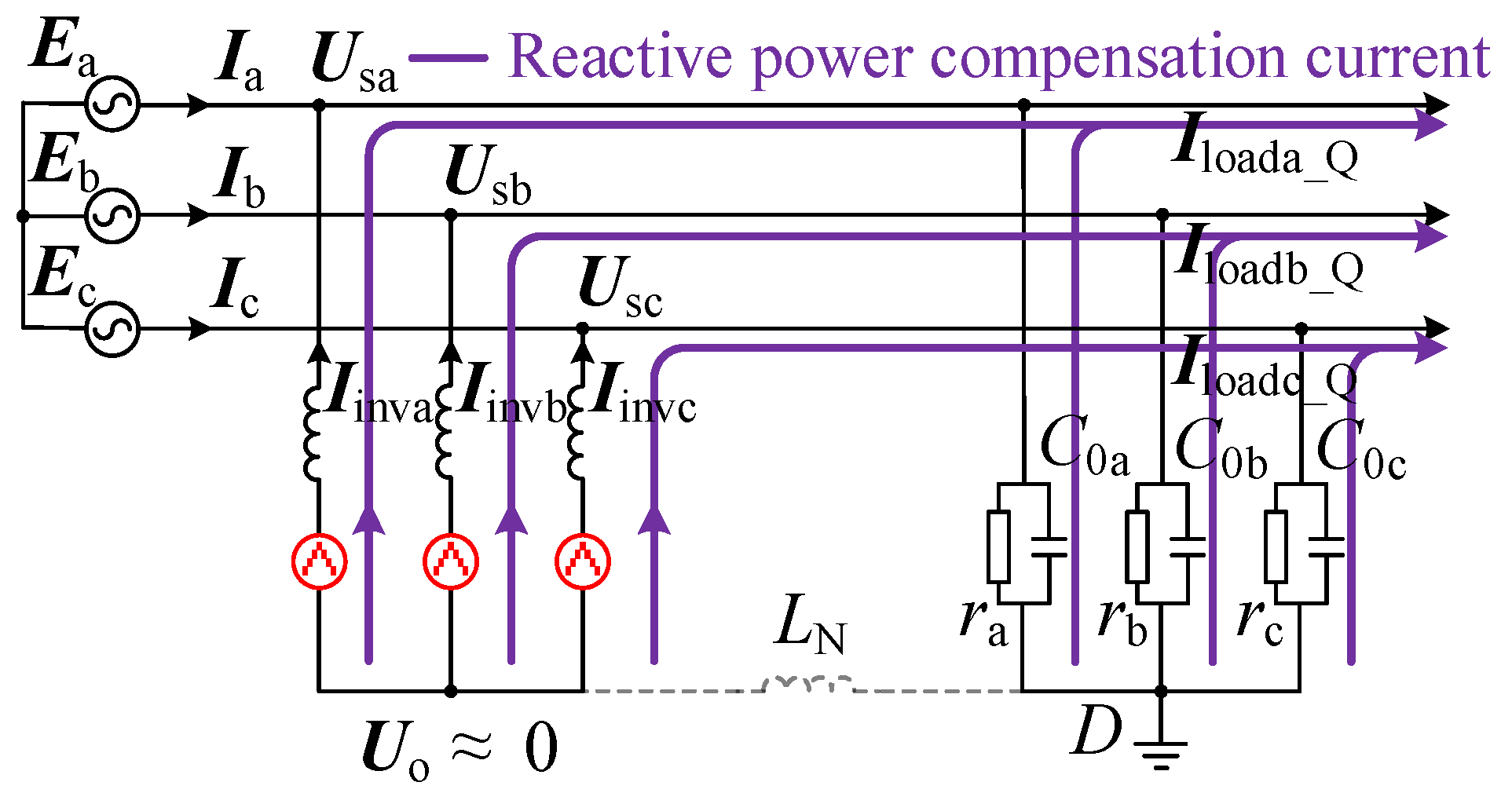

2.1. Analysis of Reactive Power Compensation Mode

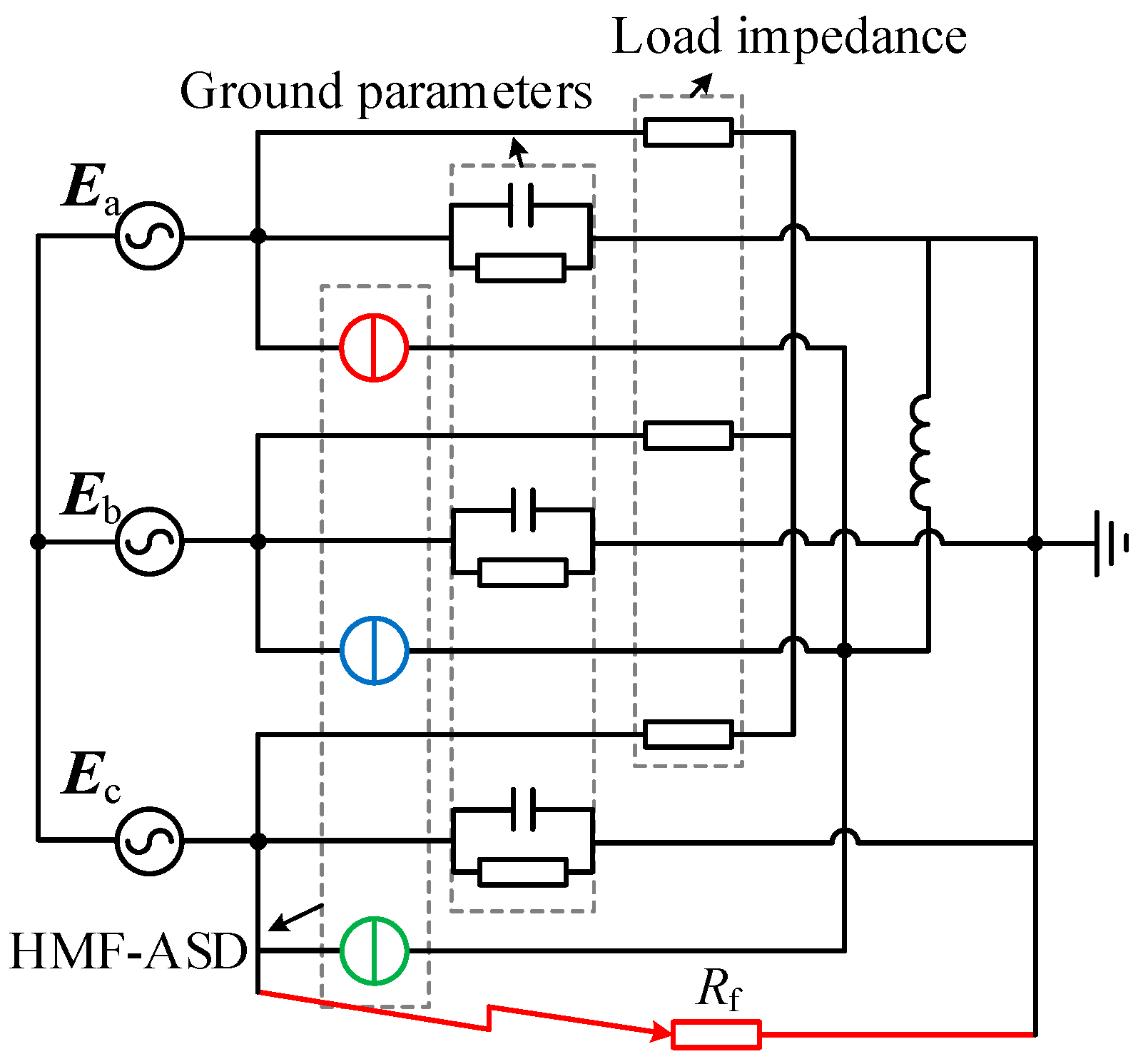

2.2. Analysis of Arc Suppression Mode

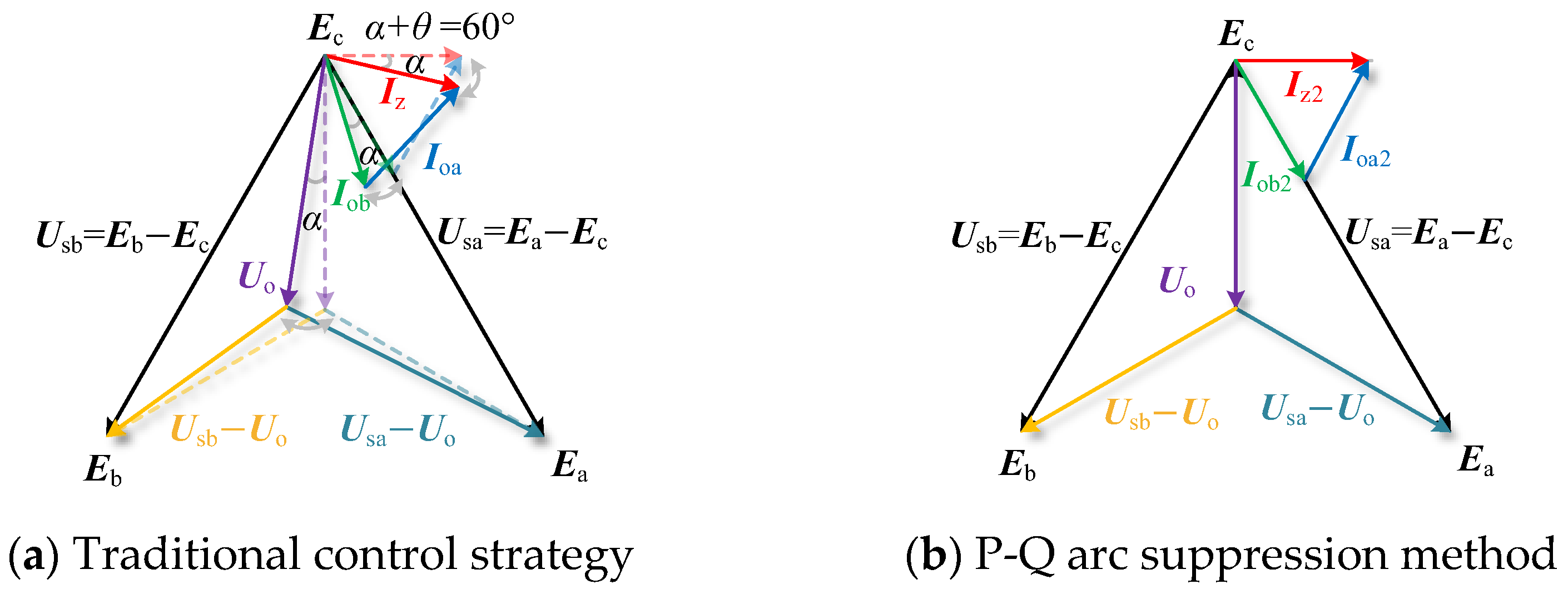

3. Failure Mechanism of Traditional Arc Suppression Method

3.1. Power Characteristics of Traditional Arc Suppression Method

3.2. Control Strategy of the Traditional Arc Suppression Method

4. P-Q Arc Suppression Method Based on DC-Link Voltage Stability

- (1)

- Power loop

- (2)

- Voltage stabilizing loop

- (3)

- Current loop

- (1)

- As for Scheme I, the influence of a zero sequence loop is not considered. Further, the existing DC-link voltage control strategies for arc suppression devices are not applicable to the condition with ground resistance. As the DC-link voltage of the HMF-ASD progressively decreases, fault current escalates, ultimately compromising arc suppression capability.

- (2)

- As for Scheme II, the DC side of the HMF-ASD is connected to auxiliary DC power supplies to provide arc suppression energy. While this method enables complete fault current compensation with minimal control complexity, it incurs relatively high costs.

- (3)

- To achieve DC-link voltage stability and full fault current compensation without auxiliary power supplies, this paper introduces a P-Q-based arc suppression strategy. A comparative analysis with existing methods is presented in Table 2. The proposed method demonstrates superior cost-effectiveness and arc suppression performance compared to conventional approaches, though its control complexity exceeds that of Scheme II.

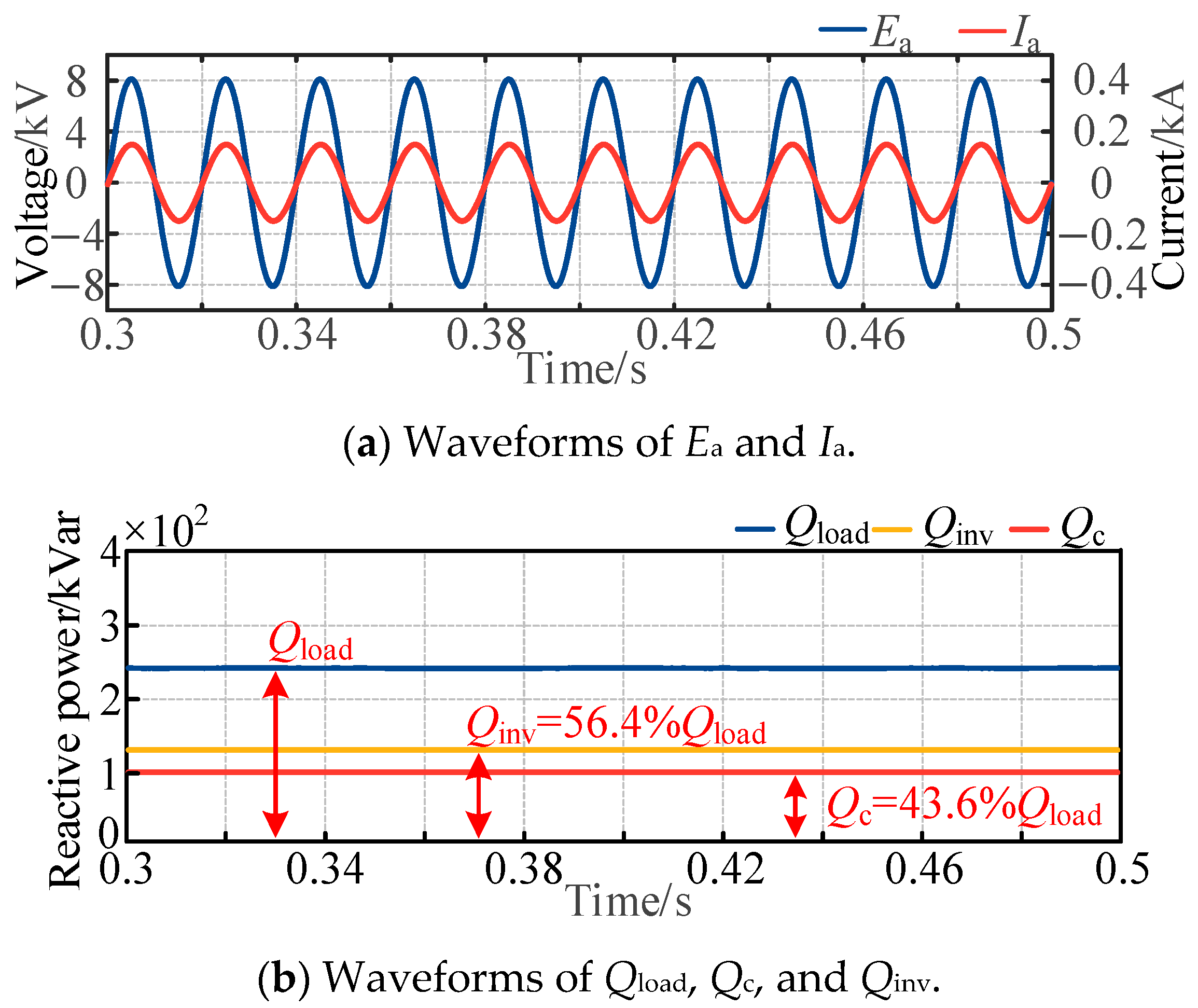

5. Simulation Results

5.1. Simulation of Reactive Power Compensation Mode

5.2. Simulation of Arc Suppression Mode

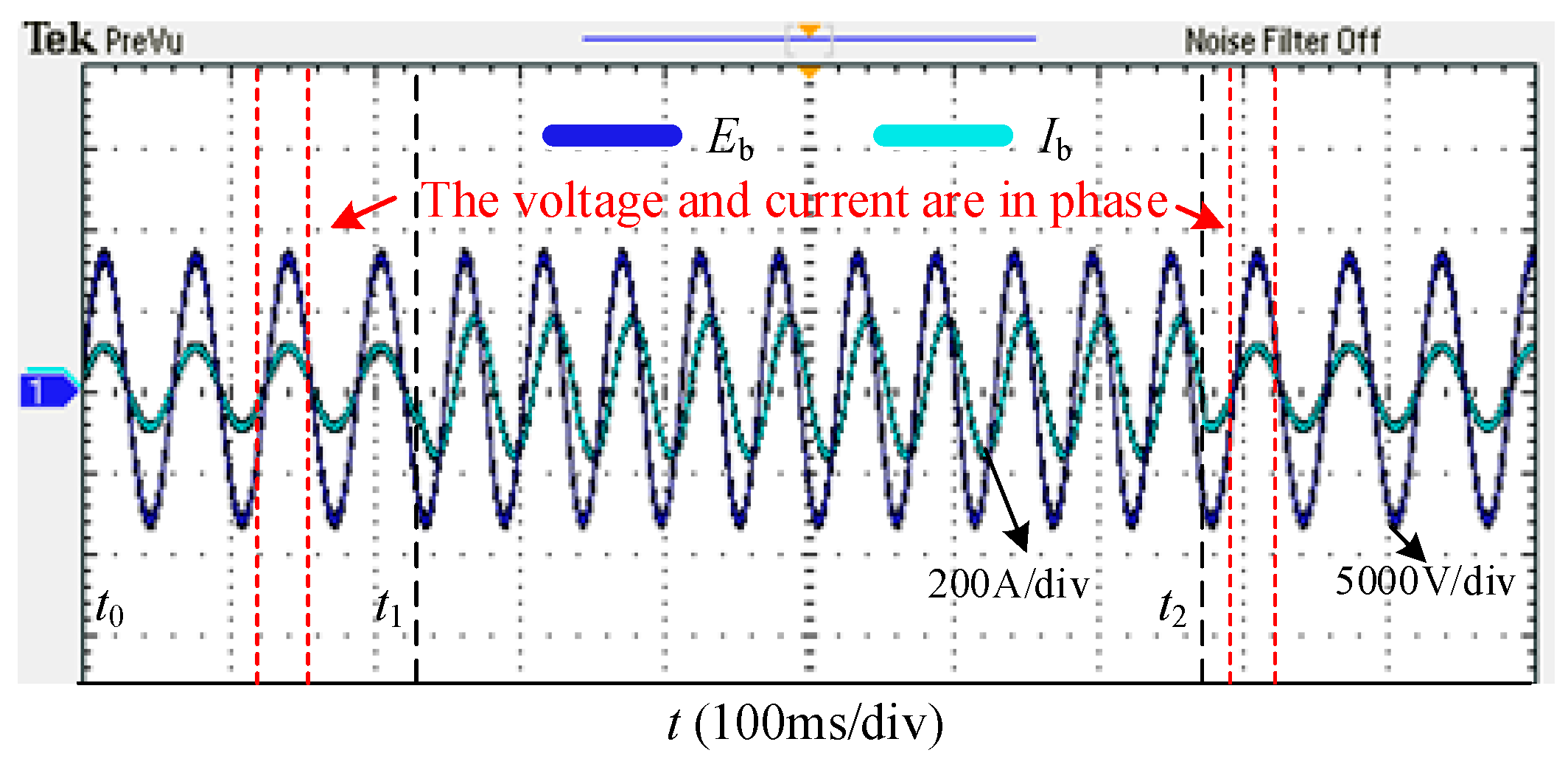

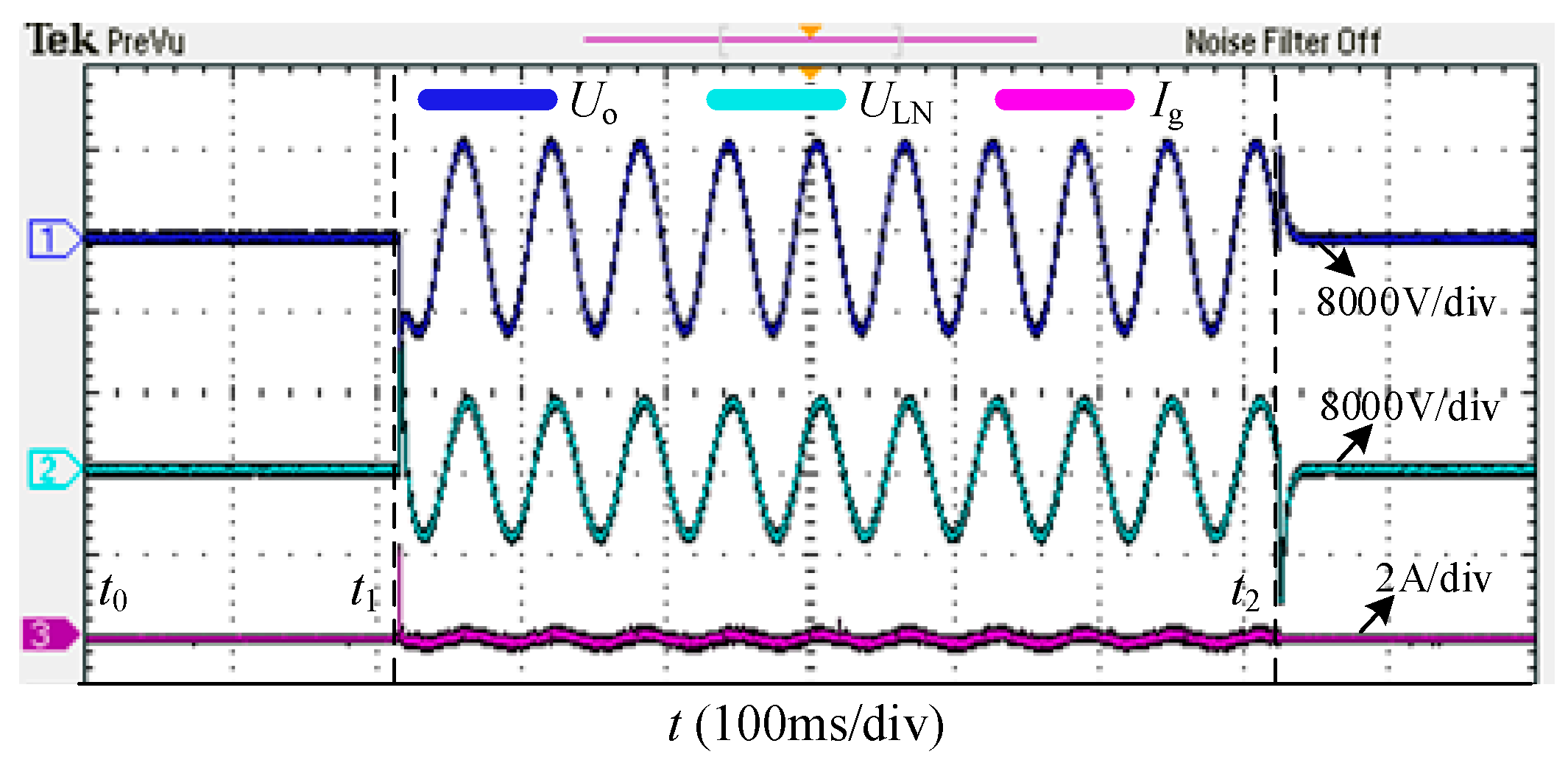

6. Experimental Results

7. Conclusions

- (1)

- The working principle of the HMF-ASD is introduced and the current flow of the HMF-ASD in two modes is analyzed.

- (2)

- The influence mechanism of the traditional arc suppression method on the output active power and energy flow direction of the HMF-ASD is analyzed. The internal causes of DC link voltage changes are clarified.

- (3)

- The phase relationship between voltage and current under arc suppression mode is analyzed, and a P-Q arc suppression method is proposed. By controlling the HMF-ASD to compensate only zero-sequence reactive power, the HMF-ASD can stabilize the DC-link voltage.

- (4)

- Compared with existing methods, the proposed method has lower cost and better arc suppression effect, but the control complexity is relatively high.

- (5)

- In the future, the performance improvement of PLL under unbalanced and fault conditions will be further studied.

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

Nomenclature

| Parameters | Definitions |

| Ex | System voltage |

| Usx | Busbar voltage |

| Ug | Fault voltage |

| Uo | The voltage at the common point of HMF-ASD |

| Uinvx | The voltage borne by the active part of HMF-ASD |

| Ix | System current |

| Ig | Fault current |

| Iinvx | Output current of HMF-ASD |

| Iloadx_Q | Reactive currents of the load |

| Iox | Arc suppression currents |

| Iox1 | The active component of the stabilizing current of HMF-ASD |

| Iz | Total arc suppression current |

| rx | The ground resistance |

| C0x | The ground capacitance |

| Cdc | The DC-link capacitance |

| Lf | Filter inductance |

| LN | Arc suppression inductance |

| Rf | The ground-fault resistance |

| Pinvx | The active power transmitted by HMF-ASD |

| Pzab | The zero-sequence active power using traditional arc suppression method |

| Pzab′ | The zero-sequence active power using P-Q arc suppression method |

| Qx* | The reactive power reference values |

| Qx | The actual reactive power values |

| Qload | The reactive power of the load |

| Qc | The reactive power of the ground capacitance |

| Qinv | The reactive power of HMF-ASD |

| Qzab | The zero-sequence reactive power using traditional arc suppression method |

| Qzab′ | The zero-sequence reactive power using P-Q arc suppression method |

| izx | The current reference values corresponding to power loops |

| idcx | The current reference values corresponding to voltage stabilizing loops |

| N | The number of cascades |

| Udcx.ref | The reference value of DC-link voltage |

| ∑Udcxi | The actual value of DC-link voltage |

| ULN | The voltage of arc suppression inductance |

| α | The angle between the ground resistance and capacitance |

References

- Zhu, R.; Liserre, M. Control of Smart Transformer Under Single-Phase to Ground Fault Condition. IEEE Trans. Power Electron. 2020, 35, 2034–2043. [Google Scholar] [CrossRef]

- Huang, Z.; Guo, Q.; Xiao, Z.; Tu, C.; Sun, K.; Wang, L.; Zhu, D.; Hou, Y. Hybrid Multifunctional Arc Suppression Inverter With Its Steady and Transient State Operation Optimization Method. IEEE Trans. Power Electron. 2025, 40, 10313–10323. [Google Scholar] [CrossRef]

- Tang, J.; Xiong, B.; Li, Y.; Yuan, C.; Qiu, Y. Faulted Feeder Identification Based on Active Adjustment of Arc Suppression Coil and Similarity Measure of Zero-Sequence Currents. IEEE Trans. Power Deliv. 2021, 36, 3903–3913. [Google Scholar] [CrossRef]

- Liu, K.; Zhang, S.; Li, B.; Zhang, C.; Liu, B.; Jin, H.; Zhao, J. Flexible Grounding System for Single-Phase to Ground Faults in Distribution Networks: A Systematic Review of Developments. IEEE Trans. Power Deliv. 2022, 37, 1640–1649. [Google Scholar] [CrossRef]

- Li, L.; Zeng, X.; Bai, H.; Yu, K.; Li, J.; Peng, H.; Wang, Z.; Luo, H.; Wang, F. Analysis and Design of Flexible Arc Suppression Device Based on Proportional Series Lagging Control. Int. J. Electr. Power Energy Syst. 2022, 143, 108478. [Google Scholar] [CrossRef]

- Tan, L.; Wang, Y.; Yin, X.; Qiao, J.; Xu, W. Injected Current Regulation Based Stator Ground Fault Arc Suppression Method for Large Hydro-Generators. Int. J. Electr. Power Energy Syst. 2022, 143, 108513. [Google Scholar] [CrossRef]

- Belik, M.; Kuchanskyy, V.; Rubanenko, O. The Method of the Secondary Arc Suppression in Cycle Single-Phase Auto Reclose with High-Level Penetration Renewable Energy Sources. Energies 2023, 16, 6880. [Google Scholar] [CrossRef]

- Ouyang, S.; Liu, J.; Yang, Y.; Chen, X.; Song, S.; Wu, H. Control Strategy for Arc-Suppression-Coil-Grounded Star-Connected Power Electronic Transformers. IEEE Trans. Power Electron. 2019, 34, 5294–5311. [Google Scholar] [CrossRef]

- Wang, W.; Gao, X.; Fan, B.; Zeng, X.; Yao, G. Faulty Phase Detection Method under Single-Line-to-Ground Fault Considering Distributed Parameters Asymmetry and Line Impedance in Distribution Networks. IEEE Trans. Power Deliv. 2022, 37, 1513–1522. [Google Scholar] [CrossRef]

- Zeng, X.; Xu, Y.; Wang, Y. Some Novel Techniques for Insulation Parameters Measurement and Petersen-Coil Control in Distribution Systems. IEEE Trans. Ind. Electron. 2010, 57, 1445–1451. [Google Scholar] [CrossRef]

- Fan, B.; Yao, G.; Yu, K.; Zeng, X.; Wang, W.; Zhuo, C.; Guerrero, J. Principle of Flexible Ground-Fault Arc Suppression Device Based on Zero-Sequence Voltage Regulation. IEEE Access 2021, 9, 2382–2389. [Google Scholar] [CrossRef]

- Zheng, Z.; Guo, M.; Yang, N.; Jin, T. Flexible Arc-Suppression Method Based on Improved Distributed Commutations Modulation for Distribution Networks. Int. J. Electr. Power Energy Syst. 2020, 116, 105580. [Google Scholar] [CrossRef]

- Zhou, X.; Lu, S. An Arc-Suppression Method Based on the Coordinated Operation of the Petersen Coil and the Static Synchronous Compensator in Distribution Networks. Trans. China Electr. Soc. 2019, 34, 1251–1262. [Google Scholar]

- You, J.; Guo, M. Integrated Converter with Reactive Power Compensation and Fault Suppression and Its Control Strategy. Power Syst. Technol. 2022, 46, 2241–2248. [Google Scholar]

- Koyama, Y.; Nakazawa, Y.; Mochikawa, H.; Kuzumaki, A.; Sano, K.; Okada, N. A Transformerless 6.6-kV STATCOM Based on a Hybrid Cascade Multilevel Converter Using SiC Devices. IEEE Trans. Power Electron. 2018, 33, 7411–7423. [Google Scholar] [CrossRef]

- Wang, H.; Zhang, J.; Xia, X.; Gao, F.; Cheng, J. DC-Link Capacitance Design for Cascaded H-Bridge STATCOM With Sum of Squares Formulation. IEEE Trans. Power Electron. 2024, 39, 5733–5749. [Google Scholar] [CrossRef]

- Zhao, G.; Guo, M.; Zhang, B.; Zheng, Z.; Hong, Q. Cascaded H-Bridge Converter-Based Flexible Arc Suppression Method Adapting to Line Parameter Variations. IEEE Trans. Power Electron. 2025, 40, 11809–11819. [Google Scholar] [CrossRef]

- Pang, R.; Ding, W. Series Arc Fault Characteristics and Detection Method of a Photovoltaic System. Energies 2023, 16, 8016. [Google Scholar] [CrossRef]

- Cong, H.; Wang, Y.; Hu, X.; Zhang, X.; Su, W.; Li, Q. Simulation Study on the Suppression Effect on Secondary Arcs Based on Online Injection Power Compensation. IEEE Trans. Power Deliv. 2025, 40, 878–888. [Google Scholar] [CrossRef]

- Guo, C.; Guo, M. Quasi-PR Control Based Flexible Arc Suppression Method in Power Distribution Networks. In Proceedings of the 2020 IEEE 1st China International Youth Conference on Electrical Engineering (CIYCEE), Wuhan, China, 1–4 November 2020; pp. 1–7. [Google Scholar]

- Qiu, W.; Guo, M.; Yang, G.; Zheng, Z. Model-Predictive-Control-Based Flexible Arc-Suppression Method for Earth Fault in Distribution Networks. IEEE Access 2019, 7, 16051–16065. [Google Scholar] [CrossRef]

- Huang, Z.; Guo, Q.; Tu, C.; Hou, Y.; Jiang, F.; Wang, X.; Xiao, F.; Xiao, Z. A Non-neutral Alternate Arc Suppression Method for Single Phase Grounding Fault in Active Distribution Network. Int. J. Electr. Power Energy Syst. 2023, 152, 109182. [Google Scholar] [CrossRef]

- Chen, Y.; Lu, S.; Zhou, X.; Liang, S. Two-Phase Current Injection Method for Single Line-to-Ground Fault Arc-Suppression with Revised STATCOM. IEEE Access. 2020, 8, 188299–188308. [Google Scholar] [CrossRef]

- Hou, Y.; Guo, Q.; Tu, C.; Jiang, F.; Wang, L.; Wang, X. Adaptive Active Voltage-Type Arc Suppression Strategy Considering the Influence of Line Parameters in Active Distribution Network. IEEE Trans. Ind. Electron. 2023, 70, 4799–4808. [Google Scholar] [CrossRef]

- Bains, T.P.S.; Sidhu, T.S.; Xu, Z.; Voloh, I.; Zadeh, M.R.D. Impedance-Based Fault Location Algorithm for Ground Faults in Series-Capacitor-Compensated Transmission Lines. IEEE Trans. Power Deliv. 2018, 33, 189–199. [Google Scholar] [CrossRef]

| The Range of θ | Pinva | Pinvb | Pinvc |

|---|---|---|---|

| 0 ≤ θ < 30° | + | + | 0 |

| θ = 30° | + | 0 | 0 |

| 30° < θ ≤ 60° | + | − | 0 |

| Contrast Type | Scheme I | Scheme II | P-Q Arc Suppression Method |

|---|---|---|---|

| Cost | Low | High | Low |

| The effect of arc suppression | Little | Great | Great |

| Complexity | Medium | Low | Medium |

| Parameters | Values | Parameters | Values |

|---|---|---|---|

| Distribution network voltage (kV) | 10 | Filter inductance (mH) | 5 |

| Ground resistance (kΩ) | 30 | Active power of load (MW) | 1 |

| Ground capacitance (uF) | 10 | Power factor of load | 0.97 |

| Ground-fault resistance (Ω) | 1 | DC-link capacitance (mF) | 3 |

| Arc suppression inductance (mH) | 330 | Number of cascaded modules | 5 |

| Proportional coefficient of the power loop | 0.0175 | Integral coefficient of the power loop | 15 |

| Proportional coefficient of the stabilizing loop | 0.2 | Integral coefficient of the stabilizing loop | 20 |

| Proportional coefficient of the current loop | 5 | Integral coefficient of the current loop | 30 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Liu, H.; Huang, Z.; Zhang, C.; Guo, Q.; Yang, J. A P-Q Arc Suppression Method Based on DC-Link Voltage Stability for Hybrid Multifunctional Arc Suppression Devices. Energies 2025, 18, 4278. https://doi.org/10.3390/en18164278

Liu H, Huang Z, Zhang C, Guo Q, Yang J. A P-Q Arc Suppression Method Based on DC-Link Voltage Stability for Hybrid Multifunctional Arc Suppression Devices. Energies. 2025; 18(16):4278. https://doi.org/10.3390/en18164278

Chicago/Turabian StyleLiu, Hongwen, Zejun Huang, Chunli Zhang, Qi Guo, and Jindong Yang. 2025. "A P-Q Arc Suppression Method Based on DC-Link Voltage Stability for Hybrid Multifunctional Arc Suppression Devices" Energies 18, no. 16: 4278. https://doi.org/10.3390/en18164278

APA StyleLiu, H., Huang, Z., Zhang, C., Guo, Q., & Yang, J. (2025). A P-Q Arc Suppression Method Based on DC-Link Voltage Stability for Hybrid Multifunctional Arc Suppression Devices. Energies, 18(16), 4278. https://doi.org/10.3390/en18164278