The Influence of Switching Frequency on Control in Voltage Source Inverters

Abstract

1. Introduction

2. Design of the Experimental Voltage Source Inverter

3. Measuring the VSI Properties

4. Discrete Model of the VSI

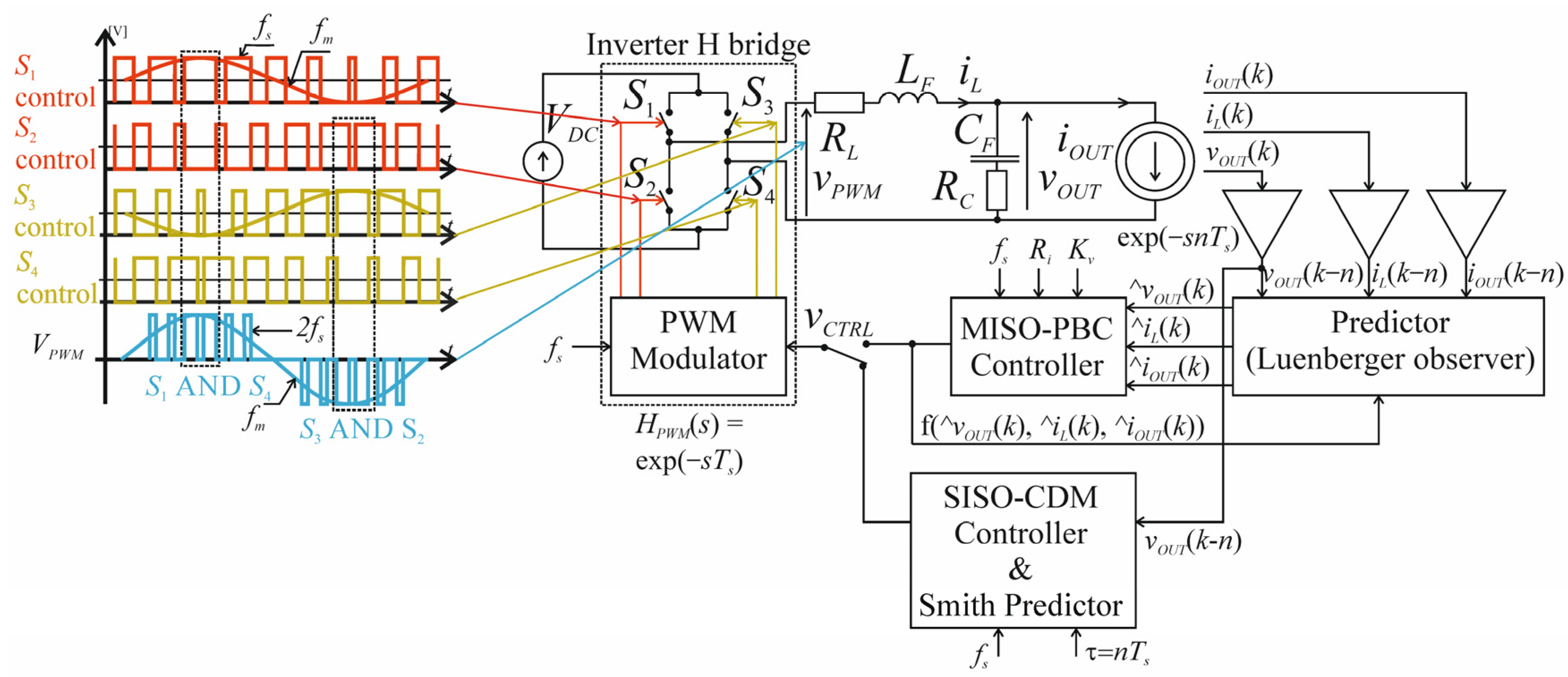

5. SISO-CDM Control of VSI

6. The MISO-PBC Controller of VSI

7. The Experimental Verification

8. Discussion

9. Conclusions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Van der Broeck, H.W.; Miller, M. Harmonics in DC to AC converters of single-phase uninterruptible power supplies. In Proceedings of the 17th International Telecommunications Energy Conference 1995 (INTELEC’ 95), The Hague, The Netherlands, 29 October–1 November 1995; pp. 653–658. [Google Scholar]

- Bernacki, K.; Rymarski, Z. Electromagnetic compatibility of voltage source inverters for uninterruptible power supply system depending on the pulse-width modulation scheme. IET Power Electronics 2015, 8, 1026–1034. [Google Scholar] [CrossRef]

- Rymarski, Z. Improving Low-Frequency Digital Control in the Voltage Source Inverter for the UPS System. Electronics 2024, 13, 1469. [Google Scholar] [CrossRef]

- Bertotti, G. General properties of power losses in soft ferromagnetic materials. IEEE Trans. Magn. 1988, 24, 621–630. [Google Scholar] [CrossRef]

- Bernacki, K.; Rymarski, Z.; Dyga, Ł. Selecting the coil core powder material for the output filter of a voltage source inverter. Electron. Lett. 2017, 53, 1068–1069. [Google Scholar] [CrossRef]

- Manabe, S. Coeficient diagram method. IFAC Proc. 1998, 31, 211–222. [Google Scholar]

- Manabe, S. Importance of coefficient diagram in polynomial method. In Proceedings of the 42nd IEEE Conference on Decision and Control, Maui, HI, USA, 9–12 December 2003; pp. 3489–3494. [Google Scholar]

- Coelho, J.P.; Pinho, T.M.; Boaventura-Cunha, J. Controller system design using the coefficient diagram method. Arab. J. Sci. Eng. 2016, 41, 3663–3681. [Google Scholar] [CrossRef]

- Ortega, R.; Perez, J.A.L.; Nicklasson, P.J.; Sira-Ramirez, H. Passivity-Based Control of Euler-Lagrange Systems: Mechanical, Electrical and Electromechanical Applications (Communications and Control Engineering); Springer: London, UK, 1998. [Google Scholar]

- Wang, Z.; Goldsmith, P. Modified energy-balancing-based control for the tracking problem. IET Control Theory Appl. 2008, 2, 310–312. [Google Scholar] [CrossRef]

- Ortega, R.; Garcia-Canseco, E. Interconnection and Damping Assignment Passivity-Based Control: A Survey. Eur. J. Control 2004, 5, 432–450. [Google Scholar] [CrossRef]

- Ortega, R.; Garcia-Canseco, E. Interconnection and Damping Assignment Passivity-Based Control: Towards a Constructive Procedure—Part I. In Proceedings of the 43rd IEEE Conference on Decision and Control, Nassau, Bahamas, 14–17 December 2004; pp. 3412–3417. [Google Scholar] [CrossRef]

- Ortega, R.; Espinosa-Perez, G. Passivity-based control with simultaneous energy-shaping and damping injection: The induction motor case study. IFAC Proc. 2005, 38, 477–482. [Google Scholar] [CrossRef]

- Komurcugil, H. Improved passivity-based control method and its robustness analysis for single-phase uninterruptible power supply inverters. IET Power Electron. 2015, 8, 1558–1570. [Google Scholar] [CrossRef]

- Serra, F.M.; De Angelo, C.H.; Forchetti, D.G. IDA-PBC control of a DC-AC converter for sinusoidal three-phase voltage generation. Int. J. Electron. 2017, 104, 93–110. [Google Scholar] [CrossRef]

- Rymarski, Z.; Bernacki, K. Technical Limits of Passivity-Based Control Gains for a Single-Phase Voltage Source Inverter. Energies 2021, 14, 4560. [Google Scholar] [CrossRef]

- Rymarski, Z. Design Method of Single-Phase Inverters for UPS Systems. Int. J. Electron. 2009, 96, 521–535. [Google Scholar] [CrossRef]

- Micrometals Alloy Powder Core Catalog. 2021. Available online: https://micrometals.com/design-and-applications/literature/ (accessed on 10 June 2024).

- Rymarski, Z. Measuring the real parameters of single-phase voltage source inverters for UPS systems. Int. J. Electron. 2017, 104, 1020–1033. [Google Scholar] [CrossRef]

- Rymarski, Z.; Bernacki, K.; Dyga, Ł. Measuring the power conversion losses in voltage source inverters. AEU-Int. J. Electron. Commun. 2020, 124, 153359. [Google Scholar] [CrossRef]

- Kawamura, A.; Chuarayapratip, R.; Haneyoshi, T. Deadbeat control of PWM inverter with modified pulse patterns for uninterruptible power supply. IEEE Trans. Ind. Electron. 1988, 35, 295–300. [Google Scholar] [CrossRef]

- Rymarski, Z. The discrete model of the power stage of the voltage source inverter for UPS. Int. J. Electron. 2011, 98, 1291–1304. [Google Scholar] [CrossRef]

- Ben-Brahim, L.; Yokoyama, T.; Kawamura, A. Digital control for UPS inverters. In Proceedings of the Fifth International Conference on Power Electronics and Drive Systems, PEDS 2003, Singapore, 17–20 November 2003; Volume 2, pp. 1252–1257. [Google Scholar]

- Deng, H.; Srinivasan, D.; Oruganti, R. Modeling and control of single-phase UPS inverters: A survey. In Proceedings of the International Conference on Power Electronics and Drives Systems, PEDS 2005, Kuala Lumpur, Malaysia, 28 November–1 December 2005; Volume 2, pp. 848–853. [Google Scholar]

- Borsalani, J.; Dastfan, A. Decoupled phase voltages control of three phase four-leg voltage source inverter via state feedback. In Proceedings of the 2012 2nd International eConference on Computer and Knowledge Engineering (ICCKE), Mashhad, Iran, 18–19 October 2012; pp. 71–76. [Google Scholar] [CrossRef]

- Moon, S.; Choe, J.M.; Lai, J.S. Design of a state-space controller employing a deadbeat state observer for ups inverters. In Proceedings of the 2017 Asian Conference on Energy, Power and Transportation Electrification (ACEPT), Singapore, 24–26 October 2017; pp. 1–6. [Google Scholar] [CrossRef]

- Hu, C.; Wang, Y.; Luo, S.; Zhang, F. State-space model of an inverter-based micro-grid. In Proceedings of the 2018 3rd International Conference on Intelligent Green Building and Smart Grid (IGBSG), Yilan, Taiwan, 22–25 April 2018; pp. 1–7. [Google Scholar] [CrossRef]

- Ali, M.S.; Hou, Z.K.; Noori, M.N. Stability and performance of feedback control systems with time delays. Comput. Struct. 1998, 66, 241–248. [Google Scholar] [CrossRef]

- Mousa-Abadian, M.; Momeni-Masuleh, S.H.; Haeri, M. Stabilization of linear time-delayed systems by delayed feedback. Comput. Methods Differ. Equ. 2019, 7, 302–318. Available online: https://cmde.tabrizu.ac.ir/article_8553.html (accessed on 9 April 2024).

- Deng, Y.; Léchappé, V.; Moulay, E.; Chen, Z.; Liang, B.; Plestan, F.; Han, Q.L. Predictor-based control of time-delay systems: A survey. Int. J. Syst. Sci. 2022, 53, 2496–2534. [Google Scholar] [CrossRef]

- Gomez, M.; You, S.; Murray, R.M. Time-Delayed Feedback Channel Design: Discrete Time H∞ Approach. In Proceedings of the 2014 American Control Conference (ACC), Portland, OR, USA, 4–6 June 2014; Available online: http://www.cds.caltech.edu/~murray/papers/gym14-acc.html (accessed on 14 June 2024).

- Sipahi, R.; Niculescu, S.I.; Abdallah, C.; Michiels, W.; Gu, K. Stability and Stabilization of Systems with Time Delay. IEEE Control Syst. Mag. 2011, 31, 38–65. [Google Scholar]

- Levine, W.S.; Reyhanoglu, M. The Control Handbook. In Control System Fudamentals; CRC Press Taylor & Francis Group: Boca Raton, FL, USA, 2010; ISBN 9781420073645. [Google Scholar]

- de Bosio, F.; Ribeiro, L.A.D.S.; Freijedo, F.D.; Pastorelli, M.; Guerrero, J.M. Discrete-Time Domain Modeling of Voltage Source Inverters in Standalone Applications: Enhancement of Regulators Performance by Means of Smith Predictor. IEEE Trans. Power Electron. 2017, 32, 8100–8114. [Google Scholar] [CrossRef]

- Wang, Z.; Zhou, K.; Li, S.; Yang, Y. Fractional-order time delay compensation in deadbeat control for power converters. In Proceedings of the 2018 IEEE International Power Electronics and Application Conference and Exposition (PEAC), Shenzhen, China, 4–7 November 2018; pp. 1–6. [Google Scholar] [CrossRef]

- Khefifi, N.; Houari, A.; Ait-Ahmed, M.; Machmoum, M.; Ghanes, M. Robust IDA-PBC based Load Voltage Controller for Power Quality Enhancement of Standalone Microgrids. In Proceedings of the IEEE IECON 2018—44th Annual Conference of the IEEE Industrial Electronics Society, Washington, DC, USA, 21–23 October 2018; pp. 249–254. [Google Scholar] [CrossRef]

- Rymarski, Z.; Bernacki, K. Different Features of Control Systems for Single-Phase Voltage Source Inverters. Energies 2020, 13, 4100. [Google Scholar] [CrossRef]

- Luenberger, D.G. Observing the state of a linear system. IEEE Trans. Mil. Electron. 1964, 8, 74–80. [Google Scholar] [CrossRef]

- Luenberger, D.G. An introduction to observers. IEEE Trans. Autom. Control 1971, 16, 596–602. [Google Scholar] [CrossRef]

- Davis, J.H. Luenberger Observers. In Foundations of Deterministic and Stochastic Control. Systems & Control: Foundations & Applications; Birkhäuser: Boston, MA, USA, 2002; pp. 245–254. [Google Scholar] [CrossRef]

- Montagner, V.F.; Carati, E.G.; Grundling, H.A. An adaptive linear quadratic regulator with repetitive controller applied to uninterruptible power supplies. In Proceedings of the Industry Applications Conference 2000, Rome, Italy, 8–12 October 2000; Volume 4, pp. 2231–2236. [Google Scholar]

- Saoudi, M.; Hani, B.; Aissa, C. Efficient Deadbeat Control of Single-Phase Inverter with Observer for High Performance Applications. Przeglad Elektrotechniczny 2023, 99, 237. [Google Scholar] [CrossRef]

- Fan, H.; Li, Z.; Rodriguez, J.; Wang, B. Model Free Predictive Current Control for Voltage Source Inverter using Luenberger Observer. In Proceedings of the 2023 IEEE International Conference on Predictive Control of Electrical Drives and Power Electronics (PRECEDE), Wuhan, China, 16–19 June 2023; pp. 1–6. [Google Scholar] [CrossRef]

- Heydaridoostabad, H.; Ghazi, R. A new approach to design an observer for load current of UPS based on Fourier series theory in model predictive control system. Int. J. Electr. Power Energy Syst. 2018, 104, 898–909. [Google Scholar] [CrossRef]

- Kawamura, A.; Ishihara, K. Real time digital feedback control of three phase PWM inverter with quick transient response suitable for uninterruptible power supply. In Proceedings of the IEEE Industry Applications Society Annual Meeting, Pittsburgh, PA, USA, 2–7 October 1988; Volume 1, pp. 728–734. [Google Scholar]

- Bernacki, K.; Rymarski, Z. A Contemporary Design Process for Single-Phase Voltage Source Inverter Control Systems. Sensors 2022, 22, 7211. [Google Scholar] [CrossRef]

- IEC 62040-3:2021; Uninterruptible Power Systems (UPS)—Part 3: Method of Specifying the Performance and Test Requirements. IEC: Geneva, Switzerland, 2021.

| fs [Hz] | Open Loop THD | CDM, τ = 3Ts, THD | CDM + Smith P., τ = 3Ts, THD | CDM, τ = 4Ts, THD | CDM + Smith P., τ = 4Ts, THD |

|---|---|---|---|---|---|

| 12,800 | 6.80% | 3.27% | 3.06% | 3.06% | 3.27% |

| 25,600 | 6.80% | 4.27% | 1.83% | 1.10% | 1.88% |

| 51,200 | 6.80% | 1.21% | 0.85% | 0.31% | 0.89% |

| fs [Hz] | Open Loop THD | PBC | PBC + Luenberger Observer (l1 = 1.2, l2 = 1.2, l3 = 0.8) |

|---|---|---|---|

| 12,800 | THD = 6.80% | Ri = 3, Kv = 0.1, THD = 4.65% | Ri = 5, Kv = 0.1 THD = 3.45% |

| 25,600 | THD = 6.80% | Ri = 5, Kv = 0.3, THD = 0.89% | Ri = 5, Kv = 0.3, THD = 1.77% |

| 51,200 | THD = 6.80% | Ri = 20, Kv = 0.3, THD = 0.27% | Ri = 5, Kv = 0.3, THD = 2.34% |

| fs [Hz] | Open Loop THD | CDM | CDM + Smith Predictor (n = 2) |

|---|---|---|---|

| 12,800 | THD = 6.80% | τ = 6, THD = 5.5% | τ = 6, THD = 4.4% |

| 25,600 | THD = 6.80% | τ = 6, THD = 3.1% | τ = 6, THD = 3.6% |

| 51,200 | THD = 6.80% | τ = 8, THD = 1.8% | τ = 8, THD = 2% |

| fs [Hz] | Open Loop THD | PBC | PBC + Luenberger Observer (l1 = 1.2, l2 = 1.2, l3 = 0.8) |

|---|---|---|---|

| 12,800 | THD = 6.80% | Ri = 5, Kv = 0.2, THD = 4.4% | Ri = 15, Kv = 0.4 THD = 3.0% |

| 25,600 | THD = 6.80% | Ri = 10, Kv = 0.3, THD = 2.3% | Ri = 20, Kv = 0.3, THD = 3.1% |

| 51,200 | THD = 6.80% | Ri = 15, Kv = 0.3, THD = 1.9% | Ri = 30, Kv = 0.2, THD = 2.2% |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Rymarski, Z. The Influence of Switching Frequency on Control in Voltage Source Inverters. Energies 2024, 17, 4508. https://doi.org/10.3390/en17174508

Rymarski Z. The Influence of Switching Frequency on Control in Voltage Source Inverters. Energies. 2024; 17(17):4508. https://doi.org/10.3390/en17174508

Chicago/Turabian StyleRymarski, Zbigniew. 2024. "The Influence of Switching Frequency on Control in Voltage Source Inverters" Energies 17, no. 17: 4508. https://doi.org/10.3390/en17174508

APA StyleRymarski, Z. (2024). The Influence of Switching Frequency on Control in Voltage Source Inverters. Energies, 17(17), 4508. https://doi.org/10.3390/en17174508