Dead-Time Free Modulation Scheme for IM Drive System Fed by Voltage Source Inverter

Abstract

1. Introduction

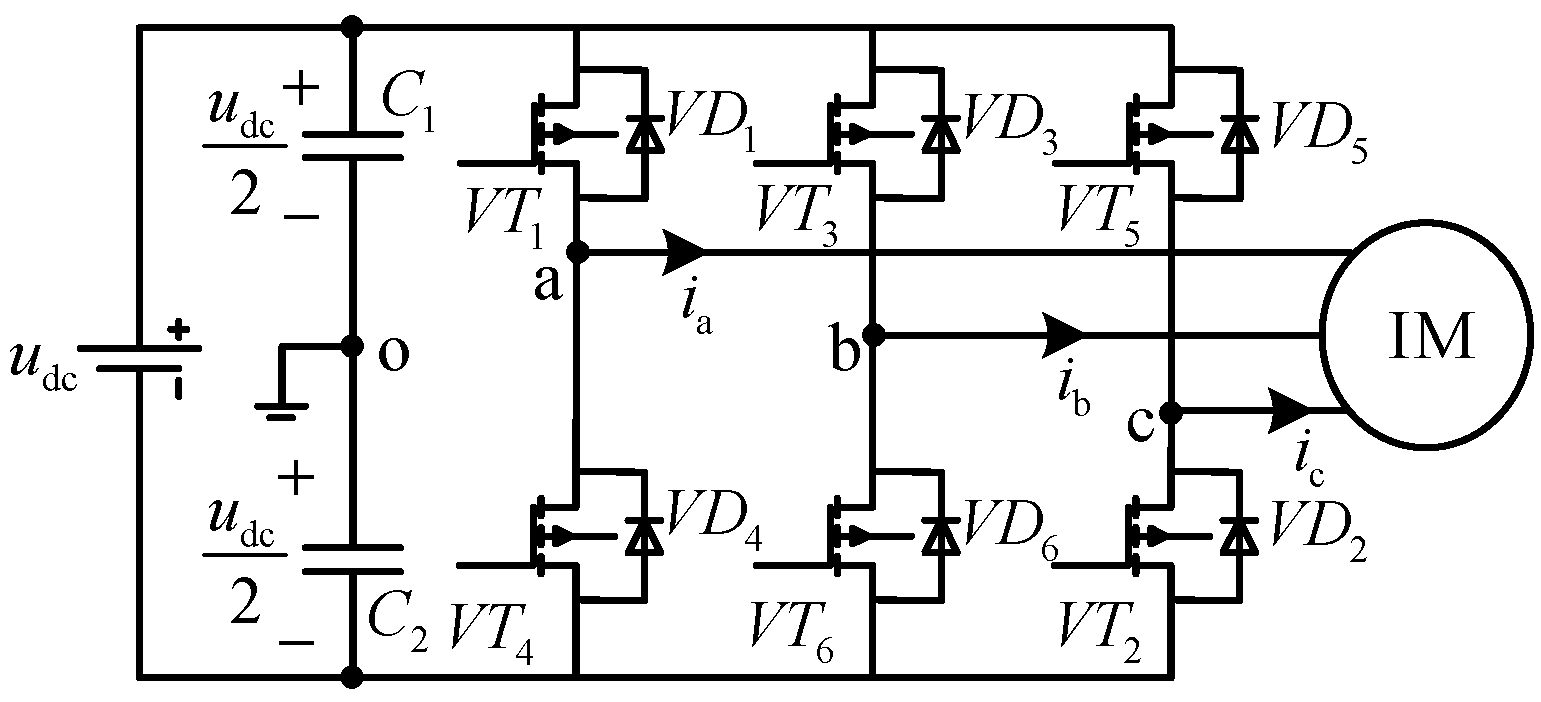

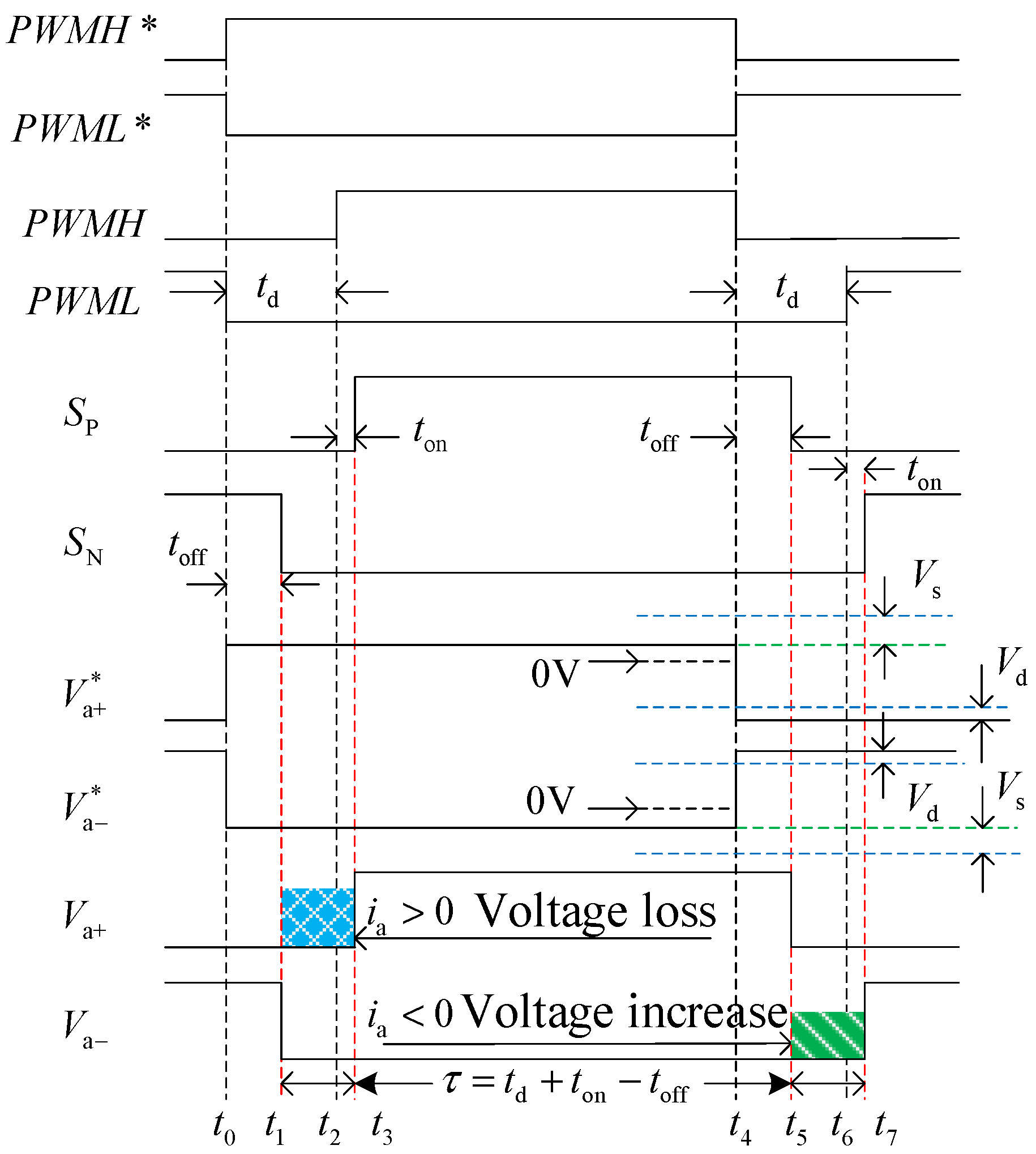

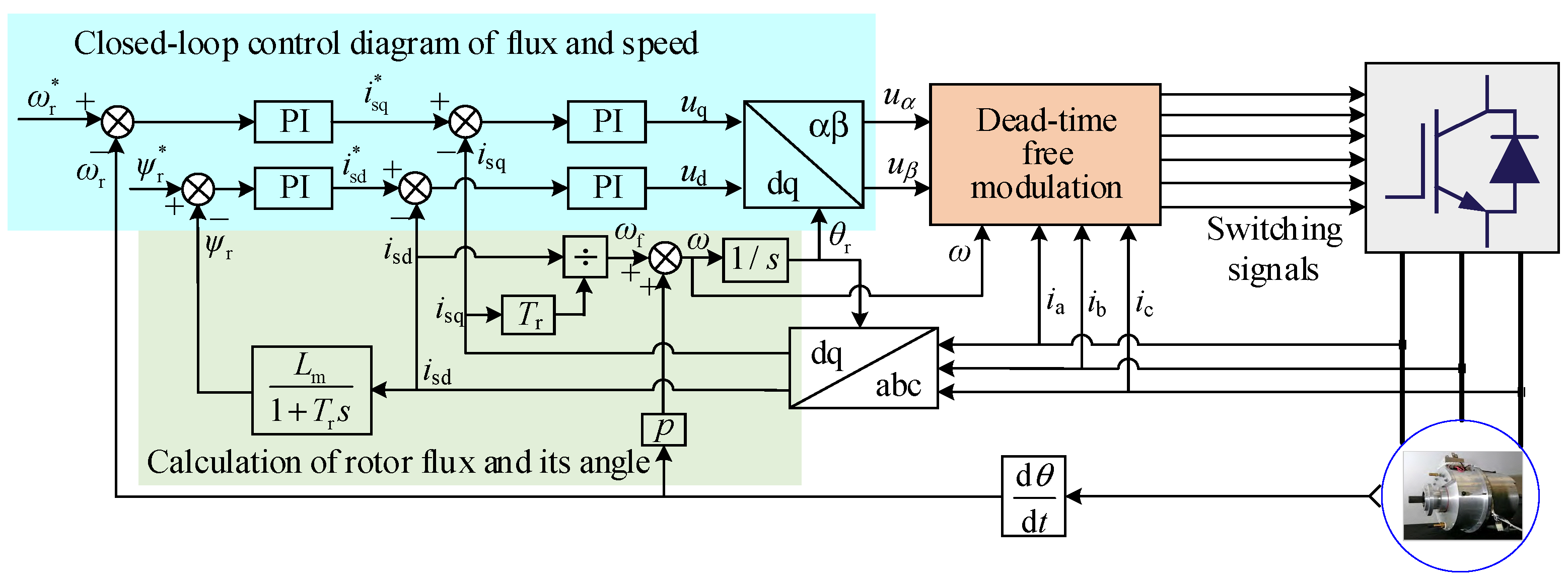

2. Nonlinear Voltage Error Analysis of VSI

2.1. Nonlinear Voltage Error Caused by the Dead-Time and Conduction Voltage Drop

- (1)

- When the phase-A current satisfies ia > 0.

- (2)

- When the phase-A current satisfies ia < 0.

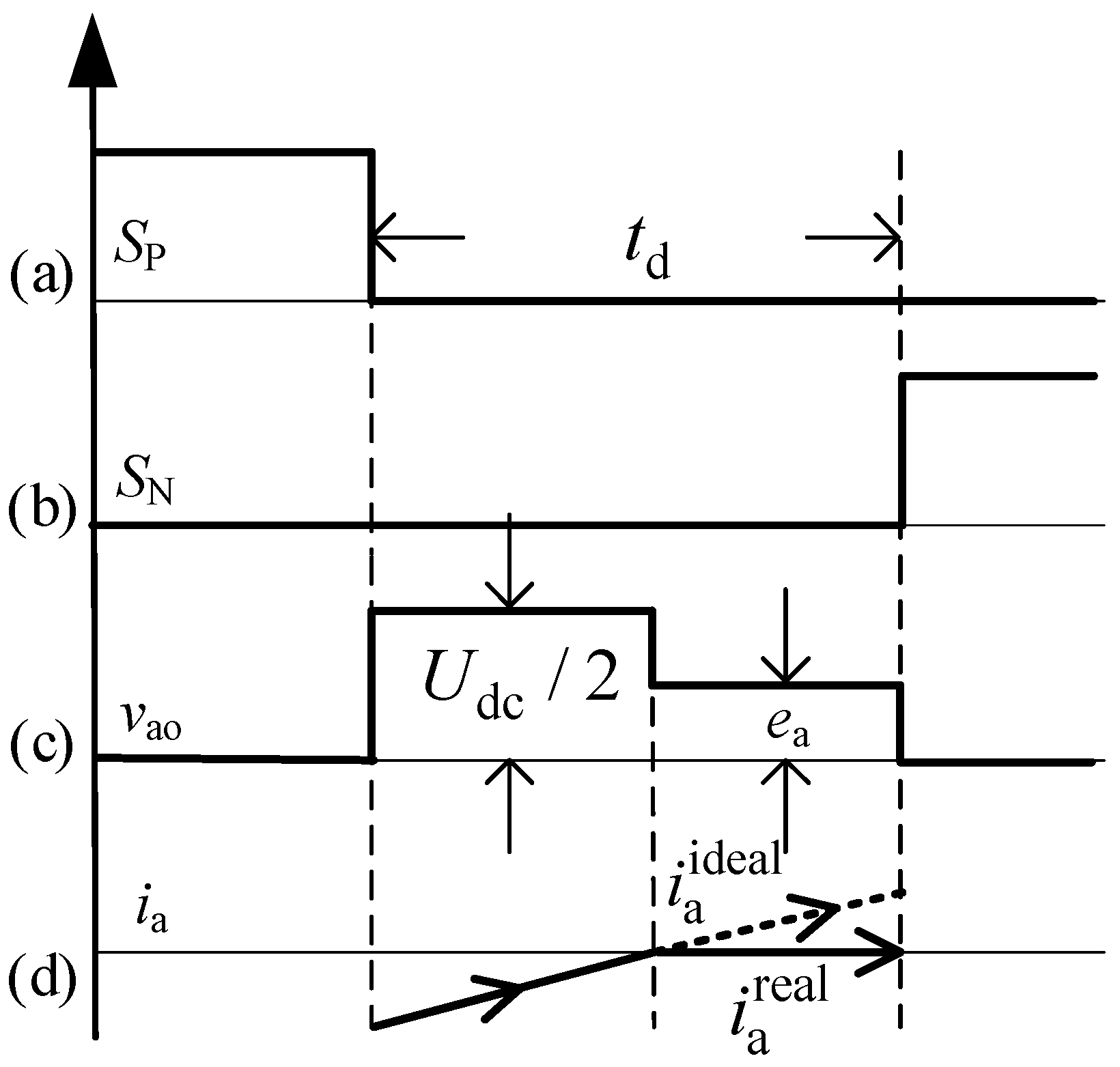

2.2. Zero Current Clamping Effect When the Phase Current Crosses Zero

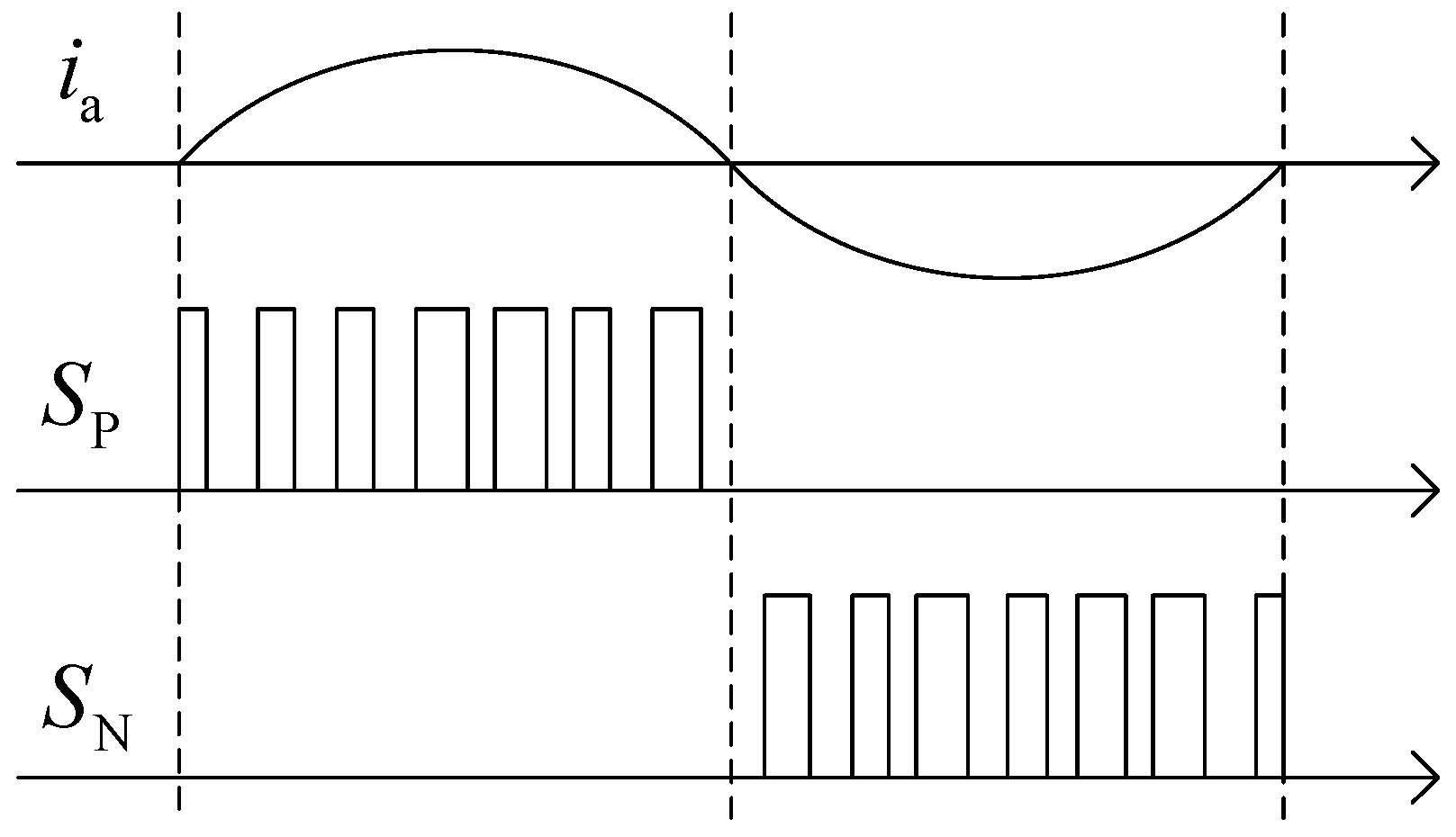

3. Dead-Time Elimination Strategy near Non-Zero Crossing Points

4. Modulation for the Phase Current Crossing Zero in Advance

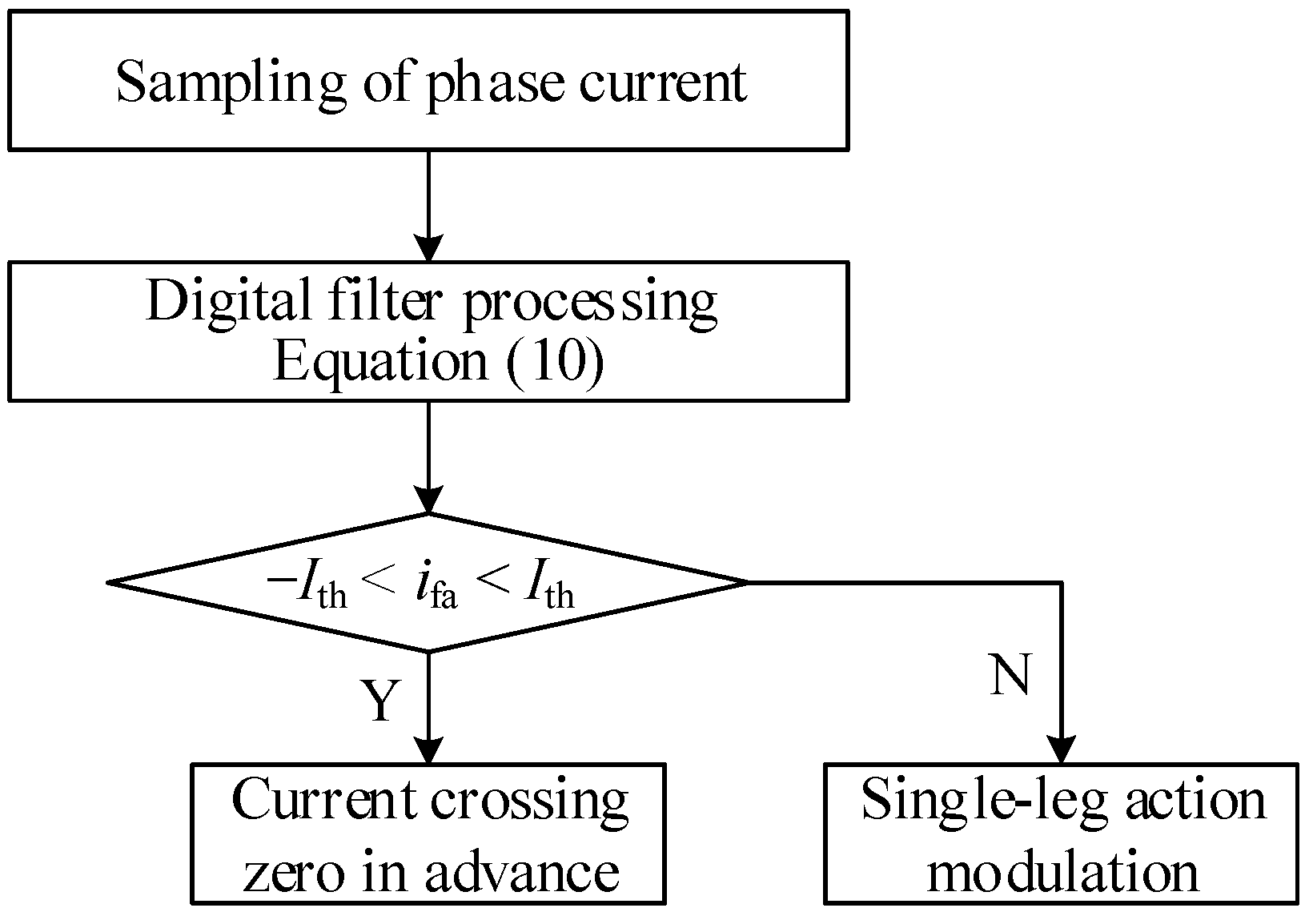

5. Selection Principle of the Two Proposed Modulation Schemes

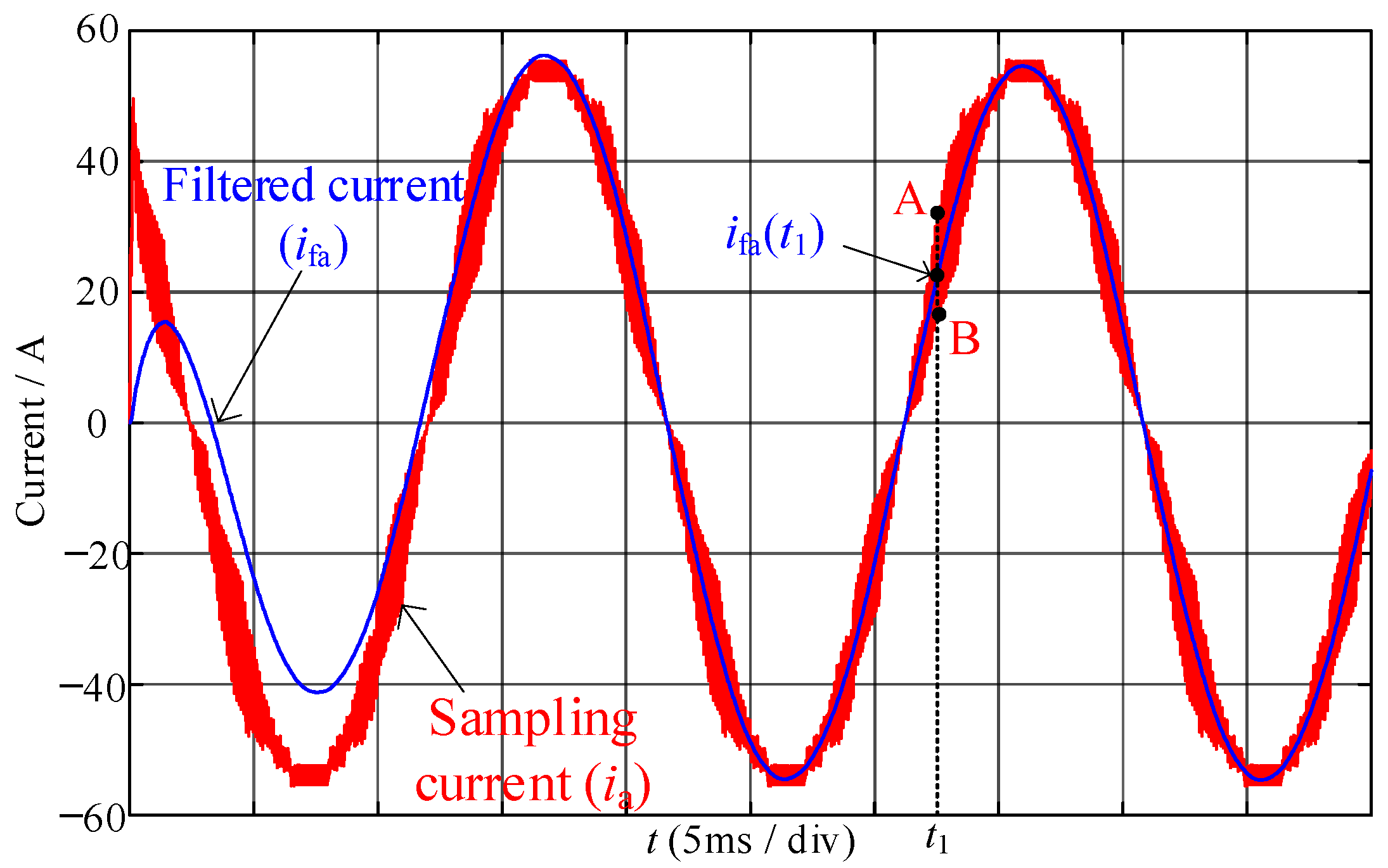

6. Discrete Filtering Processing of the Sampling Current

7. Experimental Results and Analysis

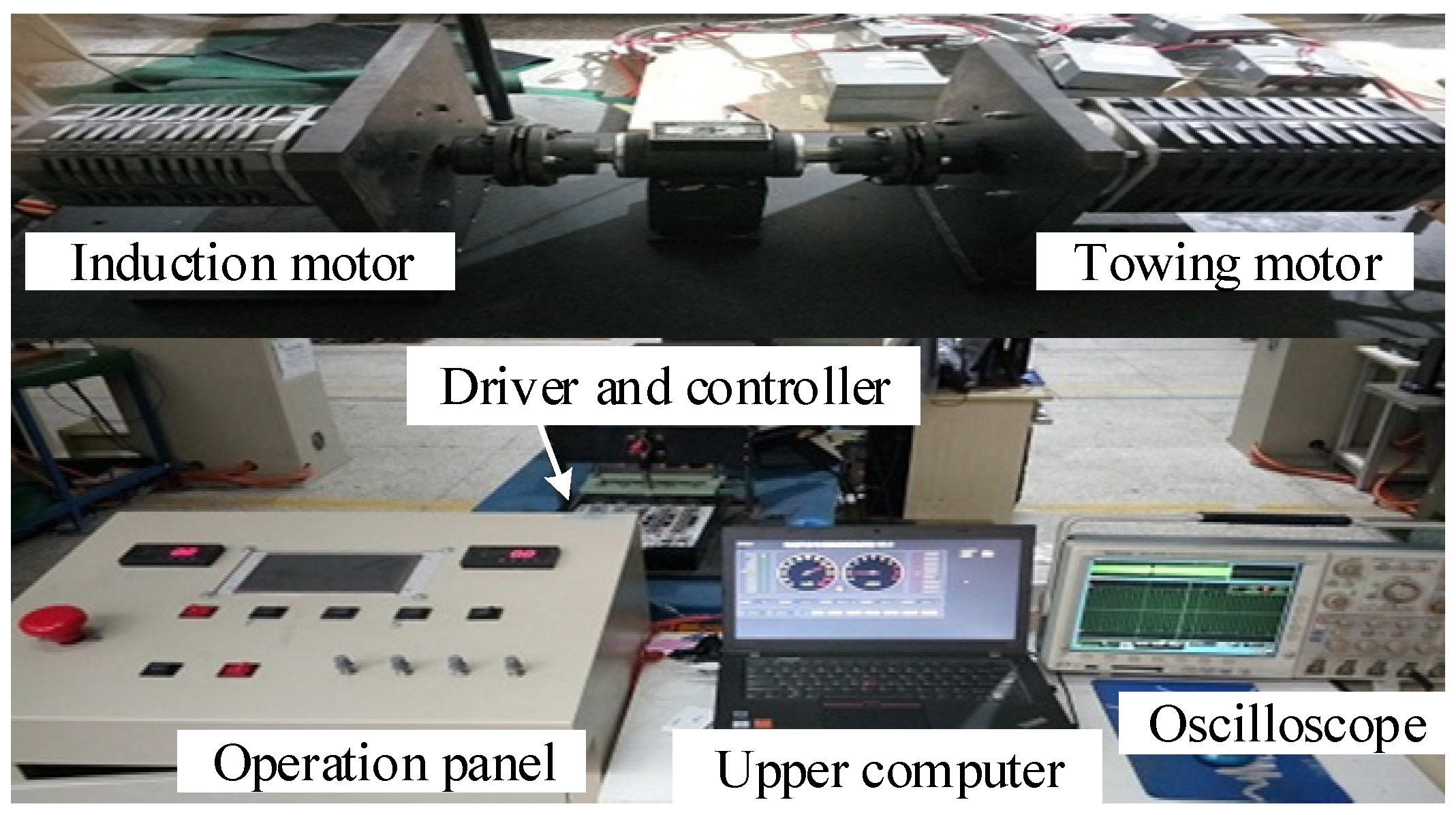

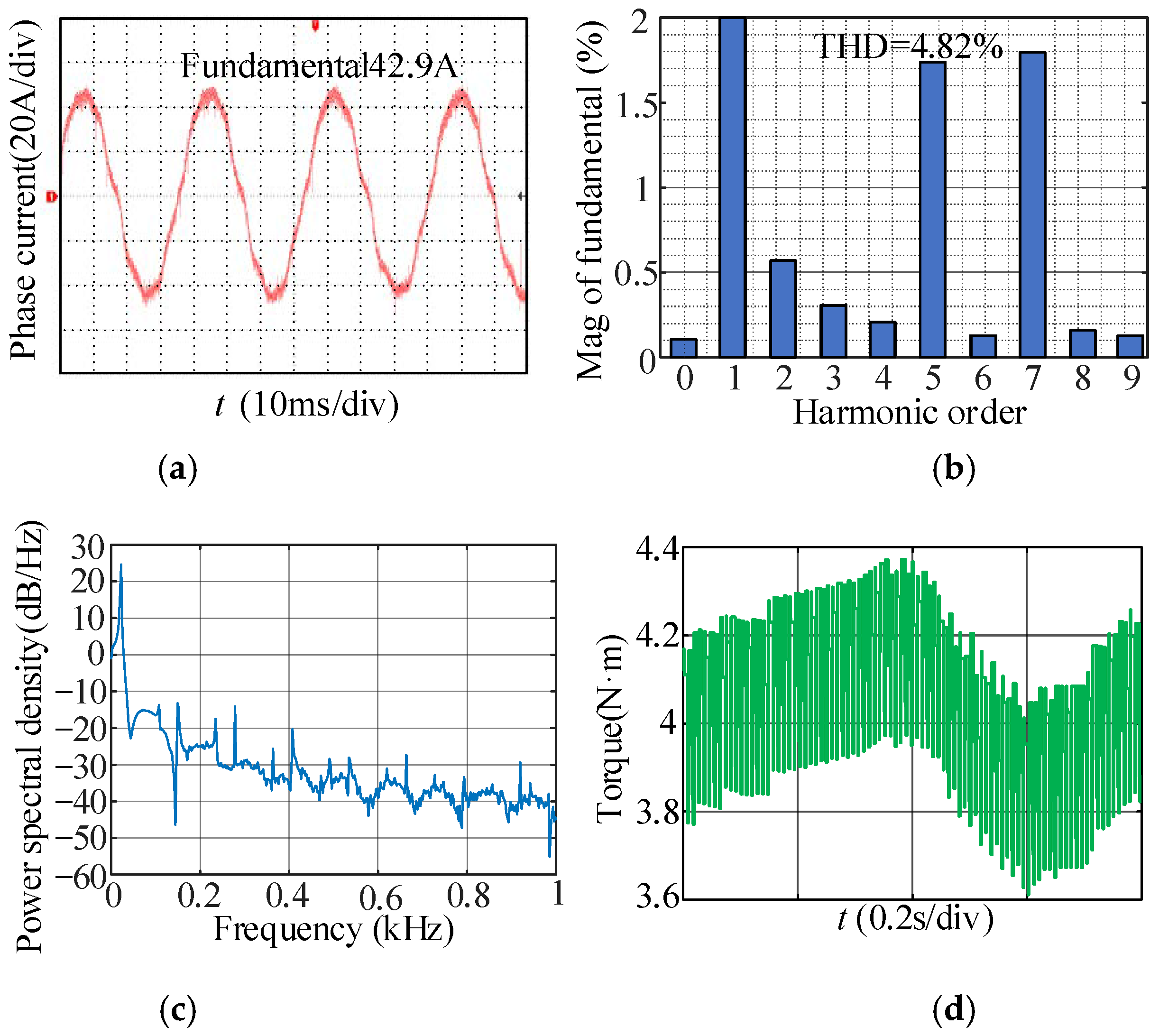

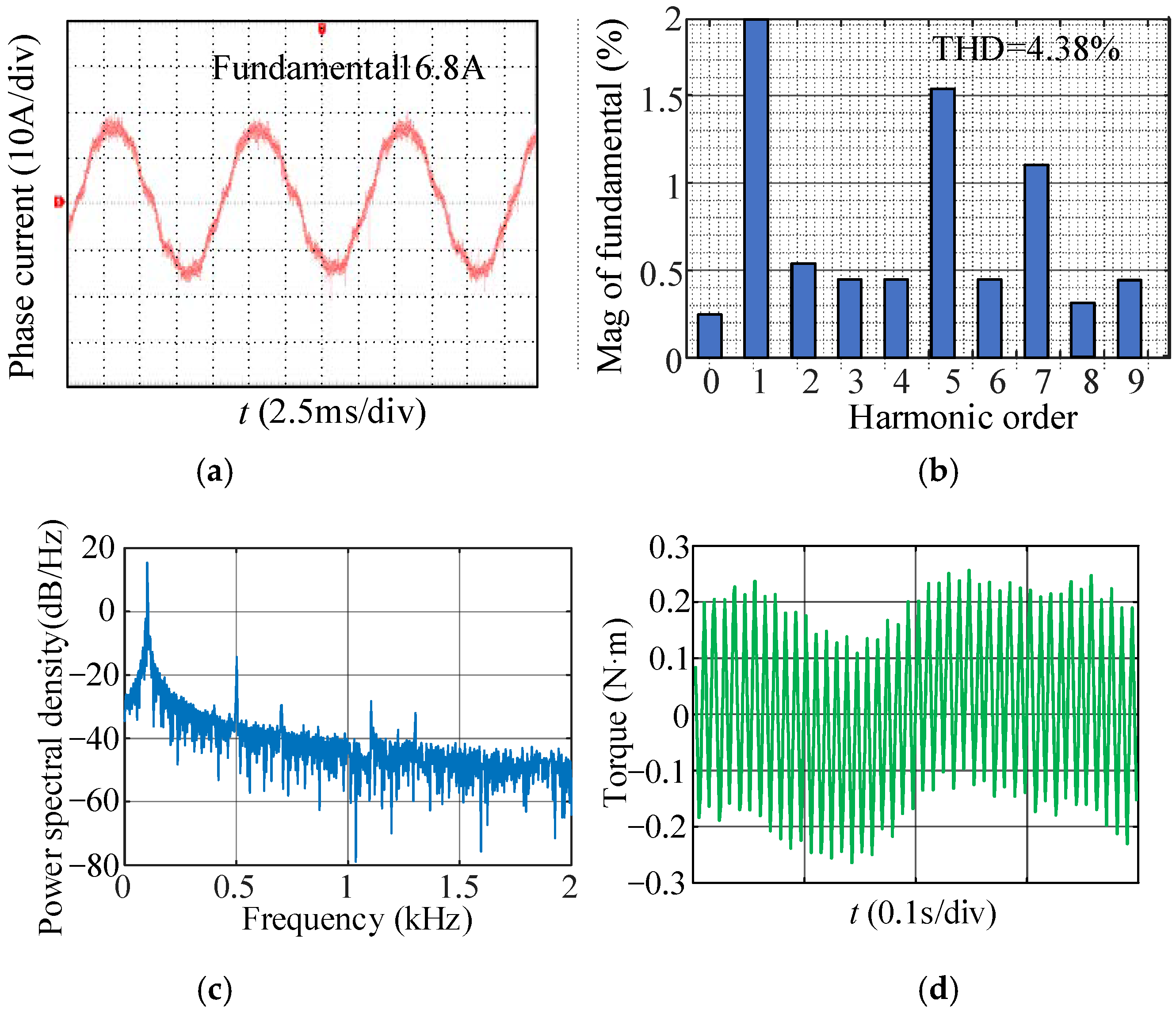

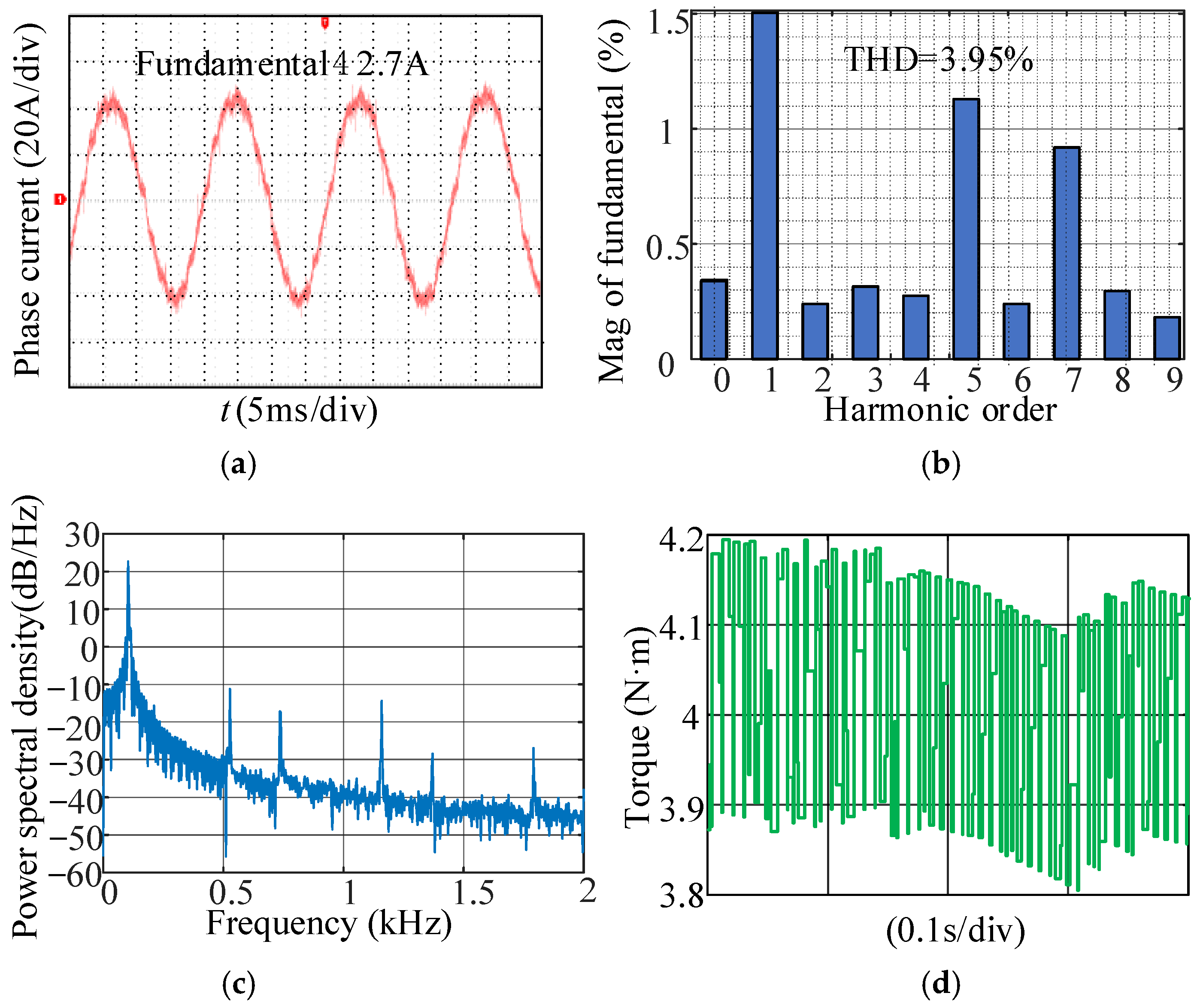

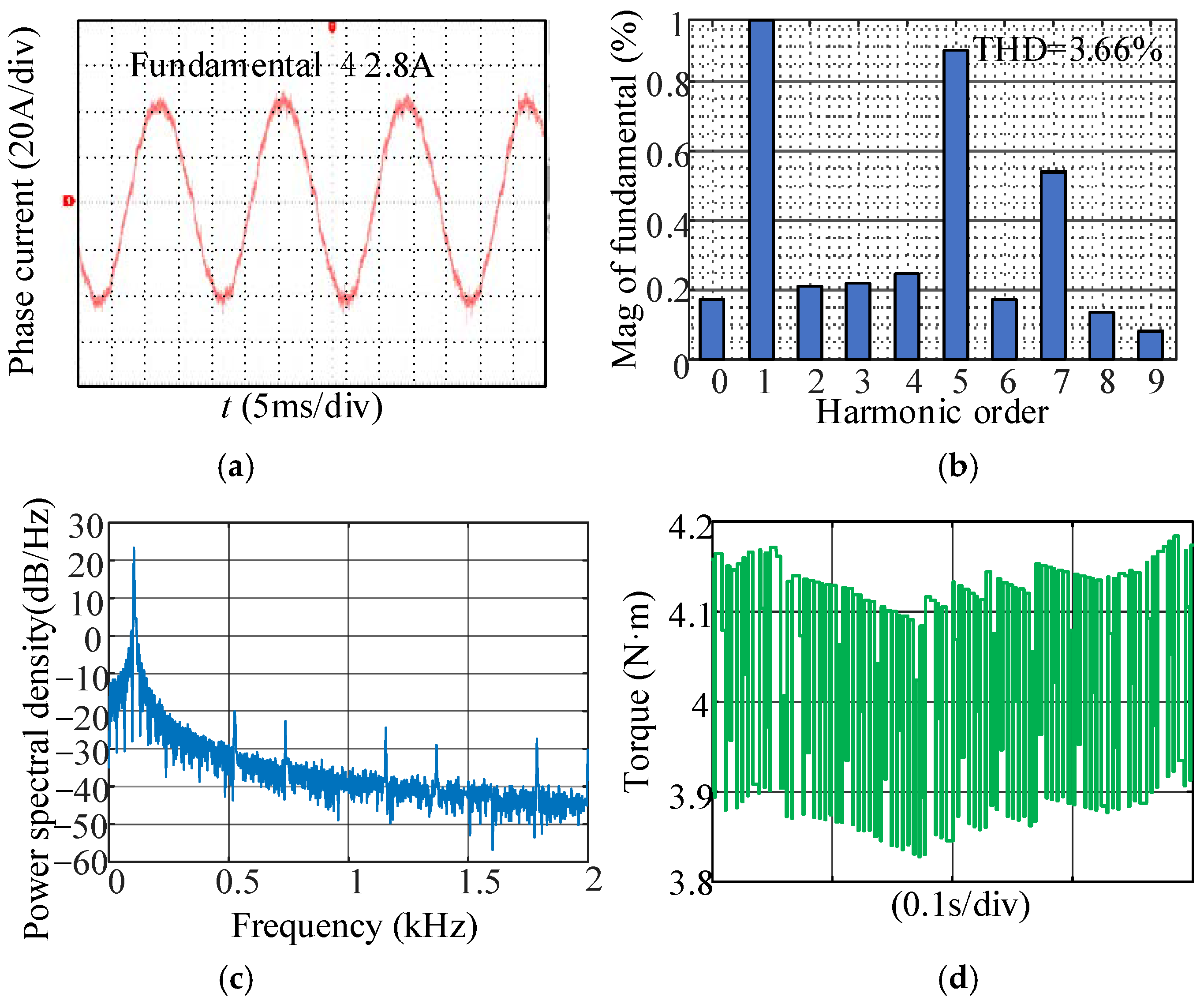

7.1. Experimental Results

7.2. Discussion and Analysis of the Experimental Results

8. Conclusions

- (1)

- In the non-zero crossing region of the phase current, due to only one tube in the upper and lower bridge arms being in action, the deadtime is eliminated. The nonlinear error between the actual output voltage and the ideal voltage is very little, so the fifth and seventh harmonics of the output voltage can be reduced from the root. The fifth and seventh harmonics and the THD in the phase current under the proposed dead-time free modulation are less than those under other compensation schemes, and the torque ripple minimization can be achieved;

- (2)

- Near the zero crossing point, the inverter remains in the switching state that can output the maximum voltage whose polarity is the same as the changing direction of the phase current, which accelerates the phase current crossing zero. Compared to other compensation schemes, this method is more effective in suppressing the zero current clamp effect, and the dead-time is avoided.

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Payarou, T.; Pillay, P. Integrated Multipurpose Power Electronics Interface for Electric Vehicles. IEEE Trans. Transp. Electrif. 2023, 9, 2429–2443. [Google Scholar] [CrossRef]

- Nezamuddin, O.N.; Nicholas, C.L.; Santos, E.C.D. The Problem of Electric Vehicle Charging: State-of-the-Art and an Innovative Solution. IEEE Trans. Intell. Transp. Syst. 2022, 23, 4663–4673. [Google Scholar] [CrossRef]

- Dong, Z.; Song, Z.; Wang, W.; Liu, C. Improved Zero-Sequence Current Hysteresis Control-Based Space Vector Modulation for Open-End Winding PMSM Drives with Common DC Bus. IEEE Trans. Ind. Electron. 2023, 70, 10755–10760. [Google Scholar] [CrossRef]

- Diao, N.; Sun, X.; Song, C.; Zhang, Q.; Zhang, Z. A Multimodulation Times SVPWM for Dead-Time Effect Elimination in Three-Level Neutral Point Clamped Converters. IEEE Trans. Ind. Electron. 2021, 68, 5476–5485. [Google Scholar] [CrossRef]

- Zhou, Y.; Wang, Z.; Xin, G.; Yuan, J.; Shi, X. Dead Time Optimization for Synchronous Switching of SiC MOSFETs Considering Nonlinear Gate Capacitance. IEEE Trans. Power Electron. 2023, 38, 5665–5669. [Google Scholar] [CrossRef]

- Arandhakar, S.; Jayaram, N.; Shankar, Y.R.; Gaurav; Kishore, P.S.V.; Halder, S. Emerging Intelligent Bidirectional Charging Strategy Based on Recurrent Neural Network Accosting EMI and Temperature Effects for Electric Vehicle. IEEE Access 2022, 10, 121741–121761. [Google Scholar] [CrossRef]

- Feng, W.; Zhang, W.; Huang, S. A Novel Parameter Estimation Method for PMSM by Using Chaotic Particle Swarm Optimization with Dynamic Self-Optimization. IEEE Trans. Veh. Technol. 2023, 72, 8424–8432. [Google Scholar] [CrossRef]

- Hwang, S.H.; Kim, J.M. Dead time compensation method for voltage-fed PWM inverter. IEEE Trans. Energy Convers. 2010, 25, 1–10. [Google Scholar] [CrossRef]

- Zhang, Z.; Xu, L. Dead-Time Compensation of Inverters Considering Snubber and Parasitic Capacitance. IEEE Trans. Power Electron. 2014, 29, 3179–3187. [Google Scholar] [CrossRef]

- Xu, C.; Liu, P.; Liu, T.; Miao, Y.R. Overlap Time Compensation and Characteristic Analysis for Current Source Photovoltaic Grid-Connected Inverter. Energies 2024, 17, 1768. [Google Scholar] [CrossRef]

- Lee, J.-H.; Sul, S.-K. Inverter Nonlinearity Compensation Through Deadtime Effect Estimation. IEEE Trans. Power Electron. 2021, 36, 10684–10694. [Google Scholar] [CrossRef]

- Wang, L.; Xu, J.; Chen, Q.; Chen, Z.; Huang, R. An Improved Trapezoidal Voltage Method for Dead-Time Compensation in Three-Phase Voltage Source Converter. IEEE Trans. Power Electron. 2022, 37, 8785–8789. [Google Scholar] [CrossRef]

- Liao, Y.; Zhen, S.; Liu, R.; Yao, J. Torque ripple suppression of permanent magnet synchronous motor by the harmonic injection. Proc. CSEE 2011, 31, 119–127. [Google Scholar]

- Song, P.Y.; Liu, Y.H.; Liu, T.; Wang, H.; Wang, L. A Novel Suppression Method for Low-Order Harmonics Causing Resonance of Induction Motor. Machines 2022, 10, 1206. [Google Scholar] [CrossRef]

- Xu, Y.; Zheng, B.; Wang, G.; Yan, H.; Zou, J. Current Harmonic Suppression in Dual Three-Phase Permanent Magnet Synchronous Machine with Extended State Observer. IEEE Trans. Power Electron. 2020, 35, 12166–12180. [Google Scholar] [CrossRef]

- Hu, M.; Hua, W.; Cheng, C.; Wang, Y.; Lu, C. Discrete-Time Frequency-Domain Disturbance Observer to Mitigate Harmonic Current in PMSM Drives and the Implementation with Reduced Delay. IEEE Trans. Power Electron. 2023, 38, 9482–9493. [Google Scholar] [CrossRef]

- Choi, C.-H.; Seok, J.-K. Pulsating Signal Injection-Based Axis Switching Sensorless Control of Surface-Mounted Permanent-Magnet Motors for Minimal Zero-Current Clamping Effects. IEEE Trans. Ind. Appl. 2008, 44, 1741–1748. [Google Scholar] [CrossRef]

- Xu, F.; Liu, J.; Zhang, X. Analysis of Deadtime Effects and Optimum Deadtime Control for Bidirectional Inductive Power Transfer Converters. IEEE Trans. Ind. Electron. 2024, 71, 6929–6937. [Google Scholar] [CrossRef]

- Feng, W.; Zhang, W.; Miao, Y.; Huang, S.; Yang, S. Low Frequency Resonance Reduction Method of Induction Motor Used by Electric Vehicle Based on Sixth Harmonic Suppression in dq Coordinate. Trans. China Electrotech. Soc. 2023, 38, 6632–6645. [Google Scholar]

| Category | Part Number | Parameters |

|---|---|---|

| DC power supply | PR300-4 | 72 V |

| Switching tubes (IGBT) | IPB042N10N | 100 V/100 A |

| Current sensors | MLX91205 | / |

| Digital signal controller | TMS320F28035 | / |

| Encoder | OIH | 2500 C/T |

| Parameters | Value |

|---|---|

| Rated voltage/frequence/power | 72 V/50 Hz/1.5 kW |

| Rated torque/speed | 4 N·m/1500 r/min |

| Stator resistance, rotor resistance | 0.047 Ω, 0.028 Ω |

| Stator leakage inductance, rotor leakage inductance | 81.46 μH, 81.27 μH |

| Magnetic inductance | 2.29 mH |

| Moment of inertia | 0.0164 kg·m2 |

| Number of pole pairs | 2 |

| Tube conduction voltage drop | 0.5 V |

| Body diode conduction voltage drop | 0.7 V |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Xu, Q.; Yi, L.; Long, X.; Luo, L.; Miao, Y. Dead-Time Free Modulation Scheme for IM Drive System Fed by Voltage Source Inverter. Energies 2024, 17, 3845. https://doi.org/10.3390/en17153845

Xu Q, Yi L, Long X, Luo L, Miao Y. Dead-Time Free Modulation Scheme for IM Drive System Fed by Voltage Source Inverter. Energies. 2024; 17(15):3845. https://doi.org/10.3390/en17153845

Chicago/Turabian StyleXu, Qiwei, Liangwu Yi, Xuehan Long, Lingyan Luo, and Yiru Miao. 2024. "Dead-Time Free Modulation Scheme for IM Drive System Fed by Voltage Source Inverter" Energies 17, no. 15: 3845. https://doi.org/10.3390/en17153845

APA StyleXu, Q., Yi, L., Long, X., Luo, L., & Miao, Y. (2024). Dead-Time Free Modulation Scheme for IM Drive System Fed by Voltage Source Inverter. Energies, 17(15), 3845. https://doi.org/10.3390/en17153845