A Review of Non-Isolated High-Gain Y-Source Converters Topologies

Abstract

1. Introduction

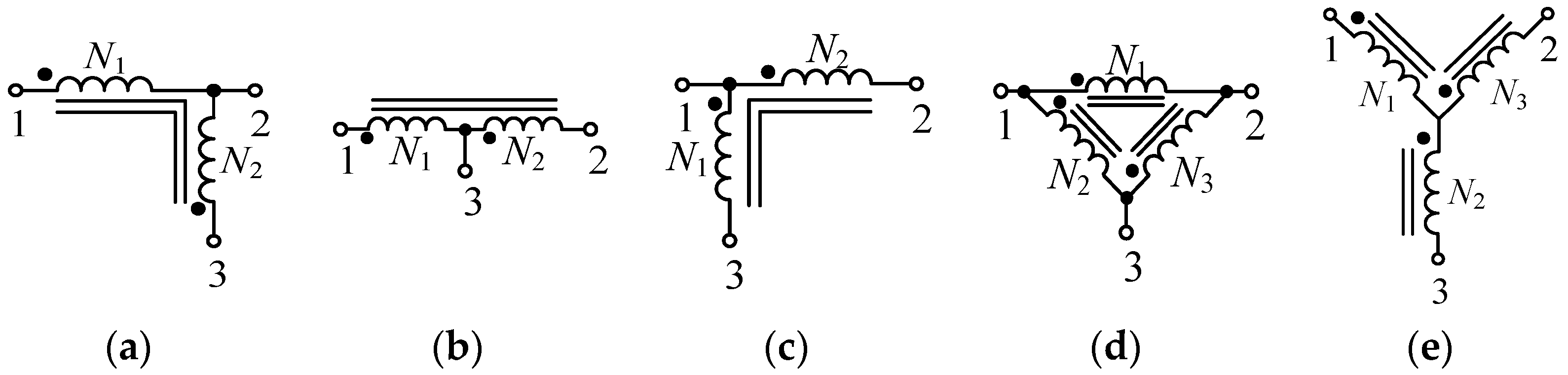

2. Basic Topology of Y-Source Converters

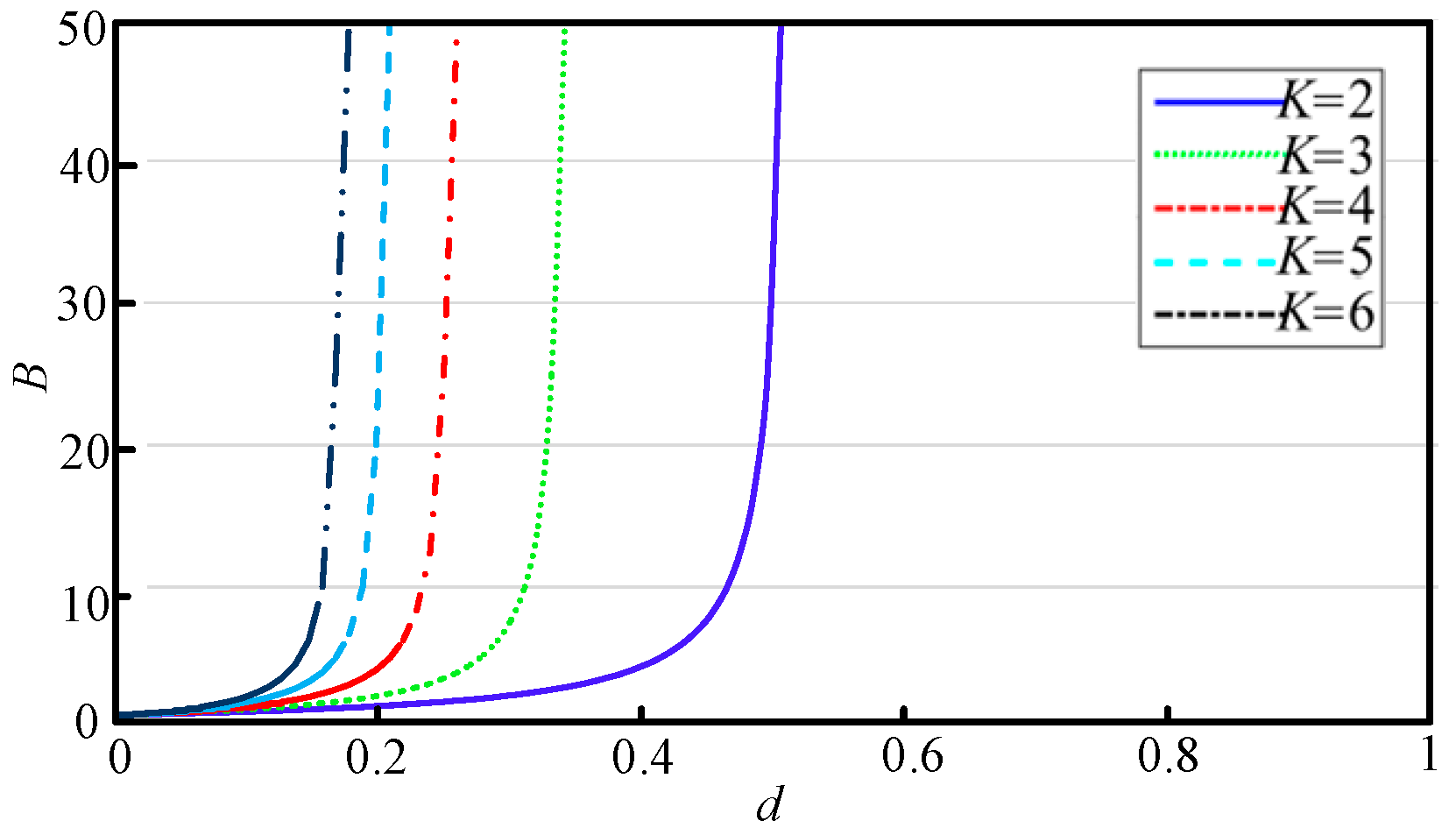

2.1. Traditional Y-Source Converter (YSC)

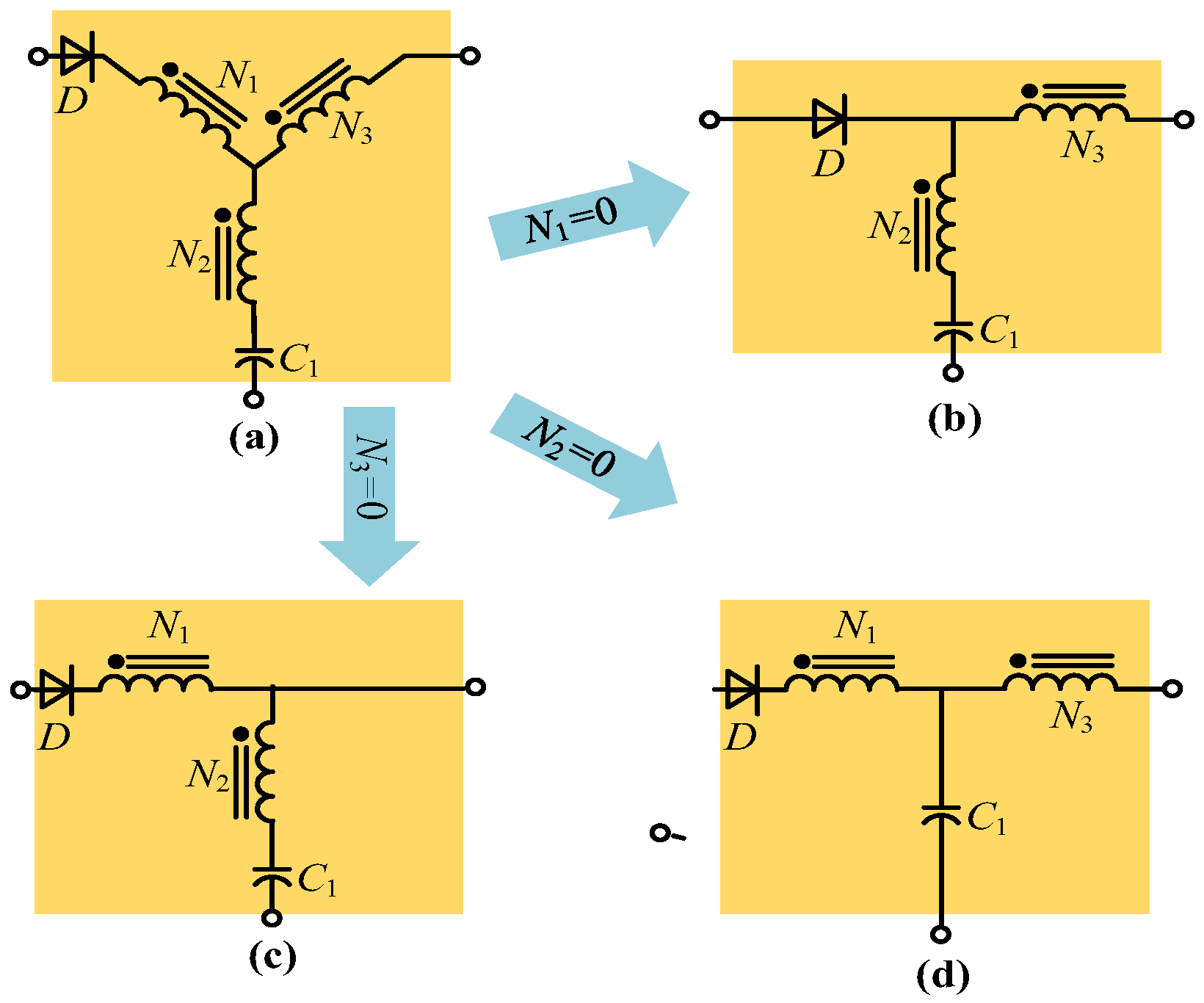

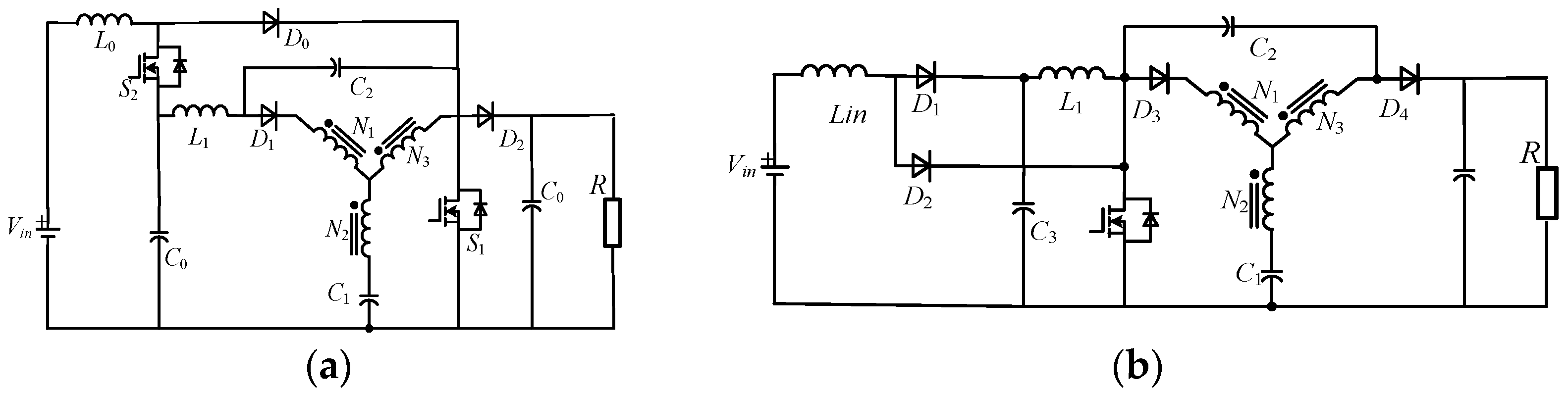

2.2. Quasi Y-Source Converters (qYSCs)

2.3. Modified Y-Source Converter (M-YSC)

2.4. Properties Comparison among Different Impedance Source Networks

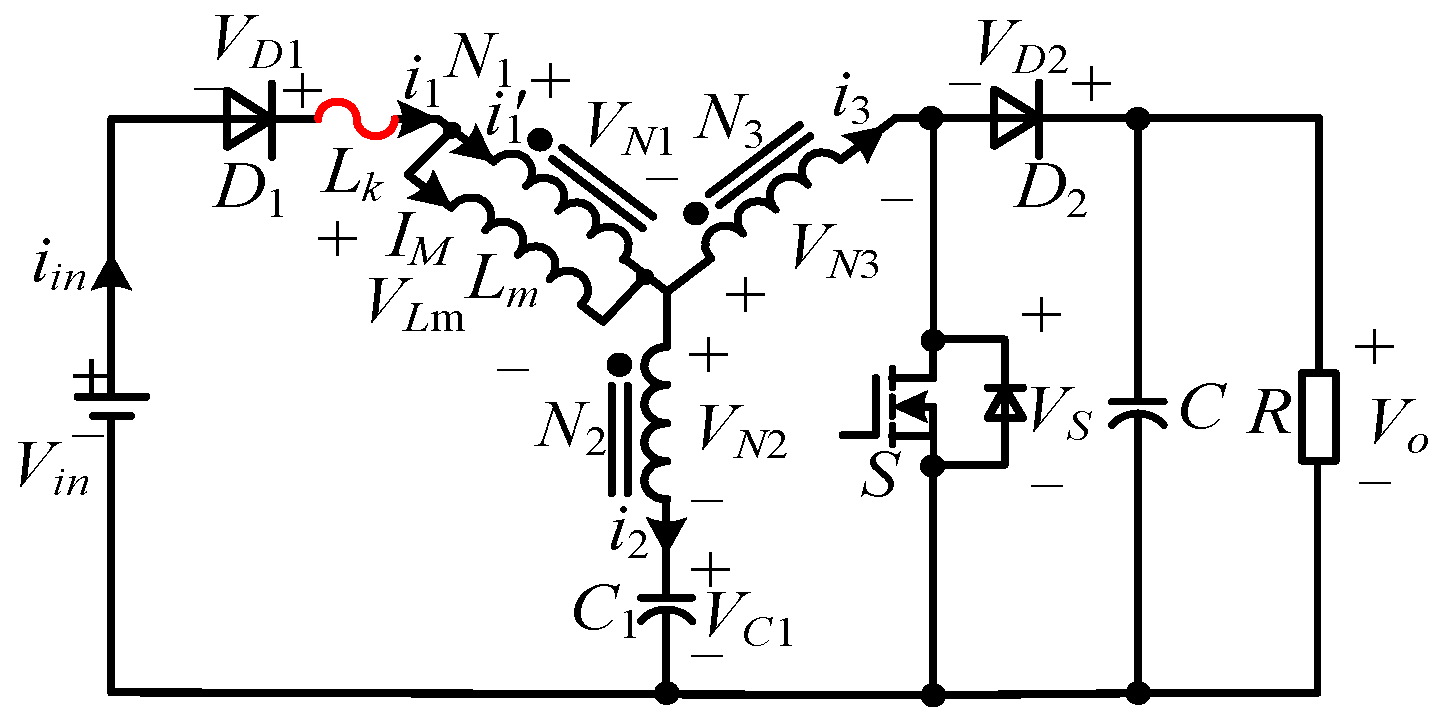

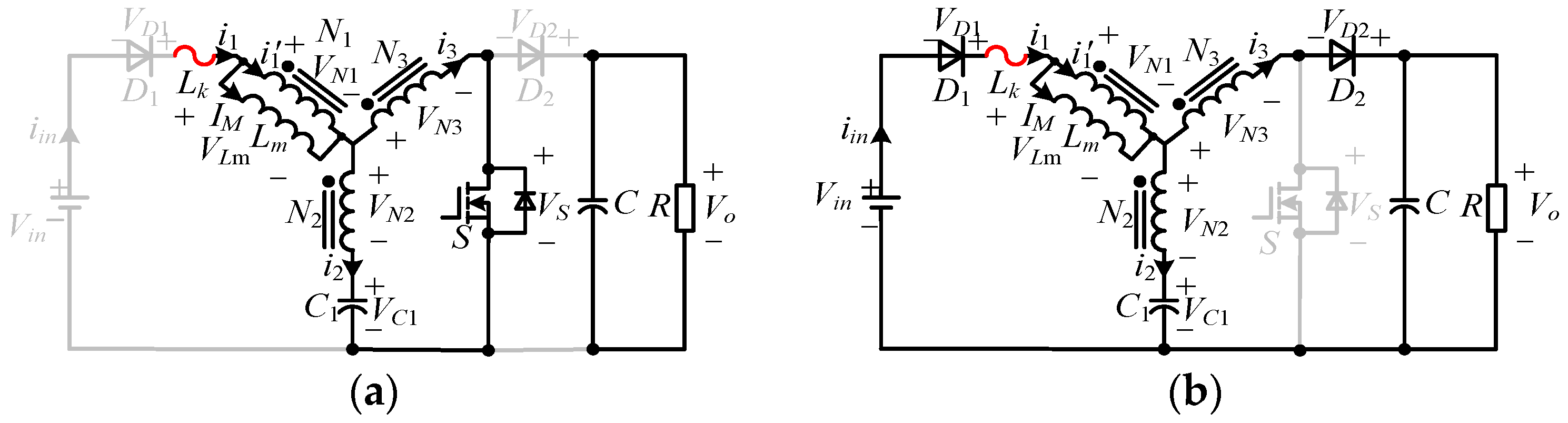

3. Effects of Leakage Inductances on Y-Source Network

3.1. The Analysis of the Effects of Leakage Inductances

3.2. The Low-Voltage-Overshoot Y-Source Converters

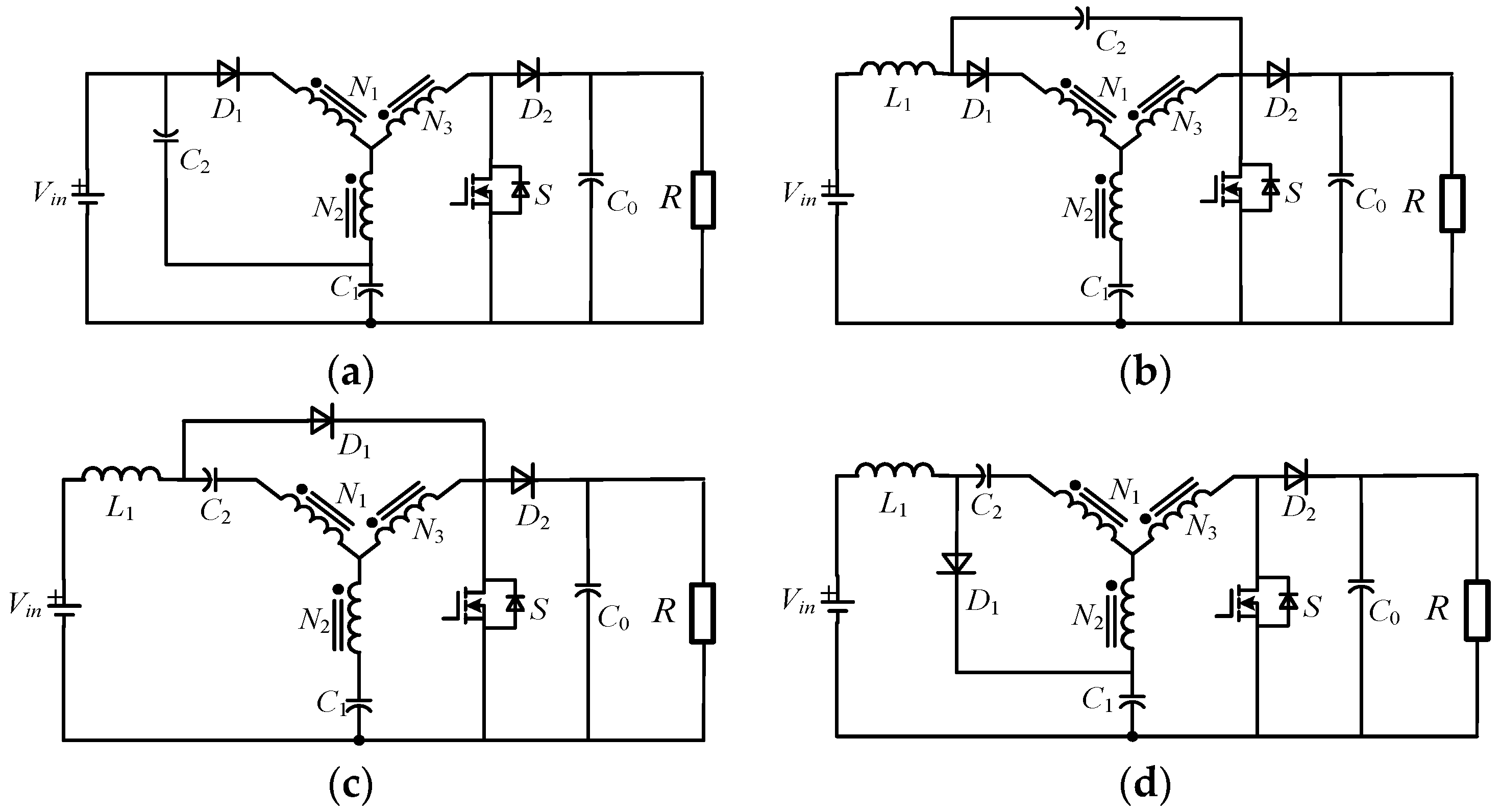

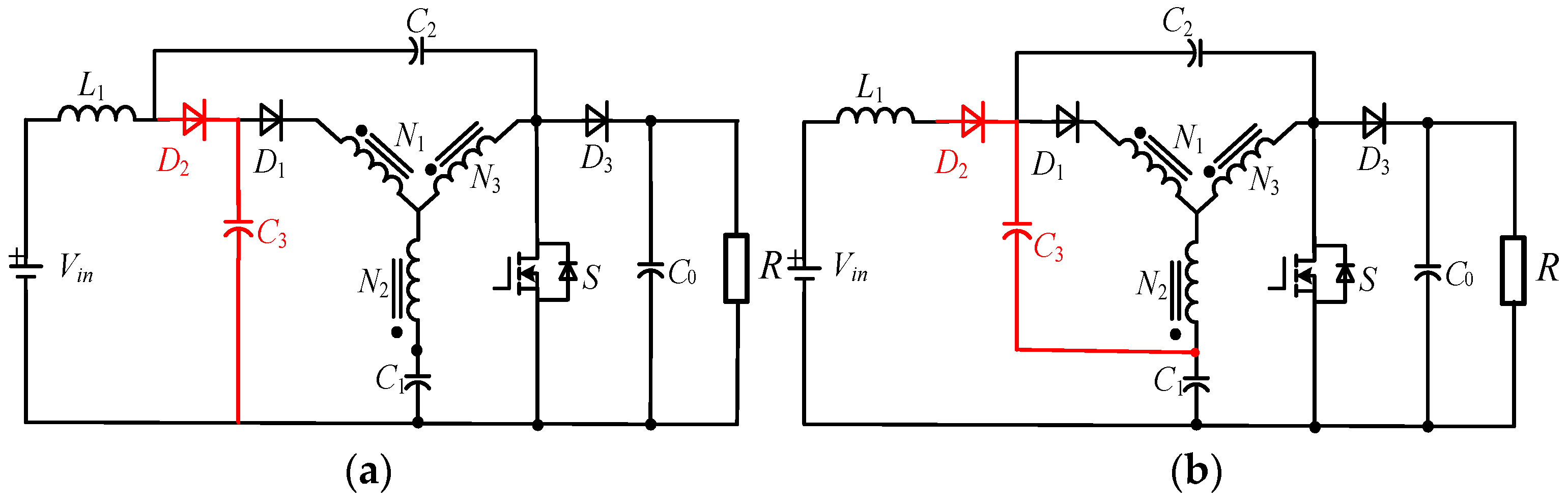

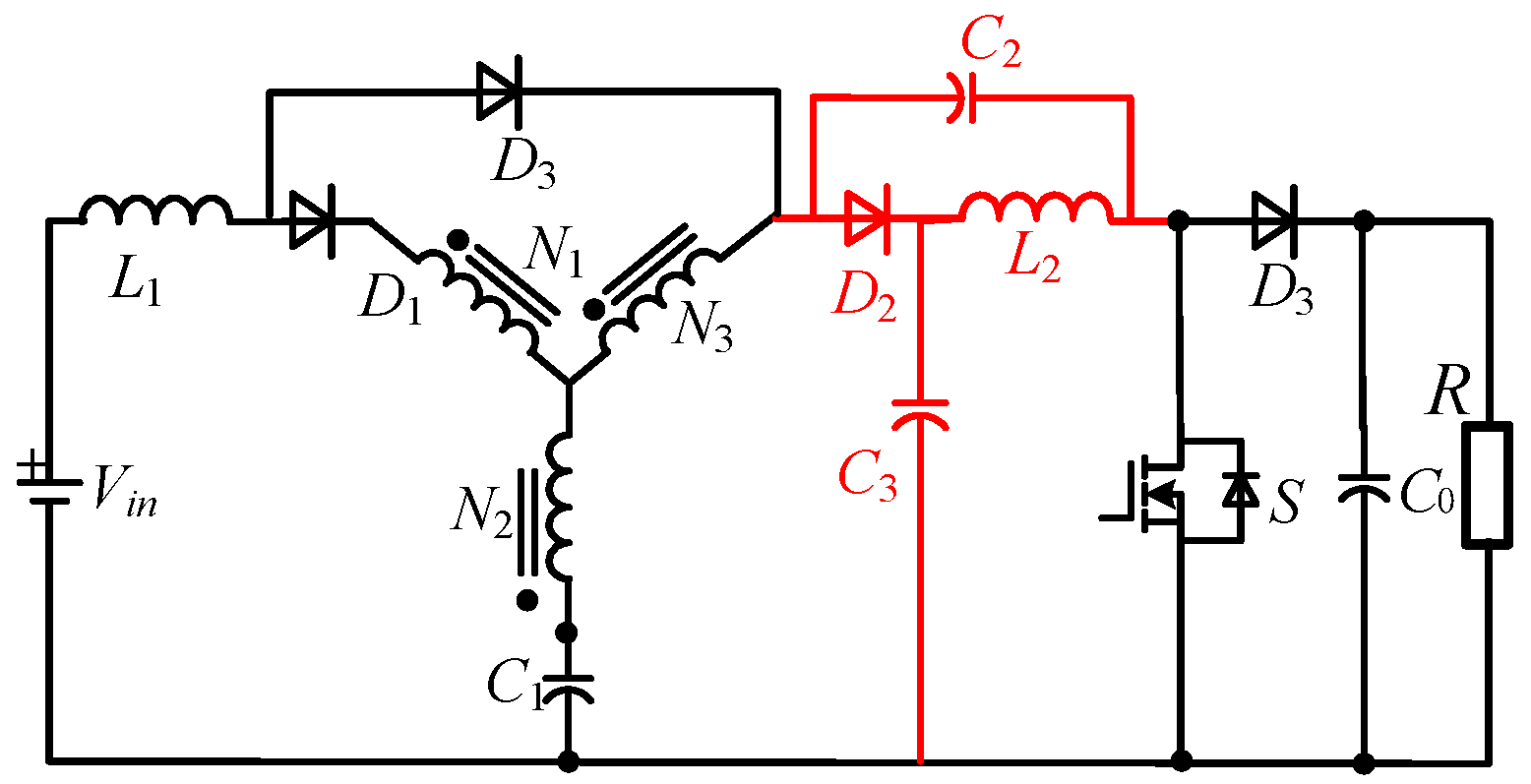

3.2.1. The Voltage-Double Quasi Y-Source Converters (VD-qYSCs)

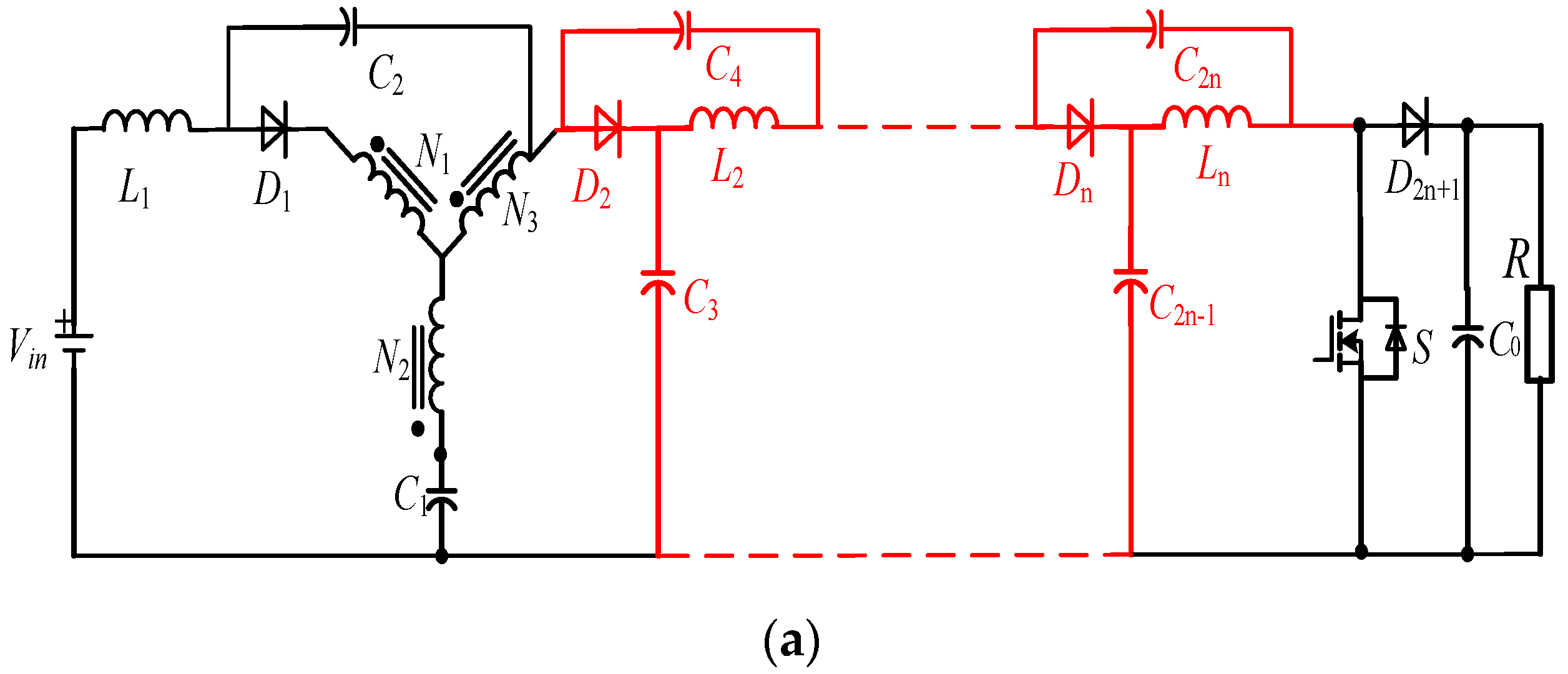

3.2.2. The Low-Voltage-Overshoot High-Efficiency Quasi Y-Source Converters (LH-qYSCs)

3.2.3. The Low-Voltage-Overshoot High-Step-Up Quasi Y-Source Converters (HS-qYSCs) and the Diode-Assisted Quasi Y-Source Converter (DA-qYSC)

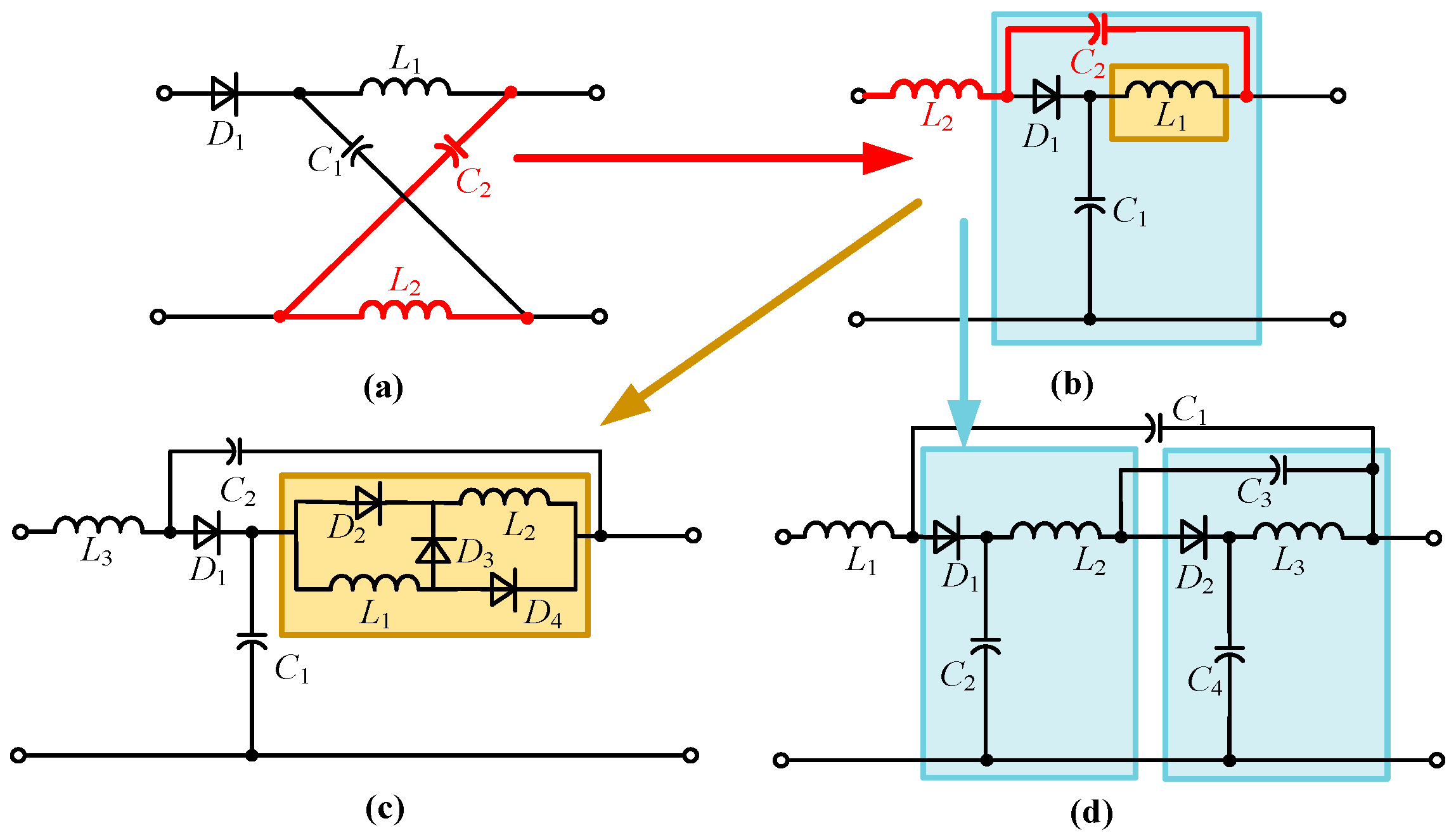

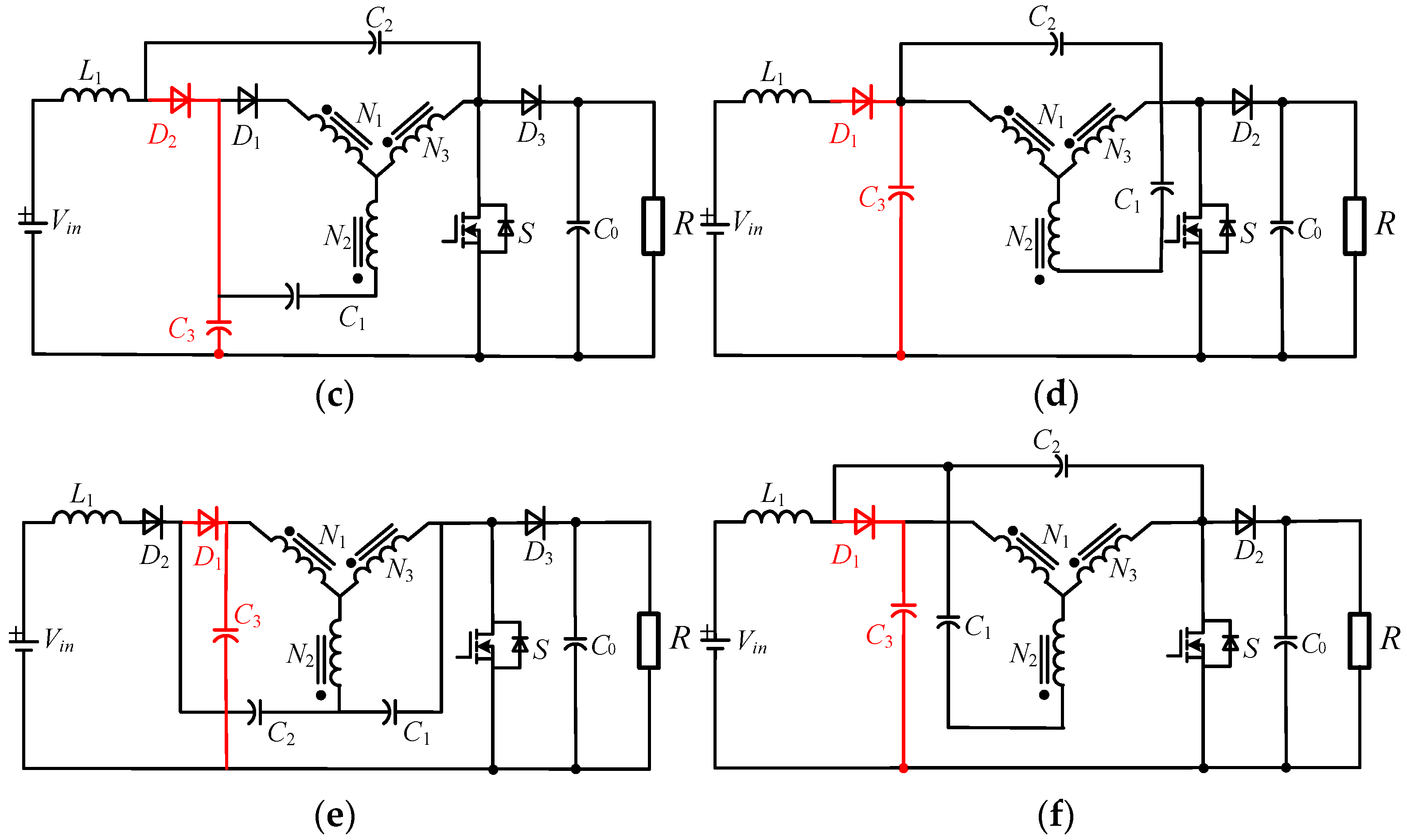

3.2.4. The Low- Voltage-Overshoot High-Step-Up Cascaded Quasi Y-Source Converters (HSC-qYSCs)

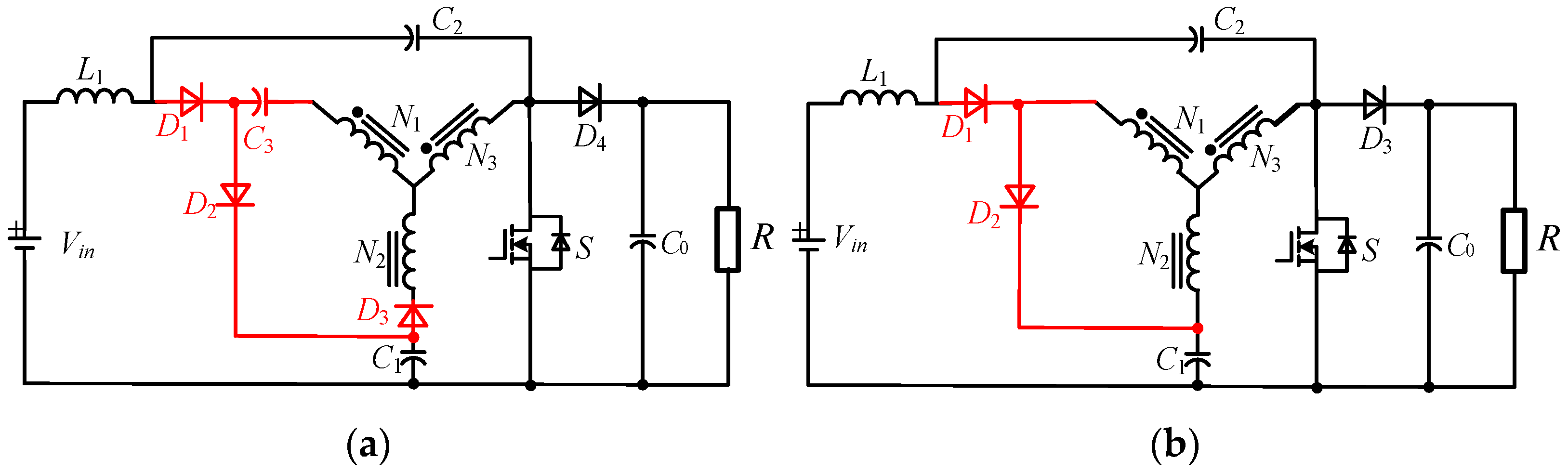

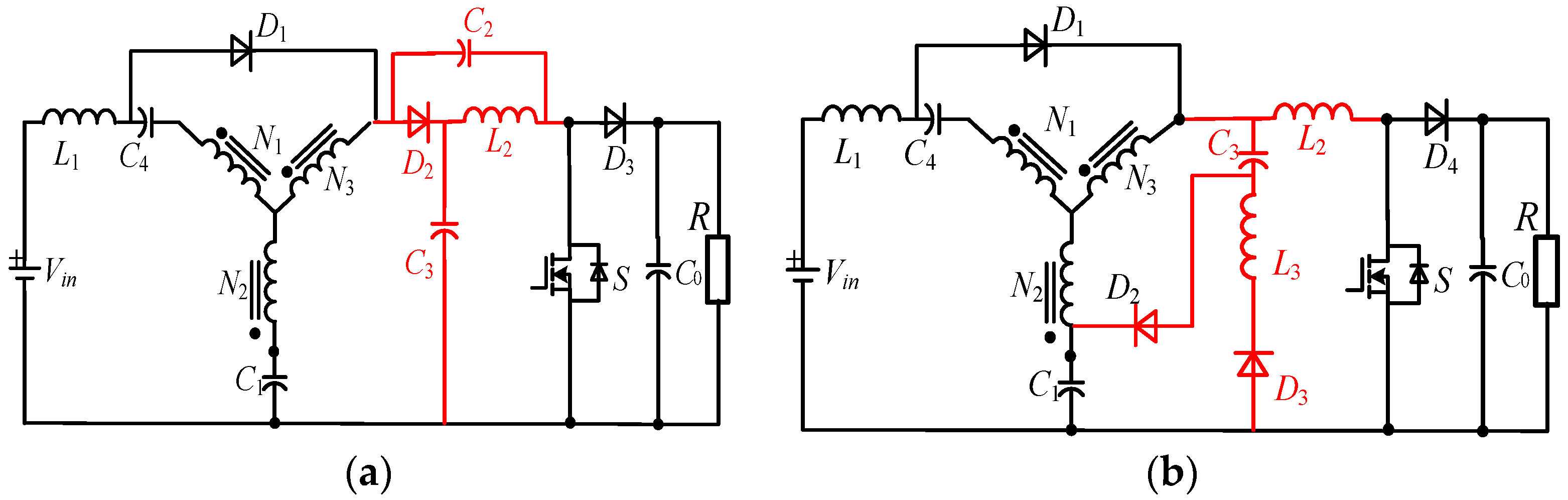

3.2.5. The Optimized Quasi Y-Source Converter (O-qYSC) and the Inductor-Capacitor-Diode Quasi Y-Source Converter (LCD-qYSC)

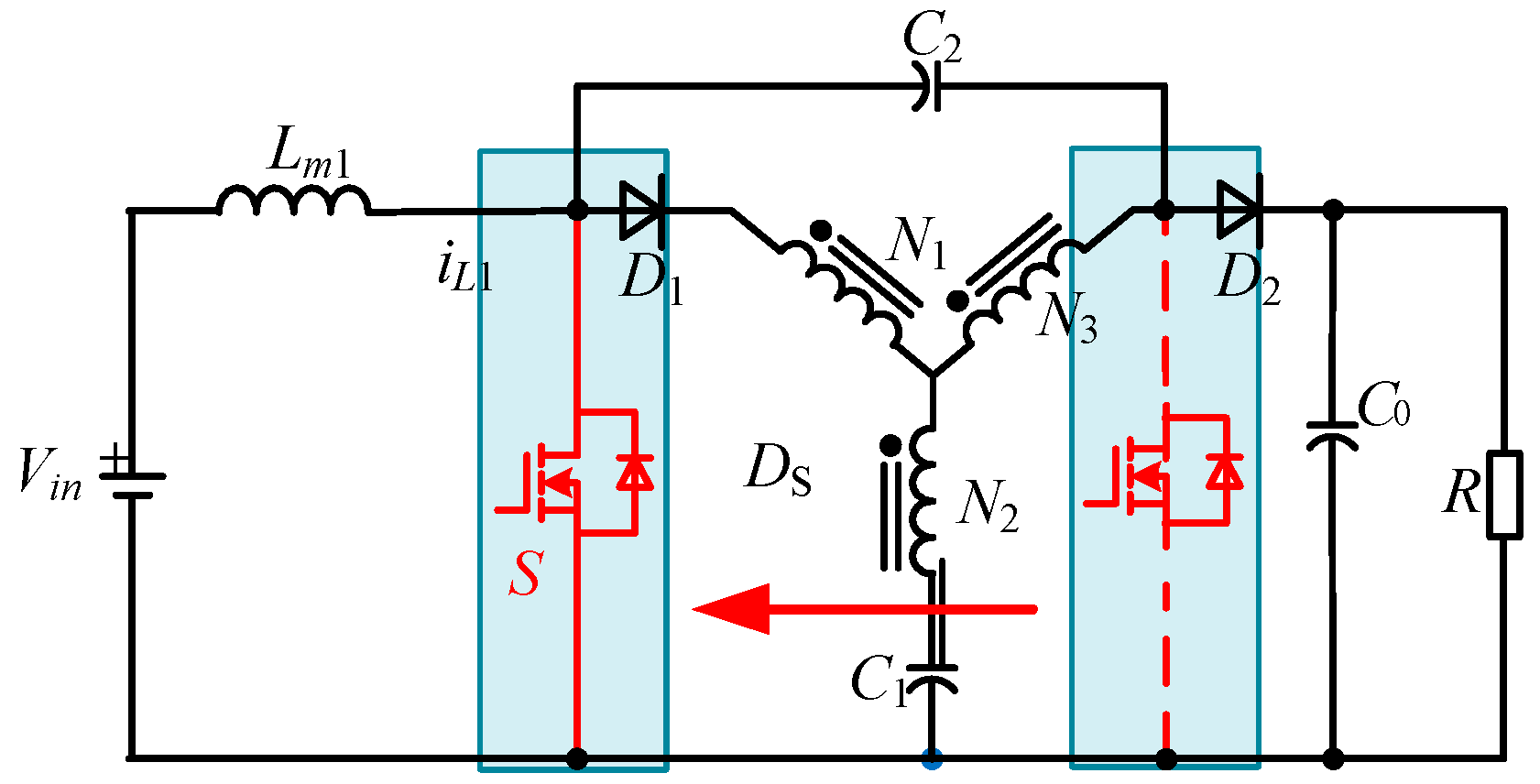

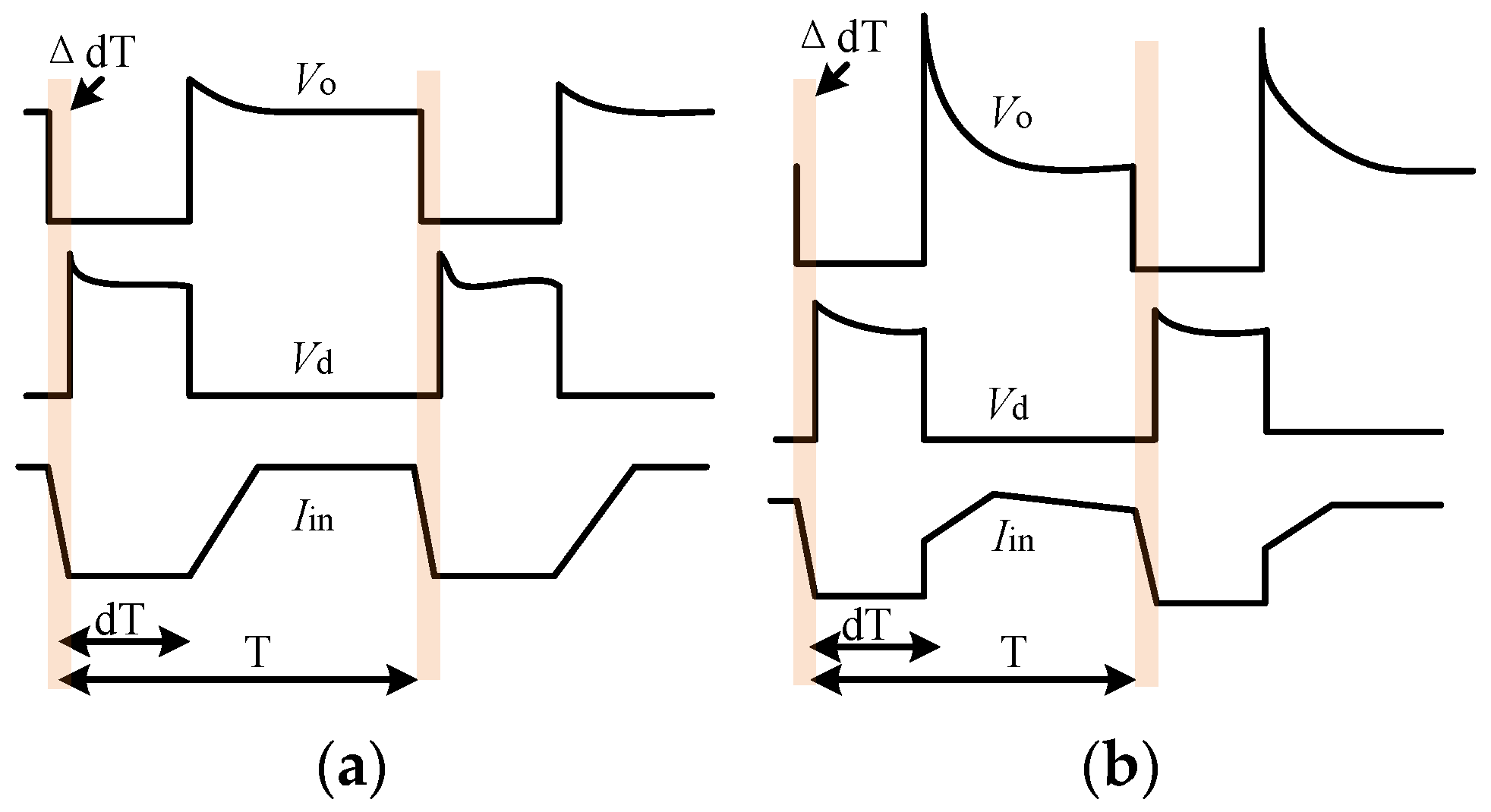

3.2.6. The Active Clamped Quasi Y-Source Converters (AC-qYSCs)

3.3. Properties Comparison among Different Y-Source Converters with the Absorbing Circuit

4. The Optimization of YSCs’ Key Indicators

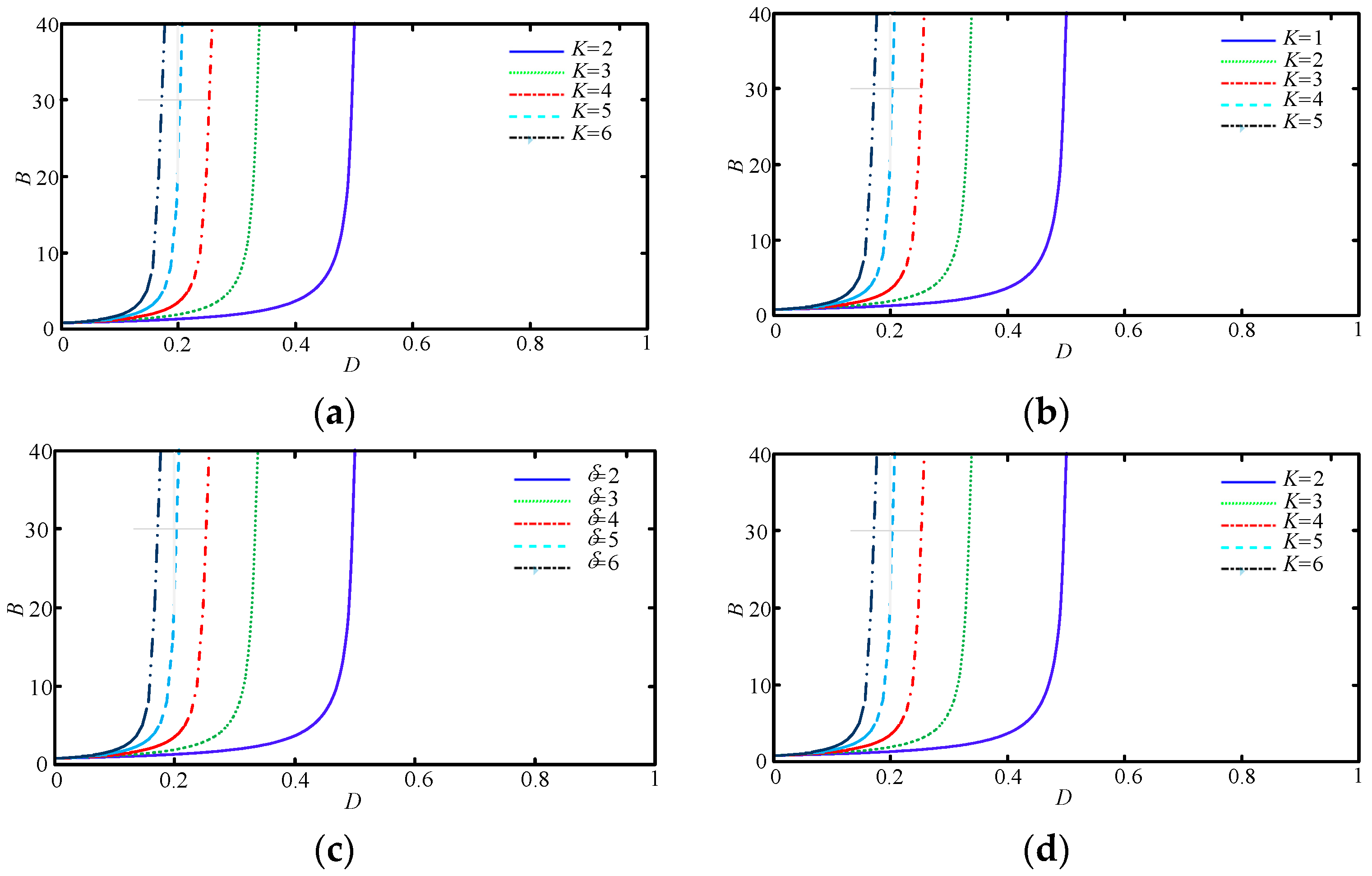

4.1. The Y-Source Converters Combined with Various Boosting Structures

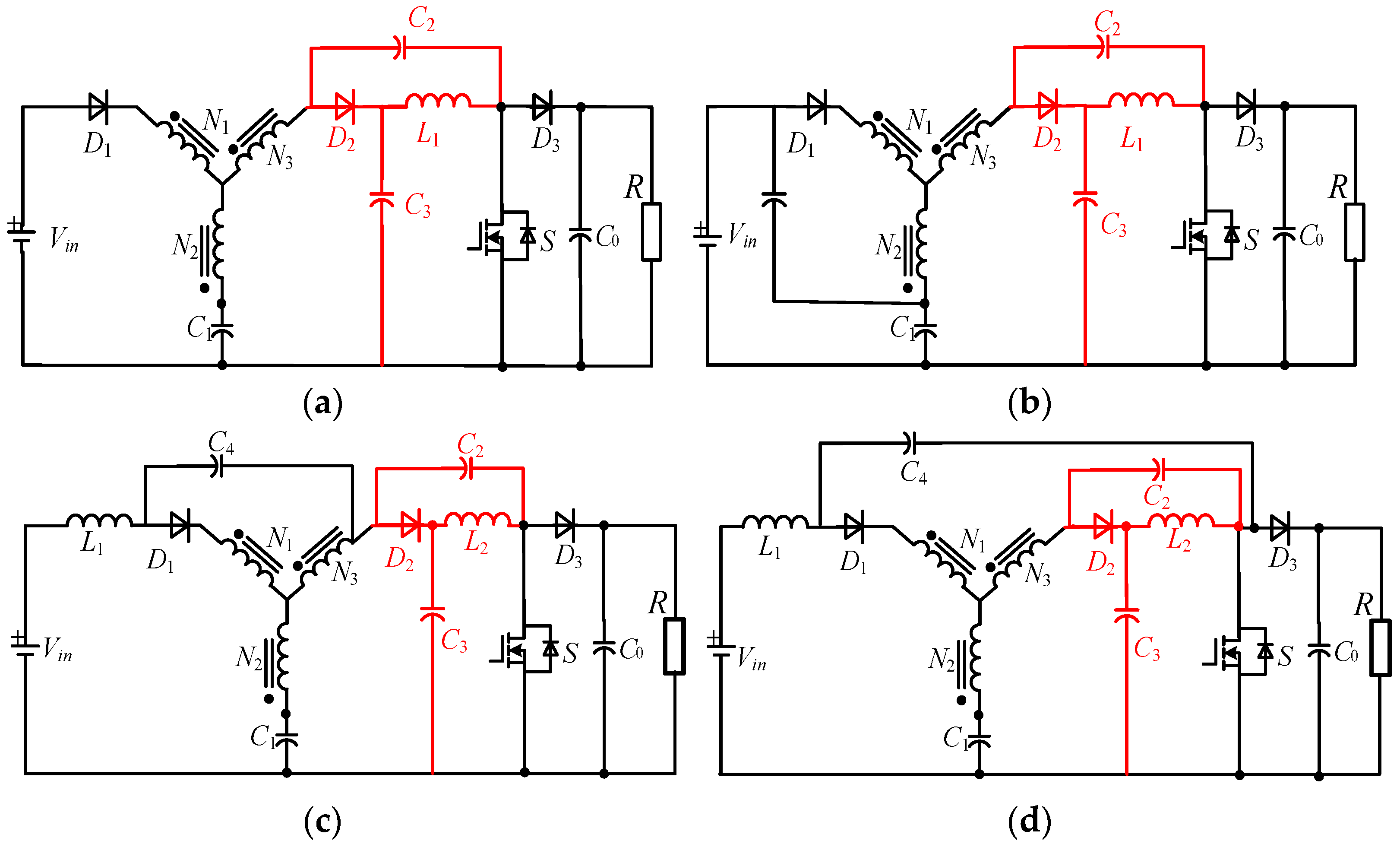

4.1.1. The Y-Source Converters Combined with a Boost Converter

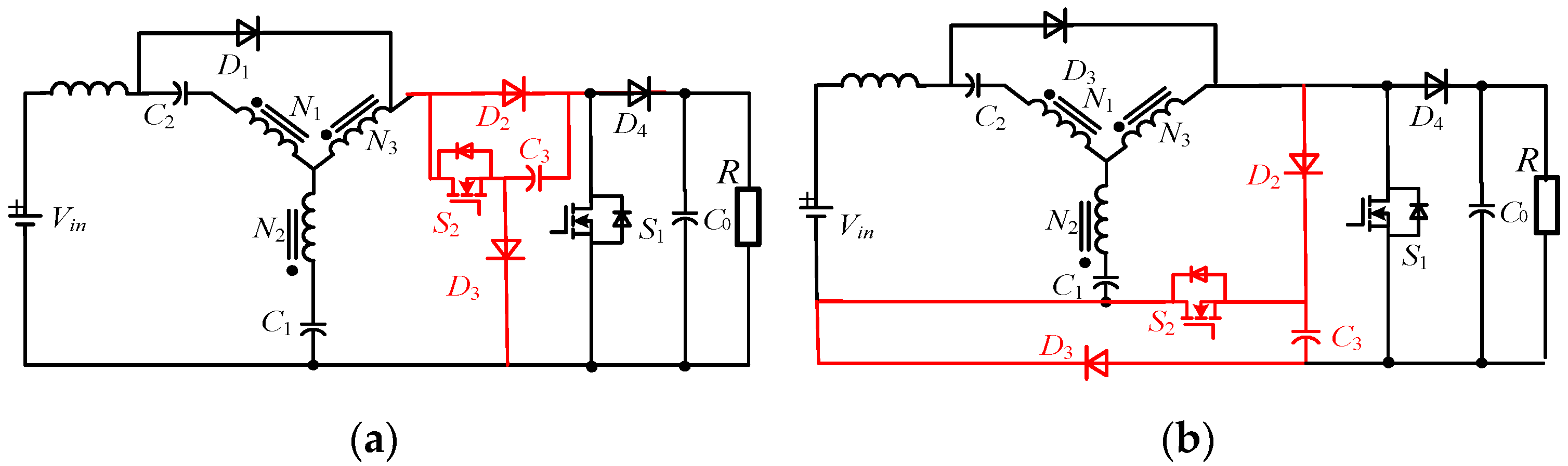

- The Quasi Y-Source Converters combined with a Boost Converter (CB-qYSC)

- 2.

- The Modified Y-Source Converters combined with a Boost Converter (CB-M-YSC)

4.1.2. YSC Combined with Different Step-Up Cells

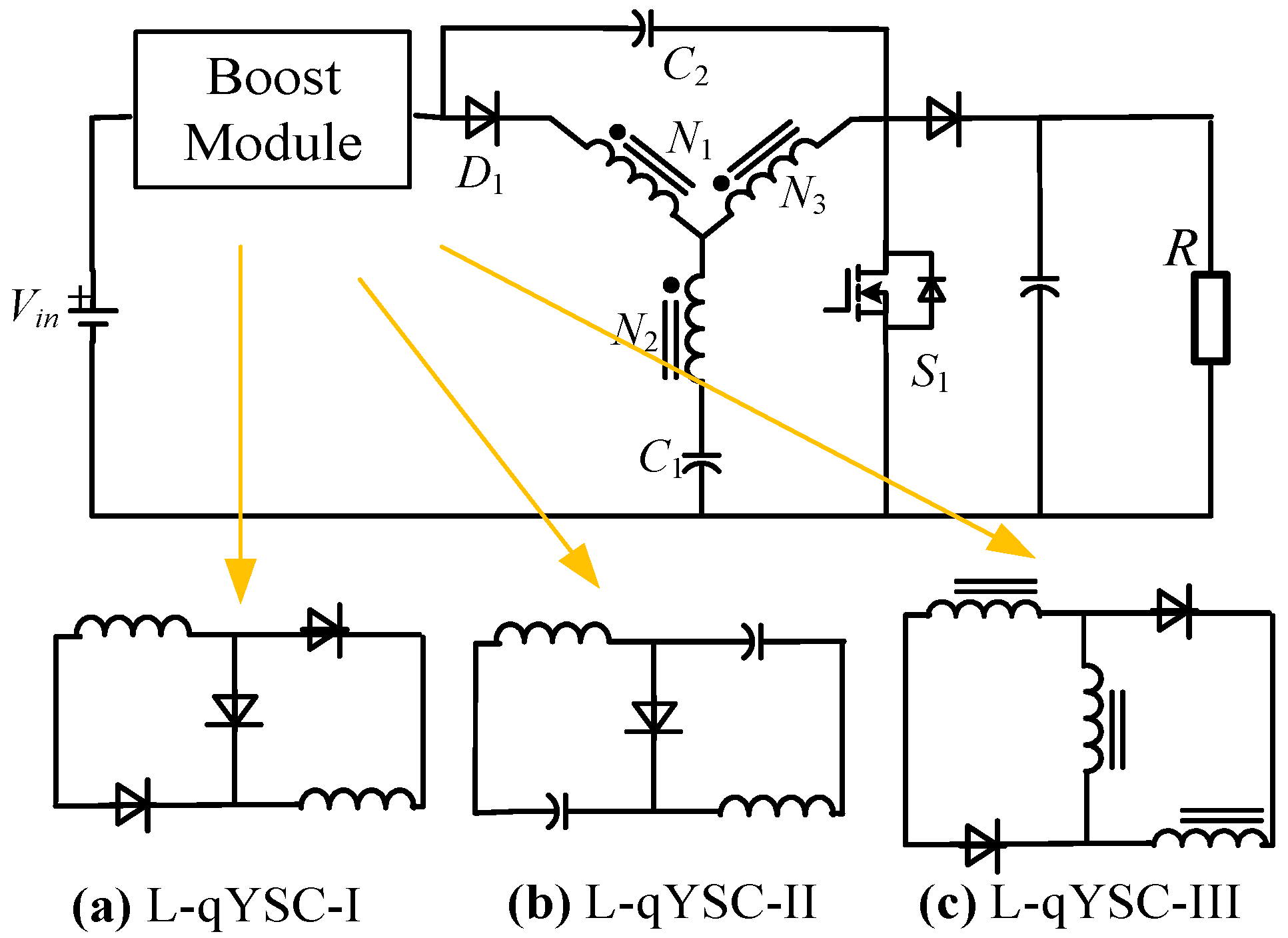

- The quasi Y-Source Converter with series Inductance modules (L-qYSC)

- 2.

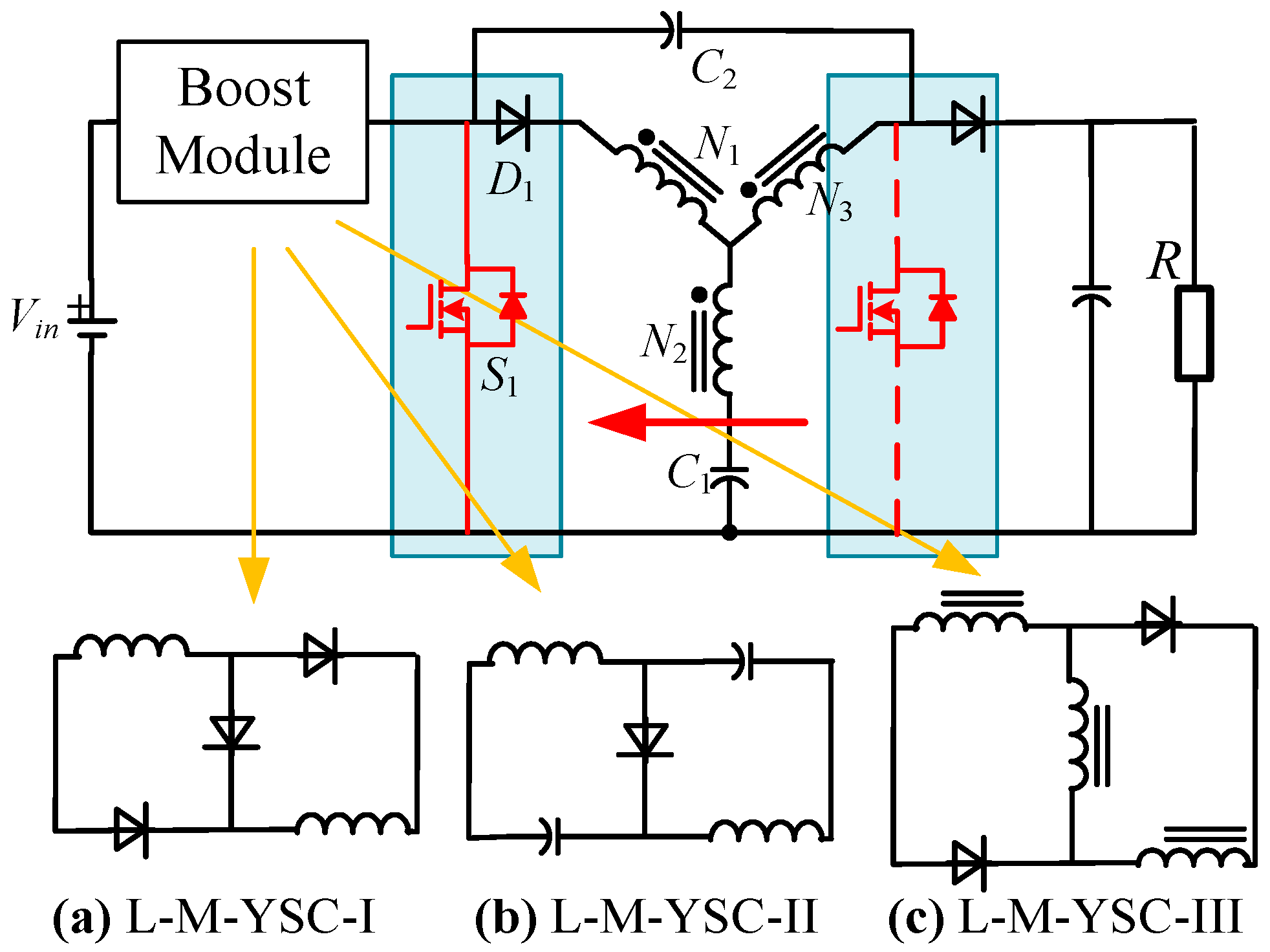

- The Modified Y-Source Converter with Series Inductance Modules (L-M-YSC)

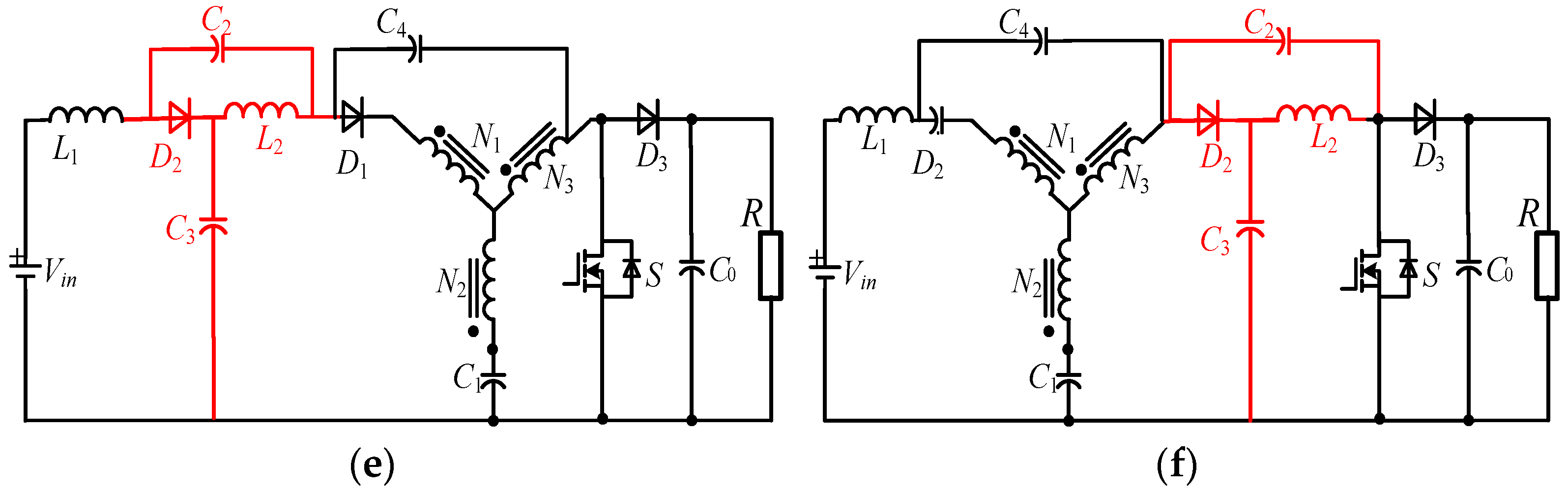

4.2. YSC with Low Input Current Ripple

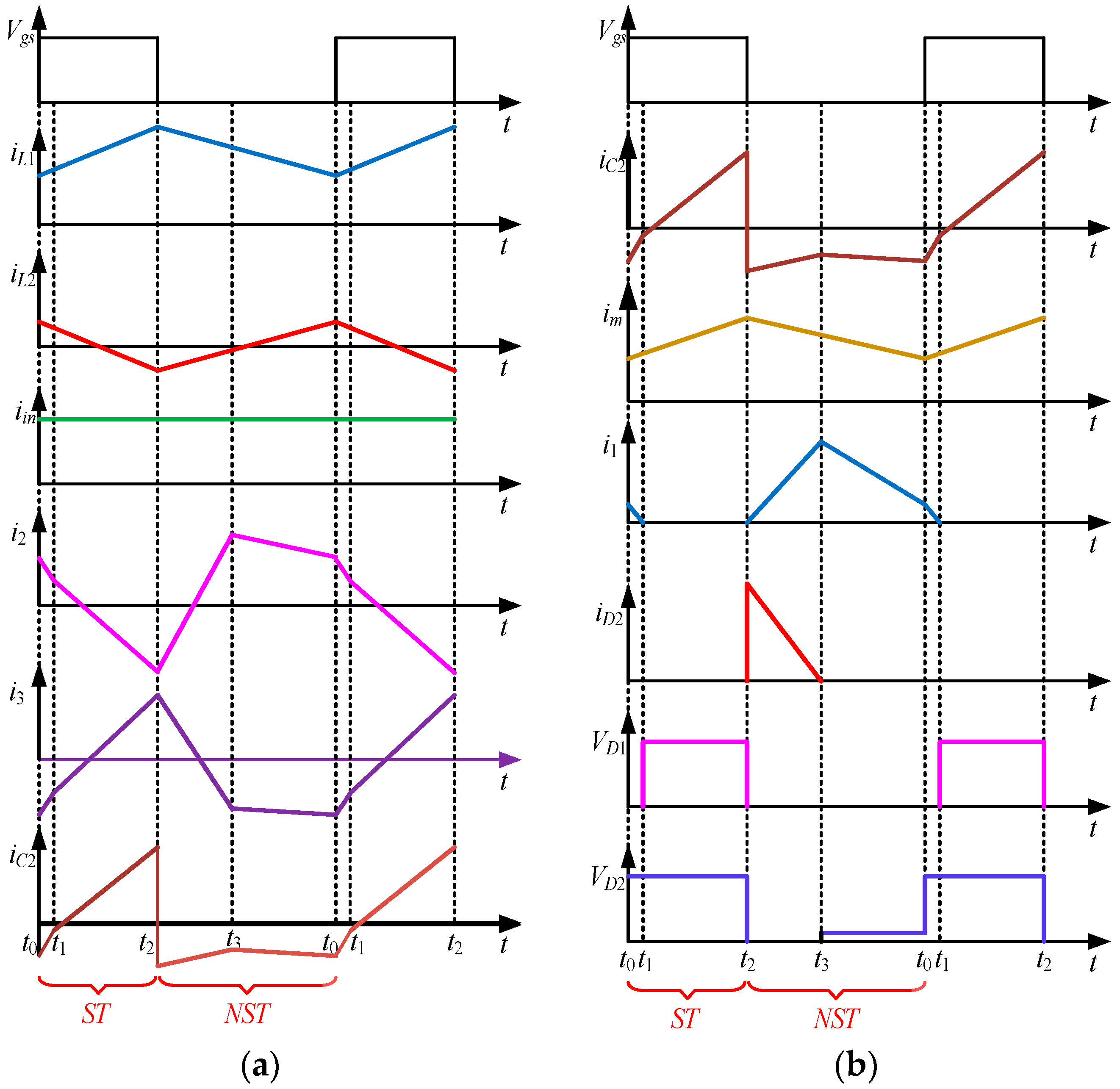

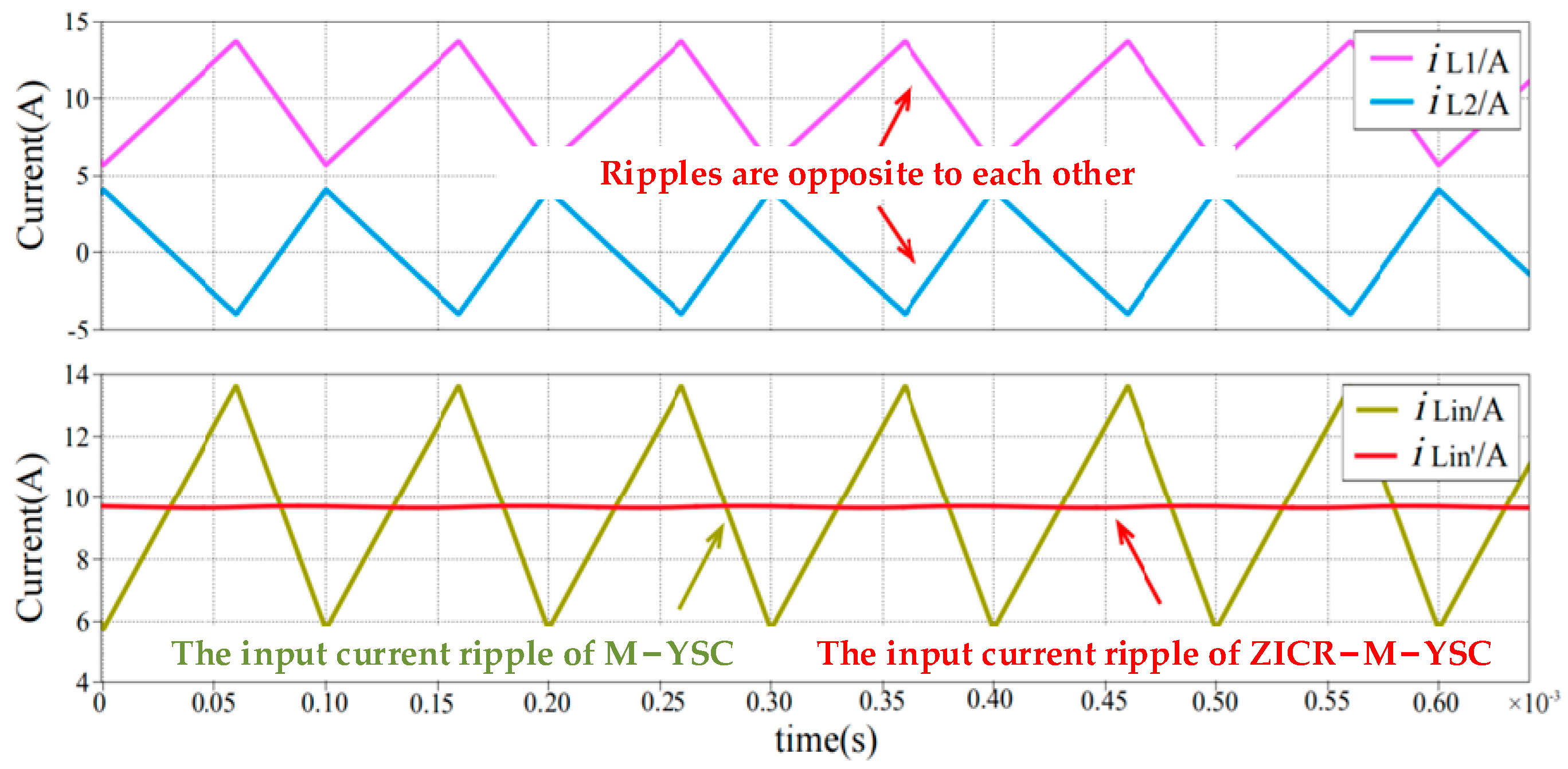

4.2.1. A Family of Modified Y-Source Converter with Zero Input Current Ripple (ZICR-M-YSC)

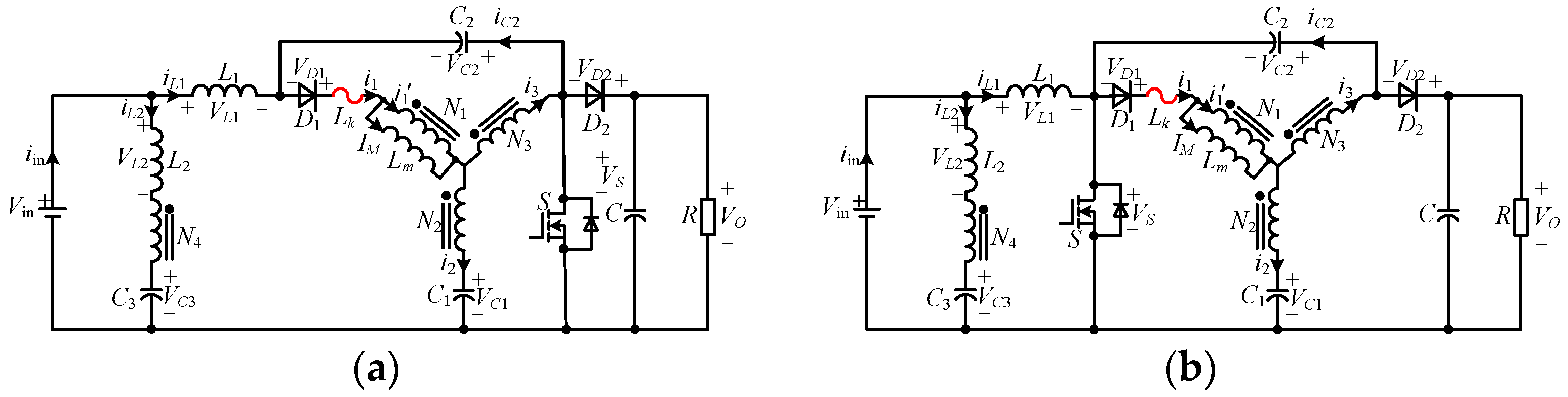

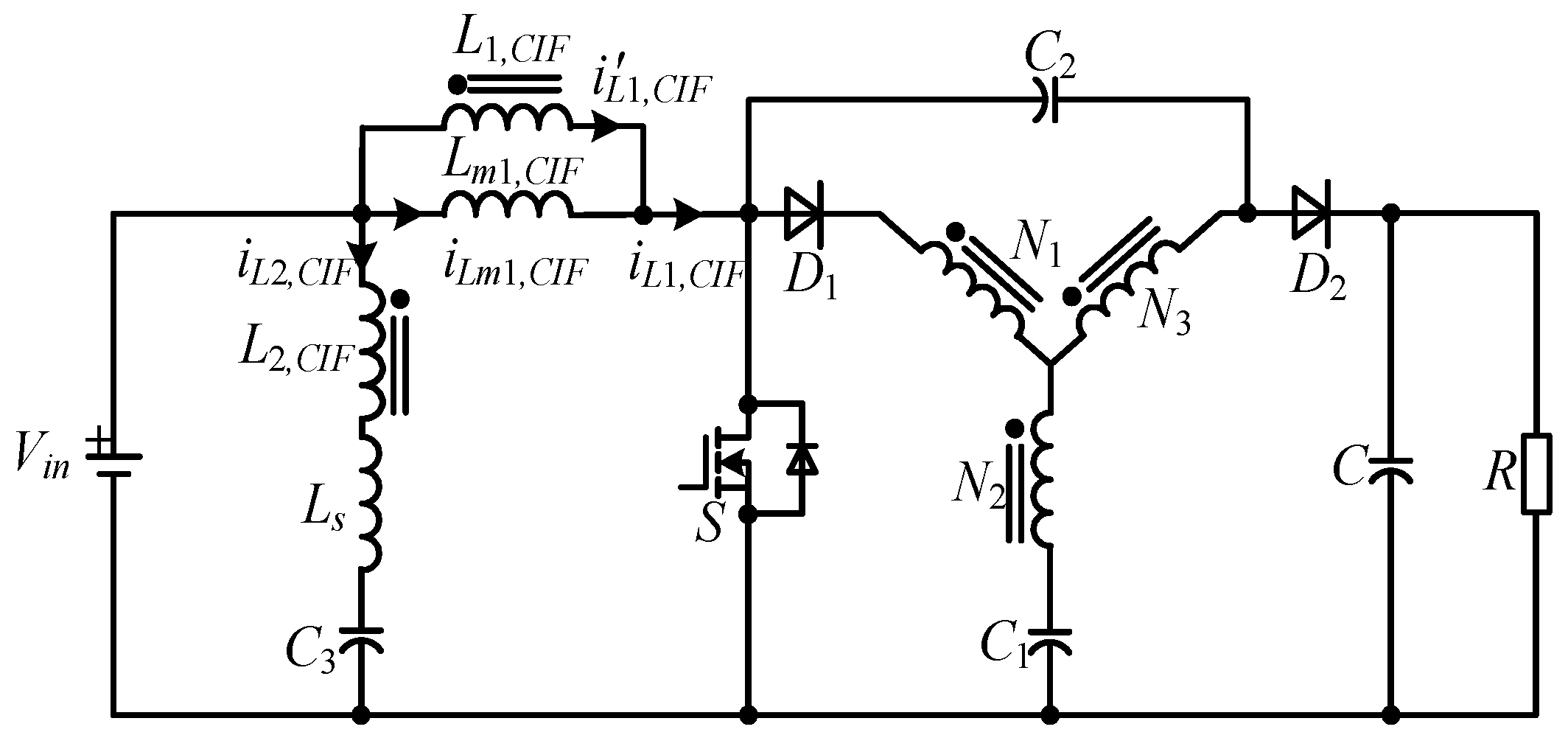

4.2.2. A Modified Y-Source Converter Using the Conventional Coupled Inductor Filter (CIF-M-YSC)

4.3. High-Efficiency Y-Source Converters

4.3.1. The Isolation Type Zero Current Switching Quasi Y-Source Converter (I-ZCS-qYSC)

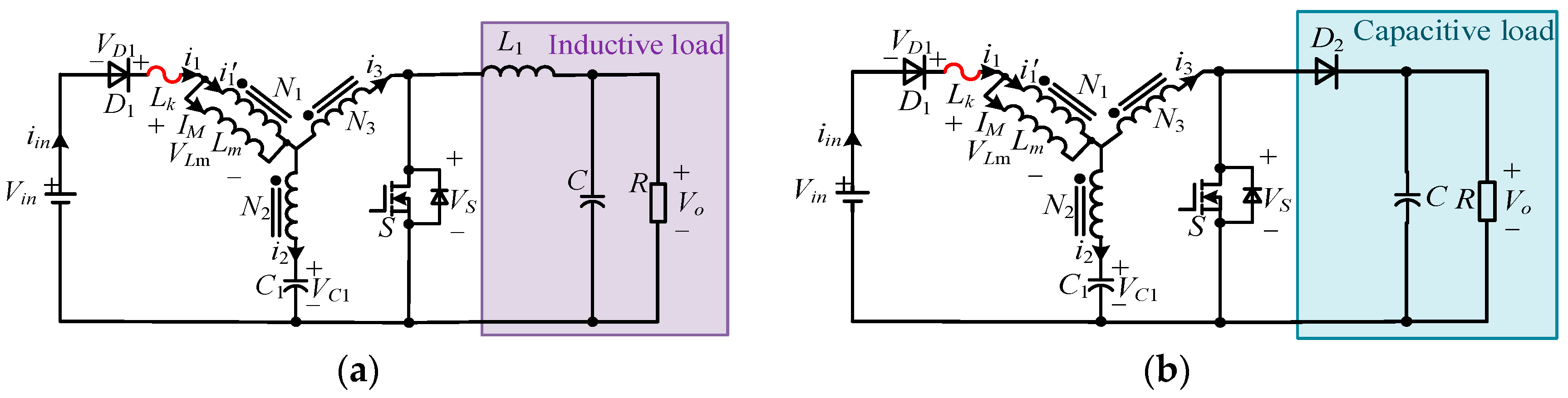

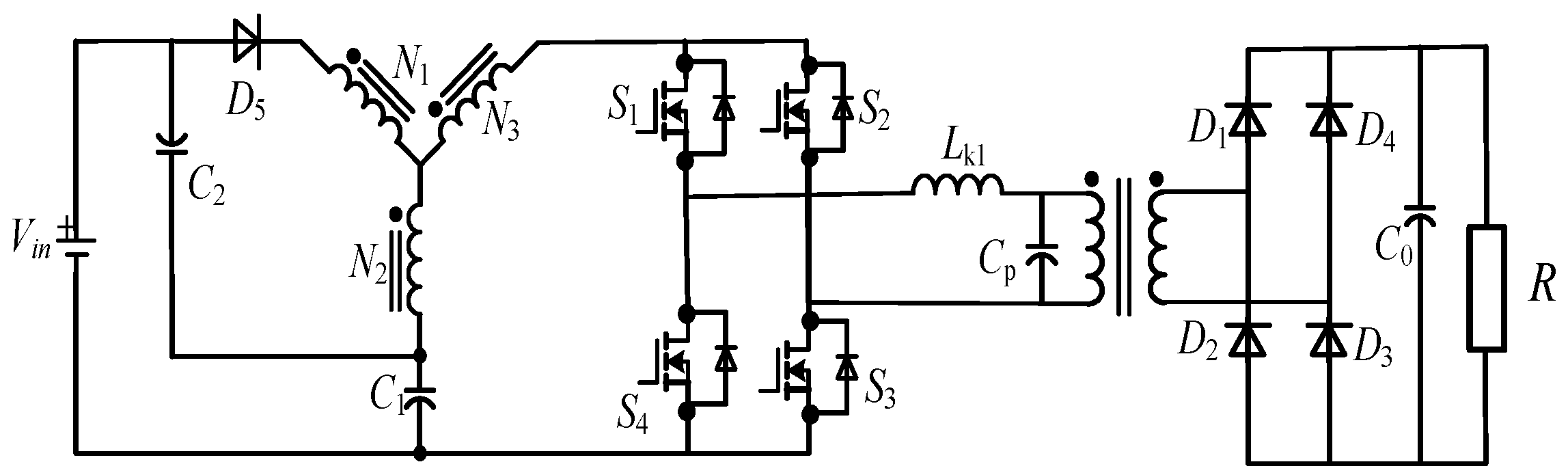

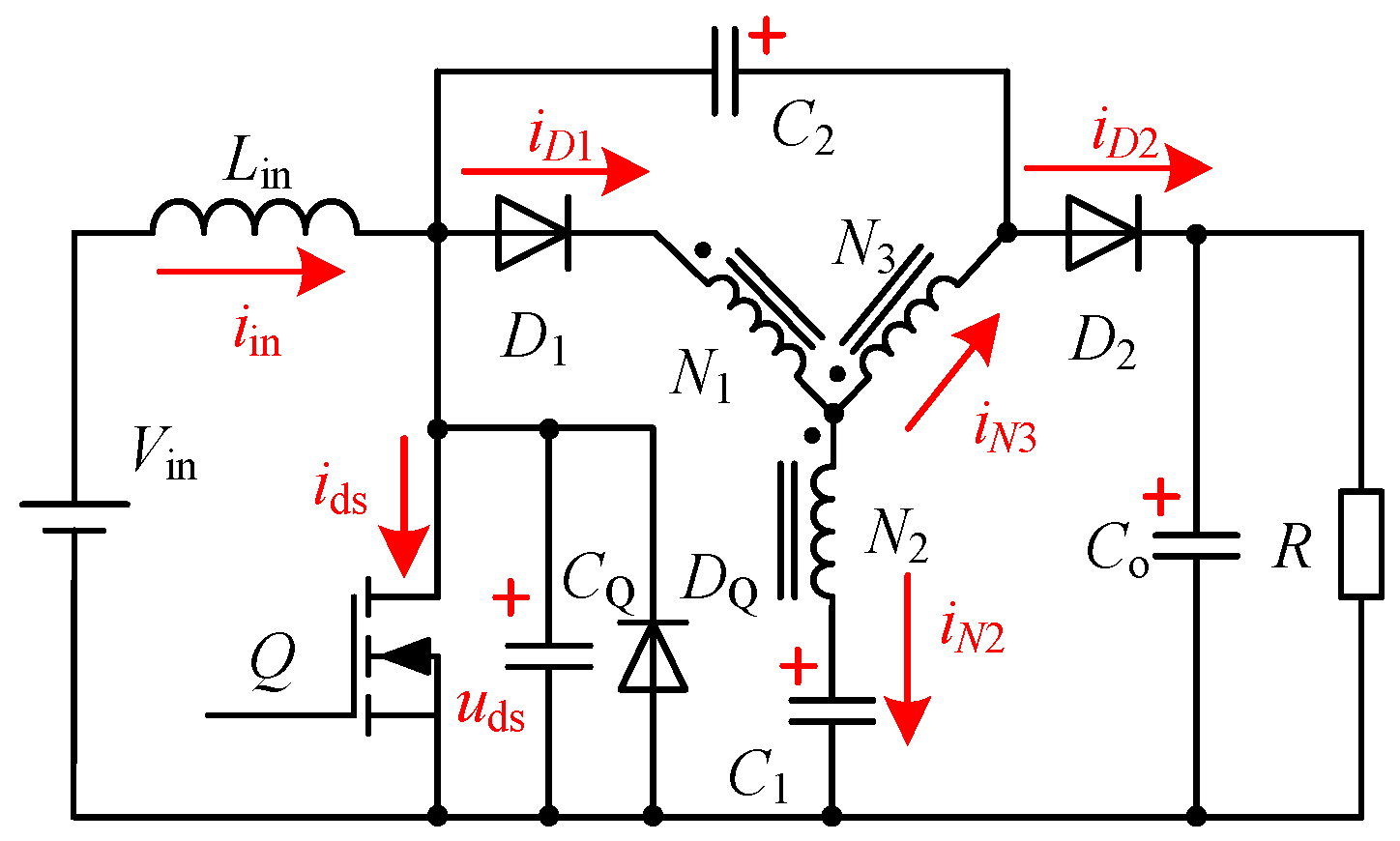

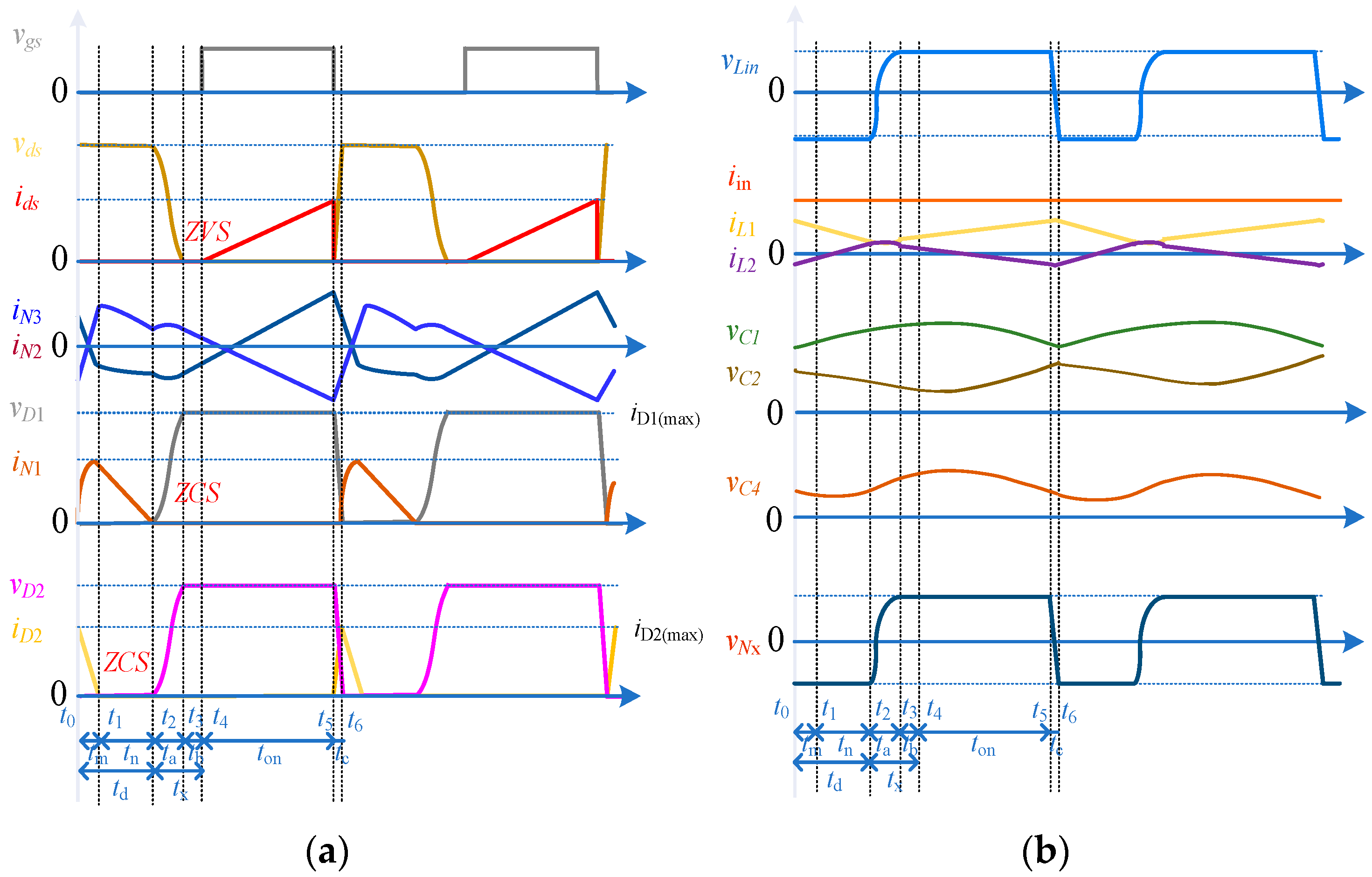

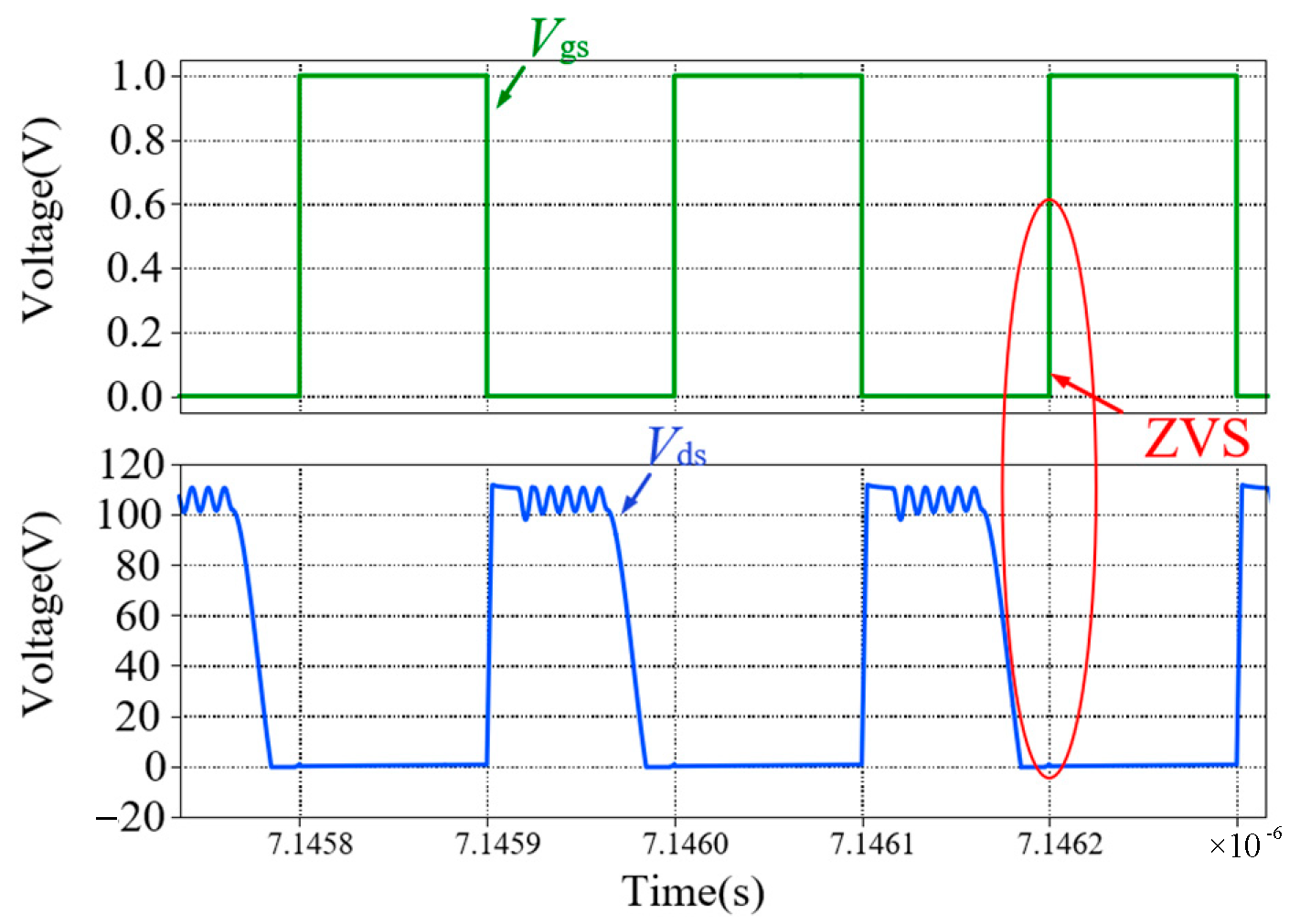

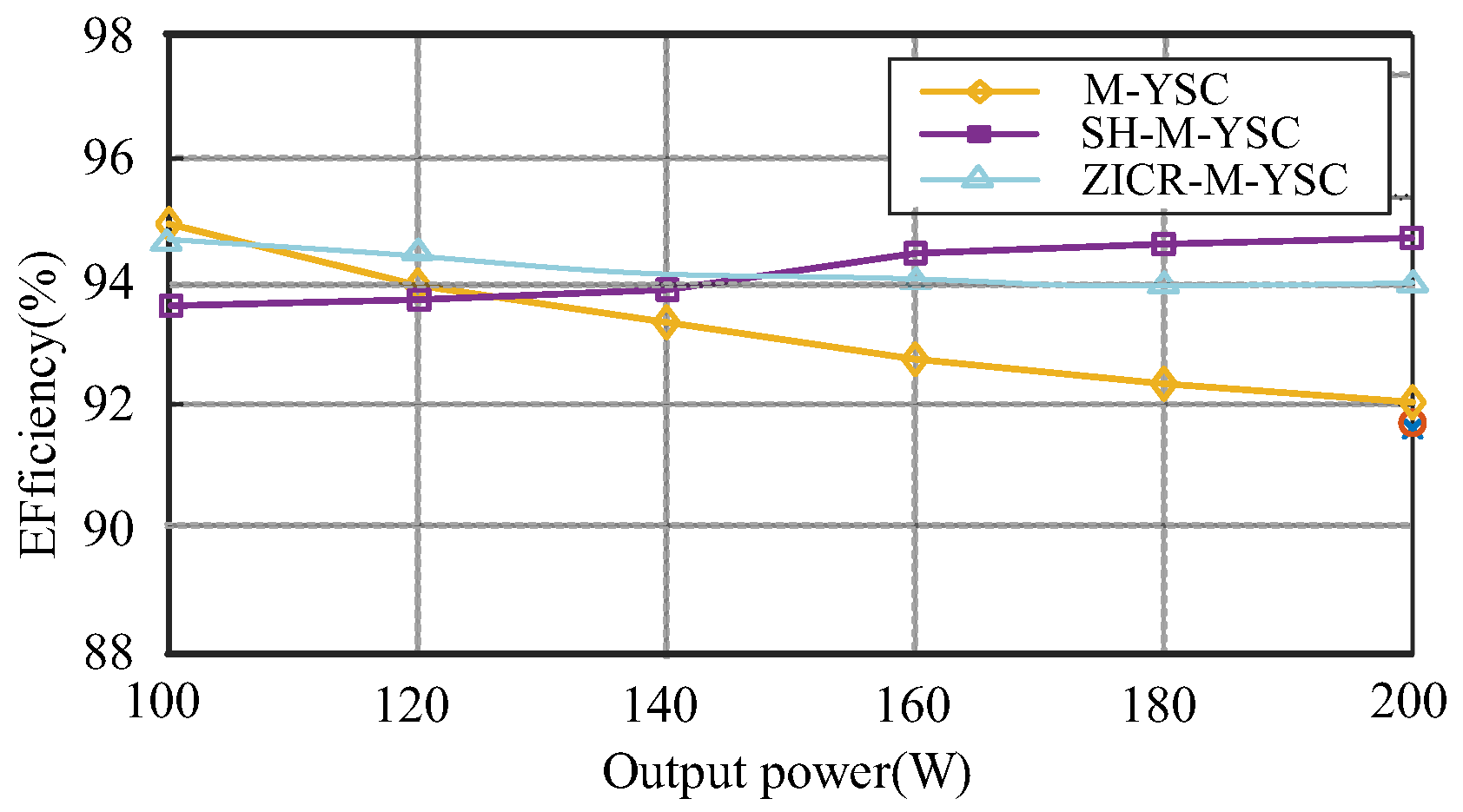

4.3.2. The Modified Y-Source Converter with Soft Switching Characteristic and High Voltage Gain (SH-M-YSC)

5. Conclusions

- To reveal the corresponding relationship between topology and function, a YSC topology can be divided into basic structure and characteristic circuits. The basic structure (YSC, qYSC, M-YSC) determines the general properties of topology, as shown in Table 2. The clamping circuits, absorption circuits, boost circuit, filtering circuits and resonant circuit in Section 3 and Section 4 are characteristic circuits, which determine the additional functions of the topology. According to the application scenario, the basic structure and characteristic circuits can be selected relatively independently, and the most appropriate topology can be obtained.

- To solve the problem of voltage overshoot caused by leakage inductance, an additional voltage clamp circuit is added to the basic topology. Changing the position of components will result in different stresses of components, with the clamping principle unchanged. Similarly, the position of boost circuit and absorption circuit is also flexible, which is conducive to improving the comprehensive performance of topology while the key characteristics remained.

- The absorption circuit of ZICR-M-YSC makes the input current ripple close to zero and can operate in DCM, but its efficiency is reduced, which can be compensated by the resonant circuit of SH-M-YSC. Therefore, in order to inherit the advantages of both, ZICR-M-YSC and SH-M-YSC can be combined to form a new topology. Taking this as an example, by merging different characteristic circuits, topologies with multiple excellent characteristics can be obtained.

- As analyzed above, most characteristic circuits are relatively independent of the Y-source structure, resulting in limited ability to adjust the winding current. Through the magnetic connection with the y-source winding, the impedance source structure can be fundamentally optimized, and better performance can be achieved.

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Bui, D.M.; Le, P.D.; Cao, T.M.; Nguyen, H.T.; Tran, T.V.; Nguyen, H.M. Boost-Converter Reliability Assessment for Renewable-Energy Generation Systems in a Low-Voltage DC Microgrid. Energy Rep. 2022, 8, 821–835. [Google Scholar] [CrossRef]

- Peng, F.Z. Z-Source Inverter. IEEE Trans. Ind. Appl. 2003, 39, 504–510. [Google Scholar] [CrossRef]

- Miyani, P.B.; Sant, A.V. Bode Diagram Based Control System Design of Three Phase Grid Tied Photovoltaic Systems with Quasi-Z Source Inverter. Mater. Today Proc. 2022, 62, 7248–7254. [Google Scholar] [CrossRef]

- Madani, A.R.; Samani, A.G.; Ezoji, H. Optimized Designed X-Shape Impedance in Voltage Type Z-Source Inverter Based on Average Modeling. Int. J. Electr. Power Energy Syst. 2024, 157, 109799. [Google Scholar] [CrossRef]

- Savrun, M.M. Z-Source Converter Integrated Dc Electric Spring for Power Quality Improvement in Dc Microgrid. Eng. Sci. Technol. Int. J. 2021, 24, 1408–1414. [Google Scholar] [CrossRef]

- Ortega, M.; Lanagrán, E.; Ortega, M.V.; Jurado, F. Design and Integration of Z-Source Converters for Energy Management with Series Operation: Applied to DC Microgrid. Int. J. Electr. Power Energy Syst. 2021, 128, 106781. [Google Scholar] [CrossRef]

- Kishor, Y.; Patel, R.N.; Kumar Sahu, L. Reliability Analysis of Modified Z-Source Based High Gain Converter for PV Application. Appl. Energy 2023, 332, 120508. [Google Scholar] [CrossRef]

- Raja Nayak, M.; Tulasi, V.V.K.; Divya Teja, K.; Koushic, K.; Suresh Naik, B. Implementation of Quasi Z-Source Inverter for Renewable Energy Applications. Mater. Today Proc. 2023, 80, 2458–2463. [Google Scholar] [CrossRef]

- Tang, Y.; Xie, S.J.; Zhang, C.H.; Xu, Z.G. Improved Z-Source Inverter with Reduced Z-Source Capacitor Voltage Stress and Soft-Start Capability. IEEE Trans. Power Electron. 2009, 24, 409–415. [Google Scholar] [CrossRef]

- Babaei, E.; Shokati Asl, E. A New Topology for Z-Source Half-Bridge Inverter with Low Voltage Stress on Capacitors. Electr. Power Syst. Res. 2016, 140, 722–734. [Google Scholar] [CrossRef]

- Kapil, P.N.; Sant, A.V. Implementation of PWM Scheme for Z-Source Inverter Using Embedded Target on SIMULINK. Mater. Today Proc. 2022, 62, 7168–7173. [Google Scholar] [CrossRef]

- Anderson, J.; Peng, F.Z. A Class of Quasi-Z-Source Inverters. In Proceedings of the 2008 IEEE Industry Applications Society Annual Meeting, Edmonton, AB, Canada, 5–9 October 2008; IEEE: New York, NY, USA; pp. 1–7. [Google Scholar] [CrossRef]

- Liu, H.L.; He, Y.Y.; ZhangLiu, M.Y. Quasi-Switched-Inductor Z-Source Inverter. In Proceedings of the 2016 IEEE 8th International Power Electronics and Motion Control Conference (IPEMC-ECCE Asia), Hefei, China, 22–26 May 2016; IEEE: New York, NY, USA; pp. 1222–1229. [Google Scholar] [CrossRef]

- Bakeer, A.; Ismeil, M.A.; Orabi, M. A Modified Two Switched-Inductors Quasi Z-Source Inverter. In Proceedings of the 2015 IEEE Applied Power Electronics Conference and Exposition (APEC), Charlotte, NC, USA, 15–19 March 2015; IEEE: New York, NY, USA; pp. 1693–1699. [Google Scholar] [CrossRef]

- Mokhtari, K.; Shokri-Kojori, S.; Aliyari-Shoorehdeli, M. A New Generalized State-Space Averaged Model, Control Design and Stability Analysis for Three Phase Grid-Connected Quasi-Z-Source Inverters. Int. J. Electr. Power Energy Syst. 2024, 158, 109932. [Google Scholar] [CrossRef]

- Chitra, K.; Kamatchikannan, V.; Viji, K.; Lakshmanan, M. Simple Boost PWM Controlled Cascaded Quasi Z-Source Inverter. Mater. Today Proc. 2021, 45, 3161–3169. [Google Scholar] [CrossRef]

- Loh, P.C.; Blaabjerg, F. Magnetically Coupled Impedance-Source Inverters. IEEE Trans. Ind. Appl. 2013, 49, 2177–2187. [Google Scholar] [CrossRef]

- Adamowicz, M. LCCT-Z-Source Inverters. In Proceedings of the 2011 10th International Conference on Environment and Electrical Engineering, Rome, Italy, 8–11 May 2011; IEEE: New York, NY, USA; pp. 1–6. [Google Scholar] [CrossRef]

- Strzelecki, R.; Adamowicz, M.; Strzelecka, N.; Bury, W. New Type T-Source Inverter. In Proceedings of the 2009 Compatability and Power Electronics, Badajoz, Spain, 20–22 May 2009; IEEE: New York, NY, USA; pp. 191–195. [Google Scholar] [CrossRef]

- Song, W.; Wang, C.; An, N.; Han, Z.; Xue, D.; Wheeler, P. Research on Definition of Short-Circuit Region for Γ-Source Circuit Breaker. IEEE Trans. Power Electron. 2024, 39, 6271–6280. [Google Scholar] [CrossRef]

- Hakemi, A.; Sanatkar-Chayjani, M.; Monfared, M. Δ-Source Impedance Network. IEEE Trans. Ind. Electron. 2017, 64, 7842–7851. [Google Scholar] [CrossRef]

- Siwakoti, Y.P.; Town, G.E.; Loh, P.C.; Blaabjerg, F. Y-Source Inverter. In Proceedings of the 2014 IEEE 5th International Symposium on Power Electronics for Distributed Generation Systems (PEDG), Galway, Ireland, 24–27 June 2014; IEEE: New York, NY, USA; pp. 1–6. [Google Scholar] [CrossRef]

- Li, X.; Qin, C.; Chu, Z. Novel Space Vector Modulation Method for the Quasi-Z-Source Asymmetrical Three-Level Inverter. IEEE Trans. Circuits Syst. II 2024, 71, 281–285. [Google Scholar] [CrossRef]

- Zhang, R.; Wang, S.; Li, Y.; Ma, J.; Wang, P.; Liu, T. A Simplified Space Vector Modulation for the Single-Phase Active Power Decoupling Quasi-Z-Source Inverter. Int. J. Electr. Power Energy Syst. 2024, 156, 109699. [Google Scholar] [CrossRef]

- Samanbakhsh, R.; Koohi, P.; Martin Ibanez, F.; Martin, F.; Terzija, V. A Z-Source Inverter with Switched Network in the Grid-Connected Applications. Int. J. Electr. Power Energy Syst. 2023, 147, 108819. [Google Scholar] [CrossRef]

- Carrasco-González, D.; Horrillo-Quintero, P.; García-Triviño, P.; Sarrias-Mena, R.; Andrés García-Vázquez, C.; Fernández-Ramírez, L.M. Control of PV Power Plants with Quasi-Z-Source Cascaded H-Bridge Multilevel Inverters under Failure. Int. J. Electr. Power Energy Syst. 2024, 157, 109803. [Google Scholar] [CrossRef]

- Mousavi, S.M.J.; Zargariafshar, D.; Babaei, E.; Ahmed, H.F. A Single-Phase Z-Source AC–AC Converter with Continuous Input Current and without Commutation Issue. IEEE Trans. Ind. Electron. 2024. [Google Scholar] [CrossRef]

- AL-Hakeem, K.M.; Ahmad, O.A. Buck-Boost In-Out of Phase Y-Source AC Matrix Converter. In Proceedings of the 2018 Third Scientific Conference of Electrical Engineering (SCEE), Baghdad, Iraq, 19–20 December 2018; IEEE: New York, NY, USA; pp. 274–279. [Google Scholar] [CrossRef]

- Mousavi, S.M.J.; Babaei, E.; Sabahi, M.; Komurcugil, H. A Class of Bidirectional Single-Phase Z-Source AC–AC Converter with Continuous Input Current and Reduced Component Count. IEEE Trans. Power Electron. 2023, 38, 6311–6318. [Google Scholar] [CrossRef]

- Büchele Neto, C.M.; Santos, R.; Serrão Gonçalves, F.A. A Comparative Analysis of Coupled-Inductors Designs for the Y-Source DC-DC Converter. In Proceedings of the 2023 15th IEEE International Conference on Industry Applications (INDUSCON), São Bernardo do Campo, Brazil, 22–24 November 2023; IEEE: New York, NY, USA; pp. 1418–1423. [Google Scholar] [CrossRef]

- Li, H.; Lin, J.; Lin, Y.; Jin, T. A High Step-Up Hybrid Y-Source-Quasi-Z Source DC–DC Converter for Renewable Energy Applications. IEEE Trans. Ind. Electron. 2024, 71, 10681–10692. [Google Scholar] [CrossRef]

- Zhou, M.; Liu, C.; Zhang, M.; Mao, X.; Zhang, Y. High Step-Up Soft-Switching DC–DC Converter Integrated with Y-Source Network. IEEE J. Emerg. Sel. Top. Power Electron. 2023, 11, 3348–3358. [Google Scholar] [CrossRef]

- Masoud, A.; Packnezhad, M.; Farzanehfard, H. A Single-Switch Ultra-High Step-Up DC-DC Converter with Low Voltage Stress Based on Quadratic Y-Sources Topology. In Proceedings of the 2023 14th Power Electronics, Drive Systems, and Technologies Conference (PEDSTC), Babol, Iran, 31 January–2 February 2023; IEEE: New York, NY, USA; pp. 1–6. [Google Scholar] [CrossRef]

- Tian, P.; Jin, Y.; Zhang, G.; Peng, S.; Huang, C.; Wang, C.; Xie, N. An Implicit Z-Bus Based Sequential Power Flow Algorithm for VSC AC/DC Systems. Int. J. Electr. Power Energy Syst. 2024, 155, 109648. [Google Scholar] [CrossRef]

- Reddivari, R.; Jena, D. Improved Gamma Type Y-Source Inverter for Rooftop PV Based V-G Applications. Int. J. Electr. Power Energy Syst. 2022, 142, 108261. [Google Scholar] [CrossRef]

- Asghari-Gorji, S.; Mostaan, A.; Javadi, H. A New Structure of Y-Source Inverters with Continous Input Current and High Voltage Gain. In Proceedings of the 6th Power Electronics, Drive Systems & Technologies Conference (PEDSTC2015), Tehran, Iran, 3–4 February 2015; IEEE: New York, NY, USA; pp. 515–520. [Google Scholar] [CrossRef]

- Shehata, E.G.; Thomas, J.; Brisha, A.M.; Wageh, M. Design and Analysis of a Quasi Y-Source Impedance Network DC-DC Converter. In Proceedings of the 2017 Nineteenth International Middle East Power Systems Conference (MEPCON), Cairo, Egypt, 19–21 December 2017; IEEE: New York, NY, USA; pp. 235–241. [Google Scholar] [CrossRef]

- Abdelaal, O.; Ismeil, M.A.; Orabi, M. Model Predicitve Control Of Quasi Y-Source Inverter. In Proceedings of the 2019 21st International Middle East Power Systems Conference (MEPCON), Cairo, Egypt, 17–19 December 2019; IEEE: New York, NY, USA; pp. 478–483. [Google Scholar] [CrossRef]

- Yuan, J.; Mostaan, A.; Yang, Y.; Siwakoti, Y.P.; Blaabjerg, F. A Modified Y-Source DC–DC Converter with High Voltage-Gains and Low Switch Stresses. IEEE Trans. Power Electron. 2020, 35, 7716–7720. [Google Scholar] [CrossRef]

- Siwakoti, Y.P.; Loh, P.C.; Blaabjerg, F.; Town, G.E. Effects of Leakage Inductances on Magnetically Coupled Y-Source Network. IEEE Trans. Power Electron. 2014, 29, 5662–5666. [Google Scholar] [CrossRef]

- Reddivari, R.; Jena, D.; Gautham, T.N. Analysis, Design, and Performance Evaluation of Differential-Mode Y-Source Converters for Voltage Spikes Mitigation. IEEE Trans. Ind. Appl. 2020, 56, 6701–6710. [Google Scholar] [CrossRef]

- Cha, H.; Li, Y.; Zheng Peng, F. Practical Layouts and DC-Rail Voltage Clamping Techniques of Z-Source Inverters. IEEE Trans. Power Electron. 2016, 31, 7471–7479. [Google Scholar] [CrossRef]

- Ji, Y.; Liu, H.; Zhang, C.; Wheeler, P. Voltage-Double Magnetically Coupled Impedance Source Networks. IEEE Trans. Power Electron. 2018, 33, 5983–5994. [Google Scholar] [CrossRef]

- Liu, H.; Li, Y.; Zhou, Z.; Wang, W.; Xu, D. A Family of Low-Spike High-Efficiency Y-Source Inverters. IEEE Trans. Ind. Electron. 2019, 66, 9288–9300. [Google Scholar] [CrossRef]

- Liu, H.; Zhou, Z.; Liu, K.; Loh, P.C.; Wang, W.; Xu, D.; Blaabjerg, F. A Family of High Step-Up Coupled-Inductor Impedance-Source Inverters with Reduced Switching Spikes. IEEE Trans. Power Electron. 2018, 33, 9116–9121. [Google Scholar] [CrossRef]

- Liu, H.; Zhou, Z.; Liu, K.; Loh, P.C.; Wang, W.; Xu, D.; Blaabjerg, F. High Step-Up Y-Source Inverter with Reduced DC-Link Voltage Spikes. IEEE Trans. Power Electron. 2019, 34, 5487–5499. [Google Scholar] [CrossRef]

- Liu, H.; Shi, E.; Wang, W. Reliability Analysis of the Optimized Y-Source Inverter with Clamping Circuit. Microelectron. Reliab. 2019, 100–101, 113420. [Google Scholar] [CrossRef]

- Forouzesh, M.; Abdelhakim, A.; Siwakoti, Y.; Blaabjerg, F. Analysis and Design of an Energy Regenerative Snubber for Magnetically Coupled Impedance Source Converters. In Proceedings of the 2018 IEEE Applied Power Electronics Conference and Exposition (APEC), San Antonio, TX, USA, 4–8 March 2018; IEEE: New York, NY, USA; pp. 2555–2561. [Google Scholar] [CrossRef]

- Nguyen, M.K.; Le, T.V.; Park, S.J.; Lim, Y.C. A Class of Quasi-Switched Boost Inverters. IEEE Trans. Ind. Electron. 2015, 62, 1526–1536. [Google Scholar] [CrossRef]

- Bajestan, M.M.; Shamsinejad, M.A. Two New Magnetically Coupled-Inductor Z-Source Inverters with High Voltage Boost Capability. In Proceedings of the 2018 9th Annual Power Electronics, Drives Systems and Technologies Conference (PEDSTC), Tehran, Iran, 13–15 February 2018; IEEE: New York, NY, USA; pp. 419–425. [Google Scholar] [CrossRef]

- Nikbahar, A.; Monfared, M. Smooth DC-Link Y-Source Inverters: Suppression of Shoot-Through Current and Avoiding DC Magnetism. IEEE Trans. Power Electron. 2022, 37, 12357–12369. [Google Scholar] [CrossRef]

- Fang, X.; Ding, X.; Zhong, S.; Tian, Y. Improved Quasi-Y-Source DC-DC Converter for Renewable Energy. CPSS Trans. Power Electron. Appl. 2019, 4, 163–170. [Google Scholar] [CrossRef]

- Wang, Y.; Jing, W.; Qiu, Y.; Wang, Y.; Deng, X.; Hua, K.; Hu, B.; Xu, D. A Family of Y-Source DC/DC Converter Based on Switched Inductor. IEEE Trans. Ind. Appl. 2019, 55, 1587–1597. [Google Scholar] [CrossRef]

- Chakraborty, S.; Kumar, A. A Multilevel Based High Gain Switched Inductor Quadratic DC-DC Boost Converter. IFAC-Pap. 2022, 55, 448–453. [Google Scholar] [CrossRef]

- Joy, N.; Joy, N.; Issac, K. Dual Output Switched Inductor Double Switch Converter. Mater. Today Proc. 2022, 58, 428–432. [Google Scholar] [CrossRef]

- Saflana, N.A.; George, R.; Neema, S.; Kuruvilla, J. Switched Inductor Based Non-Isolated Buck Boost Converter with Continuous Input Current. Mater. Today Proc. 2022, 58, 587–592. [Google Scholar] [CrossRef]

- Mohan, M.; Joy, J.; James, G.; Paulose, S. Switched Inductor Based Transformerless Boost Inverter. Mater. Today Proc. 2022, 58, 496–503. [Google Scholar] [CrossRef]

- Husev, O.; Roncero-Clemente, C.; Romero-Cadaval, E.; Vinnikov, D.; Jalakas, T. Three-Level Three-Phase Quasi-Z-Source Neutral-Point-Clamped Inverter with Novel Modulation Technique for Photovoltaic Application. Electr. Power Syst. Res. 2016, 130, 10–21. [Google Scholar] [CrossRef]

- Yao, T.; Guan, Y.; Cheng, Q.; Wang, Y.; Dalla Costa, M.A.; Alonso, M.; Xu, D.; Wang, W. High Performance Y-Source Converters Based on Switched Inductor. In Proceedings of the 2022 IEEE Industry Applications Society Annual Meeting (IAS), Detroit, MI, USA, 9–14 October 2022; IEEE: New York, NY, USA; pp. 1–5. [Google Scholar] [CrossRef]

- Li, W.; He, X. Review of Nonisolated High-Step-Up DC/DC Converters in Photovoltaic Grid-Connected Applications. IEEE Trans. Ind. Electron. 2011, 58, 1239–1250. [Google Scholar] [CrossRef]

- Saadatizadeh, Z.; Babaei, E.; Blaabjerg, F.; Cecati, C. Three-Port High Step-Up and High Step-Down DC-DC Converter with Zero Input Current Ripple. IEEE Trans. Power Electron. 2021, 36, 1804–1813. [Google Scholar] [CrossRef]

- Hu, X.; Gong, C. A High Voltage Gain DC–DC Converter Integrating Coupled-Inductor and Diode–Capacitor Techniques. IEEE Trans. Power Electron. 2014, 29, 789–800. [Google Scholar] [CrossRef]

- Li, W.; Zhao, Y.; Deng, Y.; He, X. Interleaved Converter with Voltage Multiplier Cell for High Step-Up and High-Efficiency Conversion. IEEE Trans. Power Electron. 2010, 25, 2397–2408. [Google Scholar] [CrossRef]

- Wang, W.; Wang, Y.; Guan, Y.; Yao, T.; Wang, Y.; Xu, D. A Family of Impedance Source DC-DC Converters with Zero Input Current Ripple. IEEE Trans. Ind. Electron. 2023, 70, 8883–8894. [Google Scholar] [CrossRef]

- Lee, S.-W.; Do, H.-L. Zero-Ripple Input-Current High-Step-Up Boost–SEPIC DC–DC Converter with Reduced Switch-Voltage Stress. IEEE Trans. Power Electron. 2017, 32, 6170–6177. [Google Scholar] [CrossRef]

- Heidari, M.; Farzanehfard, H.; Esteki, M. A Single-Switch Single-Magnetic Core High Conversion Ratio Converter with Low Input Current Ripple and Wide Soft-Switching Range for Photovoltaic Applications. IEEE Trans. Power Electron. 2020, 35, 7226–7234. [Google Scholar] [CrossRef]

- Zheng, Y.; Brown, B.; Xie, W.; Li, S.; Smedley, K. High Step-Up DC–DC Converter with Zero Voltage Switching and Low Input Current Ripple. IEEE Trans. Power Electron. 2020, 35, 9416–9429. [Google Scholar] [CrossRef]

- Sugali, H.; Sathyan, S. Design and Analysis of Zero Current Switching Y-Source DC/DC Converter for Renewable Energy Applications. In Proceedings of the 2021 IEEE Kansas Power and Energy Conference (KPEC), Manhattan, KS, USA, 19–20 April 2021; IEEE: New York, NY, USA; pp. 1–5. [Google Scholar] [CrossRef]

- Guan, Y.; Cheng, Y.; Yao, T.; Wang, Y.; Wang, W.; Xu, D. A High-Performance DC–DC Converter with Soft Switching Characteristic and High Voltage Gain. IEEE Trans. Power Electron. 2022, 37, 12279–12288. [Google Scholar] [CrossRef]

| K | dmax | B | N1:N2:N3 |

|---|---|---|---|

| 2 | 1/2 | (1:1:3), (2:1:4), (1:2:5) | |

| 3 | 1/3 | (1:1:2), (3:1:3), (4:2:5) | |

| 4 | 1/4 | (2:1:2), (1:2:3), (5:1:3) | |

| 5 | 1/5 | (3:1:2), (2:2:3), (1:3:4) | |

| 6 | 1/6 | (4:1:2), (3:2:3), (2:3:4) |

| Class | Topology | B | dmax | Degrees of Freedom |

|---|---|---|---|---|

| Class of Z-Source | Z-Source [8] | 1 | ||

| qZ-Source [12] | 1 | |||

| SI-qZ-Source [13] | 1 | |||

| C-qZ-Source [16] | 2 | |||

| other coupled-inductance impedance Source converters | LCCT-Source [18] | 2 | ||

| T-Source [19] | 2 | |||

| Γ-Source [20] | 2 | |||

| Δ-source [21] | 2 | |||

| Class of Y-Source | Y-Source [22] | 3 |

| K | dmax | B | N1:N2:N3 |

|---|---|---|---|

| 2 | 1 | (1 + 2d)/(1 − d) | (1:1:3), (2:1:4), (1:2:5) |

| 3 | 1 | (1 + 3d)/(1 − d) | (1:1:2), (3:1:3), (4:2:5) |

| 4 | 1 | (1 + 4d)/(1 − d) | (2:1:2), (1:2:3), (5:1:3) |

| 5 | 1 | (1 + 5d)/(1 − d) | (3:1:2), (2:2:3), (1:3:4) |

| 6 | 1 | (1 + 6d)/(1 − d) | (4:1:2), (3:2:3), (2:3:4) |

| Class | Topology | B | dmax | Continuous Input Current | Inrush Current | Inductive Volume | Switching Stress | Component Voltage Stress | |||

|---|---|---|---|---|---|---|---|---|---|---|---|

| VC1, MAX /Vin | VC2, MAX /Vin | VD1, MAX /Vin | VS, MAX /Vin | ||||||||

| Traditional Y-Source | YSC [22] | no | high | big | high | - | |||||

| Quasi Y-source | qYSC-II [36] | yes | low | big | high | ||||||

| qYSC-III [38] | yes | low | small | high | |||||||

| Modified Y-Source | M-YSC [39] | 1 | yes | low | big | low | |||||

| Mode | VL |

|---|---|

| Non-Shoot-Through state | |

| Intermediate state | |

| Shoot-Through state |

| Topology | B | ILO,MAX/Iin | IS1,MAX/Iin | IS2,MAX/Iin | Average Magnetizing Current |

|---|---|---|---|---|---|

| VD-qYSC-I [42] | - | - | high | ||

| LH-qYSC-I [44] | - | - | high | ||

| DA-qYSC [45] | 1 | - | high | ||

| O-qYSC [47] | 1 | - | 0 | ||

| LCD-qYSC [48] | - | 0 | |||

| AC-qYSC-I [51] | - | 0 |

| Topology | VC1,MAX/Vin | VC2,MAX/Vin | VC3,MAX/Vin | VD1,MAX/Vin | VD2,MAX/Vin | VD3,MAX/Vin |

|---|---|---|---|---|---|---|

| VD-qYSC-I [42] | 0 | |||||

| LH-qYSC-I [44] | - | |||||

| DA-qYSC [45] | - | |||||

| O-qYSC [47] | - | |||||

| LCD-qYSC [48] | ||||||

| AC-qYSC-I [51] |

| Topology | B | VS,MAX/Vin | VD1,MAX/Vin | VD2,MAX/Vin | VC1,MAX/Vin | VC2,MAX/Vin |

|---|---|---|---|---|---|---|

| M-YSC [39] | ||||||

| CB-qYSC [52] | ||||||

| CB-M-YSC [33] | ||||||

| L-qYSC-I [53] | ||||||

| L-qYSC-II [53] | ||||||

| L-qYSC-III [53] | ||||||

| L-M-YSC-I [59] | ||||||

| L-M-YSC-II [59] | ||||||

| L-M-YSC-III [59] |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, H.; Wang, P.; Yan, E.; Wang, W.; Xu, D. A Review of Non-Isolated High-Gain Y-Source Converters Topologies. Energies 2024, 17, 2850. https://doi.org/10.3390/en17122850

Wang H, Wang P, Yan E, Wang W, Xu D. A Review of Non-Isolated High-Gain Y-Source Converters Topologies. Energies. 2024; 17(12):2850. https://doi.org/10.3390/en17122850

Chicago/Turabian StyleWang, Hao, Panbao Wang, Enpeng Yan, Wei Wang, and Dianguo Xu. 2024. "A Review of Non-Isolated High-Gain Y-Source Converters Topologies" Energies 17, no. 12: 2850. https://doi.org/10.3390/en17122850

APA StyleWang, H., Wang, P., Yan, E., Wang, W., & Xu, D. (2024). A Review of Non-Isolated High-Gain Y-Source Converters Topologies. Energies, 17(12), 2850. https://doi.org/10.3390/en17122850