A Study on the Distributed-Control Architecture of a DSP-Based Solid-State Transformer System with Implementation

Abstract

:1. Introduction

2. SST System Configuration

3. Design of D-CA for SST

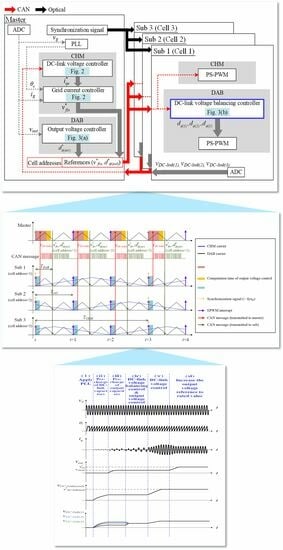

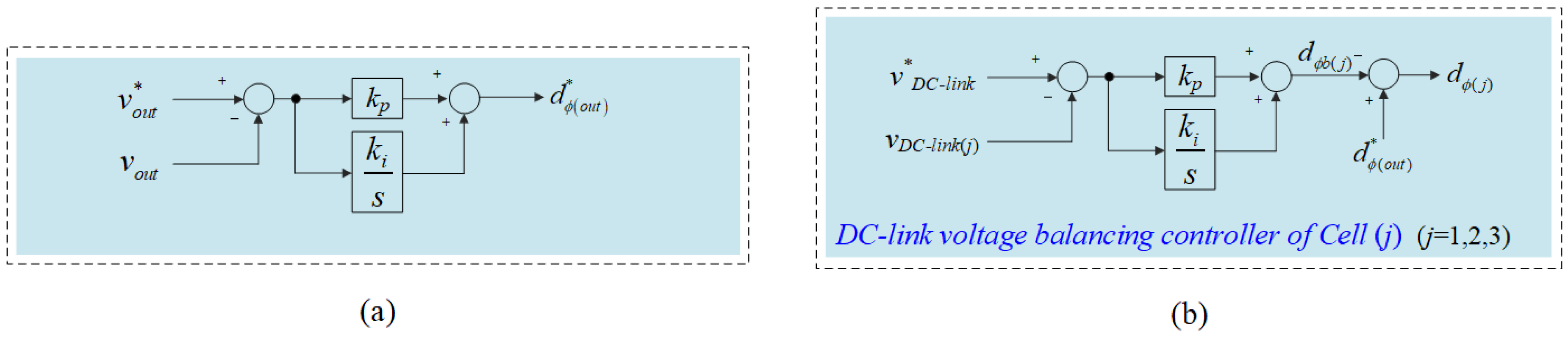

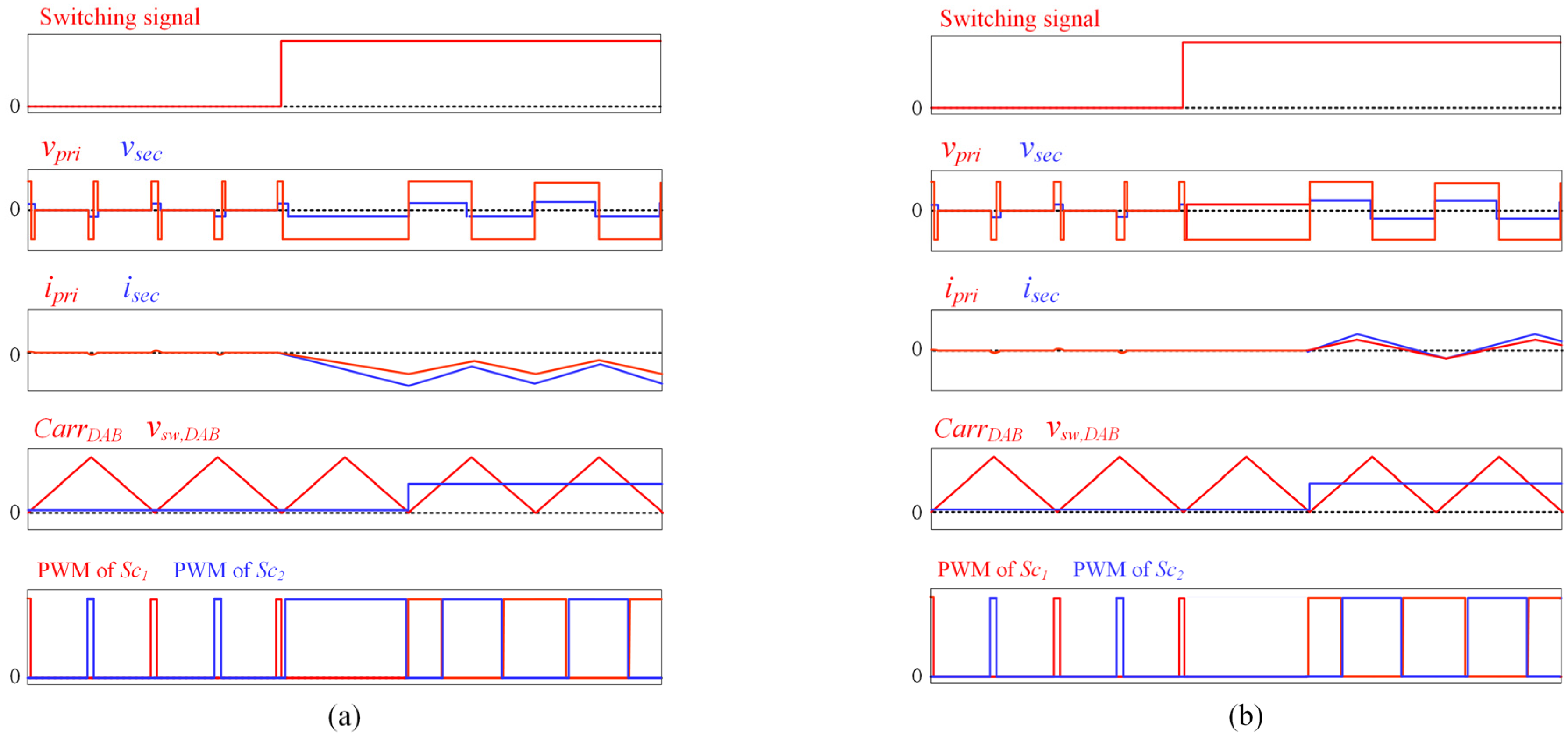

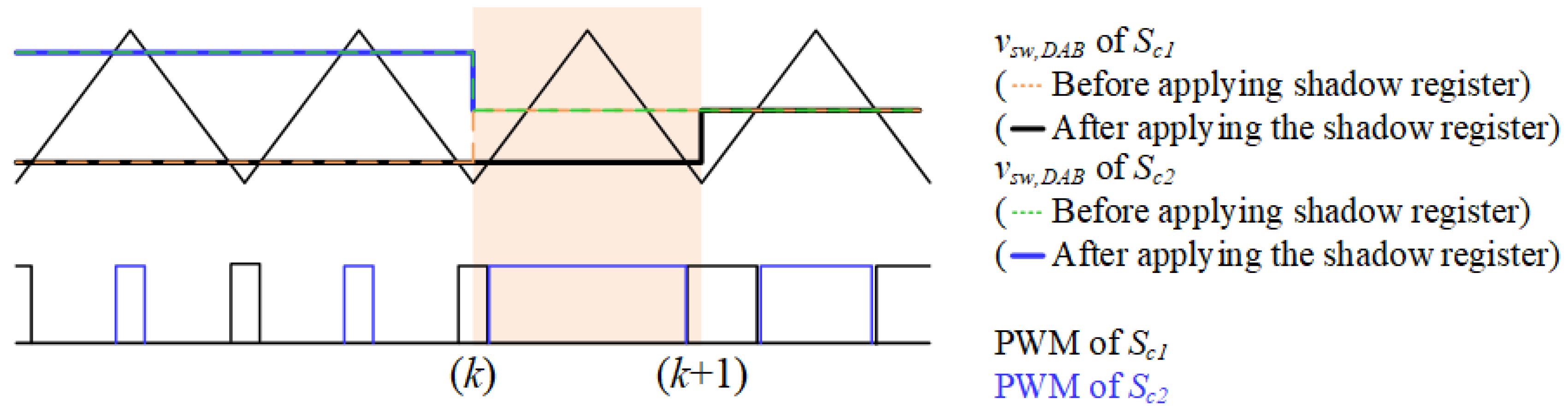

3.1. Control Technique of CHM and DAB Converters

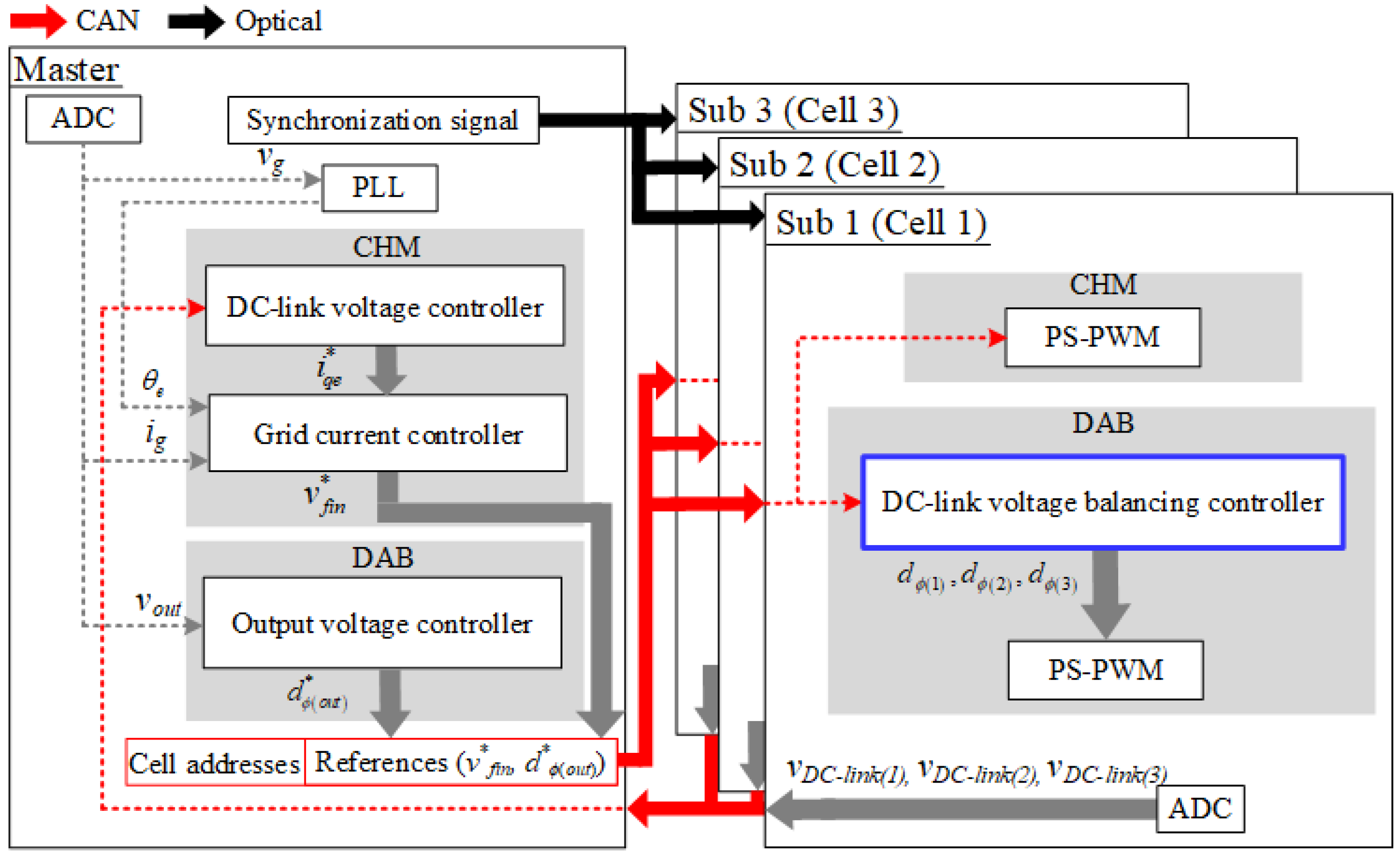

3.2. Distributed-Control Architecture (D-CA)

4. Operation Sequence with Start-Up Strategies

4.1. Operation Sequence

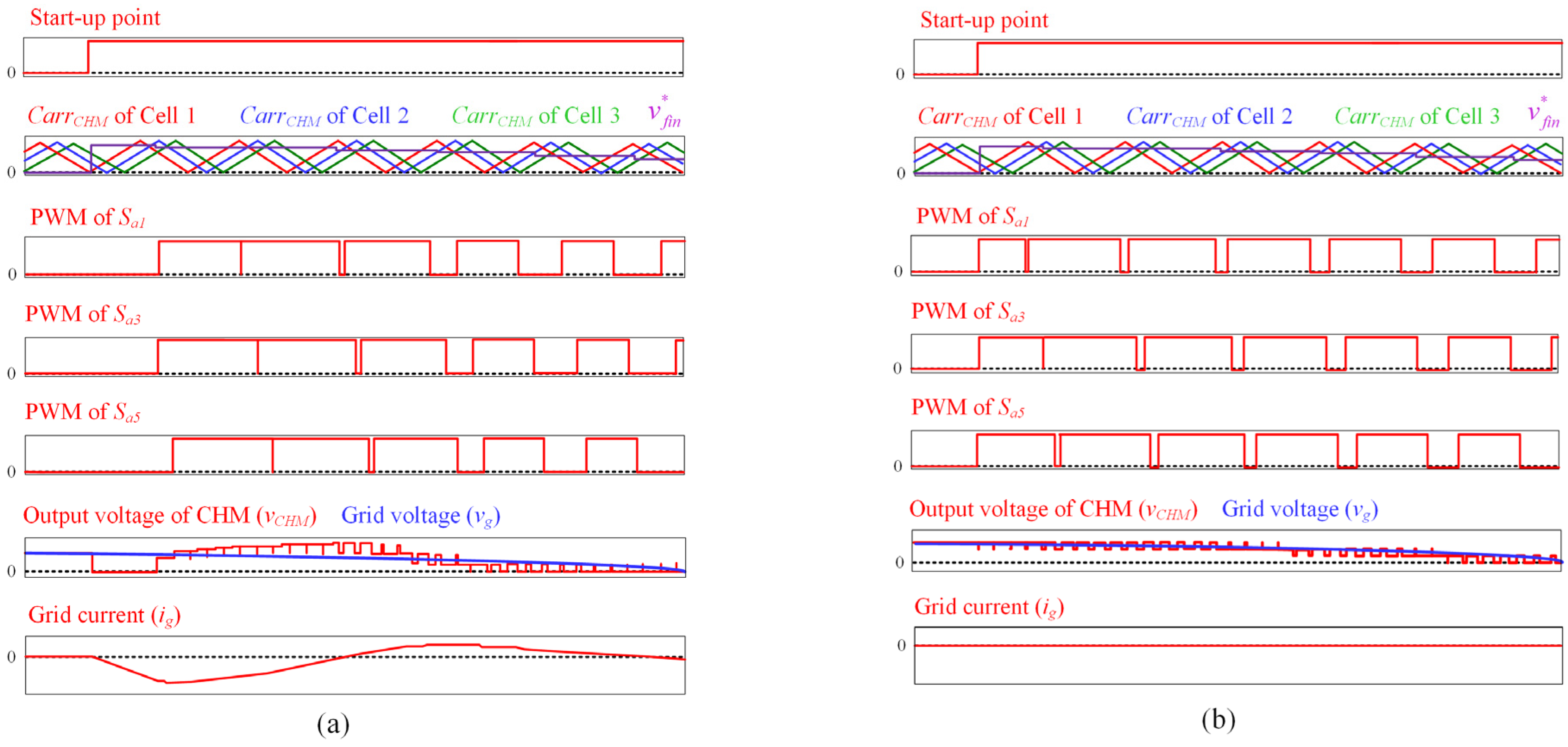

4.2. Start-Up Strategy of CHM Converter

4.3. Start-Up Strategy of DAB Converter

5. Experimental Results

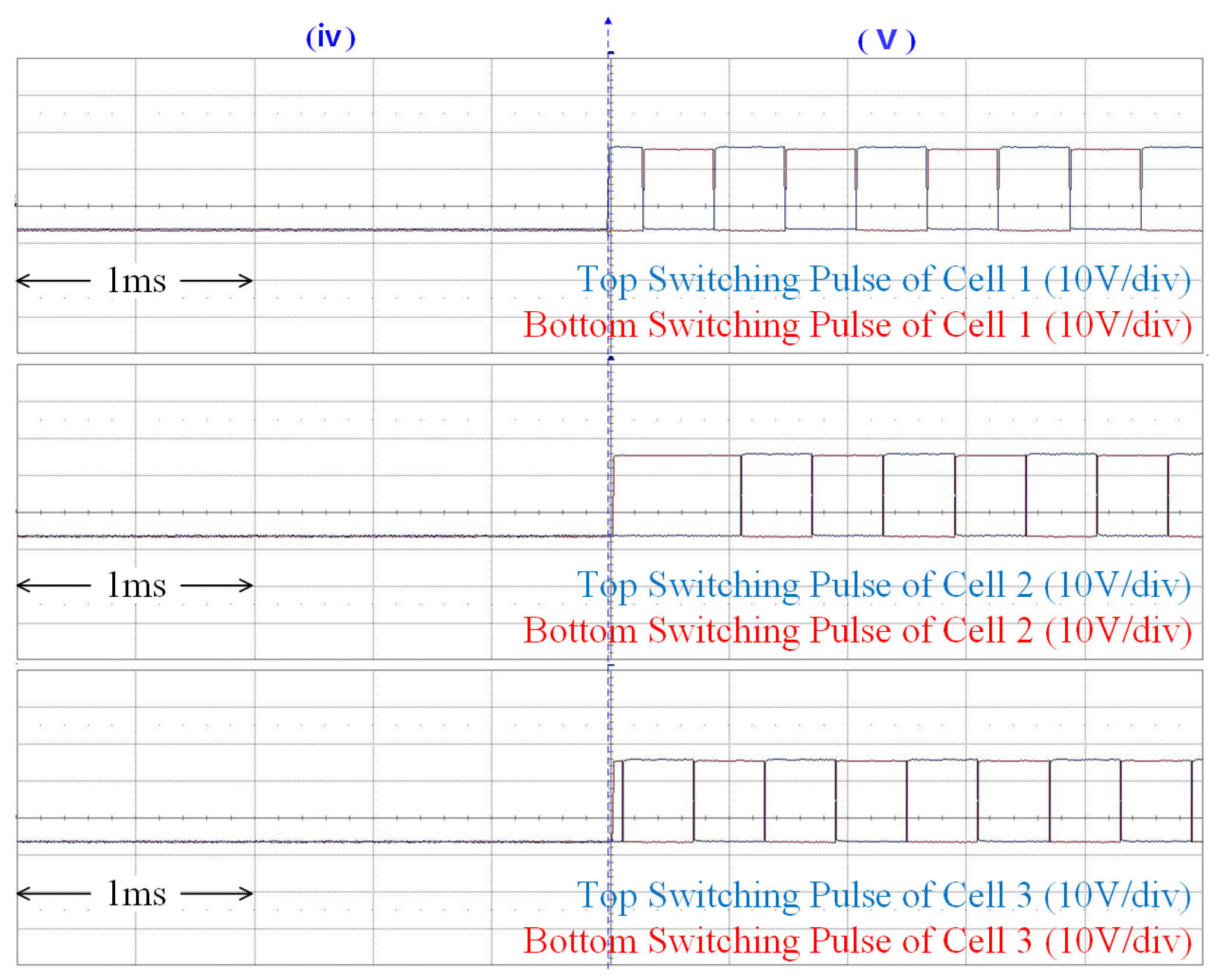

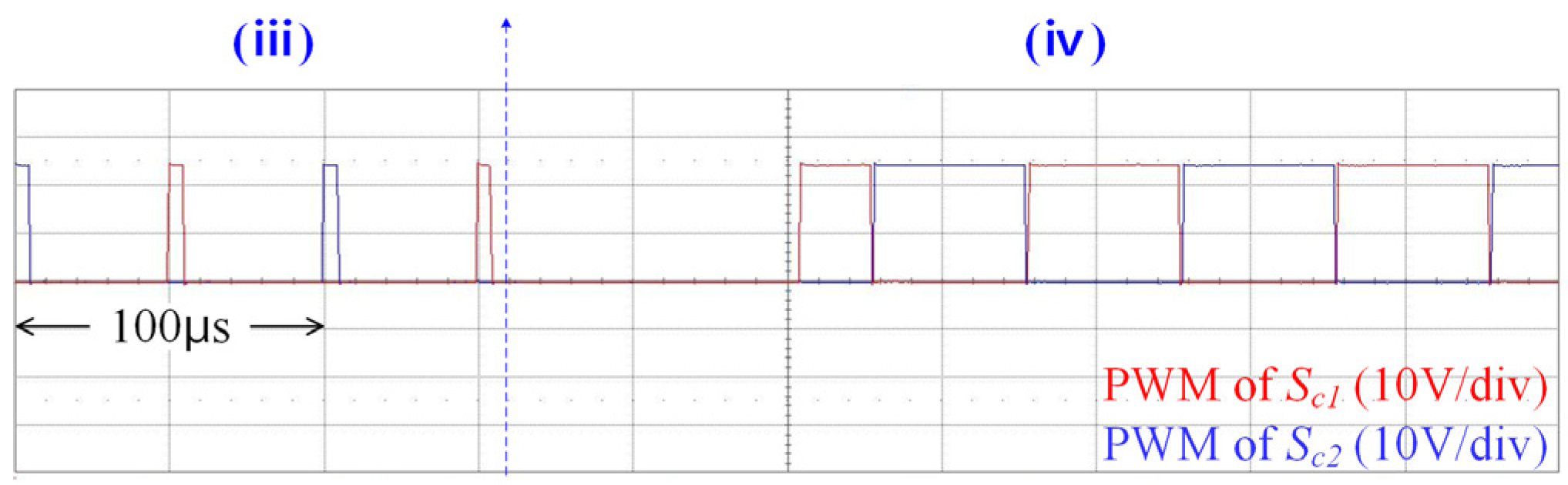

5.1. The Verification of D-CA

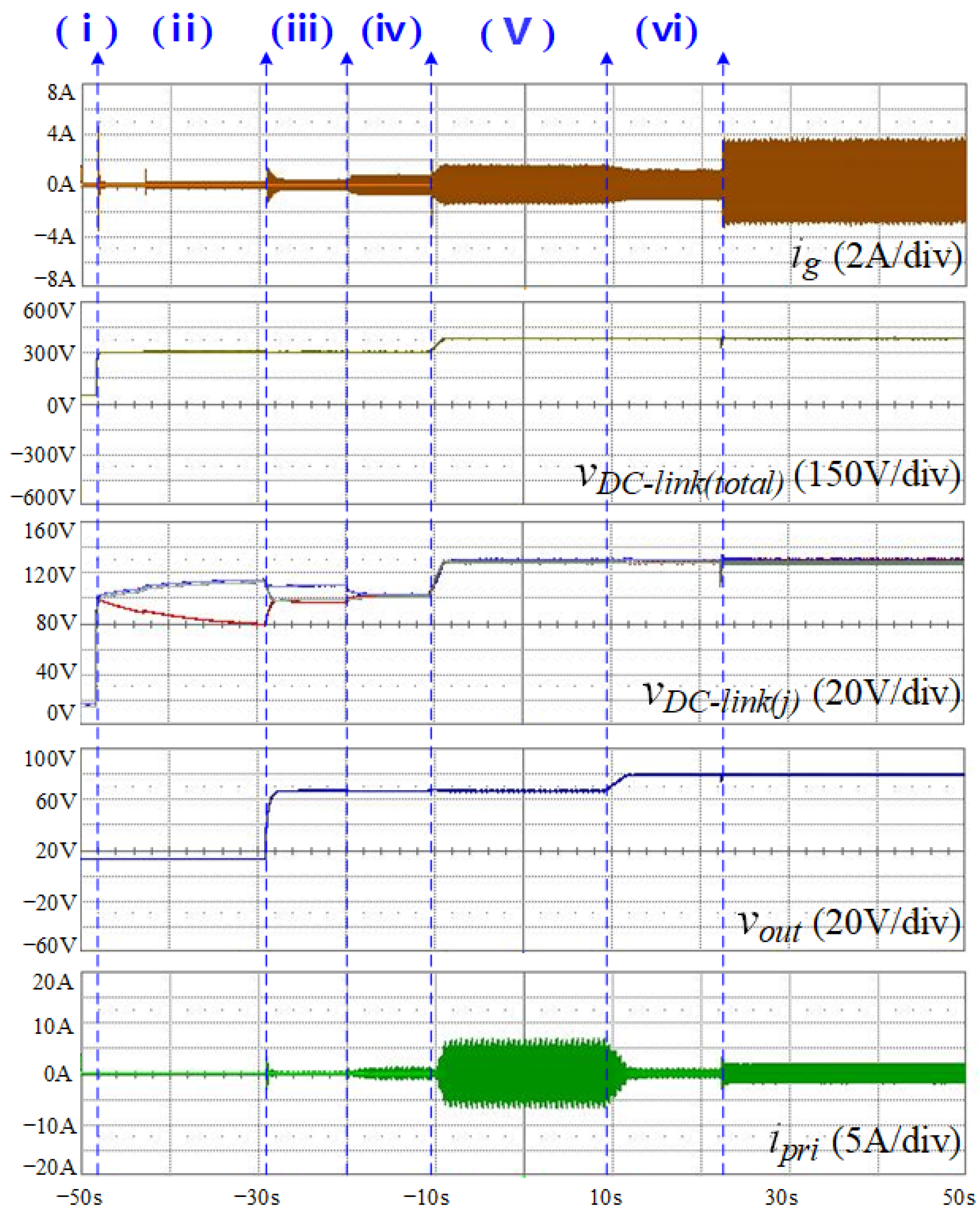

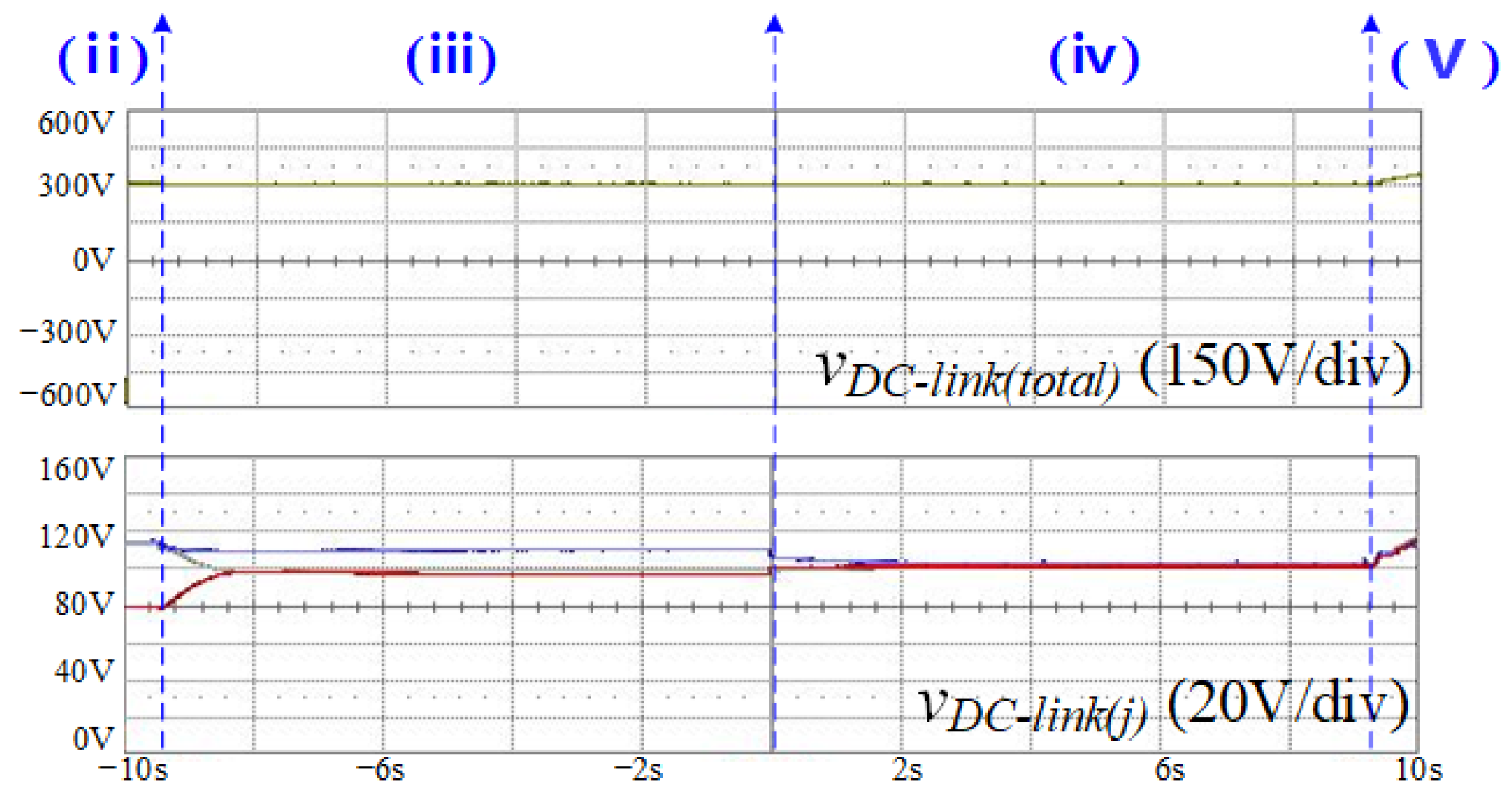

5.2. The Verification of Operation Sequence and Start-Up Strategy

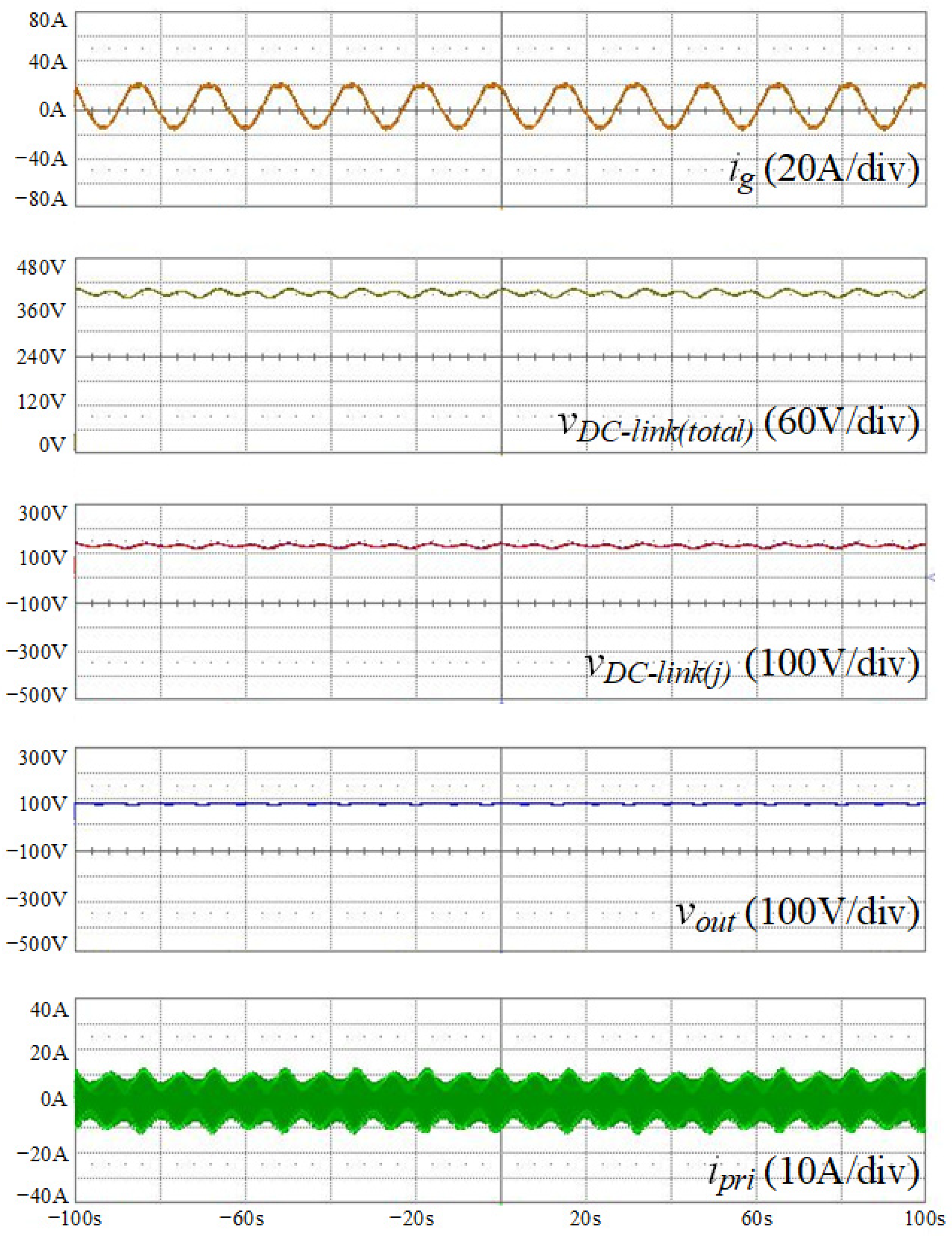

5.3. Rated Operation of the Designed SST

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Yi, Z.; Chen, K.; Yin, L.; Wang, K. Sensing as the key to the safety and sustainability of new energy storage devices. Prot. Control Mod. Power Syst. 2023, 8, 27. [Google Scholar] [CrossRef]

- Ma, N.; Yin, H.; Wang, K. Prediction of the Remaining Useful Life of Supercapacitors at Different Temperatures Based on Improved Long Short-Term Memory. Energies 2023, 16, 5240. [Google Scholar] [CrossRef]

- Syed, I.; Khadkikar, V. Replacing the Grid Interface Transformer in Wind Energy Conversion System with Solid-State Transformer. IEEE Trans. Power Syst. 2017, 32, 2152–2160. [Google Scholar] [CrossRef]

- Ronan, E.R.; Sudhoff, S.D.; Glover, S.F.; Galloway, D.L. A power electronic-based distribution transformer. IEEE Trans. Power Deliv. 2002, 17, 537–543. [Google Scholar] [CrossRef]

- Kang, M.; Enjeti, P.N.; Pitel, I.J. Analysis and design of electronic transformers for electric power distribution system. IEEE Trans. Ind. Electron. 1999, 14, 1133–1141. [Google Scholar] [CrossRef]

- Bhattacharya, S.; Zhao, T.; Wang, G.; Dutta, S.; Baek, S.; Du, Y.; Parkhideh, B.; Zhou, X.; Huang, A.Q. Design and development of Generation-I silicon based Solid State Transformer. In Proceedings of the Twenty-Fifth Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Palm Springs, CA, USA, 21–25 February 2010; pp. 1666–1673. [Google Scholar]

- Manjrekar, M.D.; Kieferndorf, R.; Venkataramanan, G. Power electronic transformers for utility applications. IEEE Ind. Appl. Conf. 2000, 4, 2496–2502. [Google Scholar]

- Zhao, T.; Yang, L.; Wang, J.; Huang, A.Q. 270 kVA Solid State Transformer Based on 10 kV SiC Power Devices. In Proceedings of the IEEE Electric Ship Technologies Symposium, Arlington, VI, USA, 21–23 May 2007; pp. 145–149. [Google Scholar]

- Wang, D.; Tian, J.; Mao, C.; Lu, J.; Duan, Y.; Qiu, J.; Cai, H. A 10-kV/400-V 500-kVA Electronic Power Transformer. IEEE Trans. Ind. Electron. 2016, 63, 6653–6663. [Google Scholar] [CrossRef]

- Venkat, J.; Shukla, A.; Kulkarni, S.V. Operation of a three phase solid state-Transformer under unbalanced load conditions. In Proceedings of the IEEE International Conference on Power Electronics, Drives and Energy Systems (PEDES), Mumbai, India, 16–19 December 2014; pp. 1–6. [Google Scholar]

- She, X.; Huang, A.Q.; Burgos, R. Review of Solid-State Transformer Technologies and Their Application in Power Distribution Systems. IEEE J. Emerg. Sel. Top. Power Electron. 2013, 1, 186–198. [Google Scholar] [CrossRef]

- Ge, J.; Zhao, Z.; Yuan, L.; Lu, T. Energy Feed-Forward and Direct Feed-Forward Control for Solid-State Transformer. IEEE Trans. Ind. Electron. 2015, 30, 4042–4047. [Google Scholar] [CrossRef]

- Lee, E.S.; Park, J.H.; Kim, M.Y.; Lee, J.S. High Efficiency Integrated Transformer Design in DAB Converters for Solid-State Transformers. IEEE Trans. Veh. Technol. 2022, 71, 7147–7160. [Google Scholar] [CrossRef]

- Rajendran, S.; Sen, S.; Guo, Z.; Huang, A.Q. 500 kVA Hybrid Solid State Transformer (HSST): Modelling and Control. In Proceedings of the IEEE Energy Conversion Congress and Exposition, Vancouver, BC, Canada, 10–14 October 2021; pp. 1135–1141. [Google Scholar]

- Busarello, T.D.; Mortezaei, A.; Paredes, H.K.; Al-Durra, A.; Pomilio, J.A.; Simoes, M.G. Simplified Small-Signal Model for Output Voltage Control of Asymmetric Cascaded H-Bridge Multilevel Inverter. IEEE Trans. on Power Electron. 2018, 33, 3509–3519. [Google Scholar] [CrossRef]

- Acharya, A.K.; Kumar, K.; Chowdary, K.V.; Sahu, P.K. Enhancement of Dynamic Performance of a Single Phase Cascaded H-Bridge Multilevel Inverter Using Closed Loop Controllers. In Proceedings of the 2020 International Conference on Computational Intelligence for Smart Power System and Sustainable Energy (CISPSSE), Keonjhar, India, 29–31 July 2020; pp. 1–5. [Google Scholar]

- Roggia, L.; Beltrame, F.; Schuch, L.; Pinheiro, J.R. Comparison between full-bridge-forward converter and DAB converter. In Proceedings of the 2013 Brazilian Power Electronics Conference, Gramado, Brazil, 27–31 October 2013; pp. 224–229. [Google Scholar]

- Wang, L.; Zhang, D.; Wang, Y.; Wu, B.; Athab, H.S. Power and Voltage Balance Control of a Novel Three-Phase Solid-State Transformer Using Multilevel Cascaded H-Bridge Inverters for Microgrid Applications. IEEE Trans. Power Electron. 2016, 31, 3289–3301. [Google Scholar] [CrossRef]

- Li, H.; Wang, Y.; Yu, C. Research on voltage balance and power balance control for three-phase cascaded multilevel converter based power electronic transformer. In Proceedings of the IECON 2016—42nd Annual Conference of the IEEE Industrial Electronics Society, Florence, Italy, 24–27 October 2016; pp. 3588–3593. [Google Scholar]

- Eroğlu, F.; Kurtoğlu, M.; Eren, A.; Vural, A.M. Level-Shifted Pulse Width Modulation Based Battery State-of-Charge Balancing Method for Single-Phase Cascaded H-Bridge Multilevel Converters. In Proceedings of the 2021 13th International Conference on Electrical and Electronics Engineering (ELECO), Bursa, Turkey, 25–27 November 2021; pp. 560–564. [Google Scholar]

- Korhonen, J.; Järvisalo, H.; Jäppinen, J.; Silventoinen, P. Level-phase-shifted pulse-width modulation for cascaded H-bridges. In Proceedings of the IECON 2022—48th Annual Conference of the IEEE Industrial Electronics Society, Brussels, Belgium, 17–20 October 2022; pp. 1–6. [Google Scholar]

- McGrath, B.P.; Holmes, D.G. Multicarrier PWM strategies for multilevel inverters. IEEE Trans. Ind. Electron. 2002, 49, 858–867. [Google Scholar] [CrossRef]

- Lee, S.Y.; Woo, M.H.; Kim, J.K.; Ryu, S.P. A novel method to improve output voltage quality of grid-connected Cascaded H-Bridge Multilevel converter with Phase-Shifted PWM and serial bus communication. In Proceedings of the 2012 IEEE Energy Conversion Congress and Exposition (ECCE), Raleigh, NC, USA, 15–20 September 2012; pp. 4513–4518. [Google Scholar]

- De Doncker, R.W.; Divan, D.M.; Kheraluwala, M.H. A three-phase soft-switched high-power-density DC/DC converter for high-power applications. IEEE Trans. Ind. Electron. 1991, 27, 63–73. [Google Scholar] [CrossRef]

- Zhou, H.; Khambadkone, A.M. Hybrid Modulation for Dual-Active-Bridge Bidirectional Converter with Extended Power Range for Ultracapacitor Application. IEEE Trans. Ind. Appl. 2009, 45, 1434–1442. [Google Scholar] [CrossRef]

- Cuartas, J.M.; de la Cruz, A.; Briz, F.; Lopez, M. Start-up, functionalities and protection issues for CHB-based solid state transformers. In Proceedings of the 2017 IEEE International Conference on Environment and Electrical Engineering and 2017 IEEE Industrial and Commercial Power Systems Europe (EEEIC/I&CPS Europe), Milan, Italy, 6–9 June 2017; pp. 1–5. [Google Scholar]

- Xiao, F.; Tu, C.; Ge, Q.; Zhou, K.; Guo, Q.; Lan, Z. Ripple Voltage Suppression and Control Strategy for CHB-Based Solid-State Transformer. IEEE J. Emerg. Sel. Top. Power Electron. 2021, 9, 1104–1118. [Google Scholar] [CrossRef]

- Hannan, M.A.; Ker, P.J.; Lipu, M.S.; Choi, Z.H.; Rahman, M.S.; Muttaqi, K.M.; Blaabjerg, F. State of the Art of Solid-State Transformers: Advanced Topologies, Implementation Issues, Recent Progress and Improvements. IEEE Access 2020, 8, 19113–19132. [Google Scholar] [CrossRef]

- Bhawal, S.; Chakraborty, S.S.; Hatua, K. Dynamic Modeling and Closed-Loop Control of a Solid-State Transformer (SST) Based on Series Resonant Converter (SRC). IEEE J. Emerg. Sel. Top. Power Electron. 2022, 10, 3733–3745. [Google Scholar] [CrossRef]

- Xu, W.; Guo, Z.; Vetrivelan, A.; Yu, R.; Huang, A.Q. Hardware Design of a 13.8-kV/3-MVA PV Plus Storage Solid-State Transformer (PVS-SST). IEEE J. Emerg. Sel. Top. Power Electron. 2022, 10, 3571–3586. [Google Scholar] [CrossRef]

- Saeed, M.; Cuartas, J.M.; Rodríguez, A.; Arias, M.; Briz, F. Energization and Start-Up of CHB-Based Modular Three-Stage Solid-State Transformers. IEEE Trans. Ind. Appl. 2018, 54, 5483–5492. [Google Scholar] [CrossRef]

- Behera, R.K.; Ojo, O. Modeling and control of DAB converter for solar micro-grid application. In Proceedings of the 2015 6th International Conference on Power Electronics Systems and Applications (PESA), Hong Kong, China, 15–17 December 2015; pp. 1–5. [Google Scholar]

| References | Introduction of Overall Control Sequence | Communication Structure Description | Control Hierarchical Architecture Description |

|---|---|---|---|

| [26] | Presence | None | None |

| [27] | Presence | None | None |

| [28] | None | None | Presence |

| [29] | None | None | Presence |

| [30] | Presence | None | Presence |

| [31] | Presence | None | Partially presence (without a balancing control) |

| Parameter | Value |

|---|---|

| Rated power of SST | 2.56 kW |

| Input grid voltage | 220 Vrms, 60 Hz |

| DC-link voltage of CHM | 390 Vdc |

| Output voltage of DAB | 80 Vdc |

| Input AC filter inductor | 1.9 mH |

| Capacitance of 1 cell DC-link | 1175 μF |

| Capacitance of DAB converter | 2350 μF |

| Switching frequency of CHM | 1.67 kHz |

| Switching frequency of DAB | 10 kHz |

| Control frequency | 5 kHz |

| Turn ratio of MFTR | 1.5:1 |

| Rated output voltage | 80 V |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ju, J.; Choi, D.; Lee, J.-S. A Study on the Distributed-Control Architecture of a DSP-Based Solid-State Transformer System with Implementation. Energies 2023, 16, 6095. https://doi.org/10.3390/en16166095

Ju J, Choi D, Lee J-S. A Study on the Distributed-Control Architecture of a DSP-Based Solid-State Transformer System with Implementation. Energies. 2023; 16(16):6095. https://doi.org/10.3390/en16166095

Chicago/Turabian StyleJu, Jiho, Dongho Choi, and June-Seok Lee. 2023. "A Study on the Distributed-Control Architecture of a DSP-Based Solid-State Transformer System with Implementation" Energies 16, no. 16: 6095. https://doi.org/10.3390/en16166095

APA StyleJu, J., Choi, D., & Lee, J.-S. (2023). A Study on the Distributed-Control Architecture of a DSP-Based Solid-State Transformer System with Implementation. Energies, 16(16), 6095. https://doi.org/10.3390/en16166095