A Bridge-Level Junction Temperature Estimation Method for SiC MOSFETs Combining Transient Voltage and Current Peaks

Abstract

1. Introduction

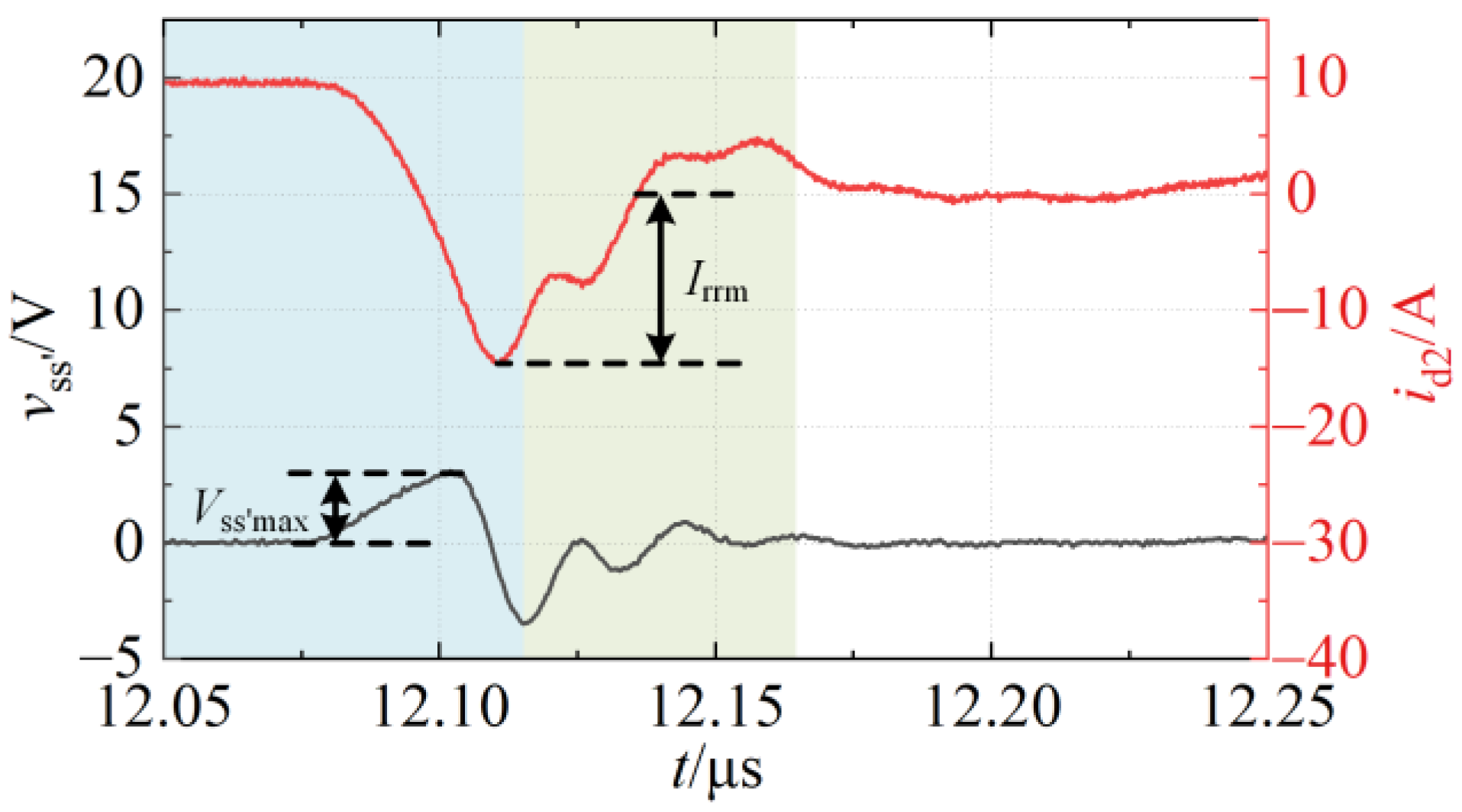

2. Theoretical Analysis of Combining Transient Peaks as a Bridge-Level TSEP

2.1. Commutation Process of SiC MOSFETs in a Phase Leg Structure

2.2. Temperature Dependence Analysis

2.2.1. Peak Induced Voltage

2.2.2. Peak Reverse Recovery Current

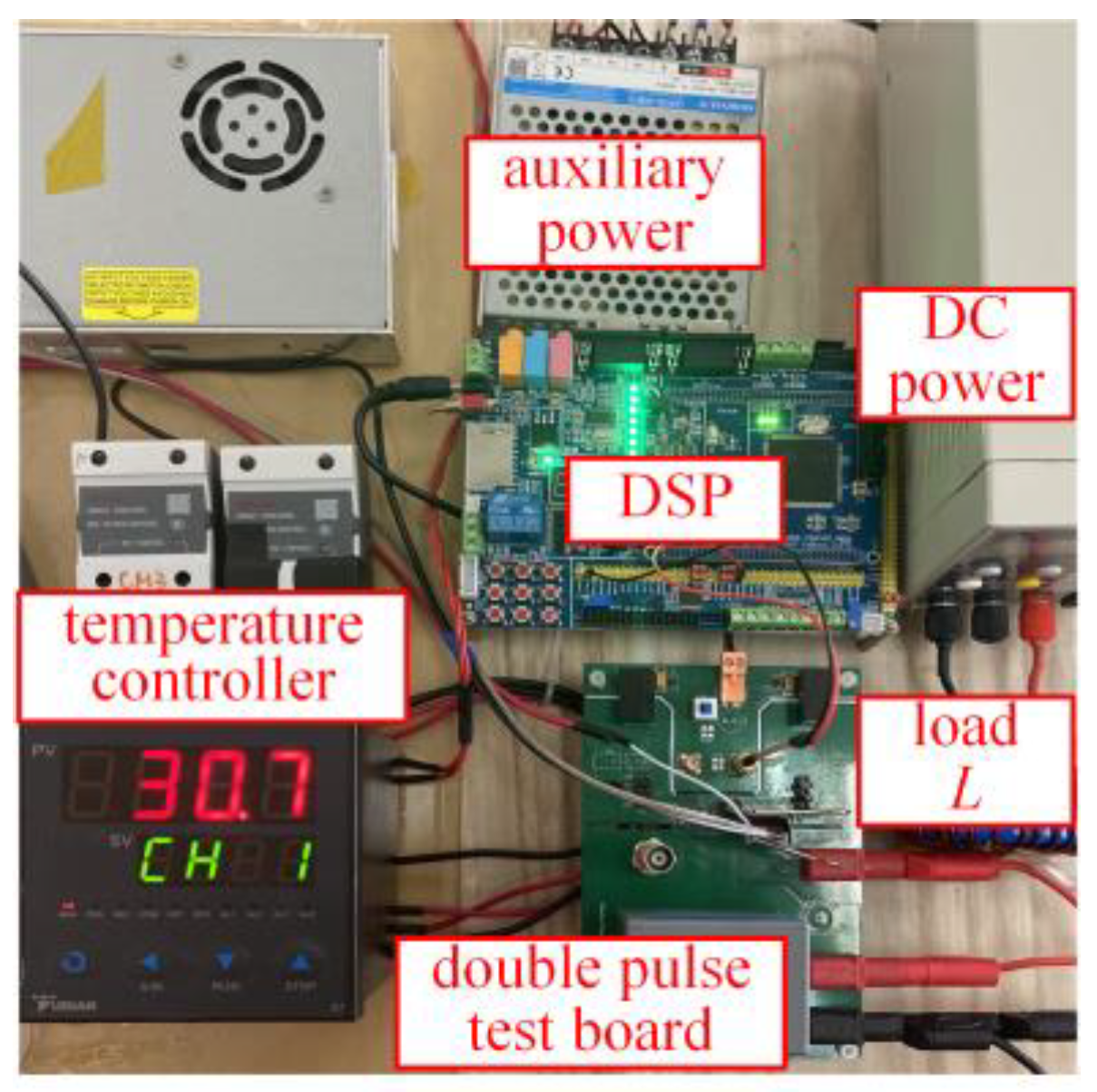

3. Experimental Results

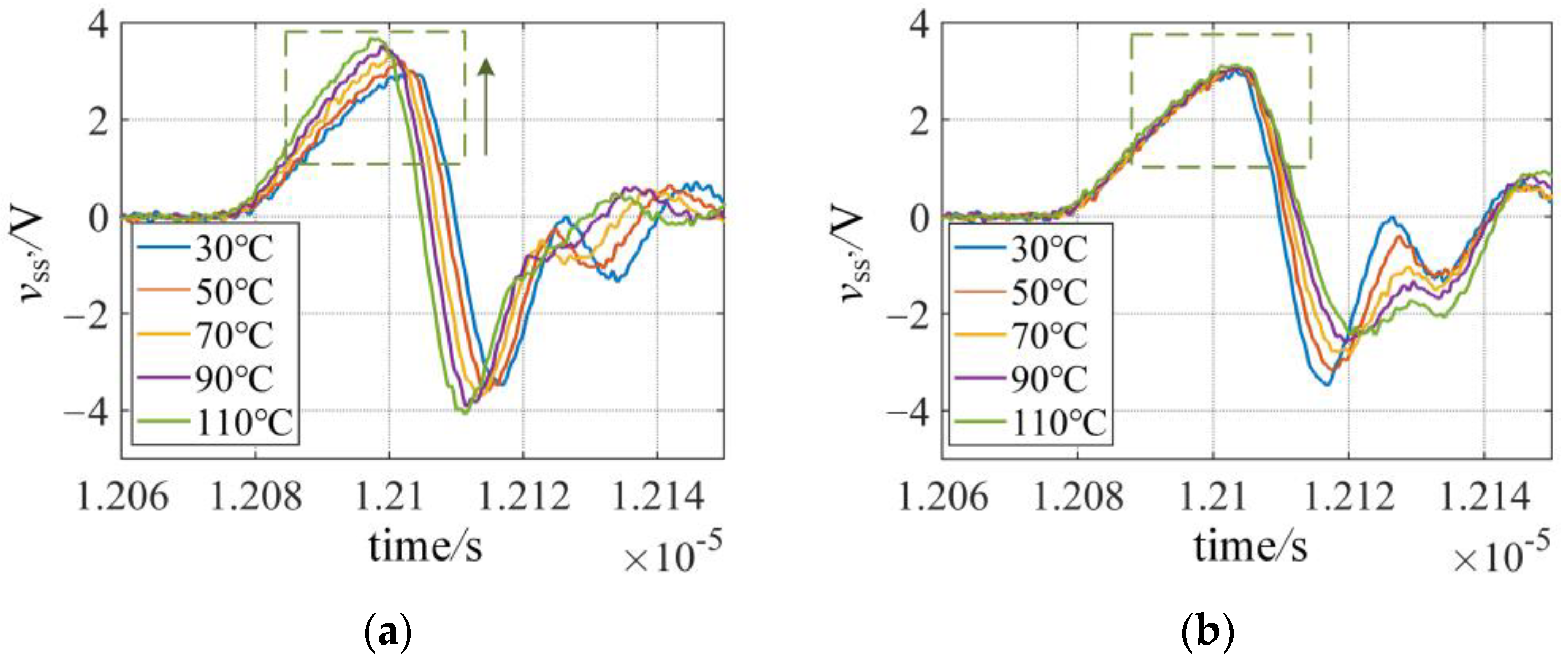

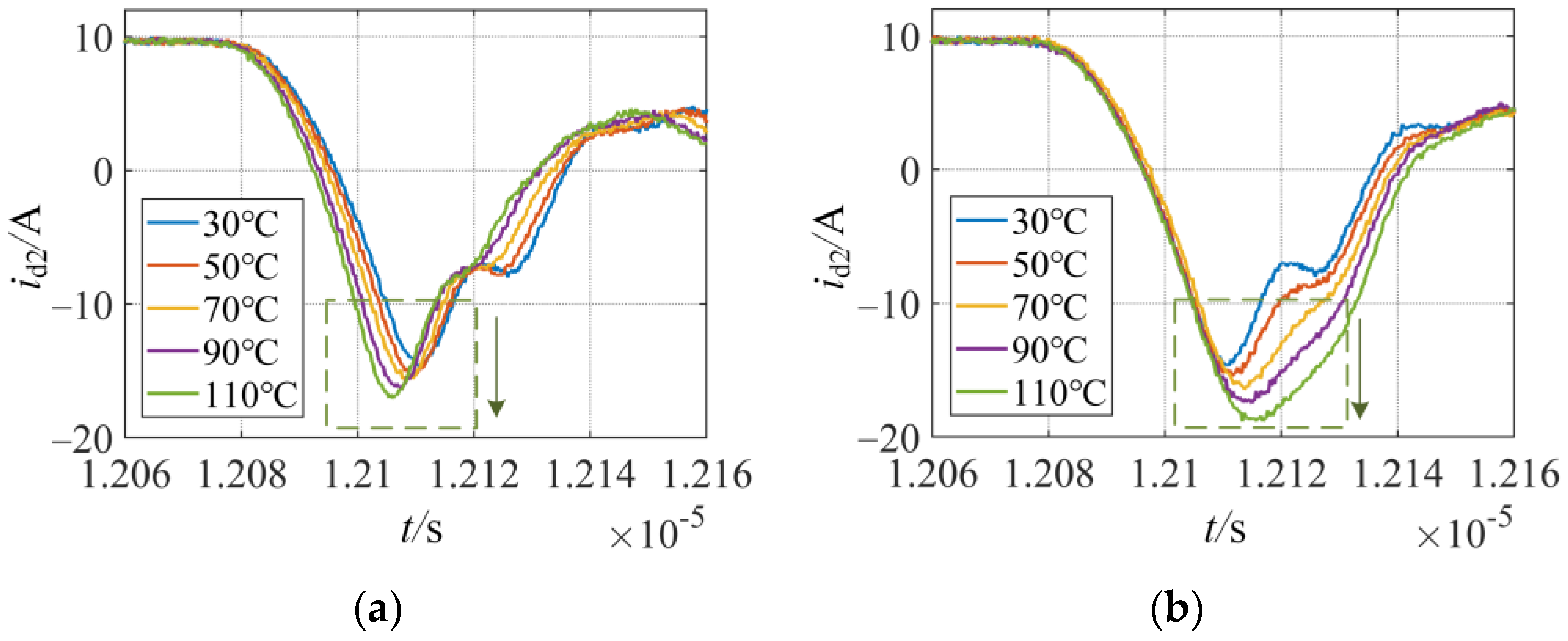

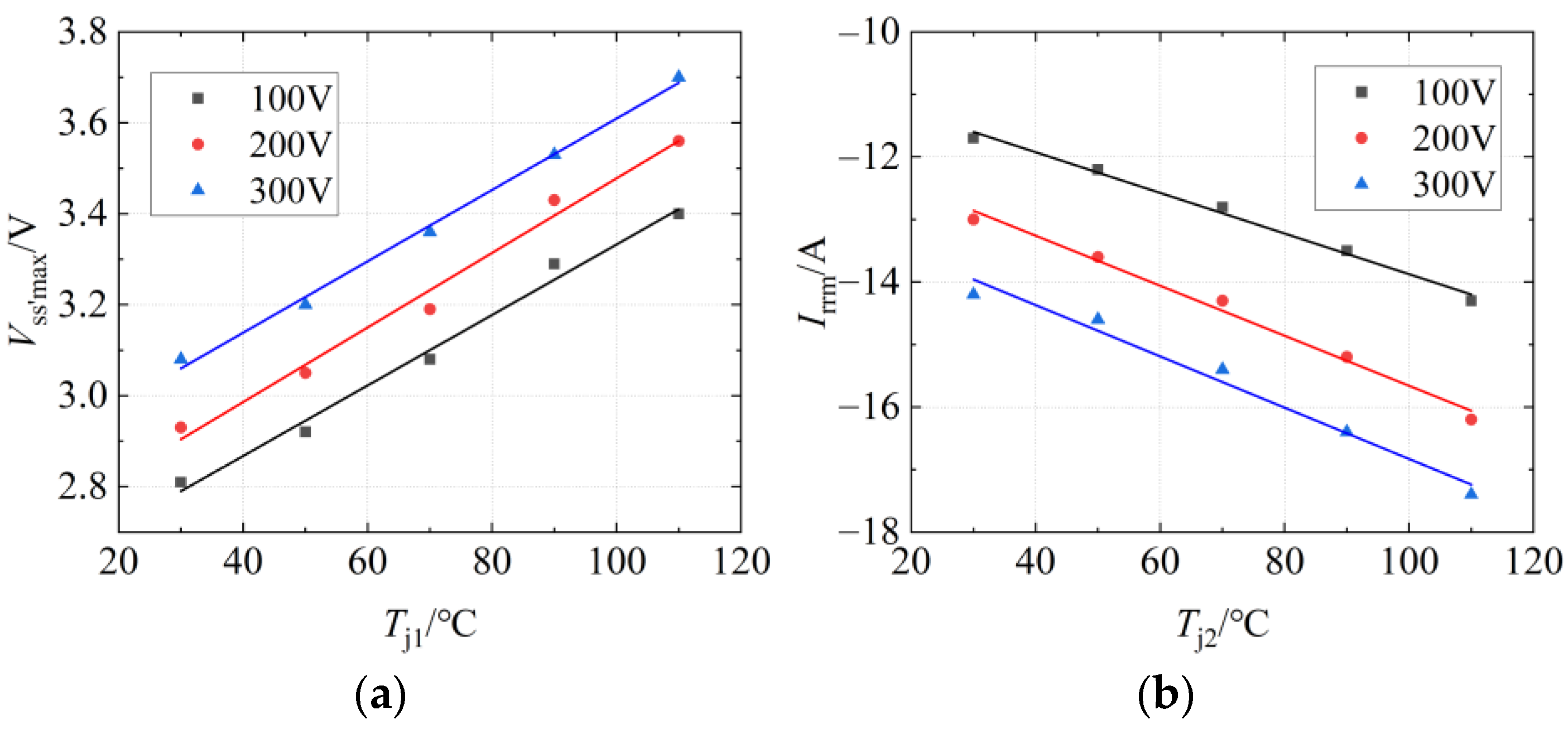

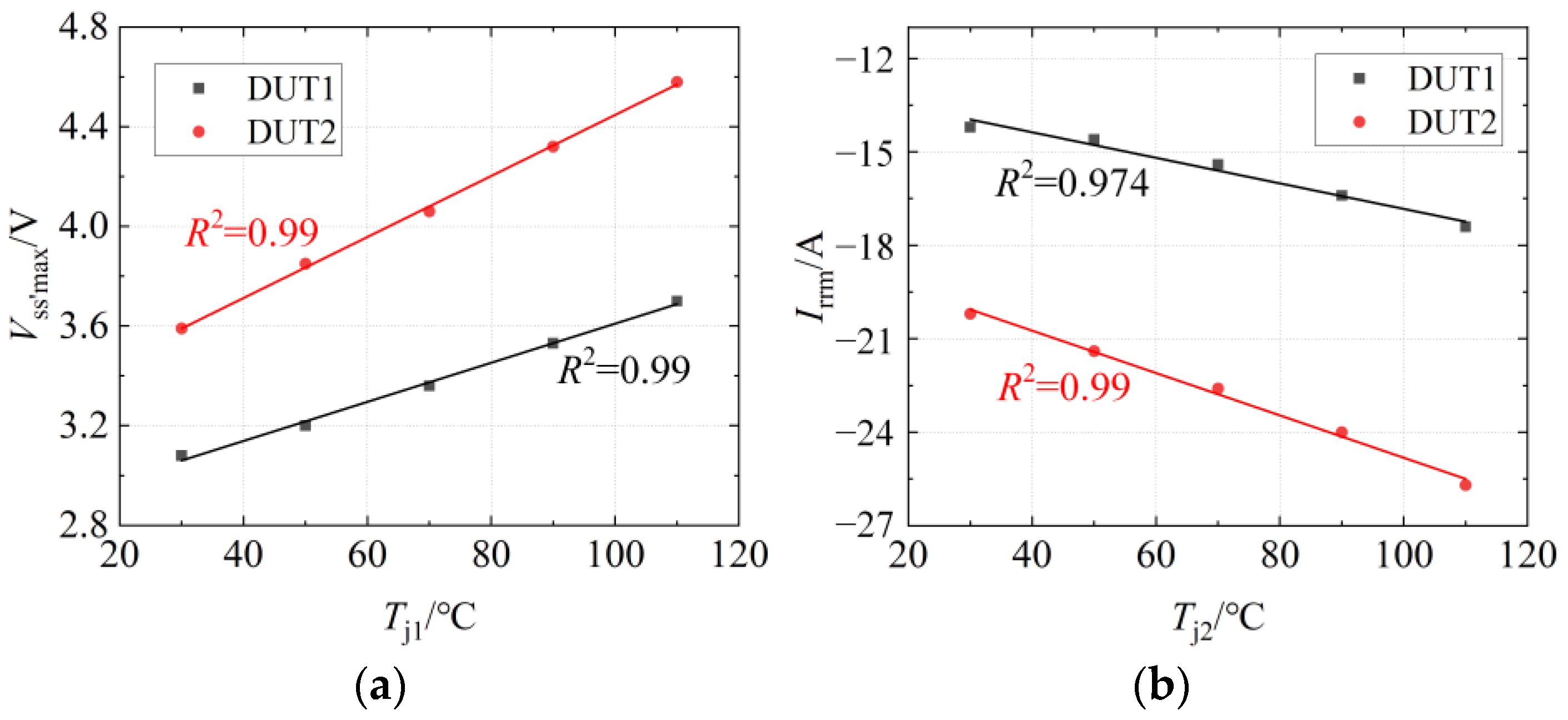

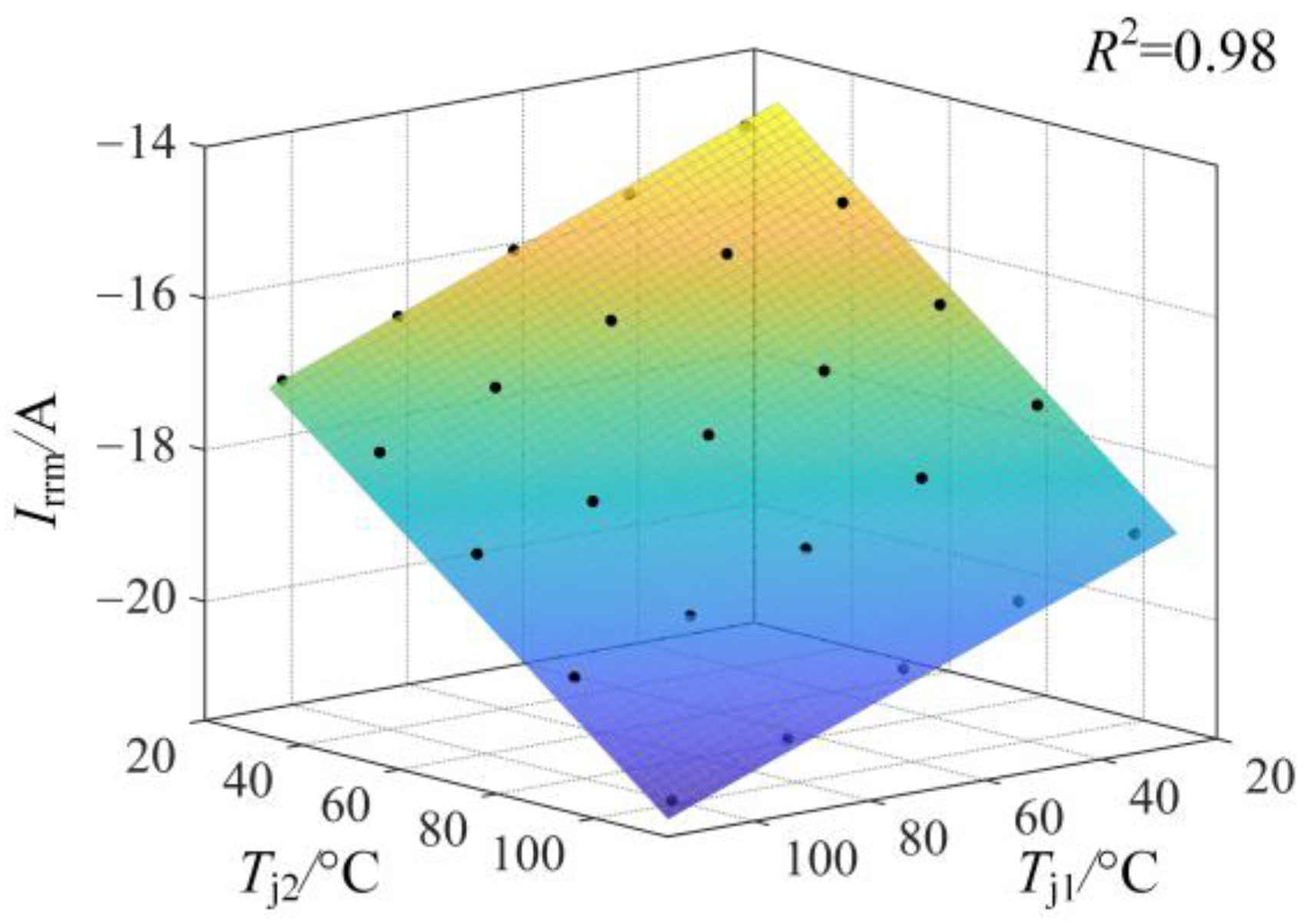

3.1. Temperature Dependence

3.2. Operating Conditions Dependence

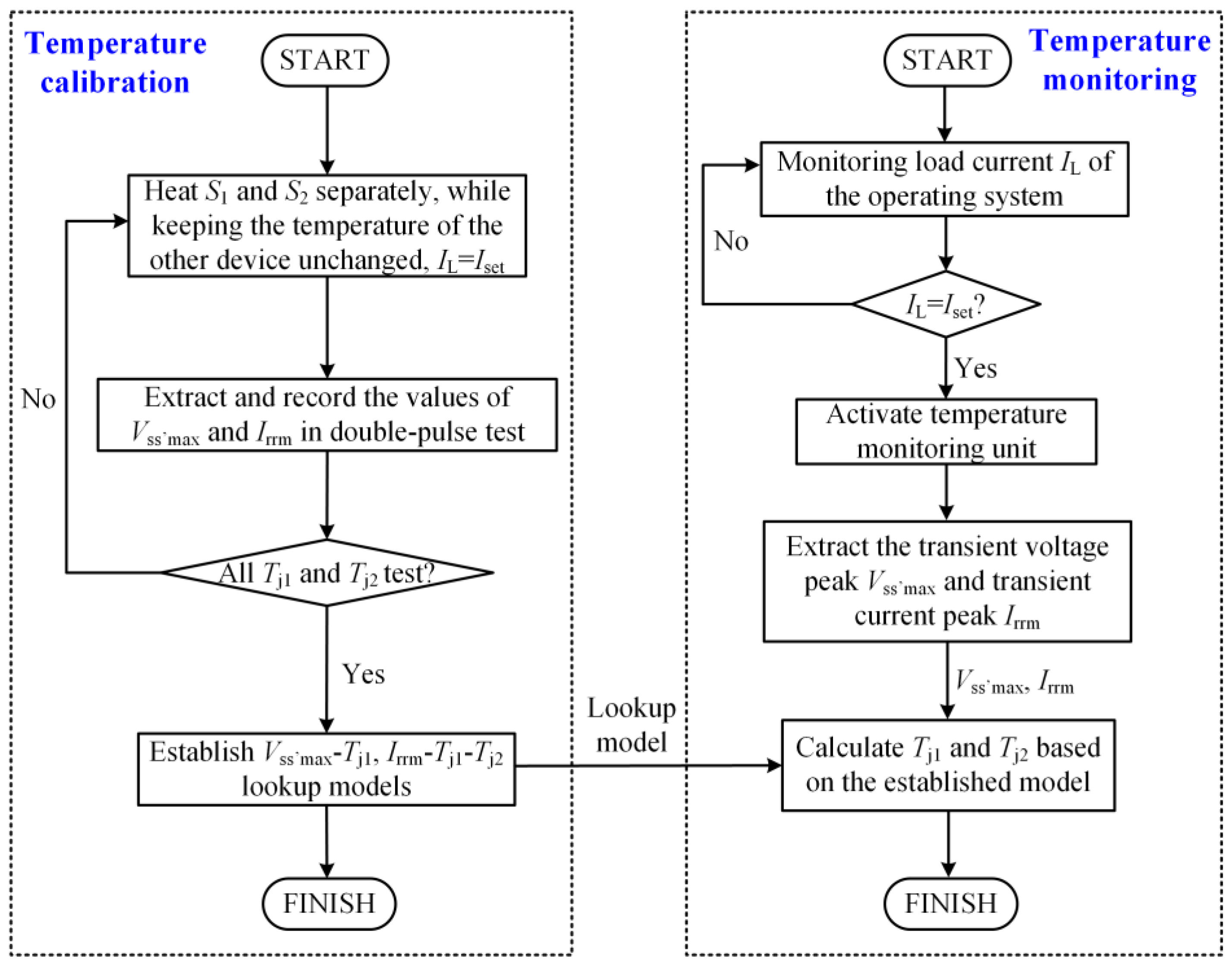

4. Temperature Verification and Online Measurement Discussion

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- She, X.; Huang, A.Q.; Lucia, O.; Ozpineci, B. Review of Silicon Carbide Power Devices and Their Applications. IEEE Trans. Ind. Electron. 2017, 64, 8193–8205. [Google Scholar] [CrossRef]

- Wang, H.; Liserre, M.; Blaabjerg, F. Toward Reliable Power Electronics: Challenges, Design Tools, and Opportunities. IEEE Ind. Electron. Mag. 2013, 7, 17–26. [Google Scholar] [CrossRef]

- Biela, J.; Schweizer, M.; Waffler, S.; Kolar, J.W. SiC versus Si—Evaluation of Potentials for Performance Improvement of Inverter and DC–DC Converter Systems by SiC Power Semiconductors. IEEE Trans. Ind. Electron. 2011, 58, 2872–2882. [Google Scholar] [CrossRef]

- Millan, J.; Godignon, P.; Perpina, X.; Perez-Tomas, A.; Rebollo, J. A Survey of Wide Bandgap Power Semiconductor Devices. IEEE Trans. Power Electron. 2014, 29, 2155–2163. [Google Scholar] [CrossRef]

- Górecki, K.; Posobkiewicz, K. Selected Problems of Power MOSFETs Thermal Parameters Measurements. Energies 2021, 14, 8353. [Google Scholar] [CrossRef]

- Bahman, A.S.; Ma, K.; Blaabjerg, F. A Lumped Thermal Model Including Thermal Coupling and Thermal Boundary Conditions for High-Power IGBT Modules. IEEE Trans. Power Electron. 2018, 33, 2518–2530. [Google Scholar] [CrossRef]

- Riccio, M.; Alessandro, V.D.; Romano, G.; Maresca, L.; Breglio, G.; Irace, A. A Temperature-Dependent SPICE Model of SiC Power MOSFETs for Within and Out-of-SOA Simulations. IEEE Trans. Power Electron. 2018, 33, 8020–8029. [Google Scholar] [CrossRef]

- Dupont, L.; Avenas, Y.; Jeannin, P.-O. Comparison of Junction Temperature Evaluations in a Power IGBT Module Using an IR Camera and Three Thermosensitive Electrical Parameters. IEEE Trans. Ind. Appl. 2013, 49, 1599–1608. [Google Scholar] [CrossRef]

- Baker, N.; Dupont, L.; Munk-Nielsen, S.; Iannuzzo, F.; Liserre, M. IR Camera Validation of IGBT Junction Temperature Measurement via Peak Gate Current. IEEE Trans. Power Electron. 2017, 32, 3099–3111. [Google Scholar] [CrossRef]

- Ni, Z.; Zheng, S.; Chinthavali, M.S.; Cao, D. Investigation of Dynamic Temperature-Sensitive Electrical Parameters for Medium-Voltage SiC and Si Devices. IEEE J. Emerg. Sel. Top. Power Electron. 2021, 9, 6408–6423. [Google Scholar] [CrossRef]

- Gelagaev, R.; Jacqmaer, P.; Driesen, J. A Fast Voltage Clamp Circuit for the Accurate Measurement of the Dynamic ON-Resistance of Power Transistors. IEEE Trans. Ind. Electron. 2015, 62, 1241–1250. [Google Scholar] [CrossRef]

- Griffo, A.; Wang, J.; Colombage, K.; Kamel, T. Real-Time Measurement of Temperature Sensitive Electrical Parameters in SiC Power MOSFETs. IEEE Trans. Ind. Electron. 2018, 65, 2663–2671. [Google Scholar] [CrossRef]

- Hoffmann, F.; Soler, V.; Mihaila, A.; Kaminski, N. Power cycling test on 3.3 kV SiC MOSFETs and the effects of bipolar degradation on the temperature estimation by VSD-method. In Proceedings of the 31st International Symposium on Power Semiconductor Devices and ICs (ISPSD), Shanghai, China, 19–23 May 2019; pp. 147–150. [Google Scholar] [CrossRef]

- Jiang, X.; Wang, J.; Yu, H.; Chen, J.; Zeng, Z.; Yang, X.; Shen, Z.J. Online Junction Temperature Measurement for SiC MOSFET Based on Dynamic Threshold Voltage Extraction. IEEE Trans. Power Electron. 2021, 36, 3757–3768. [Google Scholar] [CrossRef]

- Zhang, Z.; Dyer, J.; Wu, X.; Wang, F.; Costinett, D.; Tolbert, L.M.; Blalock, B.J. Online Junction Temperature Monitoring Using Intelligent Gate Drive for SiC Power Devices. IEEE Trans. Power Electron. 2019, 34, 7922–7932. [Google Scholar] [CrossRef]

- Yang, F.; Pu, S.; Xu, C.; Akin, B. Turn-on Delay Based Real-Time Junction Temperature Measurement for SiC MOSFETs with Aging Compensation. IEEE Trans. Power Electron. 2021, 36, 1280–1294. [Google Scholar] [CrossRef]

- Baker, N.; Munk-Nielsen, S.; Iannuzzo, F.; Liserre, M. Online junction temperature measurement using peak gate current. In Proceedings of the IEEE Applied Power Electronics Conference and Exposition (APEC), Charlotte, NC, USA, 15–19 March 2015; pp. 1270–1275. [Google Scholar] [CrossRef]

- Yang, Y.; Wu, Y.; Ding, X.; Zhang, P. Online Junction Temperature Estimation Method for SiC MOSFETs Based on the DC Bus Voltage Undershoot. IEEE Trans. Power Electron. 2023, 38, 5422–5431. [Google Scholar] [CrossRef]

- Luo, H.; Li, W.; He, X. Online High-Power P-i-N Diode Chip Temperature Extraction and Prediction Method with Maximum Recovery Current di/dt. IEEE Trans. Power Electron. 2015, 30, 2395–2404. [Google Scholar] [CrossRef]

- Peng, Y.; Shen, Y.; Wang, H. A Converter-Level on-State Voltage Measurement Method for Power Semiconductor Devices. IEEE Trans. Power Electron. 2021, 36, 1220–1224. [Google Scholar] [CrossRef]

- Baliga, B.J. Fundamentals of Power Semiconductor Devices; Spring: New York, NY, USA, 2008. [Google Scholar]

- Gonzalez, J.O.; Alatise, O.; Hu, J.; Ran, L.; Mawby, P.A. An Investigation of Temperature-Sensitive Electrical Parameters for SiC Power MOSFETs. IEEE Trans. Power Electron. 2017, 32, 7954–7966. [Google Scholar] [CrossRef]

- Zhang, Z.; Guo, B.; Wang, F.F.; Jones, E.A.; Tolbert, L.M.; Blalock, B.J. Methodology for Wide Band-Gap Device Dynamic Characterization. IEEE Trans. Power Electron. 2017, 32, 9307–9318. [Google Scholar] [CrossRef]

- Liang, M.; Li, Y.; Zheng, T.Q. Research on precise test method for switching performance of high speed SiC MOSFET. In Proceedings of the Asian Conference on Energy, Power and Transportation Electrification (ACEPT), Singapore, 25–27 October 2016; pp. 1–6. [Google Scholar] [CrossRef]

- Nguyen, T.K.; Mocevic, S.; Sun, K.; Burgos, R. Switching Current Measurement Based on Power Module Parasitics. In Proceedings of the IEEE 12th Energy Conversion Congress & Exposition—Asia (ECCE-Asia), Singapore, 24–27 May 2021; pp. 1903–1908. [Google Scholar] [CrossRef]

- Liu, T.; Wong, T.T.Y.; Shen, Z.J. A New Characterization Technique for Extracting Parasitic Inductances of SiC Power MOSFETs in Discrete and Module Packages Based on Two-Port S-Parameters Measurement. IEEE Trans. Power Electron. 2018, 33, 9819–9833. [Google Scholar] [CrossRef]

- Hu, S.; Wang, M.; Liang, Z.; He, X. A Frequency-Based Stray Parameter Extraction Method Based on Oscillation in SiC MOSFET Dynamics. IEEE Trans. Power Electron. 2021, 36, 6153–6157. [Google Scholar] [CrossRef]

- Yang, F.; Ugur, E.; Akin, B. Evaluation of Aging’s Effect on Temperature-Sensitive Electrical Parameters in SiC mosfets. IEEE Trans. Power Electron. 2020, 35, 6315–6331. [Google Scholar] [CrossRef]

- Gonzalez, J.O.; Alatise, O. Impact of the Gate Oxide Reliability of SiC MOSFETs on the Junction Temperature Estimation Using Temperature Sensitive Electrical Parameters. In Proceedings of the IEEE Energy Conversion Congress and Exposition (ECCE), Portland, OR, USA, 23–27 September 2018; pp. 837–844. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wu, S.; Sun, P.; Huang, X.; Li, K. A Bridge-Level Junction Temperature Estimation Method for SiC MOSFETs Combining Transient Voltage and Current Peaks. Energies 2023, 16, 4105. https://doi.org/10.3390/en16104105

Wu S, Sun P, Huang X, Li K. A Bridge-Level Junction Temperature Estimation Method for SiC MOSFETs Combining Transient Voltage and Current Peaks. Energies. 2023; 16(10):4105. https://doi.org/10.3390/en16104105

Chicago/Turabian StyleWu, Shuo, Pengju Sun, Xu Huang, and Kaiwei Li. 2023. "A Bridge-Level Junction Temperature Estimation Method for SiC MOSFETs Combining Transient Voltage and Current Peaks" Energies 16, no. 10: 4105. https://doi.org/10.3390/en16104105

APA StyleWu, S., Sun, P., Huang, X., & Li, K. (2023). A Bridge-Level Junction Temperature Estimation Method for SiC MOSFETs Combining Transient Voltage and Current Peaks. Energies, 16(10), 4105. https://doi.org/10.3390/en16104105