Modeling, Simulation and Development of Grid-Connected Voltage Source Converter with Selective Harmonic Mitigation: HiL and Experimental Validations

Abstract

:1. Introduction

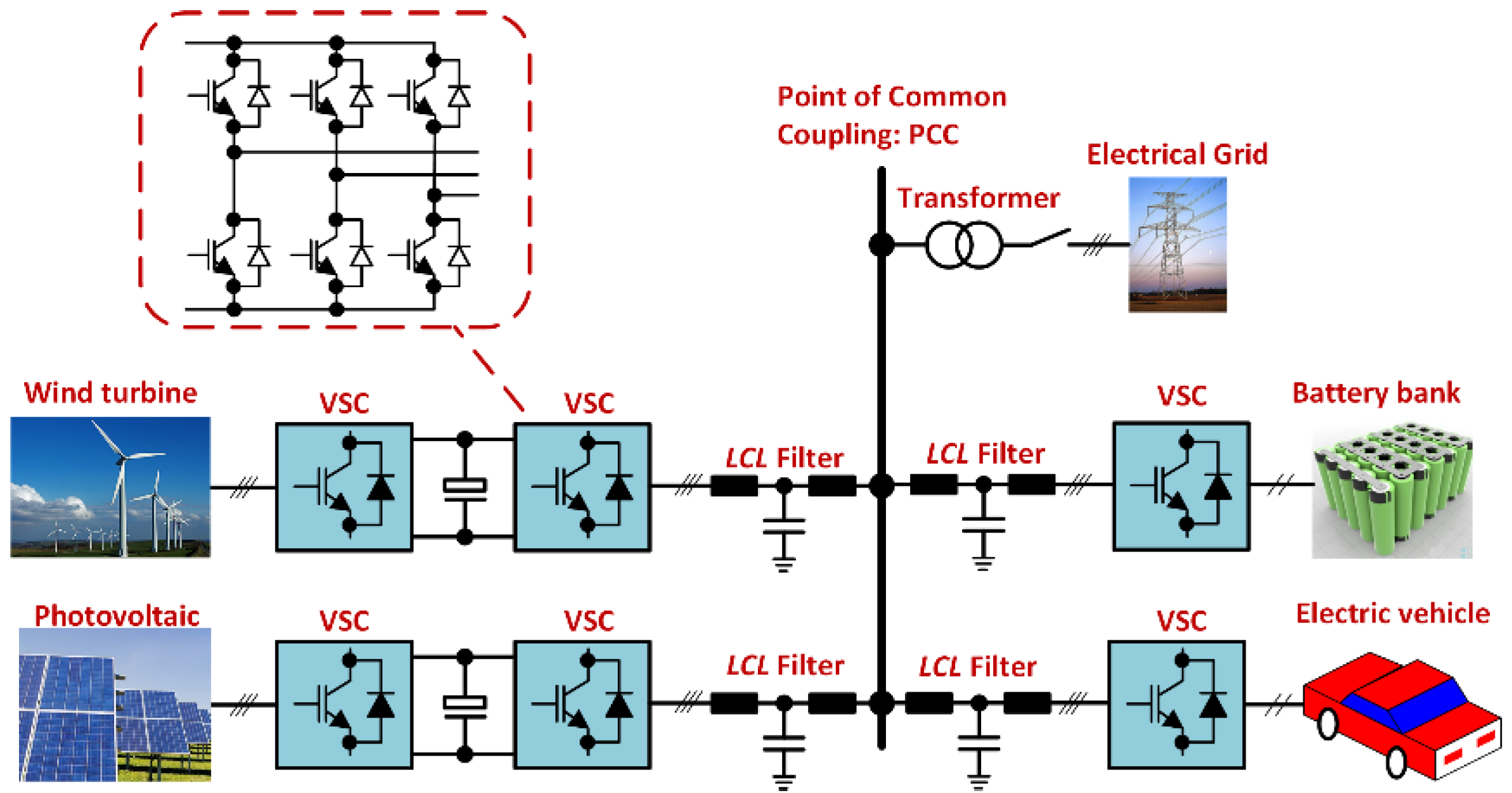

2. System Description

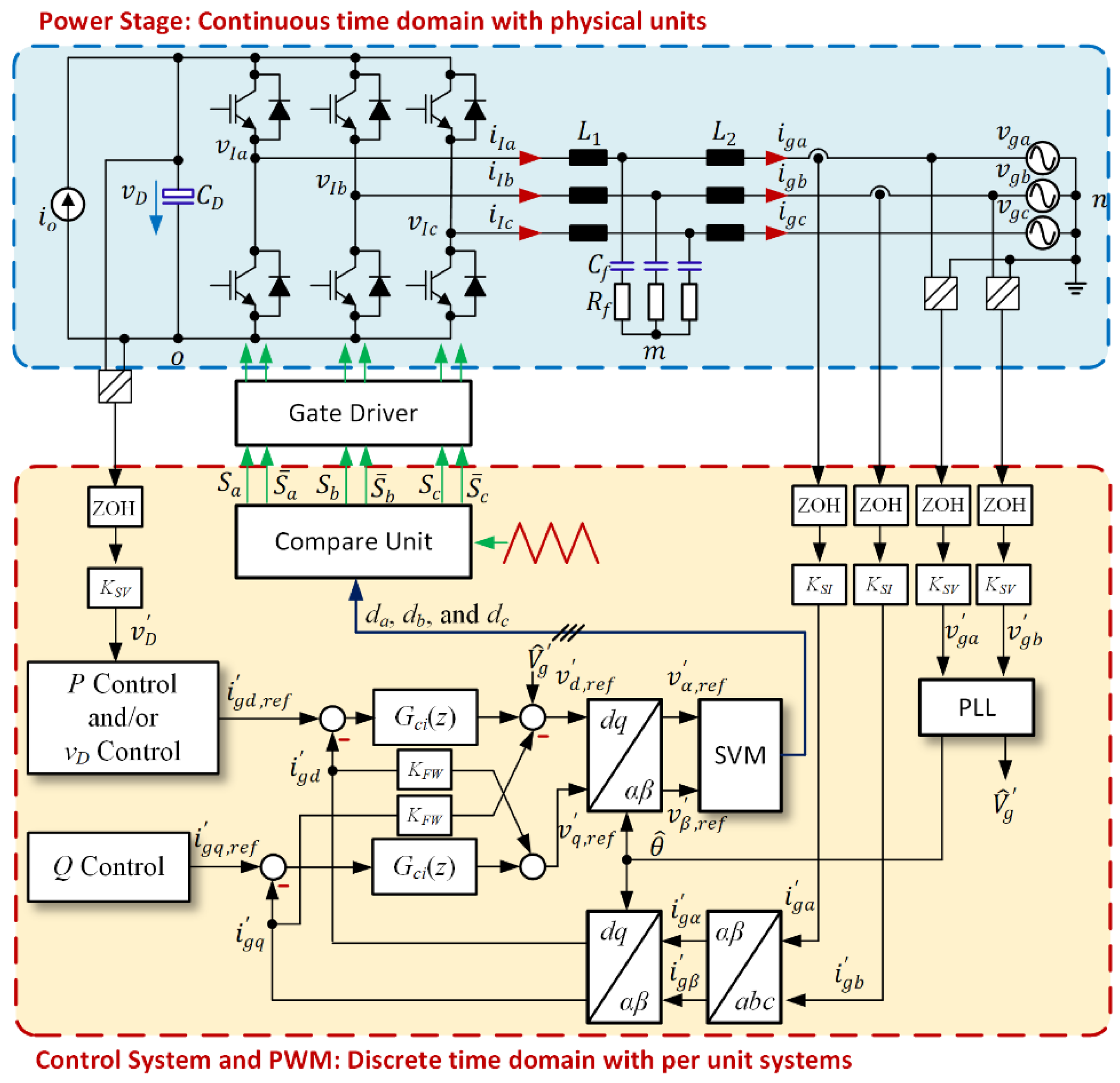

3. Modeling of the LCL-Filtered VSC

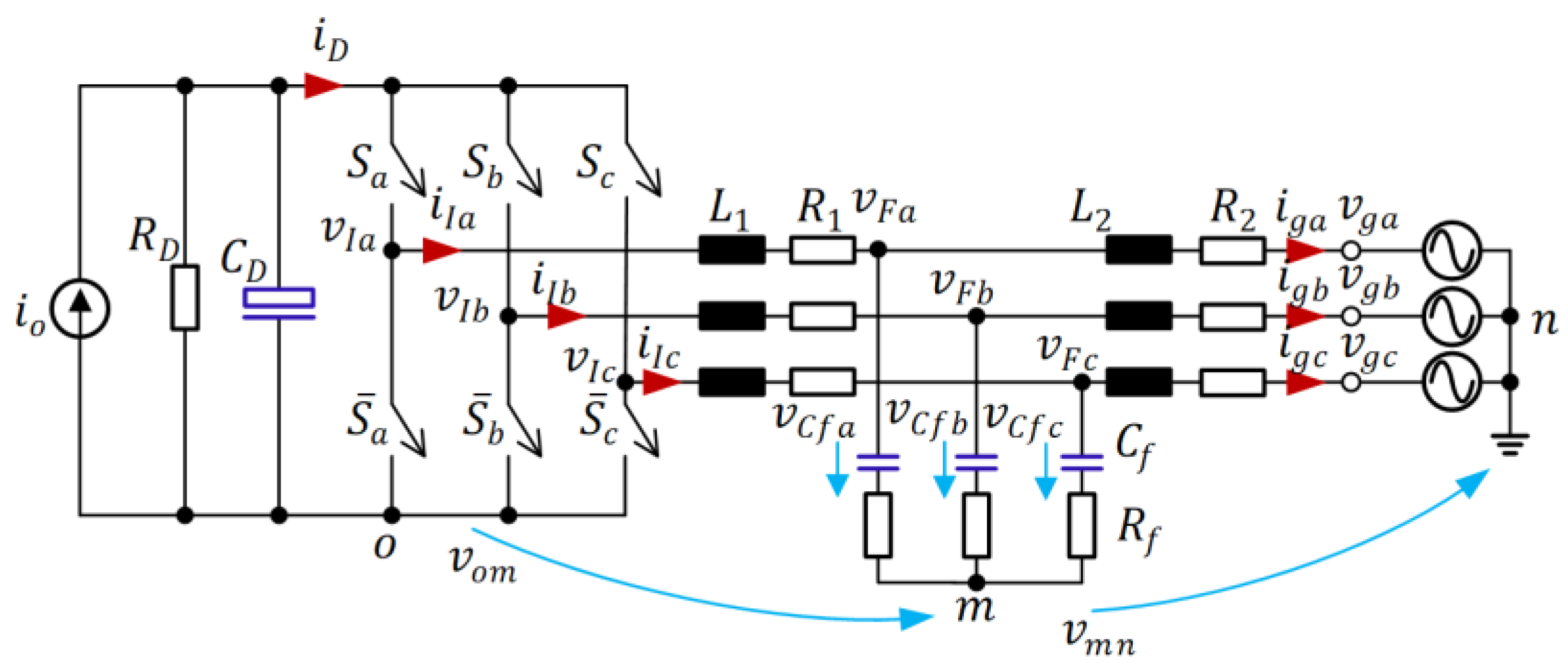

3.1. Switched Circuit Modeling of the Power Circuit

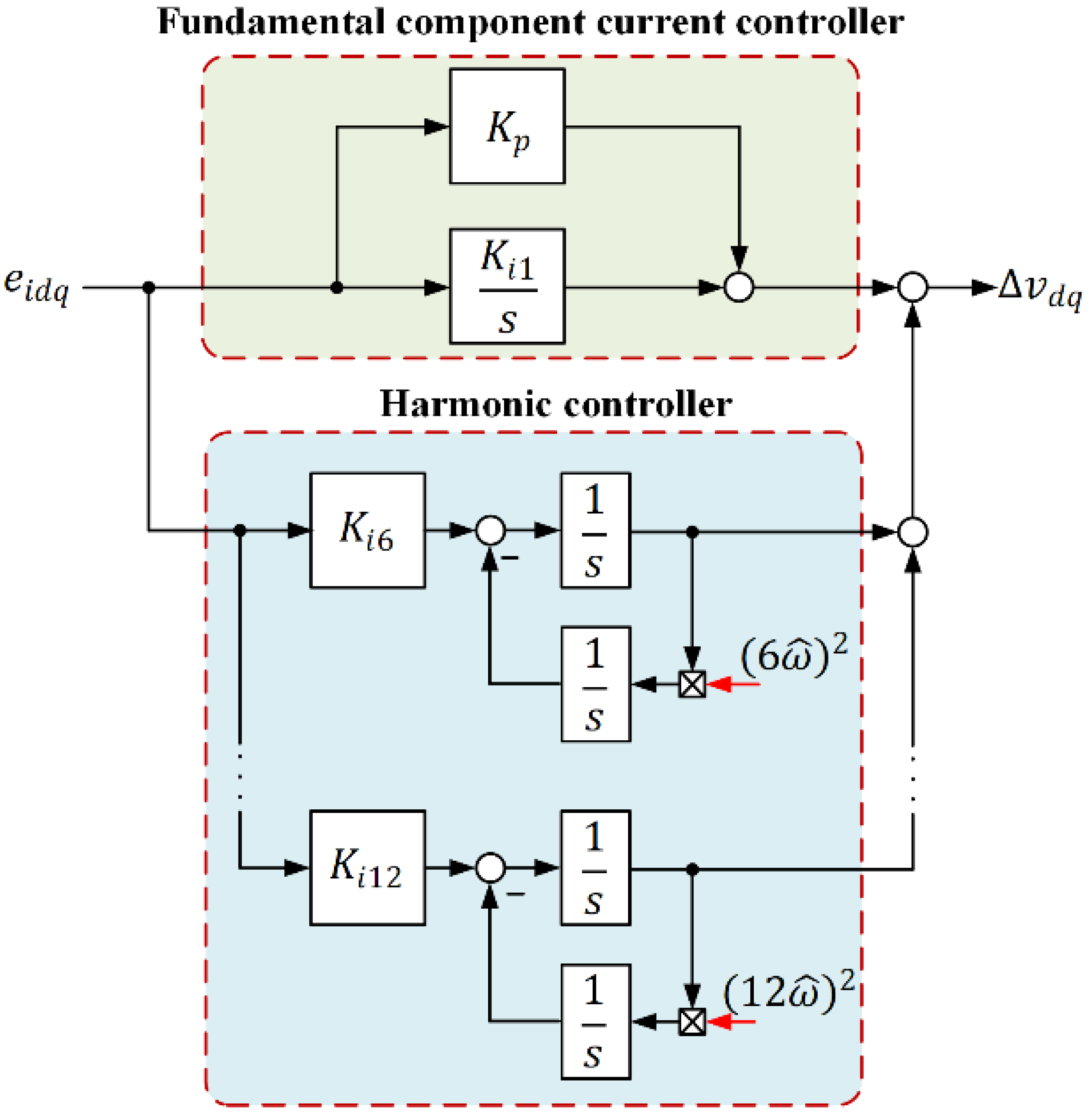

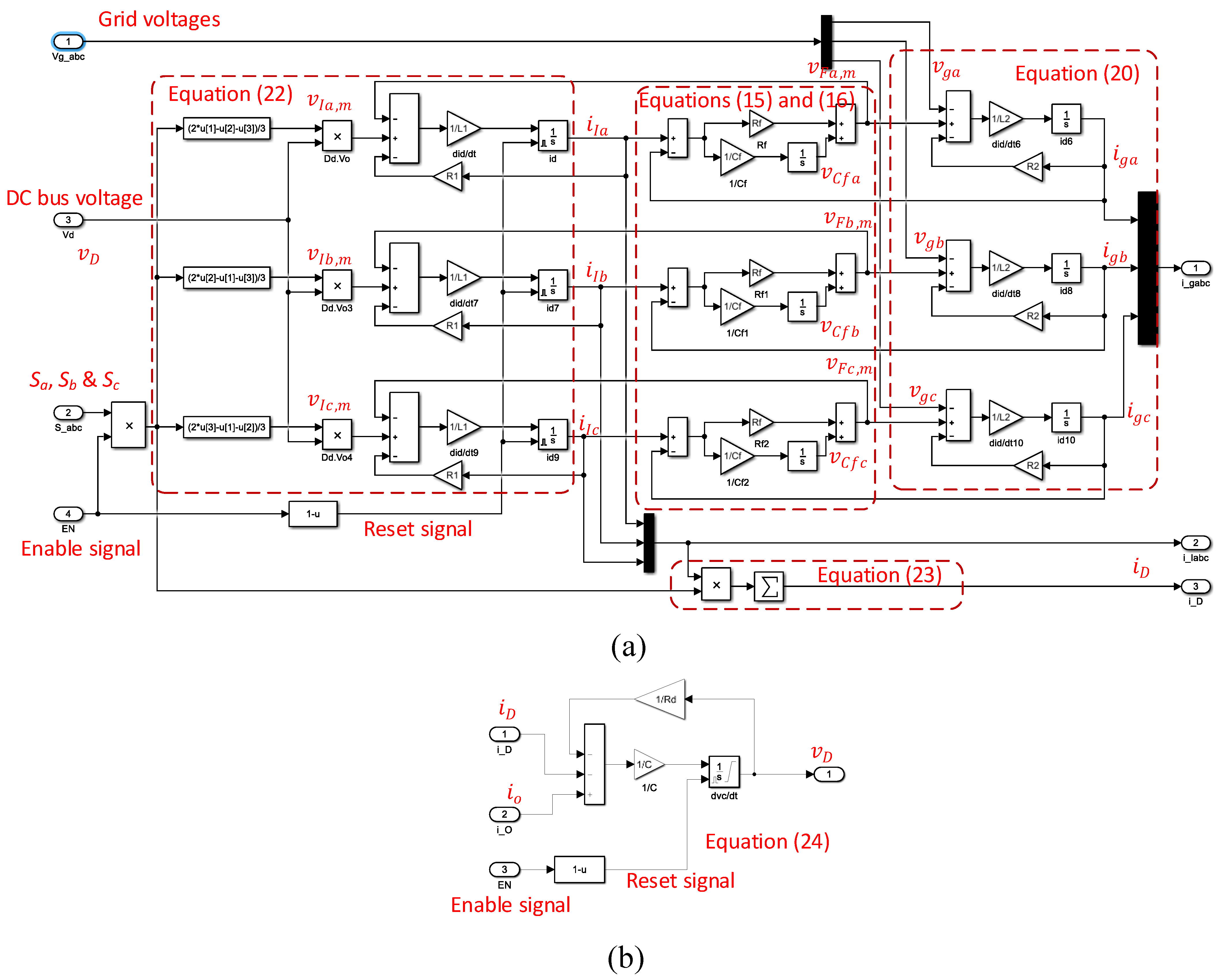

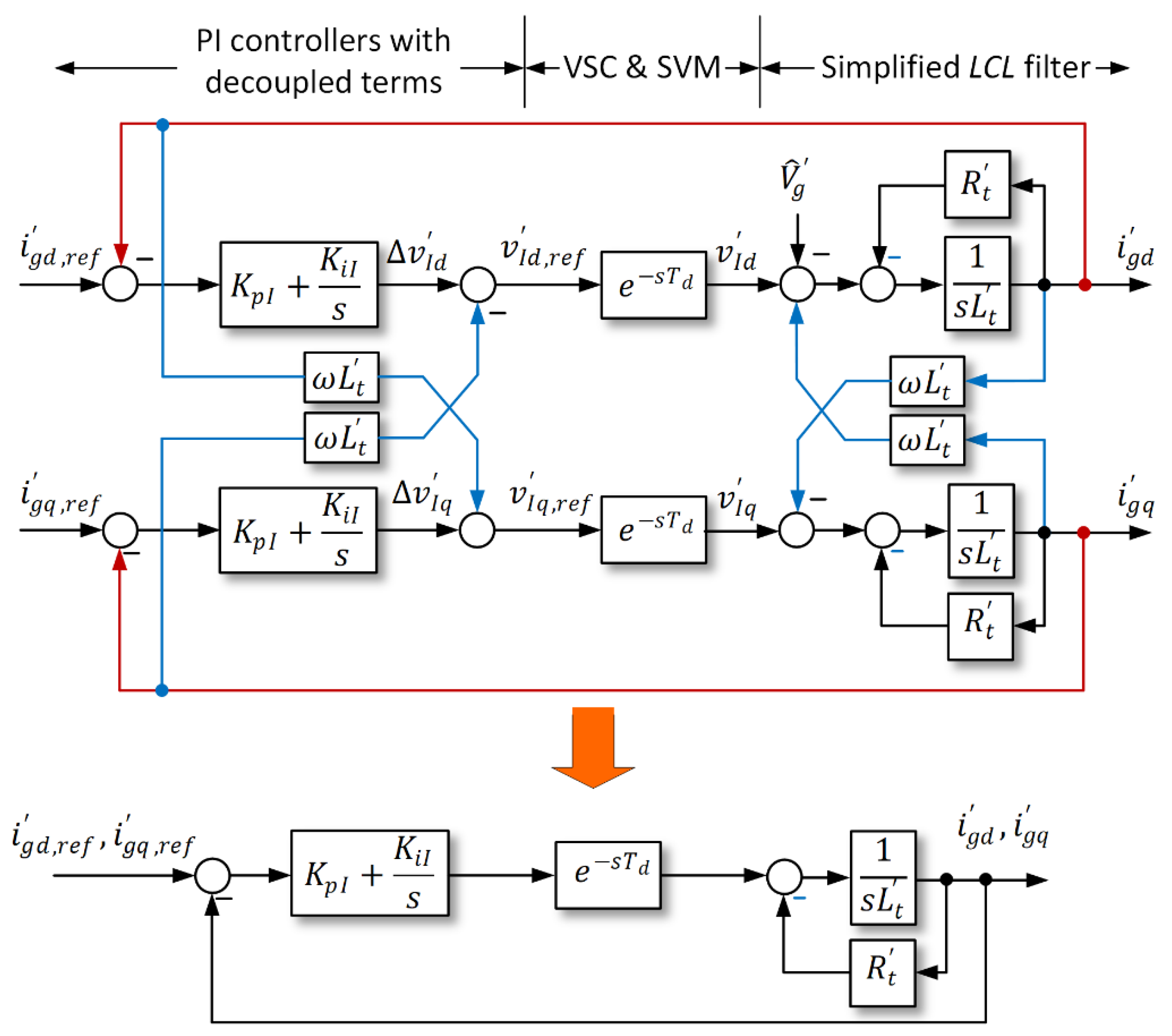

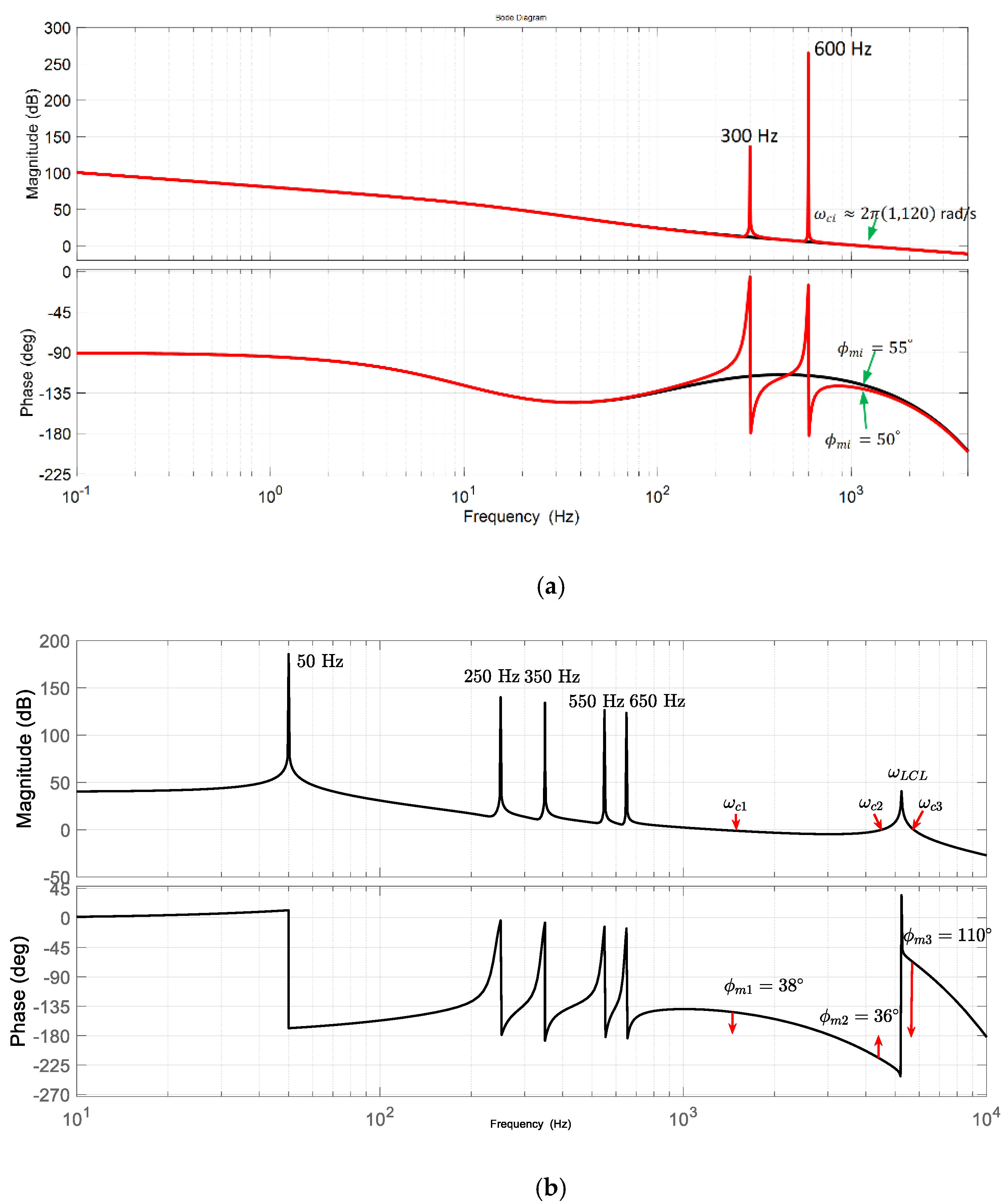

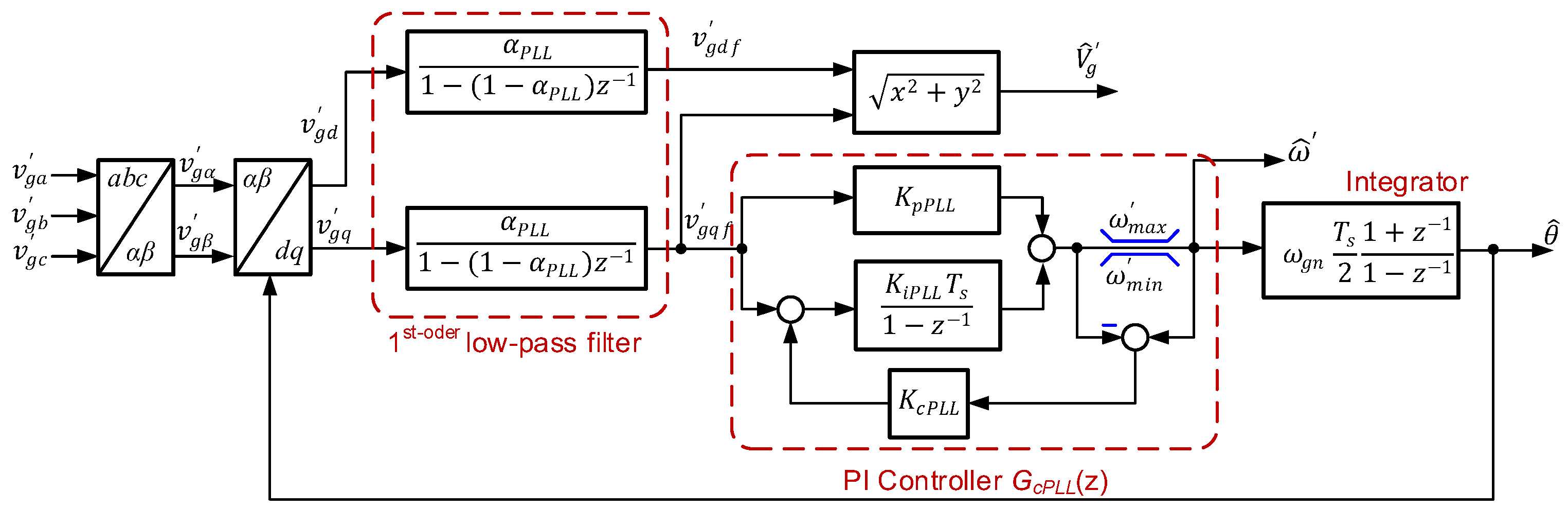

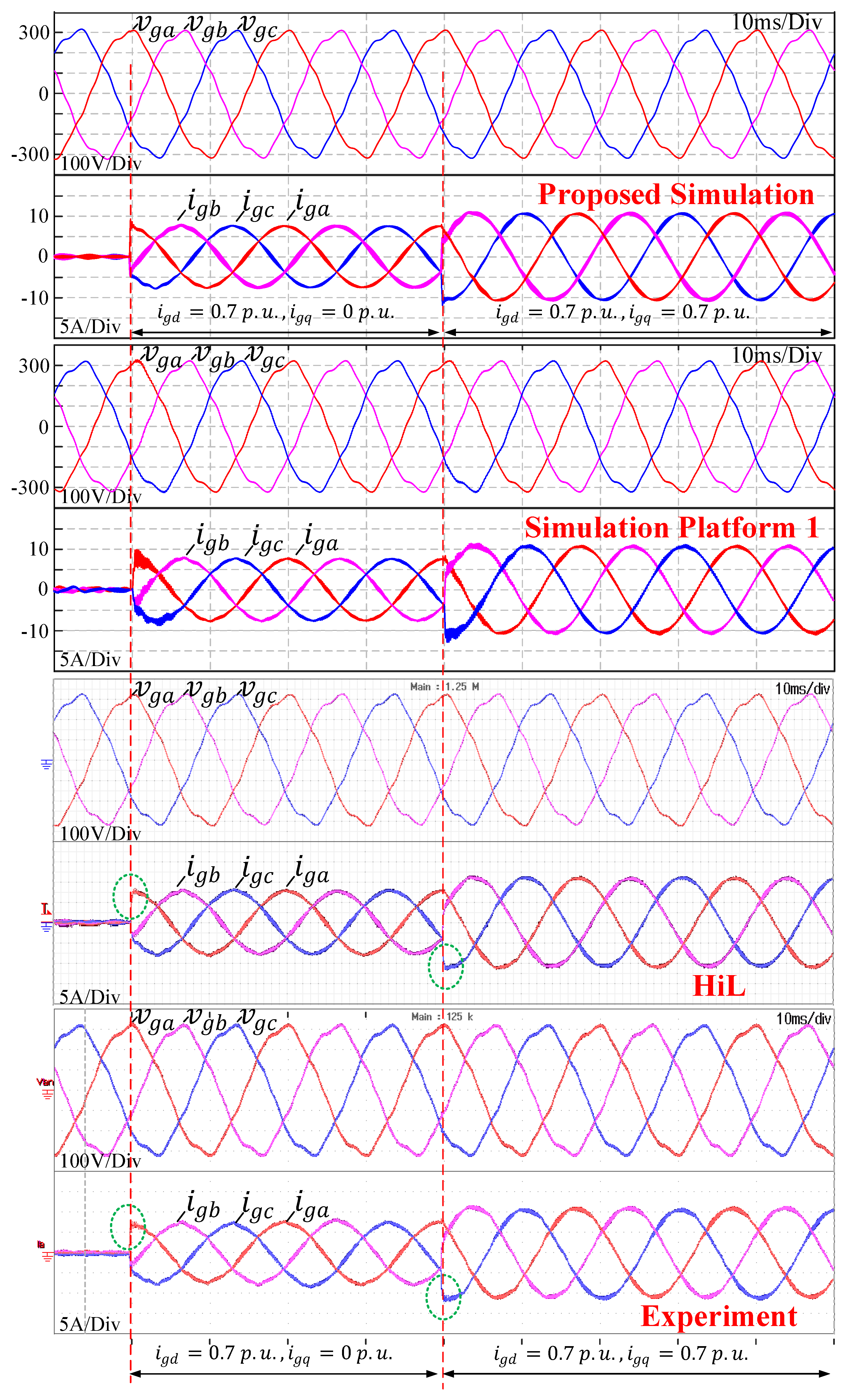

3.2. Averaged Circuit Modeling and Current Controller Design

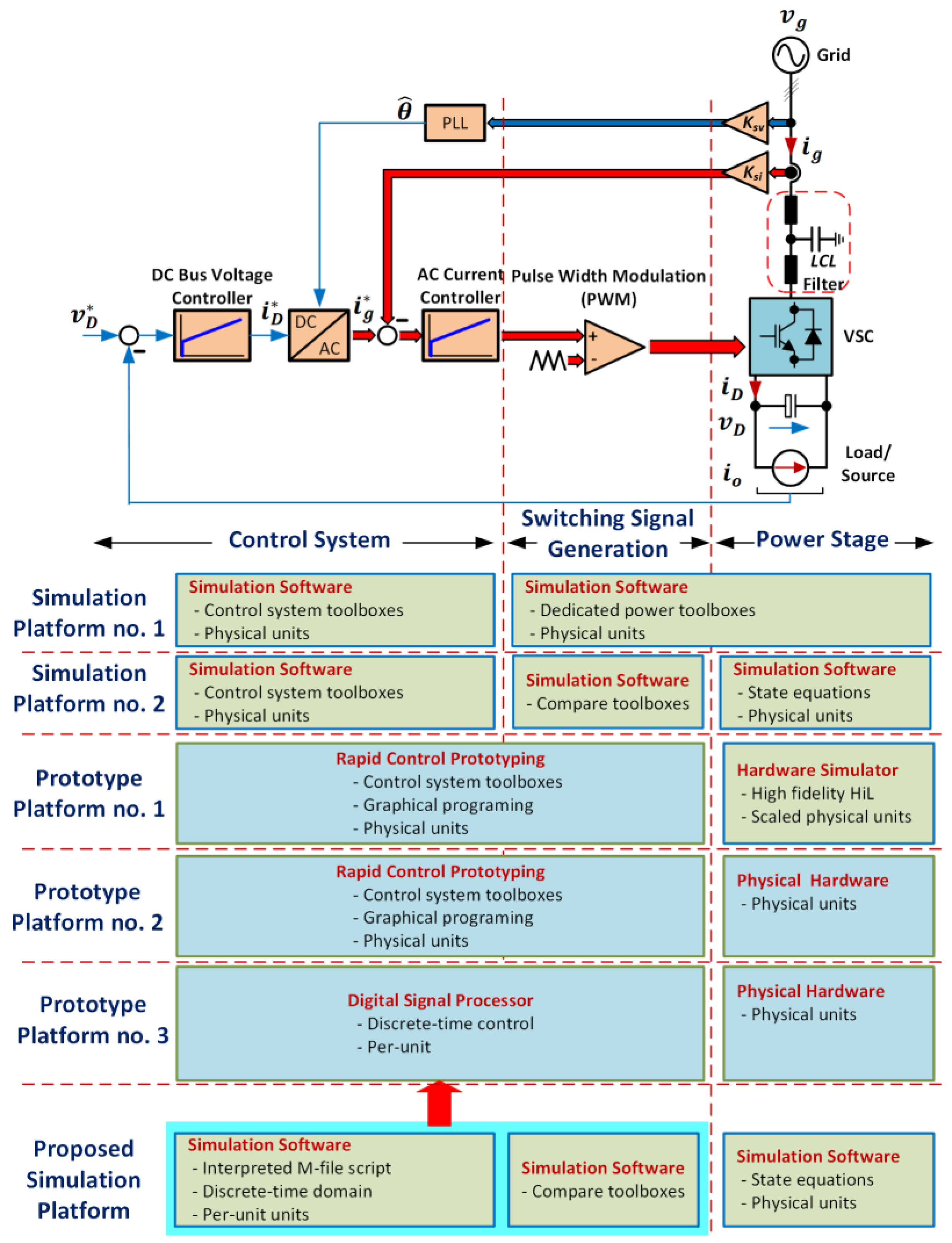

4. Simulation

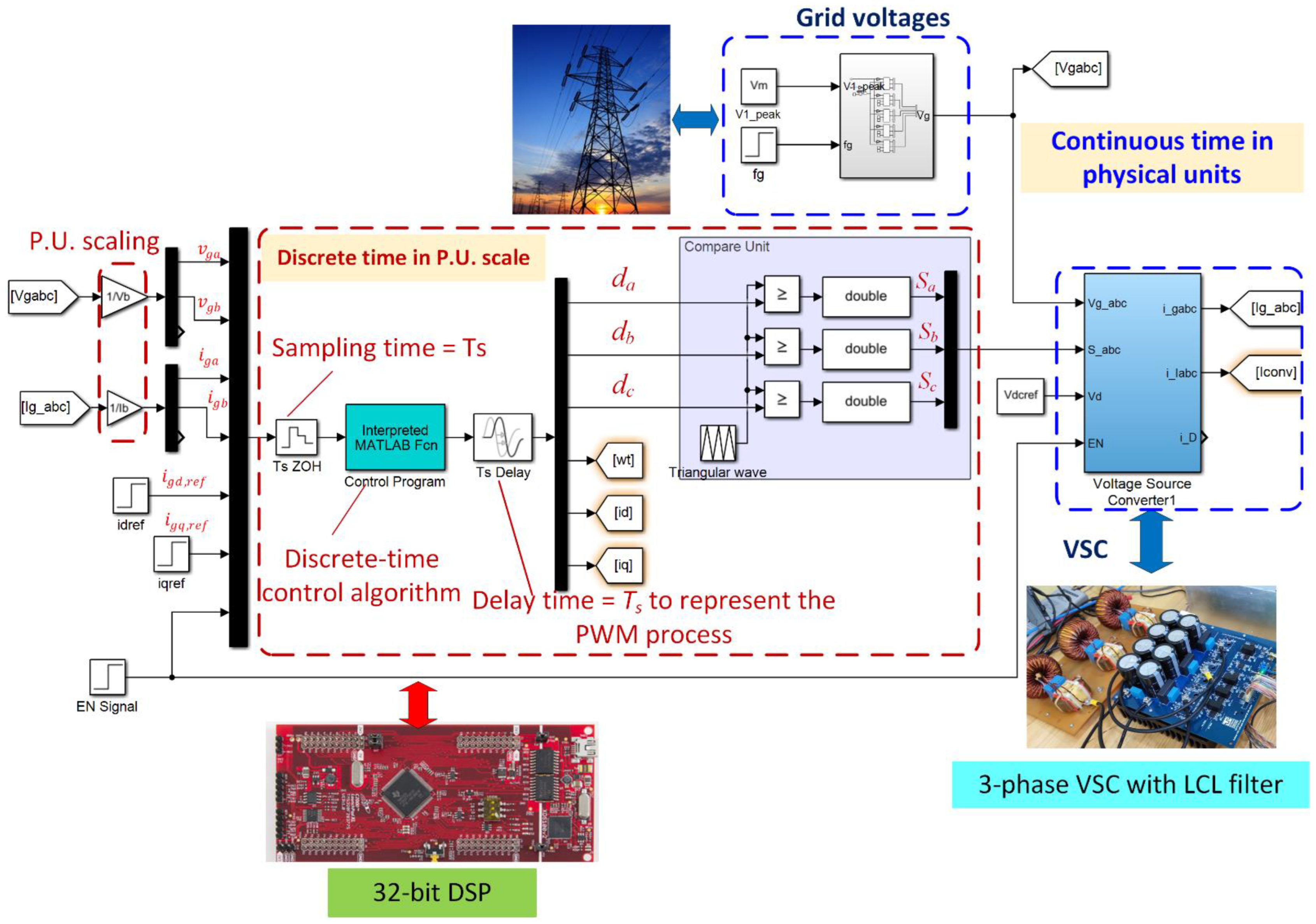

4.1. Simulation Structure

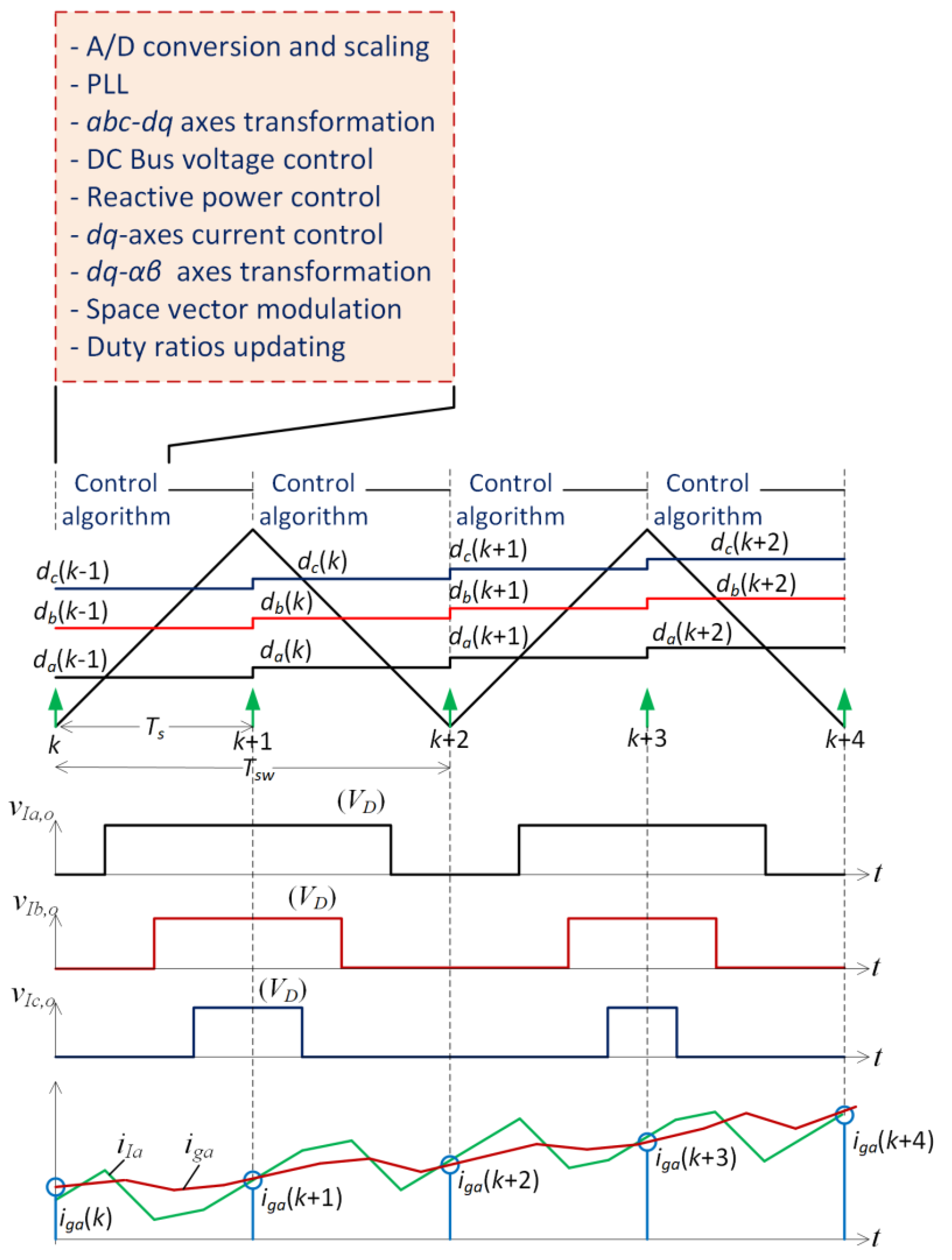

4.2. Discrete-Time Control Scheme

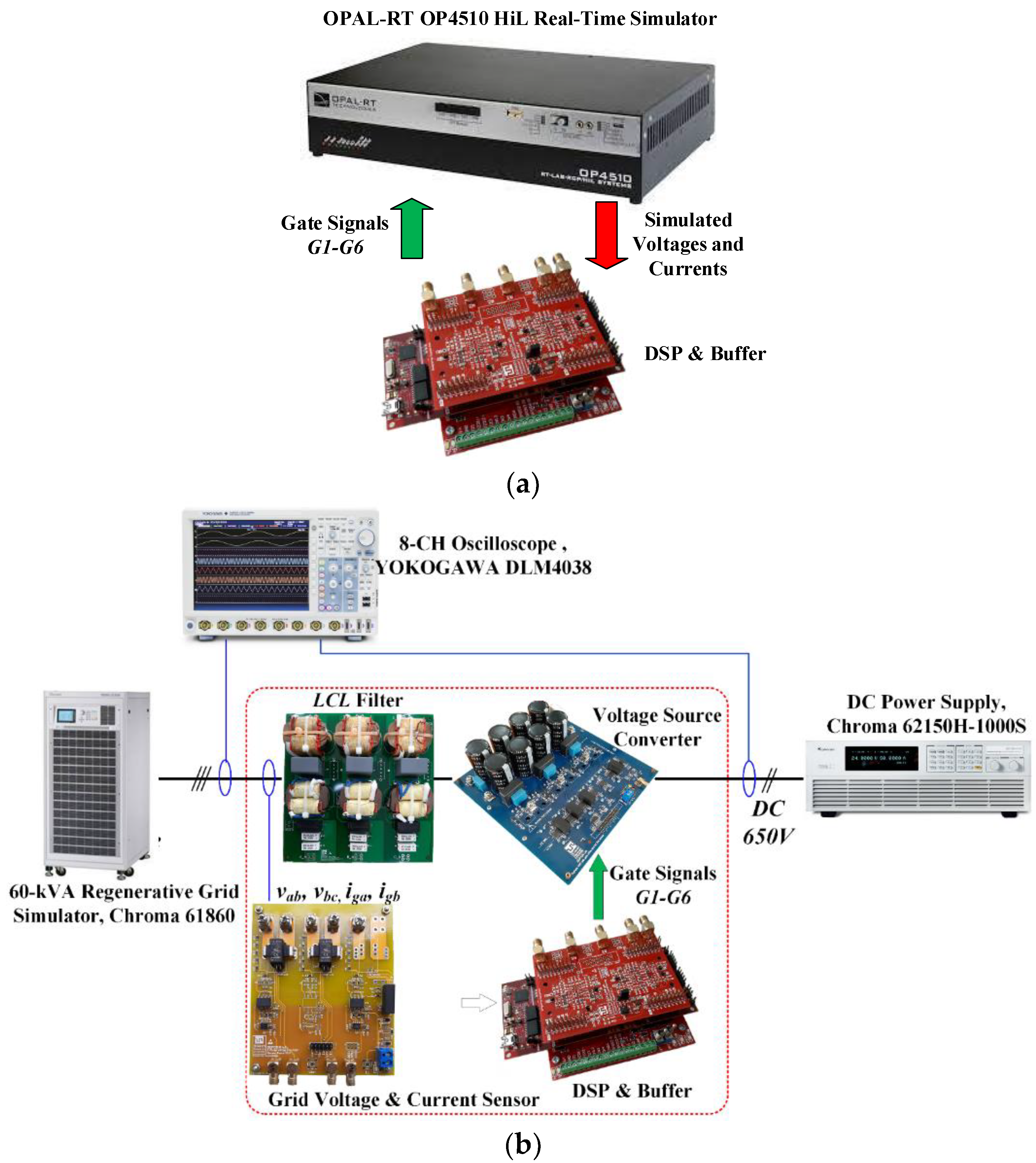

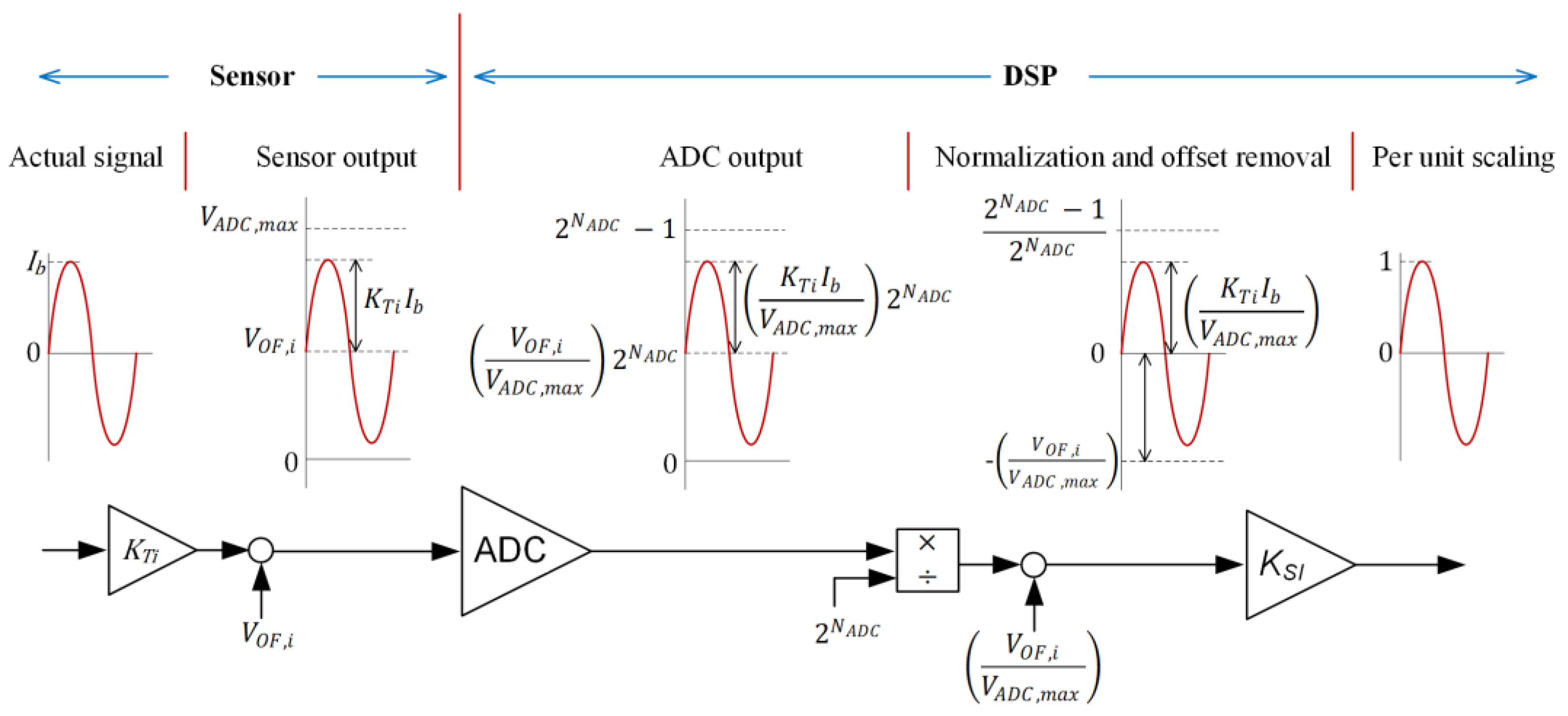

5. Implementations

6. Simulation and Experimental Validations

7. Conclusions

- Switched-circuit modeling of the power circuit is simulated in the continuous-time domain with the physical unit scale.

- The discrete-time control scheme in the per-unit scale is written in a MATLAB m file function which is executed in synchronous with the switching period.

- The m-file script is then easily translated to the C code for the TMS320F28379D DSP with the same controller parameters.

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

Nomenclature

| ADC | Analog-to-digital converter |

| DAC | Digital-to-analog converter |

| DSP | Digital signal processor |

| FPGA | Field-programmable gate array |

| HC | Harmonic controller |

| HiL | Hardware in the loop |

| IGBT | Insulated-gate bipolar transistor |

| ISR | Interrupt service routine |

| MR | Multiple resonant |

| PI | Proportional-integral |

| PIMR | Proportional-integral plus multi-resonant |

| PLL | Phase-locked loop |

| PWM | Pulse width modulation |

| RCP | Rapid control prototyping |

| SO | Symmetrical optimum |

| SVM | Space vector modulation |

| VSC | Voltage source converter |

| ZOH | Zero-order hold |

| µC | Microcontroller |

| , and | Duty ratios |

| Sampling frequency | |

| Switching frequency | |

| Resonant frequency of the LCL filter | |

| VSC DC current | |

| , , and | Grid currents |

| , , and | VSC currents |

| DC bus current | |

| , , and | VSC switching signals |

| PWM delay time | |

| Sampling period | |

| Switching period | |

| DC bus voltage | |

| , and | LCL filter voltages |

| , and | Grid voltages |

| , and | VSC terminal voltages |

| Angle of the grid voltage | |

| Phase margin | |

| Grid angular frequency | |

| Cross-over frequency | |

| Nominal grid angular frequency | |

| Subscripts | |

| and | Signals in the synchronous reference frame |

| Refence signals | |

| and | Signals in the stationary reference frame |

| Superscripts | |

| Signals in the per unit scale | |

| Symbols | |

| Peak value or estimated value | |

| averaged variables over |

References

- Huang, Z.; Krishnaswami, H.; Yuan, G.; Huang, R. Ubiquitous Power Electronics in Future Power Systems: Recommendations to Fully Utilize Fast Control Capabilities. IEEE Electrif. Mag. 2020, 8, 18–27. [Google Scholar] [CrossRef]

- Chen, M.; Poor, H.V. High-Frequency Power Electronics at the Grid Edge: A Bottom-Up Approach Toward the Smart Grid. IEEE Electrif. Mag. 2020, 8, 6–17. [Google Scholar] [CrossRef]

- Patel, N.; Kumar, A.; Gupta, N.; Ray, S.; Babu, B.C. Optimised PI-4VPI current controller for three-phase grid-integrated photovoltaic inverter under grid voltage distortions. IET Renew. Power Gener. 2020, 14, 779–792. [Google Scholar] [CrossRef]

- Jahanpour-Dehkordi, M.; Vaez-Zadeh, S.; Mohammadi, J. Development of a Combined Control System to Improve the Performance of a PMSG-Based Wind Energy Conversion System Under Normal and Grid Fault Conditions. IEEE Trans. Energy Convers. 2019, 34, 1287–1295. [Google Scholar] [CrossRef]

- Peña Asensio, A.; Gonzalez-Longatt, F.; Arnaltes, S.; Rodríguez-Amenedo, J.L. Analysis of the Converter Synchronizing Method for the Contribution of Battery Energy Storage Systems to Inertia Emulation. Energies 2020, 13, 1478. [Google Scholar] [CrossRef] [Green Version]

- Grasso, E.; Palmieri, M.; Mandriota, R.; Cupertino, F.; Nienhaus, M.; Kleen, S. Analysis and Application of the Direct Flux Control Sensorless Technique to Low-Power PMSMs. Energies 2020, 13, 1453. [Google Scholar] [CrossRef] [Green Version]

- Sun, Q.; Lv, H.; Gao, S.; Wei, K.; Mauersberger, M. Optimized Control of Reversible VSC with Stability Mechanism Study in SMES Based V2G System. IEEE Appl. Supercond. 2019, 29, 1–6. [Google Scholar] [CrossRef]

- Maksimovic, D.; Stankovic, A.M.; Thottuvelil, V.J.; Verghese, G.C. Modeling and simulation of power electronic converters. Proc. IEEE 2001, 89, 898–912. [Google Scholar] [CrossRef]

- Chakraborty, S.; Mazuela, M.; Tran, D.; Corea-Araujo, J.A.; Lan, Y.; Loiti, A.A.; Garmier, P.; Aizpuru, I.; Hegazy, O. Scalable Modeling Approach and Robust Hardware-in-the-Loop Testing of an Optimized Interleaved Bidirectional HV DC/DC Converter for Electric Vehicle Drivetrains. IEEE Access 2020, 8, 115515–115536. [Google Scholar] [CrossRef]

- Adib, A.; Mirafzal, B.; Wang, X.; Blaabjerg, F. On Stability of Voltage Source Inverters in Weak Grids. IEEE Access 2018, 6, 4427–4439. [Google Scholar] [CrossRef]

- Xin, Z.; Wang, X.; Loh, P.C.; Blaabjerg, F. Grid-Current-Feedback Control for LCL-Filtered Grid Converters With Enhanced Stability. IEEE Trans. Power Electron. 2017, 32, 3216–3228. [Google Scholar] [CrossRef]

- Almaguer, J.; Cárdenas, V.; Espinoza, J.; Aganza-Torres, A.; González, M. Performance and Control Strategy of Real-Time Simulation of a Three-Phase Solid-State Transformer. Appl. Sci. 2019, 9, 789. [Google Scholar] [CrossRef] [Green Version]

- Chauhan, S.; Singh, B. Control of solar PV-integrated battery energy storage system for rural area application. IET Renew. Power Gener. 2021, 15, 1030–1045. [Google Scholar] [CrossRef]

- Taul, M.G.; Wu, C.; Chou, S.F.; Blaabjerg, F. Optimal Controller Design for Transient Stability Enhancement of Grid-Following Converters Under Weak-Grid Conditions. IEEE Trans. Power Electron. 2021, 36, 10251–10264. [Google Scholar] [CrossRef]

- Sener, E.; Ertasgin, G. Current-source 1-Ph inverter design for aircraft applications. Aircr. Eng. Aerosp. Technol. 2020, 92, 1295–1305. [Google Scholar] [CrossRef]

- Duran, M.F. Digital Control of a Renewable Energy Resource Interfacing the Distribution Grid. Master’s Thesis, Escola Tècnica Superior d’Enginyeria Industrial de Barcelona, Barcelona, Spain, 2018. [Google Scholar]

- Estrada, L.; Vázquez, N.; Vaquero, J.; De Castro, Á.; Arau, J. Real-Time Hardware in the Loop Simulation Methodology for Power Converters Using LabVIEW FPGA. Energies 2020, 13, 373. [Google Scholar] [CrossRef] [Green Version]

- Nigam, S.; Ajala, O.; Dominguez-Garcia, A.D. A Controller Hardware-in-the-Loop Testbed: Verification and Validation of Microgrid Control Architectures. IEEE Electrif. Mag. 2020, 8, 92–100. [Google Scholar] [CrossRef]

- Salgado-Herrera, N.M.; Campos-Gaona, D.; Anaya-Lara, O.; Medina-Rios, A.; Tapia-Sánchez, R.; Rodríguez-Rodríguez, J.R. THD Reduction in Wind Energy System Using Type-4 Wind Turbine/PMSG Applying the Active Front-End Converter Parallel Operation. Energies 2018, 11, 2458. [Google Scholar] [CrossRef] [Green Version]

- Zhu, D.; Zou, X.; Zhao, Y.; Peng, T.; Zhou, S.; Kang, Y. Systematic controller design for digitally controlled LCL-type grid-connected inverter with grid-current-feedback active damping. Int. J. Electr. Power Energy Syst. 2019, 110, 642–652. [Google Scholar] [CrossRef]

- Samanes, J.; Urtasun, A.; Gubia, E.; Petri, A. Robust multisampled capacitor voltage active damping for grid-connected power converters. Int. J. Electr. Power Energy Syst. 2019, 105, 741–752. [Google Scholar] [CrossRef]

- Said-Romdhane, M.B.; Naouar, M.W.; Belkhodja, I.S.; Monmasson, E. An Improved LCL Filter Design in Order to Ensure Stability without Damping and Despite Large Grid Impedance Variations. Energies 2017, 10, 336. [Google Scholar] [CrossRef] [Green Version]

- Rodriguez-Diaz, E.; Freijedo, F.D.; Vasquez, J.C.; Guerrero, J.M. Analysis and Comparison of Notch Filter and Capacitor Voltage Feedforward Active Damping Techniques for LCL Grid-Connected Converters. IEEE Trans. Power Electron. 2019, 34, 3958–3972. [Google Scholar] [CrossRef] [Green Version]

- Aravena, J.; Carrasco, D.; Diaz, M.; Uriarte, M.; Rojas, F.; Cardenas, R.; Travieso, J.C. Design and Implementation of a Low-Cost Real-Time Control Platform for Power Electronics Applications. Energies 2020, 13, 1527. [Google Scholar] [CrossRef] [Green Version]

- Liserre, M.; Teodorescu, R.; Blaabjerg, F. Multiple harmonics control for three-phase grid converter systems with the use of PI-RES current controller in a rotating frame. IEEE Trans. Power Electron. 2006, 21, 836–841. [Google Scholar] [CrossRef]

- Teodorescu, R.; Blaabjerg, F.; Liserre, M.; Loh, P.C. Proportional-resonant controllers and filters for grid-connected voltage-source converters. IEE Proc. Electr. Power Appl. 2006, 153, 750–762. [Google Scholar] [CrossRef] [Green Version]

- Xin, Z.; Mattavelli, P.; Yao, W.; Yang, Y.; Blaabjerg, F.; Loh, P.C. Mitigation of Grid-Current Distortion for LCL-Filtered Voltage-Source Inverter With Inverter-Current Feedback Control. IEEE Trans. Power Electron. 2018, 33, 6248–6261. [Google Scholar] [CrossRef]

- Wang, J.; Yan, J.D.; Jiang, L.; Zou, J. Delay-dependent stability of single-loop controlled grid-connected inverters with LCL filters. IEEE Trans. Power Electron. 2016, 31, 743–757. [Google Scholar] [CrossRef] [Green Version]

- Wu, W.; Liu, Y.; He, Y.; Chung, H.S.; Liserre, M.; Blaabjerg, F. Damping Methods for Resonances Caused by LCL-Filter-Based Current-Controlled Grid-Tied Power Inverters: An Overview. IEEE Trans. Ind. Electron. 2017, 64, 7402–7413. [Google Scholar] [CrossRef] [Green Version]

- Dannehl, J.; Wessels, C.; Fuchs, F.W. Limitations of Voltage-Oriented PI Current Control of Grid-Connected PWM Rectifiers With LCL Filters. IEEE Trans. Ind. Electron. 2009, 56, 380–388. [Google Scholar] [CrossRef]

- Holmes, D.G.; Lipo, T.A.; Mcgrath, B.P.; Kong, W.Y. Optimized design of stationary frame three phase AC current regulators. IEEE Trans. Power Electron. 2009, 24, 2417–2426. [Google Scholar] [CrossRef]

- Holmes, D.G.; Lipo, T.A. Pulse Width Modulation For Power Converters Principles and Practice; IEEE Press: Manhattan, NY, USA, 2003. [Google Scholar]

- Srita, S.; Somkun, S. 3-Phase LCL-Filtered Grid-Connected VSC Modeling. Mendeley Data. 2022. Available online: https://data.mendeley.com/datasets/xbpchksg3k/1 (accessed on 1 February 2022).

- Golestan, S.; Freijedo, F.D.; Guerrero, J.M. A Systematic Approach to Design High-Order Phase-Locked Loops. IEEE Trans. Power Electron. 2015, 30, 2885–2890. [Google Scholar] [CrossRef] [Green Version]

- Åström, K.J.; Hägglund, T. PID Controllers: Theory, Design, and Tuning, 2nd ed.; ISA: Research Triangle Park, NC, USA, 1995. [Google Scholar]

- Yepes, A.G.; Freijedo, F.D.; Doval-Gandoy, J.; Lopez, O.; Malvar, J.; Fernandez-Comesana, P. Effects of discretization methods on the performance of resonant controllers. IEEE Trans. Power Electron. 2010, 25, 1692–1712. [Google Scholar] [CrossRef]

- Somkun, S. High performance current control of single-phase grid-connected converter with harmonic mitigation, power extraction and frequency adaptation capabilities. IET Power Electron. 2021, 14, 352–372. [Google Scholar] [CrossRef]

- Provicial Electricity Authority, Provincial Electricity Authority’s Regulation on the Power Network System Interconnection Code. 2016. Available online: https://www.pea.co.th/Portals/0/Document/vspp/PEA%20Interconnection%20Code%202016.pdf (accessed on 1 February 2022).

- IEEE Std 1547–2018 (Revision of IEEE Std 1547–2003); IEEE Standard for Interconnection and Interoperability of Distributed Energy Resources with Associated Electric Power Systems Interfaces; IEEE: Manhattan, NY, USA, 2018; pp. 1–138. [CrossRef]

- Trinh, Q.N.; Wang, P.; Tang, Y.; Koh, L.H.; Choo, F.H. Compensation of DC Offset and Scaling Errors in Voltage and Current Measurements of Three-Phase AC/DC Converters. IEEE Trans. Power Electron. 2018, 33, 5401–5414. [Google Scholar] [CrossRef]

- Somkun, S.; Sirisamphanwong, C.; Sukchai, S. A DSP-based interleaved boost DC-DC converter for fuel cell applications. Int. J. Hydrogen Energy 2015, 40, 6391–6404. [Google Scholar] [CrossRef]

- Somkun, S. Unbalanced synchronous reference frame control of singe-phase stand-alone inverter. Int. J. Electr. Power Energy Syst. 2019, 107, 332–343. [Google Scholar] [CrossRef]

- Somkun, S.; Chunkag, V. Unified unbalanced synchronous reference frame current control for single-phase grid-connected voltage-source converters. IEEE Trans. Ind. Electron. 2016, 63, 5425–5436. [Google Scholar] [CrossRef]

| Platforms | Products | Cost | Implementation Effort |

|---|---|---|---|

| Simulation platform 1 | MATLAB/Simulink with Simscape and Simscape Electrical | 11,800 USD | Little |

| Simulation platform 2 & proposed method | MATLAB/Simulink | 5900 USD | Moderate |

| Prototype platform 1 | dSPACE Microlabbox Associated MATLAB/Simulink products | +30,000 USD | Little |

| Prototype platform 2 | dSPACE Microlabbox OPAL-RT OP4510 Associated MATLAB/Simulink products | +80,000 USD | Little |

| Prototype platform 2 | Texas Instruments LaunchXL379D Power electronic hardware for 5-kVA 3-ph VSC | 2000 USD | Hard |

| Parameters | Value |

|---|---|

| Nominal grid voltage | Three-phase 380 V line-line 50 Hz |

| Nominal power | 5 kVA |

| Nominal DC bus voltage | 650 V |

| DC bus capacitor, | 780 µF |

| Switching frequency, | 10 kHz |

| Sampling frequency, | 20 kHz |

| DC bus resistor, | 94 kΩ |

| Converter-side inductor, | 1.4 mH |

| Winding resistance of , | 0.110 Ω |

| Grid-side inductor, | 0.7 mH |

| Winding resistance of , | 0.042 Ω |

| Filter capacitor, | 1.94 µF |

| Series resistor, | 0.001 Ω |

| Base voltage, | 311 V |

| Base current, | 10.74 A |

| Base impedance, | 28.88 Ω |

| Parameters | PLL | Current Control |

|---|---|---|

| Bandwidth | 61.3 Hz | 1111 Hz |

| Phase margin | 45° | 60° |

| Proportional gain, | 1.2247 | 0.4922 |

| Integral gain, | 0.0096 | 0.0172 |

| Correction gain, | 0.0192 | 0.0344 |

| Resonant gains, and | - | 114.5518 |

| Low-pass filter, | 0.0045 | - |

| THD | |||||

|---|---|---|---|---|---|

| 220 Vrms | 4% | 2% | 1% | 1% | 4.69% |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Srita, S.; Somkun, S.; Kaewchum, T.; Rakwichian, W.; Zacharias, P.; Kamnarn, U.; Thongpron, J.; Amorndechaphon, D.; Phattanasak, M. Modeling, Simulation and Development of Grid-Connected Voltage Source Converter with Selective Harmonic Mitigation: HiL and Experimental Validations. Energies 2022, 15, 2535. https://doi.org/10.3390/en15072535

Srita S, Somkun S, Kaewchum T, Rakwichian W, Zacharias P, Kamnarn U, Thongpron J, Amorndechaphon D, Phattanasak M. Modeling, Simulation and Development of Grid-Connected Voltage Source Converter with Selective Harmonic Mitigation: HiL and Experimental Validations. Energies. 2022; 15(7):2535. https://doi.org/10.3390/en15072535

Chicago/Turabian StyleSrita, Suparak, Sakda Somkun, Tanakorn Kaewchum, Wattanapong Rakwichian, Peter Zacharias, Uthen Kamnarn, Jutturit Thongpron, Damrong Amorndechaphon, and Matheepot Phattanasak. 2022. "Modeling, Simulation and Development of Grid-Connected Voltage Source Converter with Selective Harmonic Mitigation: HiL and Experimental Validations" Energies 15, no. 7: 2535. https://doi.org/10.3390/en15072535

APA StyleSrita, S., Somkun, S., Kaewchum, T., Rakwichian, W., Zacharias, P., Kamnarn, U., Thongpron, J., Amorndechaphon, D., & Phattanasak, M. (2022). Modeling, Simulation and Development of Grid-Connected Voltage Source Converter with Selective Harmonic Mitigation: HiL and Experimental Validations. Energies, 15(7), 2535. https://doi.org/10.3390/en15072535